A New Low-Voltage Low-Power Dual-Mode VCII-Based SIMO Universal Filter

Abstract

1. Introduction

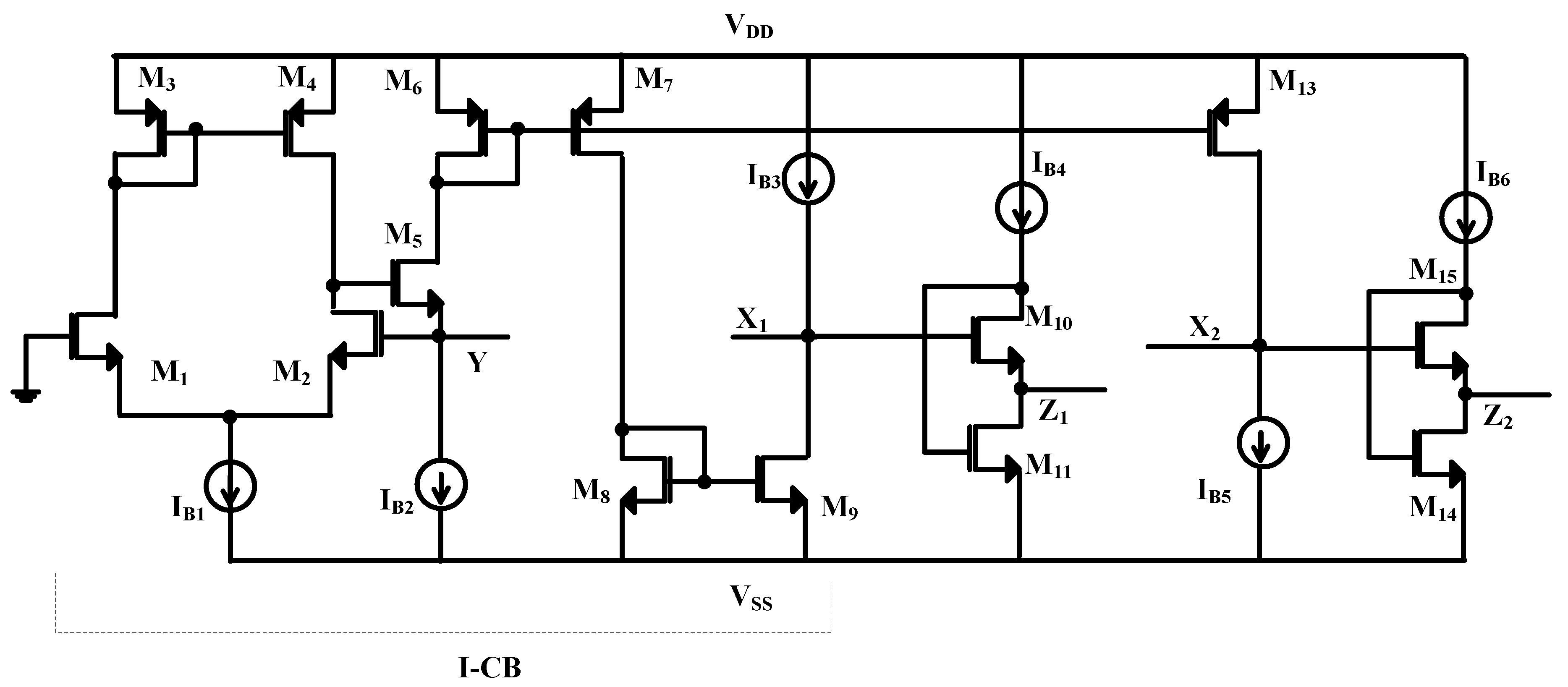

2. The VCII Internal Circuit Design

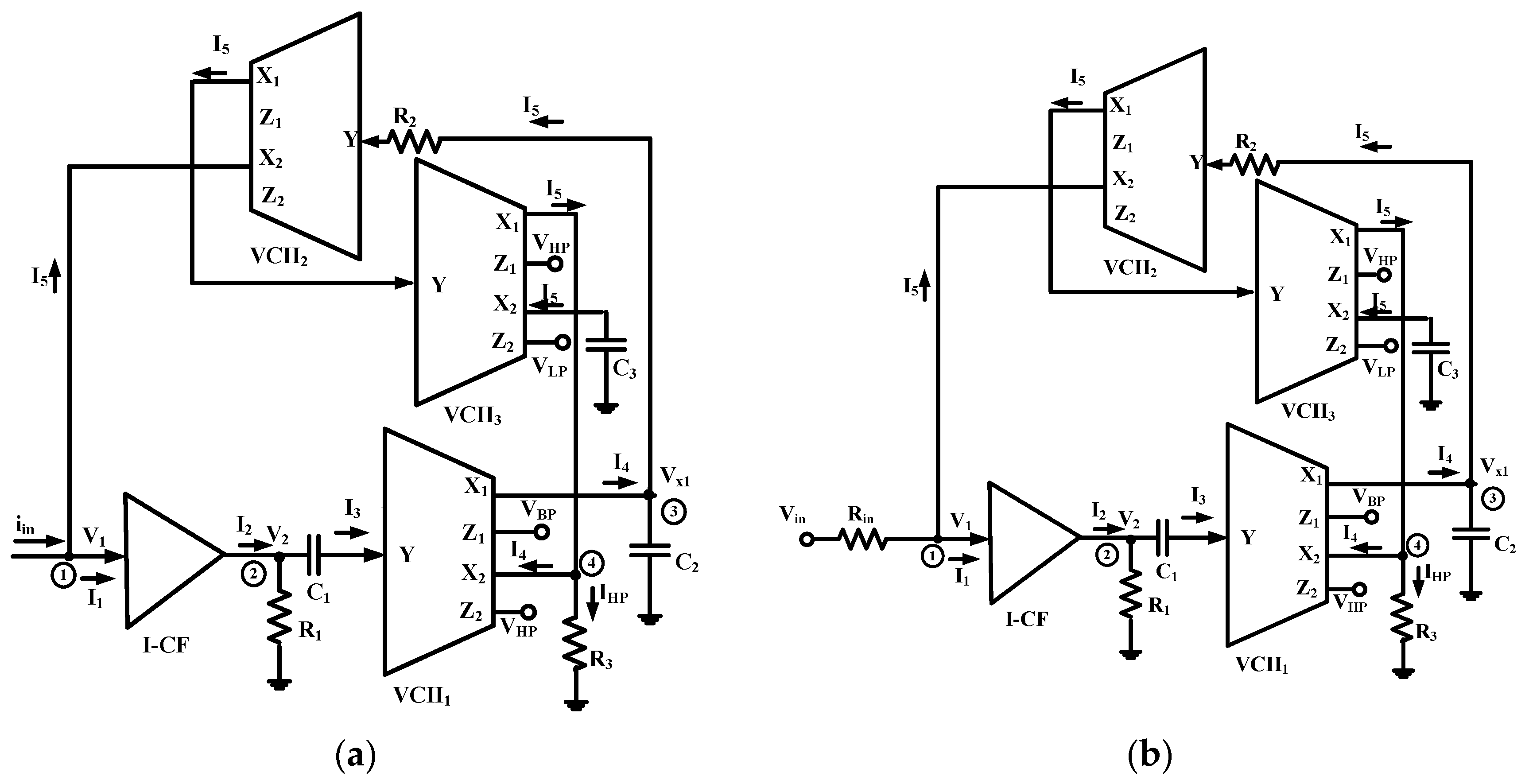

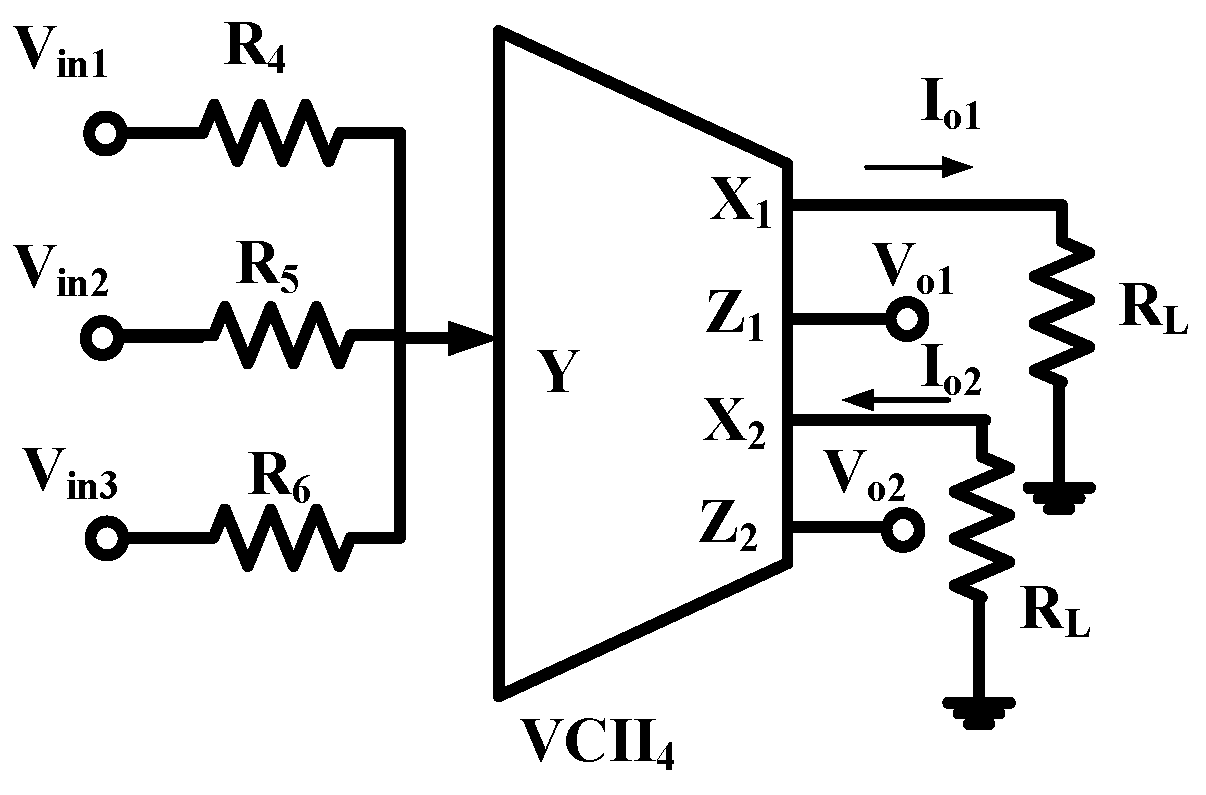

3. The Proposed Universal Filter

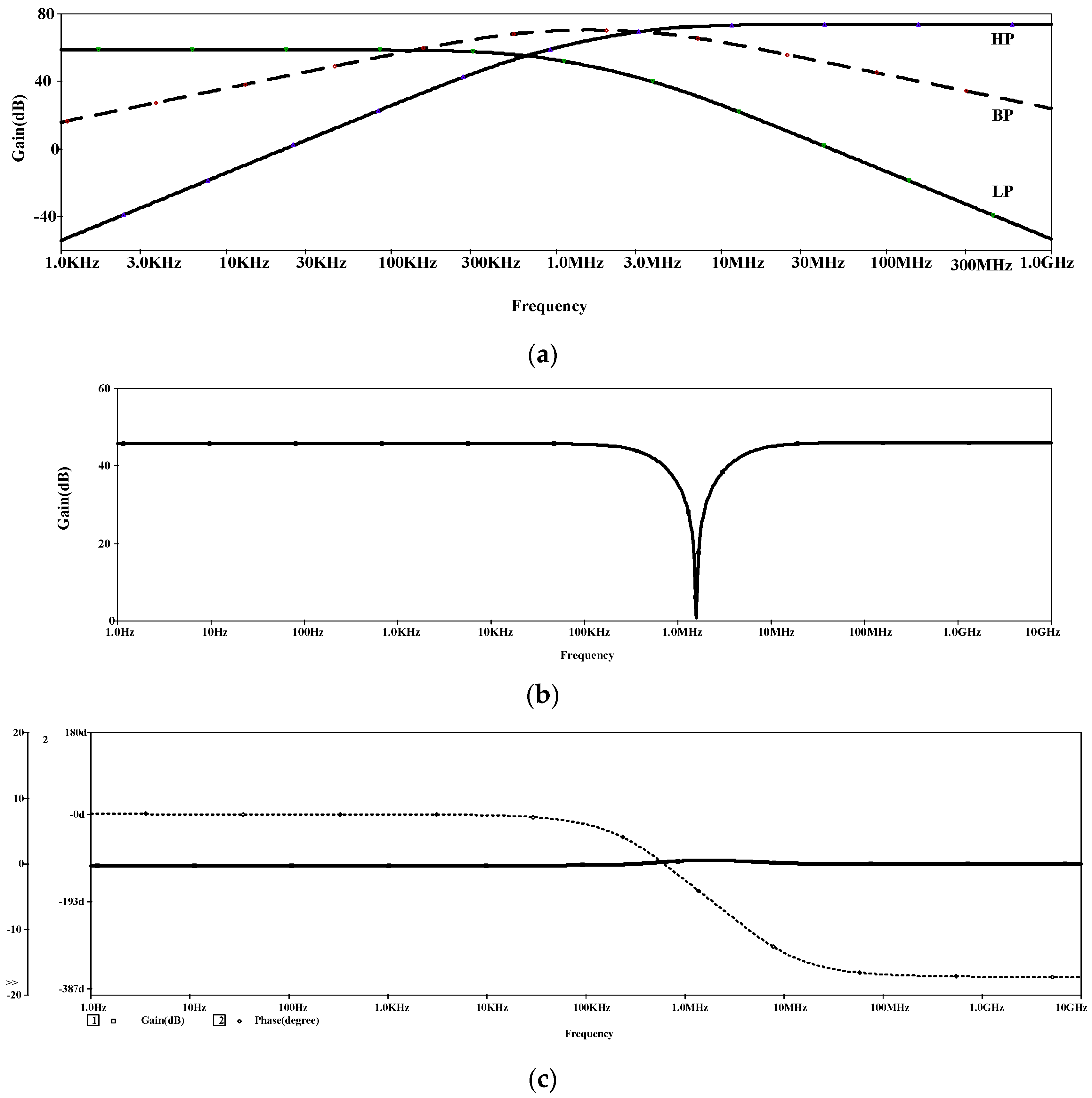

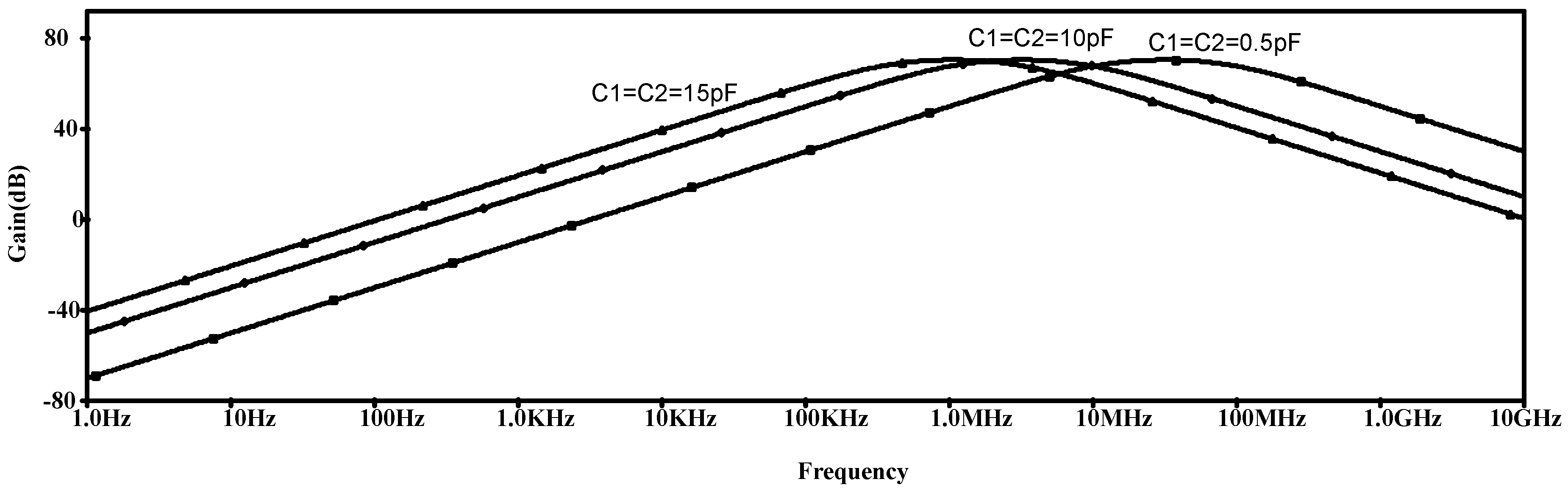

4. Non-Ideal Analysis

5. Simulation Results and Comparative Analysis

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Alexander, C.; Sadiku, M. Fundamental of Electric Circuits, 2nd ed.; McGraw-Hill: New York, NY, USA, 2004. [Google Scholar]

- Ibrahim, M.; Minaei, S.; Kuntman, H. A 22.5 MHz current-mode KHN-biquad using differential voltage current conveyor and grounded passive elements. AEU Int. J. Electron. Commun. 2005, 59, 311–318. [Google Scholar] [CrossRef]

- Stornelli, V.; Pantoli, L.; Leuzzi, G.; Ferri, G. Fully differential DDA-based fifth and seventh order Bessel low pass filters and buffers for DCR radio systems. Analog Integr. Circuits Signal Process. 2013, 75, 305–310. [Google Scholar] [CrossRef]

- Alzaher, H.; Al-Ghamdi, M.; Ismail, M. CMOS low-power bandpass IF filter for Bluetooth. IET Circuits Devices Syst. 2007, 1, 7–12. [Google Scholar] [CrossRef]

- Prommee, P.; Saising, E. CMOS-based high-order LP and BP filters using biquad functions. IET Circuits Devices Syst. 2018, 12, 326–334. [Google Scholar] [CrossRef]

- Shah, N.; Malik, M. High impedance voltage- and current-mode multifunction filters. AEU Int. J. Electron. Commun. 2005, 59, 262–266. [Google Scholar] [CrossRef]

- Chen, H. Tunable versatile current-mode universal filter based on plus-type DVCCs. AEU Int. J. Electron. Commun. 2012, 66, 332–339. [Google Scholar] [CrossRef]

- Singh, S.; Maheshwari, S.; Mohan, J.; Chauhan, D. Electronically Tunable Current-Mode Universal Biquad Filter Based on the CCCCTA. In Proceedings of the International Conference on Advances in Recent Technologies in Communication and Computing, Kottayam, India, 27–28 October 2009; pp. 424–429. [Google Scholar]

- Horng, J.; Hou, C.; Huang, W.; Yang, D. Voltage/Current-Mode Multifunction Filters Using One Current Feedback Amplifier and Grounded Capacitors. Circuits Syst. 2011, 2, 60–64. [Google Scholar] [CrossRef]

- Arora, T.; Rana, U. Multifunction Filter Employing Current Differencing Buffered Amplifier. Circuits Syst. 2016, 7, 543–550. [Google Scholar] [CrossRef][Green Version]

- Sagbas, M.; Koksal, M. A New Multi-mode Multifunction Filter Using CDBA. In Proceedings of the European Conference on Circuit Theory and Design, Cork, Ireland, 28 August–2 September 2005. [Google Scholar]

- Kumngern, M. Current-Mode Multifunction Biquadratic Filter Using a Single MCCCDTA. In Proceedings of the IEEE International Conference on Cyber Technology in Automation, Control, and Intelligent Systems (CYBER), Bangkok, Thailand, 27–31 May 2012; pp. 115–118. [Google Scholar]

- Kamat, D.; Ananda Mohan, P.; Gopalakrishna Prabhu, K. Current-mode operational transconductance amplifier-capacitor biquad filter structures based on Tarmy–Ghausi active-RC filter and second-order digital all-pass filters. IET Circuits Devices Syst. 2010, 4, 346–364. [Google Scholar] [CrossRef]

- Klungtong, S.; Thanapatay, D.; Jaikla, W. Three-Input Single-Output Voltage-Mode Multifunction Filter with Electronic Controllability Based on Single Commercially Available IC. Act. Passiv. Electron. Compon. 2017, 2017, 5240751. [Google Scholar] [CrossRef]

- Kumngern, M.; Supavarasuwat, P. A Voltage-Mode Three-Input One-Output Multifunction Filter Using Single FDCCII. In Proceedings of the 20th Asia-Pacific Conference on Communication (APCC2014), Pattaya, Thailand, 1–3 October 2014. [Google Scholar]

- Chanapromma, C.; Jaikla, W.; Chaichana, A. New Realization of Single CFCTA-Based Voltage-Mode Multifunction Filter. In Proceedings of the 3rd International Conference on Control and Robotics Engineering, Nagoya, Japan, 20–23 April 2018. [Google Scholar]

- Chaichana, A.; Sangyaem, S.; Jaikla, W. Multifunction Voltage-Mode Filter Using Single Voltage Differencing Differential Difference Amplifier. MATEC Web Conf. 2017, 95, 14003. [Google Scholar] [CrossRef]

- Ferri, G.; Stornelli, V. A 0.18 µm CMOS DDCCII for Portable LV-LP Filters. Radioengineering 2013, 22, 434–439. [Google Scholar]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High performance voltage output filter realizations using second generation voltage conveyor. Int. J. RF Microw. Comput.-Aided Eng. 2018, 28, e21534. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. An Overview on the Second Generation Voltage Conveyor: Features, Design and Applications. IEEE Trans. Circuits Syst. II Express Briefs 2018, 66, 547–551. [Google Scholar] [CrossRef]

- Carvajal, R.; Ramirez-Angulo, J.; Lopez-Martin, A.; Torralba, A.; Galan, J.; Carlosena, A.; Chavero, F. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Chen, H. Single FDCCII-based universal voltage-mode filter. AEU Int. J. Electron. Commun. 2009, 63, 713–719. [Google Scholar] [CrossRef]

| M1–M2 | 18/0.36 | M8–M9 | 9/0.9 |

| M3–M4 | 18/0.9 | M13 | 18/0.9 |

| M5 | 9/0.36 | M10, M15 | 9/0.36 |

| M6–M7 | 18/0.9 | M11, M14 | 0.9/0.36 |

| Variation in VTH and β of Transistors | ω0 | Q |

|---|---|---|

| 3% | 1.68 MHz | 0.32 |

| 5% | 1.7 MHz | 0.328 |

| # of Floating Capacitors | Used Active Building Block | Vss-Vdd (V) | Pd (mW) | Outputs | Configuration | I–O Signals | ω0 | Extra Voltage Buffer | ||

|---|---|---|---|---|---|---|---|---|---|---|

| [6] | 1 | 0 | FTFN, OTA | NA | NA | LP, BP, BS | SIMO | V–V | 7.95 KHz | Yes |

| 2 | 2 | FTFN, OTA | NA | NA | LP, HP | SIMO | I–I | 7.95 KHz | - | |

| [7] | 0 | DVCC | ±0.9 | 0.462 | BP, BS, HP | MIMO | I–I | 3.18 MHz | -* | |

| [8] | 0 | CCCCTA | ±1.85 | NA | LP, BP, HP | SIMO | I–I | 1.5 MHz | - | |

| [9] | 1 | 0 | CFOA | NA | NA | LP, BP, HP | SIMO | I–I | <1 MHz | Current buffer required at output |

| 2 | 0 | CFOA | NA | NA | LP, BP | SIMO | V–V | <1 MHz | Yes | |

| [10] | 0 | CDBA | ±1.25 | NA | LP, BP, HP | SIMO | I–V | 10 MHz | No | |

| [11] | 2 | CDBA | ±5 | NA | AP, LP, BP | SIMO | I–V | 1 MHz | No | |

| [12] | 0 | MCCCDTA | ±3 | NA | LP, BP, HP, BS, AP | MISO | I–I | 1.27 MHz | - | |

| [14] | 2 | LT1228 | ±5 | NA | LP, BP, HP, BS, AP | MISO | V–V | 159.19 KHz | No | |

| [15] | 2 | FDCCII | ±1.65 | NA | LP, BP, HP, BS, AP | MISO | V–V | 1 MHz | No | |

| [16] | 2 | CFCTA | ±5 | NA | LP, BP, HP, BS, AP | MISO | V–V | 2.8 MHz | Yes | |

| [17] | 2 | I-CB VDDDA | ±1.25 | NA | LP, BP, HP, BS, AP | MISO | V–V | 1.074 MHz | Yes | |

| This Work | 1 | I-CB, VCII± | ±0.9 | 1.47 | HP, BP, LP I-AP, NI-AP, I-BS, NI-BP | SIMO | I/V–V/I | 1–32 MHz | No | |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. A New Low-Voltage Low-Power Dual-Mode VCII-Based SIMO Universal Filter. Electronics 2019, 8, 765. https://doi.org/10.3390/electronics8070765

Safari L, Barile G, Ferri G, Stornelli V. A New Low-Voltage Low-Power Dual-Mode VCII-Based SIMO Universal Filter. Electronics. 2019; 8(7):765. https://doi.org/10.3390/electronics8070765

Chicago/Turabian StyleSafari, Leila, Gianluca Barile, Giuseppe Ferri, and Vincenzo Stornelli. 2019. "A New Low-Voltage Low-Power Dual-Mode VCII-Based SIMO Universal Filter" Electronics 8, no. 7: 765. https://doi.org/10.3390/electronics8070765

APA StyleSafari, L., Barile, G., Ferri, G., & Stornelli, V. (2019). A New Low-Voltage Low-Power Dual-Mode VCII-Based SIMO Universal Filter. Electronics, 8(7), 765. https://doi.org/10.3390/electronics8070765