Experimental Study on the Reliability of PBGA Electronic Packaging under Shock Loading

Abstract

:1. Introduction

2. Test Design

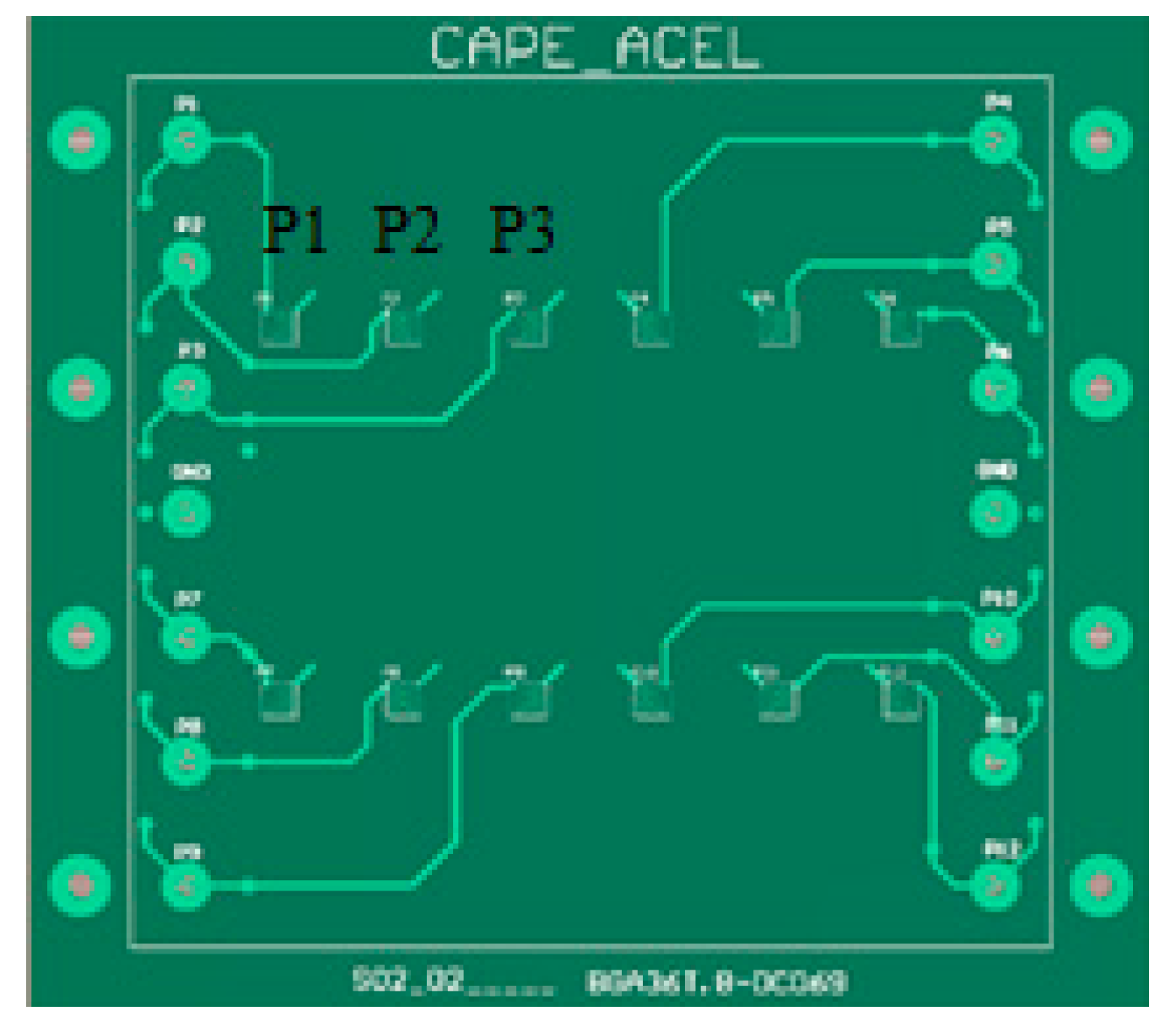

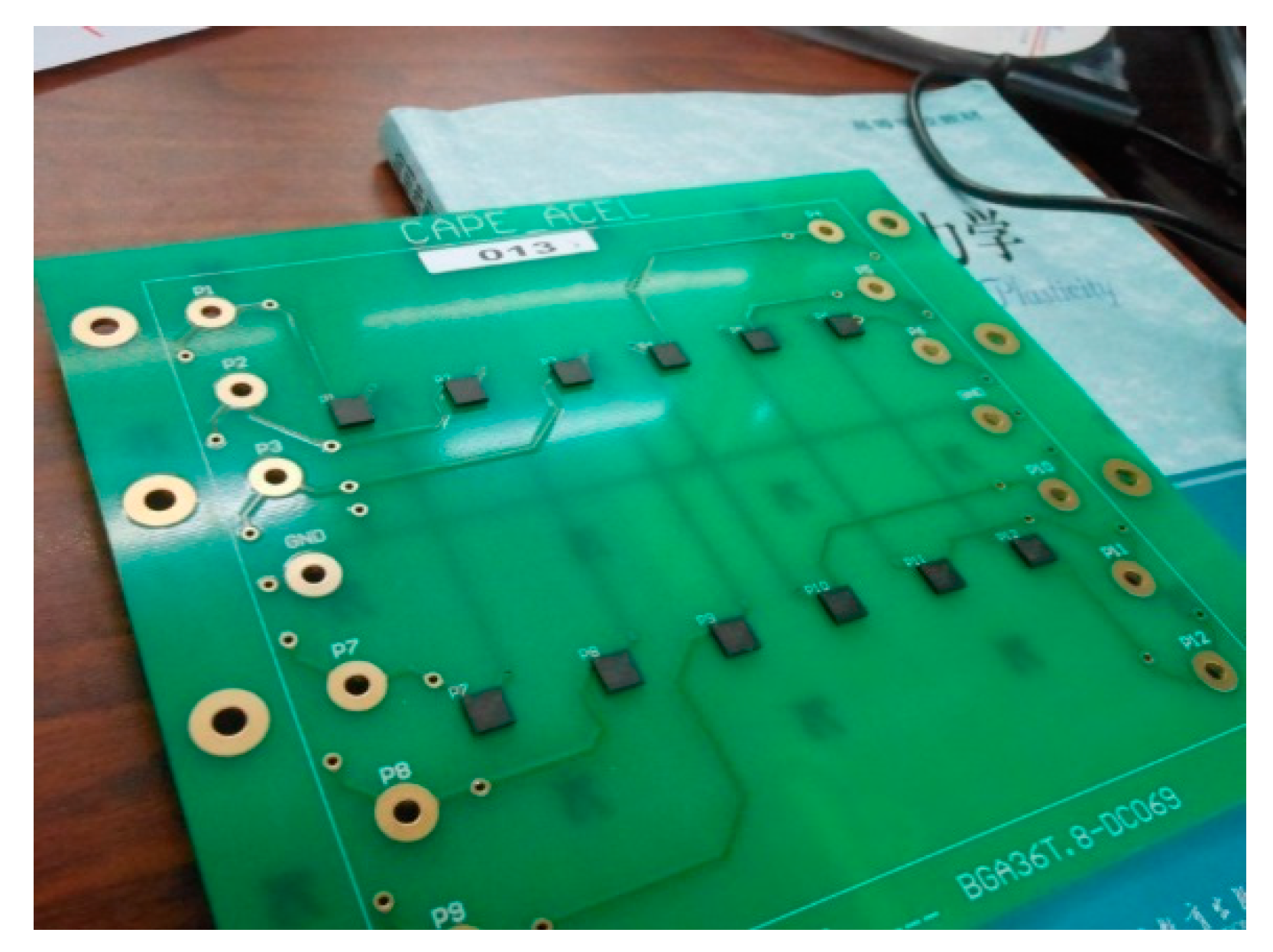

2.1. Test Sample Design

2.2. Test Loading

3. Monitoring of Test Data

4. Test Data Analysis

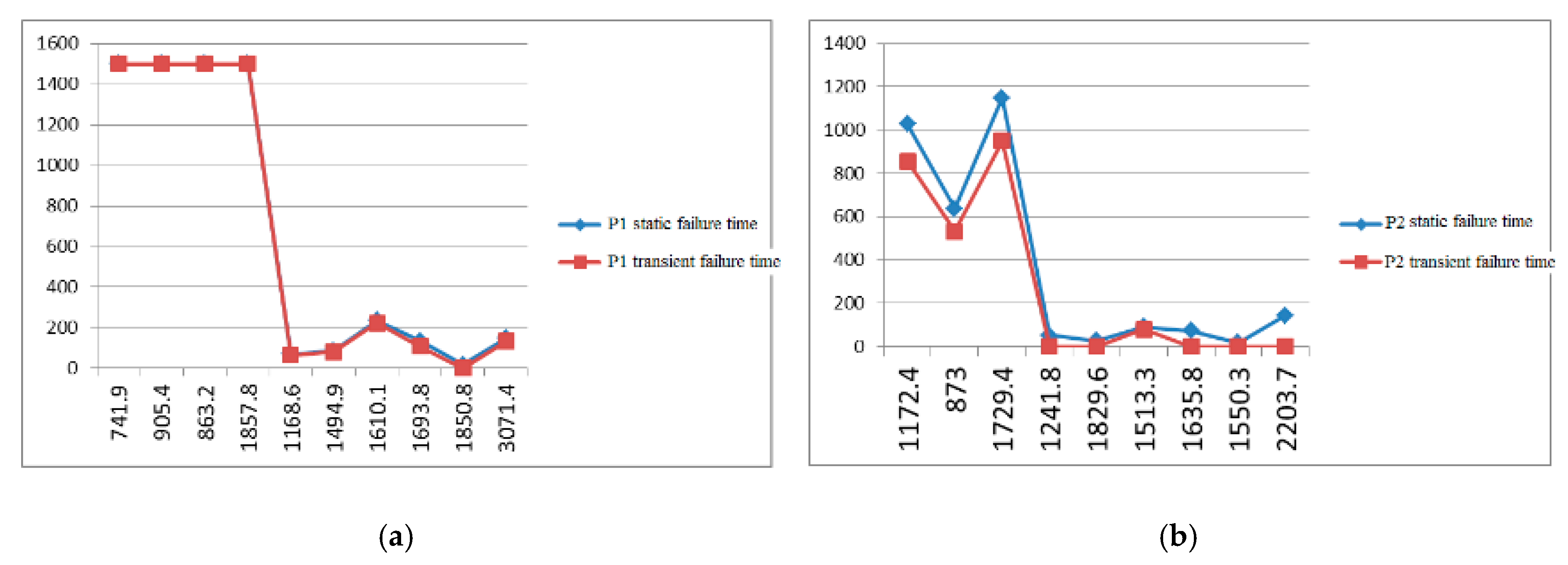

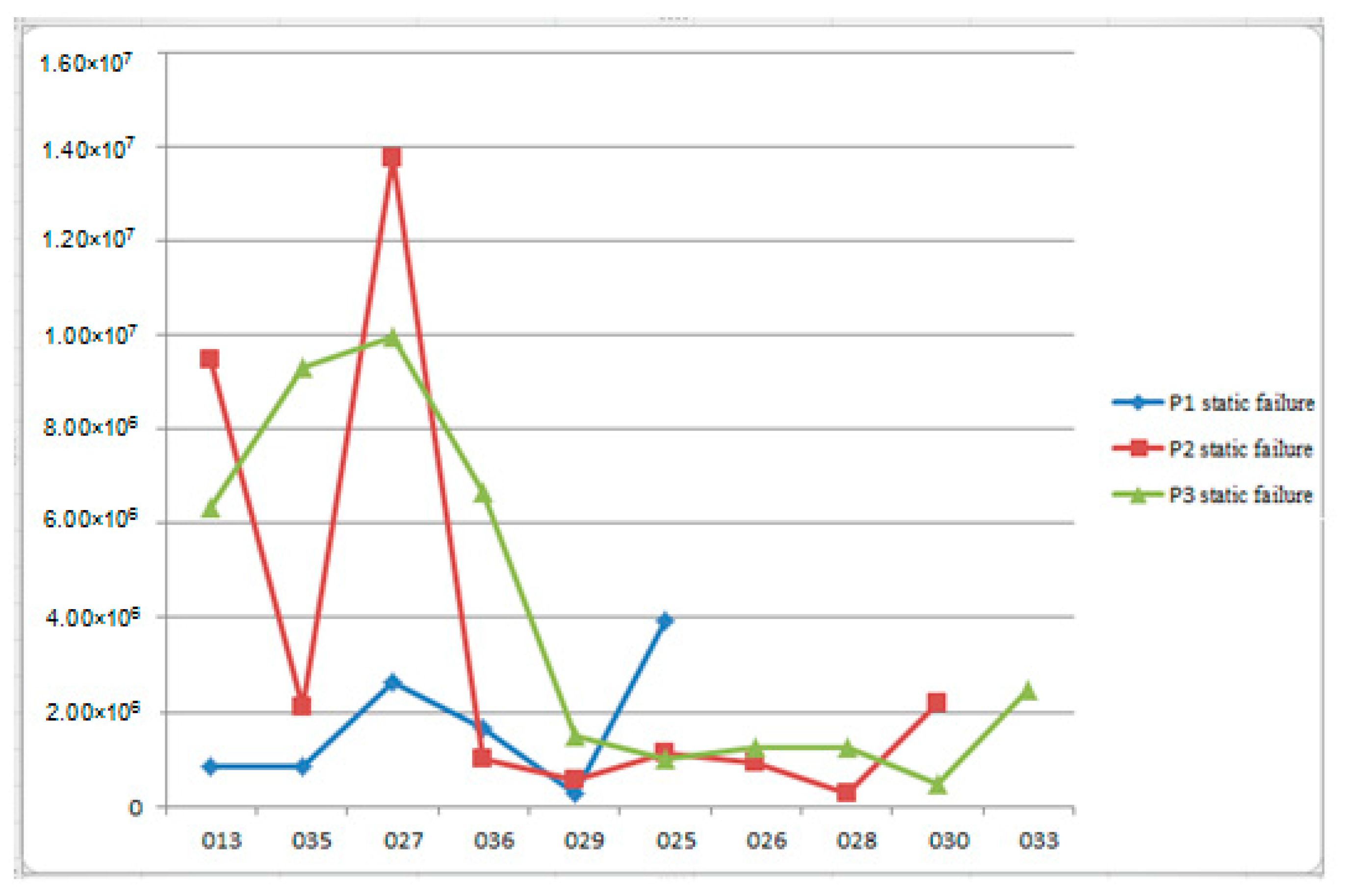

4.1. Data Analysis

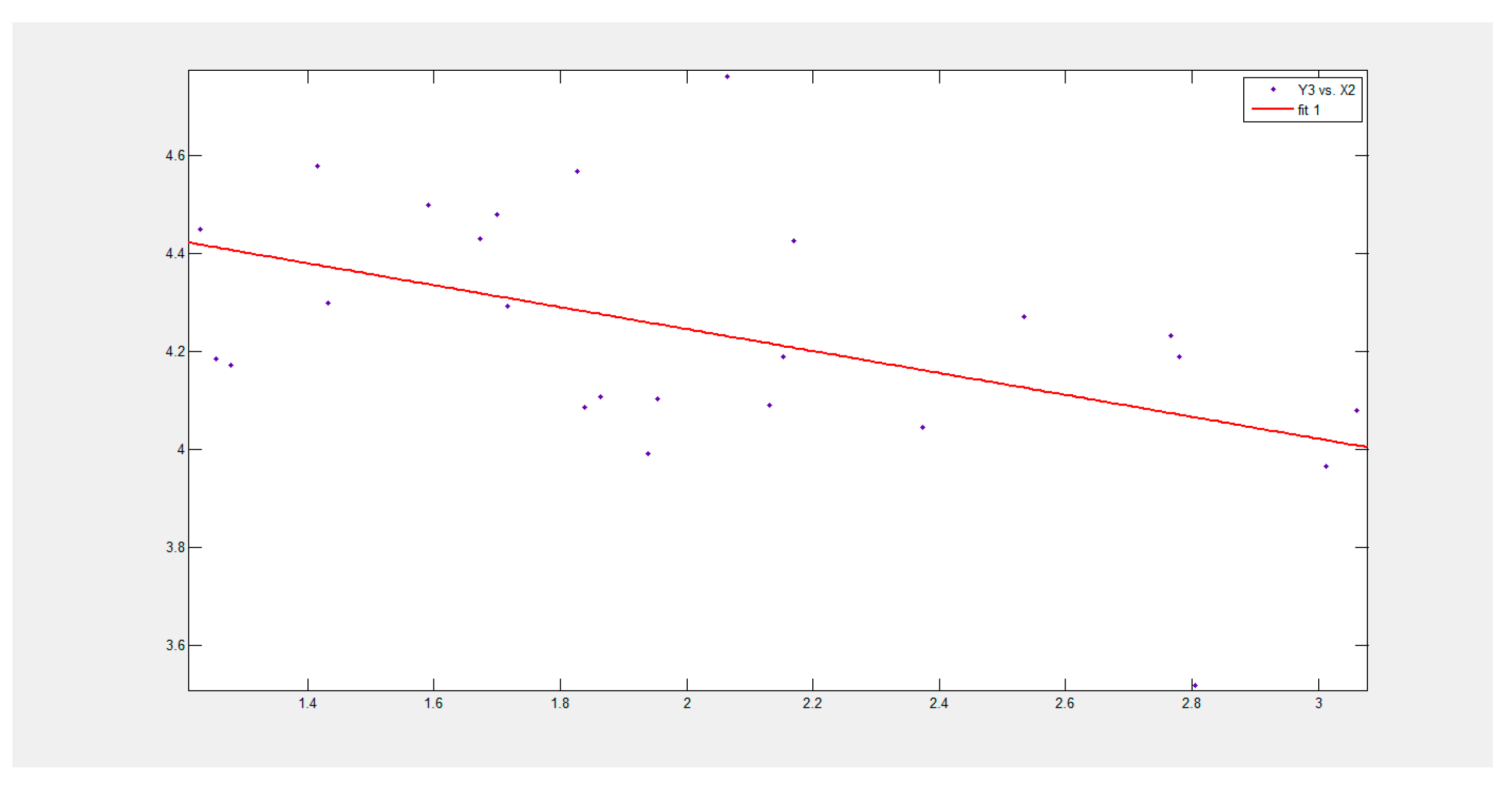

4.2. Stress–Life Analysis

4.3. Strain Energy Contrast Analysis

4.4. Solder Joint Reliability Analysis

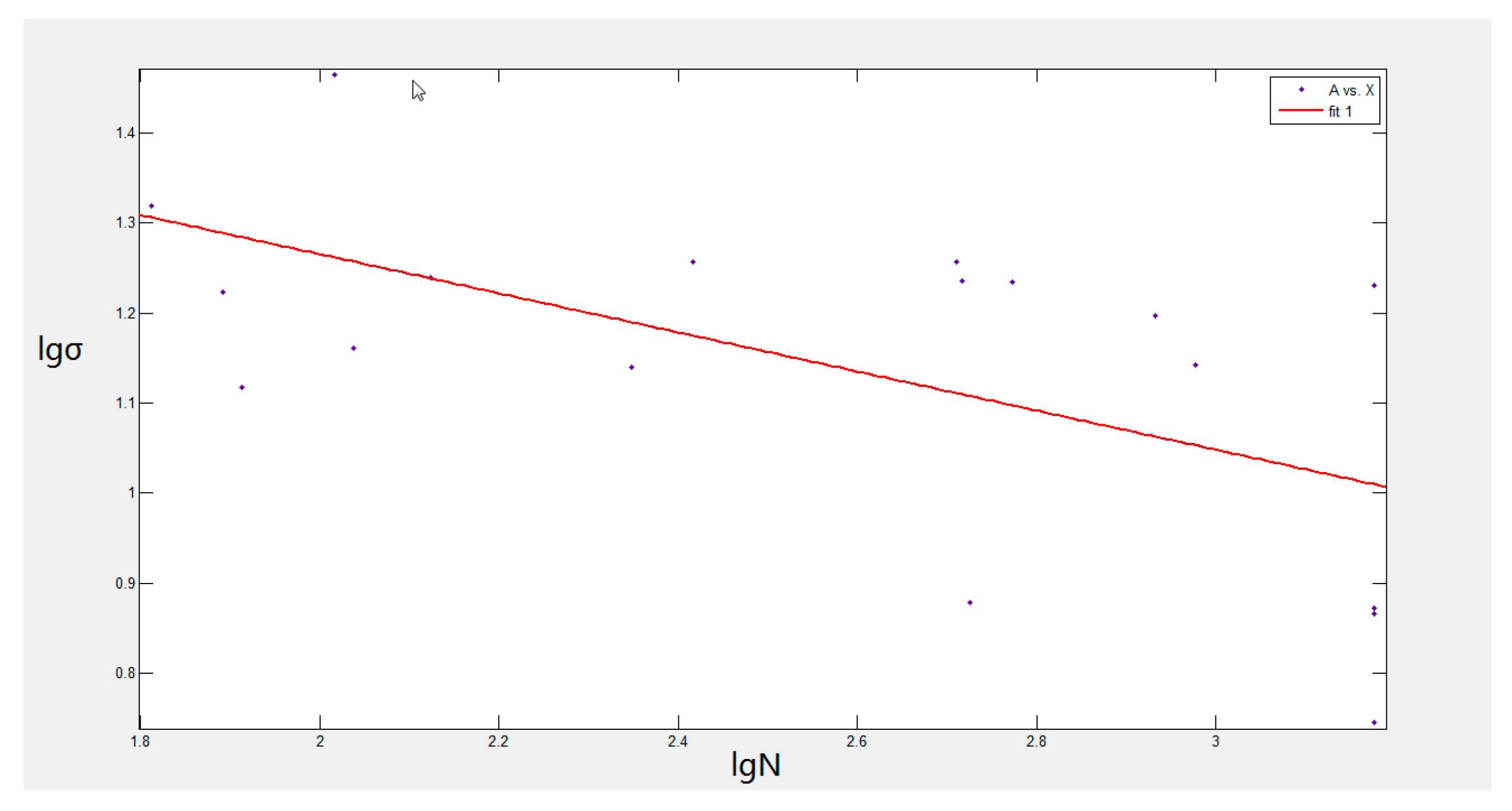

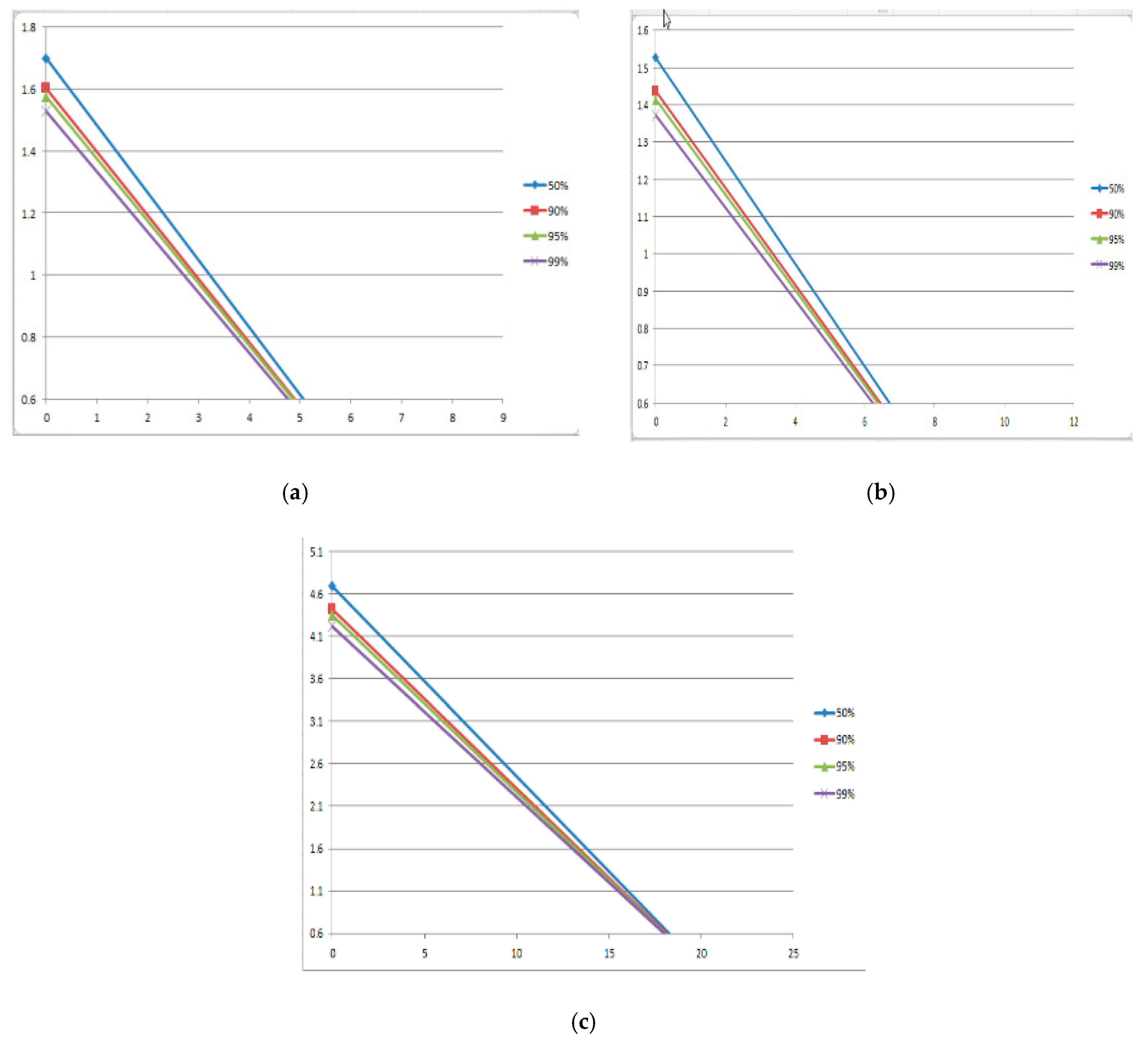

4.5. P-S-N Curve

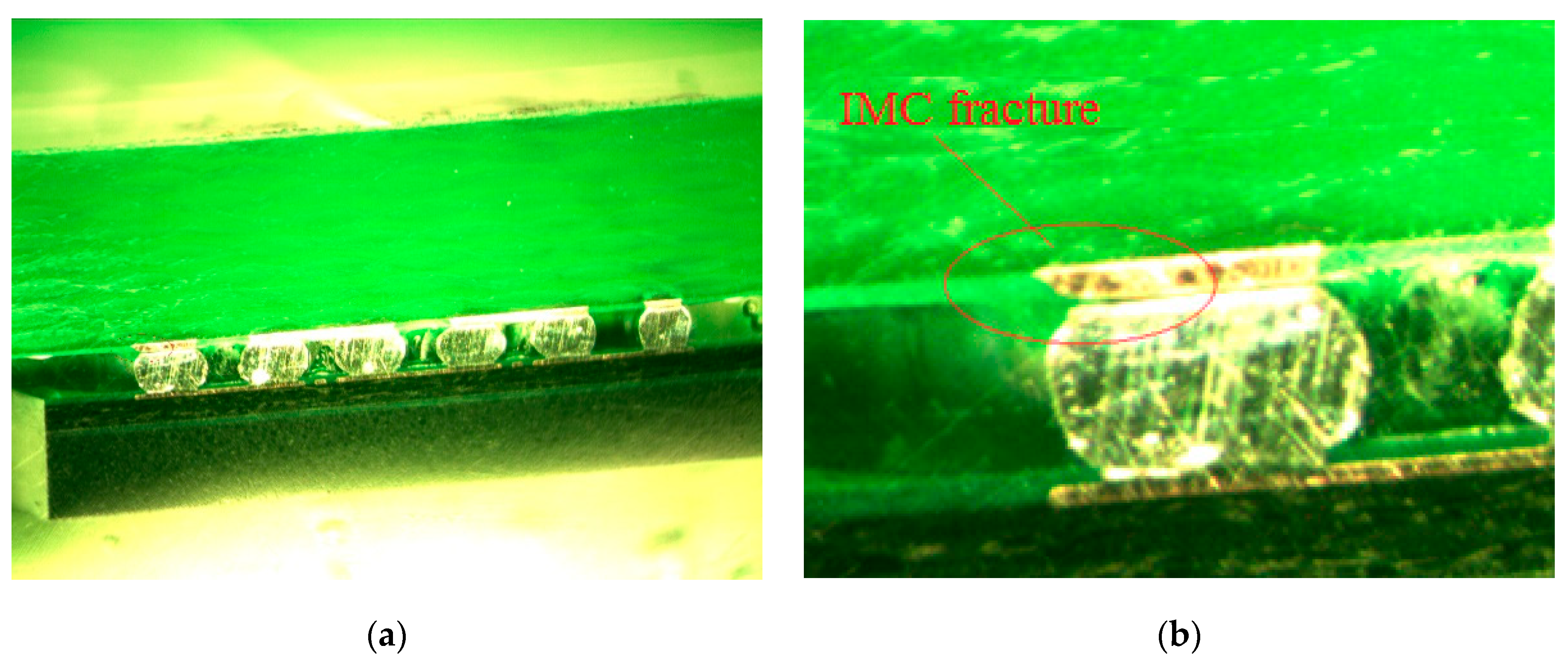

4.6. Microscopic Analysis of Failure Solder Joints

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Chinese Electronic Society Production Technology Books Editorial Board. Microelectronics Packaging Technology; China University of Science and Technology Press: Hefei, China, 2003; pp. 121–156. [Google Scholar]

- Wu, J.; Song, G.S.; Yeh, C.-P.; Wyatt, K. Drop/Impact Simulation and Test Validation of Telecommunication Products. In Proceedings of the Therm’98. Sixth Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (Cat. No.98CH36208), Seattle, WA, USA, 27–30 May 1998; pp. 330–336. [Google Scholar]

- Goyal, S.; Upasani, S.; Patel, D.M. Improving Impact Tolerance of Portable Electronic Products: Case Study of Cellular Phones. Exp. Mech. 1999, 39, 43–52. [Google Scholar] [CrossRef]

- Goyal, S.; Buratynski, E.K. Methods for Realistic Drop-Testing. Int. J. Microcircuits Electron. Packag. 2000, 23, 45–52. [Google Scholar]

- Buratynski, E.K.; Goyal, S.; Eugene, J.R. Realistic, Repeatable and Controllable Drop Testing. U.S. Patent US6374661B1, 23 April 2002. [Google Scholar]

- Ong, Y.C.; Shim, V.P.W.; Chai, T.C.; Lim, C.T. Comparison of Mechanical Response of PCB Subjected to Product-Level and Board-Level Drop Impact Tests. In Proceedings of the 5th Electronics Packaging Technology Conference (EPTC 2003), Singapore, 12–12 December 2003; pp. 223–227. [Google Scholar]

- Luan, J.E.; Tee, T.Y. Novel Board Level Drop Test Simulation using Implicit Transient Analysis with Input-G Method. In Proceedings of the 6th Electronics Packaging Technology Conference (EPTC 2004) (IEEE Cat. No.04EX971), Singapore, 8–10 December 2004; pp. 671–677. [Google Scholar]

- Tee, T.Y.; Luan, J.E.; Pek, E.; Lim, C.T.; Zhong, Z. Novel Numerical and Experimental Analysis of Dynamic Responses under Board Level Drop Test. In Proceedings of the 5th International Conference on Thermal and Mechanical Simulation and Experiments in Microelectronics and Microsystems, Brussels, Belgium, 10–12 May 2004; pp. 133–140. [Google Scholar]

- Luan, J.E.; Tee, T.Y.; Pek, E.; Lim, C.T.; Zhong, Z.; Zhou, J. Advanced Numerical and Experimental Techniques for Analysis of Dynamic Responses and Solder Joint Reliability During Drop Impact. IEEE Trans. Compon. Packag. Technol. 2006, 29, 449–456. [Google Scholar] [CrossRef]

- Luan, J.E.; Tee, T.Y. Analysis of PCB Subassembly Dynamic Responses using Integrated Analytical, Numerical and Experimental Techniques. In Proceedings of the 6th International Conference on Electronic Packaging Technology, Shenzhen, China, 30 August–2 September 2005. [Google Scholar]

- Chong, D.Y.R.; Che, F.X.; Pang, J.H.L.; Ng, K.; Tan, J.Y.N.; Low, P.T.H. Drop Impact Reliability testing for Lead-free and Lead-based Soldered IC Packages. Microelectron. Reliab. 2006, 46, 1160–1171. [Google Scholar] [CrossRef]

- Pan, K.; Zhou, B.; Yan, Y. Drop Dynamic Responses and Modal Analysis for Board Level TFBGA. In Proceedings of the 2007 International Symposium on High Density packaging and Microsystem Integration, Shanghai, China, 26–28 June 2007. [Google Scholar]

- Zhou, B. Unleaded portable electronics board level components of TFBGA drop reliability research. Master’s Thesis, Guilin University of Electronic Science and Technology, Guilin, China, June 2007. [Google Scholar]

- Qi, B. Ball grid array BGA seal fabrication of mechanical reliability analysis and prediction. Master’s Thesis, Fudan University, Shanghai, China, June 2007. [Google Scholar]

- Fan, Y.P.; Qi, B.; Wang, J.J. BGA solder ball under the board level drop test of fatigue crack behavior research. Semicond. Technol. 2008, 7, 585–588. [Google Scholar]

- Zhu, Z.J.; Zhao, M.; Guo, Q. PBGA solder joint under the environment of earthquake dynamic response finite element analysis. Vib. Shock. 2006, 25, 73–75. [Google Scholar]

- Qin, F.; Bai, J.; An, T. Board level electronic packaging drop/impact of solder joint stress analysis. J. Beijing Univ. Technol. 2007, 33, 1038–1043. [Google Scholar]

- Bai, J. In the process of the drop/impact the dynamics response of electronic packaging soldering contact. Master’s Thesis, Beijing University of Technology, Beijing, China, June 2007. [Google Scholar]

- Lu, W.S.; Feng, Z.H.; Zou, J.J. PCB based on ANSYS/ls-dyna drop simulation. J. Suzhou Univ. (Eng.) 2006, 26, 42–46. [Google Scholar]

- Zhang, J. BGA solder joints under impact loading should be finite element simulation. J. Sens. Technol. 2006, 12, 1591–1598. [Google Scholar]

- Yau, Y.H.; Hua, S.N. A comprehensive review of drop impact modeling on portable electronic devices. Appl. Mech. Rev. 2011, 64, 020803. [Google Scholar] [CrossRef]

- Zhang, B.; Xi, J.S.; Liu, P.K.; Ding, H. Failure analysis of board-level Sn-Ag-Cu solder interconnections under JEDEC standard drop test. J. Electron. Mater. 2013, 42, 2848–2855. [Google Scholar] [CrossRef]

- Mattila, T.T.; Ruotoistenmaki, H.; Raami, J.; Hokka, J.; Mäkelä, M.; Hussa, E.; Sillanpää, M.; Halkola, M. An approach to adjust the board-level drop test conditions to improve the correlation with product-level drop impact. Microelectron. Reliab. 2014, 54, 785–795. [Google Scholar] [CrossRef]

| PCB Material | Layer Number | Welding Plate and Wire Material | Solder Material | Welding Plate Processing | Resistance Welding | Handling Hole |

|---|---|---|---|---|---|---|

| FR4 | 2 | Cu | Sn63Pb37 | Chemical zedoary | Double sides | Resistance welding |

| Height Parameters | Cycle Parameters | Brake Type and Delay Settings | ||||||

|---|---|---|---|---|---|---|---|---|

| Test-bed’s total height (mm) | Increment sensitivity (mm) | Benchmark height (mm) | Cycle numbers | Time interval (s) | Shock waiting (s) | Trigger brake (ms) | Dropping brake (m/s2) | Delay time (ms) |

| 1500 | 1 | 40 | Given | 0.5 | 0.5 | 5 | 9.8 | 10 |

| Test Condition | Peak Acceleration (g) | Pulse Duration (ms) |

|---|---|---|

| H | 2900 | 0.3 |

| G | 2000 | 0.4 |

| B | 1500 | 0.5 |

| F | 900 | 0.7 |

| A | 500 | 1.0 |

| E | 340 | 1.2 |

| D | 200 | 1.5 |

| C | 100 | 2.0 |

| Strain Maximum (μ) | Stress Maximum (MPa) | Number of First Transient Failures | Number of First Static Failures | |||

|---|---|---|---|---|---|---|

| 1500 g/0.5 ms (Condition B) | Board 013 | P1 | 741.9 | 5.564 | >1,000 | >1,000 |

| P2 | - | - | 514 | 538 | ||

| P3 | 2,057.4 | 18.08 | 261 | 342 | ||

| Board 035 | P1 | 905.4 | 7.334 | >1,000 | >1,000 | |

| P2 | 1,172.4 | 15.75 | 855 | 1027 | ||

| P3 | 1,802.8 | 17.16 | 593 | 603 | ||

| Board 027 | P1 | 863.2 | 7.44 | >1,000 | >1,000 | |

| P2 | 873 | 7.566 | 531 | 637 | ||

| P3 | 1,980.7 | 17.2 | 521 | 585 | ||

| Board 036 | P1 | 1,857.8 | 17.02 | >1,000 | >1,000 | |

| P2 | 1,729.4 | 13.88 | 949 | 1,148 | ||

| P3 | 3,948.3 | 29.13 | 104 | 116 | ||

| 2900 g/0.3 ms (Condition H) | Board 029 | P1 | 1,168.6 | 20.82 | 65 | 69 |

| P2 | 1,241.8 | 31.56 | - | 52 | ||

| P3 | 1,845.6 | 32.69 | - | 50 | ||

| Board 025 | P1 | 1,494.9 | 13.10 | 82 | 87 | |

| P2 | 1,829.6 | 21.70 | - | 27 | ||

| P3 | 2,523.2 | 29.91 | - | 26 | ||

| 2000 g/0.4 ms (Condition G) | Board 026 | P1 | 1,610.1 | 13.80 | 223 | 236 |

| P2 | 1,513.3 | 16.74 | 78 | 90 | ||

| P3 | 2,149.2 | 25.01 | - | 47 | ||

| Board 028 | P1 | 1,693.8 | 14.50 | 109 | 135 | |

| P2 | 1,635.8 | 15.66 | - | 73 | ||

| P3 | 2,360.7 | 26.74 | - | 39 | ||

| Board 030 | P1 | 1,850.8 | 16.02 | - | 19 | |

| P2 | 1,550.3 | 19.76 | - | 18 | ||

| P3 | 2,306.4 | 24.41 | - | 17 | ||

| Board 033 | P1 | 3,071.4 | 17.35 | 133 | 148 | |

| P2 | 2,203.7 | 14.03 | - | 142 | ||

| P3 | 2,806.3 | 26.29 | - | 67 |

| Strain Energy Density of a Single Drop (J/m3) | Strain Energy Density of the First Transient Failure (J/m3) | Strain Energy Density of the First Statistic Failure (J/m3) | ||

|---|---|---|---|---|

| Board 013 | P1 | 2,063.97 | >2,063,970 | >2,063,970 |

| P2 | - | - | - | |

| P3 | 18,595.28 | 4,853,368.08 | 6,359,585.76 | |

| Board 035 | P1 | 3,320.10 | >3,320,100 | >3,320,100 |

| P2 | 9,232.65 | 7,893,915.75 | 9,481,931.55 | |

| P3 | 15,468.02 | 9,172,538.23 | 9,327,216.06 | |

| Board 027 | P1 | 3,211.10 | >3,211,100 | >3,211,100 |

| P2 | 3,302.56 | 1,753,658.83 | 2,103,730.72 | |

| P3 | 17,034.02 | 8,874,724.42 | 9,964,901.7 | |

| Board 036 | P1 | 15,809.88 | >15,809,878 | >15,809,878 |

| P2 | 12,002.04 | 11,389,932.16 | 13,778,341.92 | |

| P3 | 57,506.99 | 5,980,726.91 | 6,670,810.84 | |

| Board 029 | P1 | 12,165.13 | 790,733.19 | 839,393.97 |

| P2 | 19,595.604 | - | 1,018,971.41 | |

| P3 | 30,166.33 | - | 1,508,316.6 | |

| Board 025 | P1 | 9,791.60 | 802,910.79 | 851,869.20 |

| P2 | 19,851.16 | - | 535,981.32 | |

| P3 | 37,734.46 | - | 981,095.86 | |

| Board 026 | P1 | 11,109.69 | 2,477,460.87 | 2,621,886.84 |

| P2 | 12,666.32 | 987,973.04 | 1,139,968.80 | |

| P3 | 26,875.75 | - | 1,263,160.06 | |

| Board 028 | P1 | 12,280.05 | 1,338,525.45 | 1,657,806.75 |

| P2 | 12,808.31 | - | 935,006.92 | |

| P3 | 31,562.56 | 8,874,724.42 | 1,230,939.80 | |

| Board 030 | P1 | 14,824.91 | - | 281,673.25 |

| P2 | 15,316.96 | - | 275,705.35 | |

| P3 | 28,149.61 | - | 478,543.40 | |

| Board 033 | P1 | 26,644.40 | 3,543,704.54 | 3,943,371.2 |

| P2 | 15,458.96 | - | 2,195,171.68 | |

| P3 | 36,888.81 | - | 2,471,550.50 |

| B Test Conditions | H Test Conditions | G Test Conditions |

|---|---|---|

| 1239 | 74 | 102 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shao, J.; Zhang, H.; Chen, B. Experimental Study on the Reliability of PBGA Electronic Packaging under Shock Loading. Electronics 2019, 8, 279. https://doi.org/10.3390/electronics8030279

Shao J, Zhang H, Chen B. Experimental Study on the Reliability of PBGA Electronic Packaging under Shock Loading. Electronics. 2019; 8(3):279. https://doi.org/10.3390/electronics8030279

Chicago/Turabian StyleShao, Jiang, Hongjian Zhang, and Bo Chen. 2019. "Experimental Study on the Reliability of PBGA Electronic Packaging under Shock Loading" Electronics 8, no. 3: 279. https://doi.org/10.3390/electronics8030279

APA StyleShao, J., Zhang, H., & Chen, B. (2019). Experimental Study on the Reliability of PBGA Electronic Packaging under Shock Loading. Electronics, 8(3), 279. https://doi.org/10.3390/electronics8030279