Standalone Operation of Modified Seven-Level Packed U-Cell (MPUC) Single-Phase Inverter

Abstract

:1. Introduction

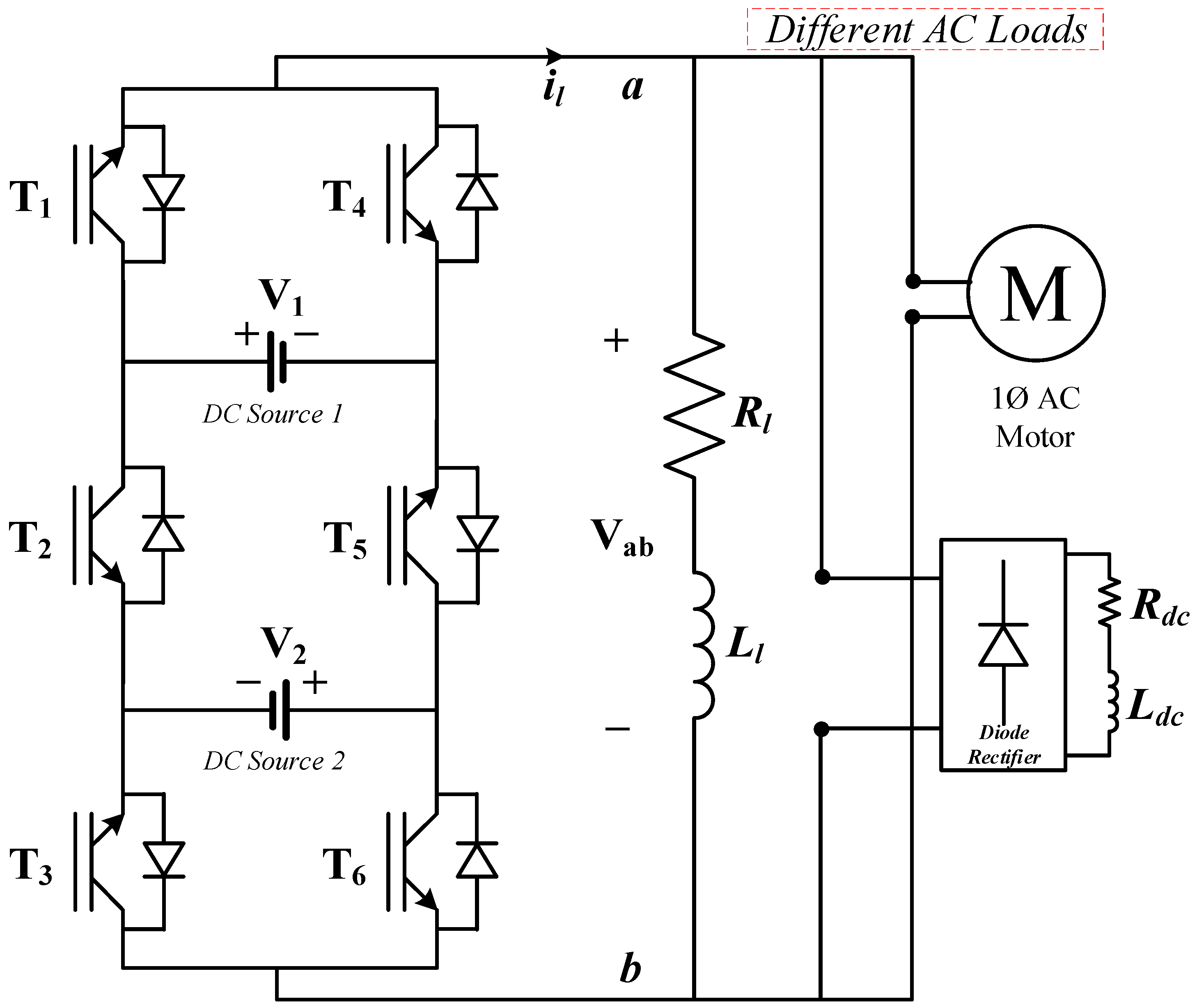

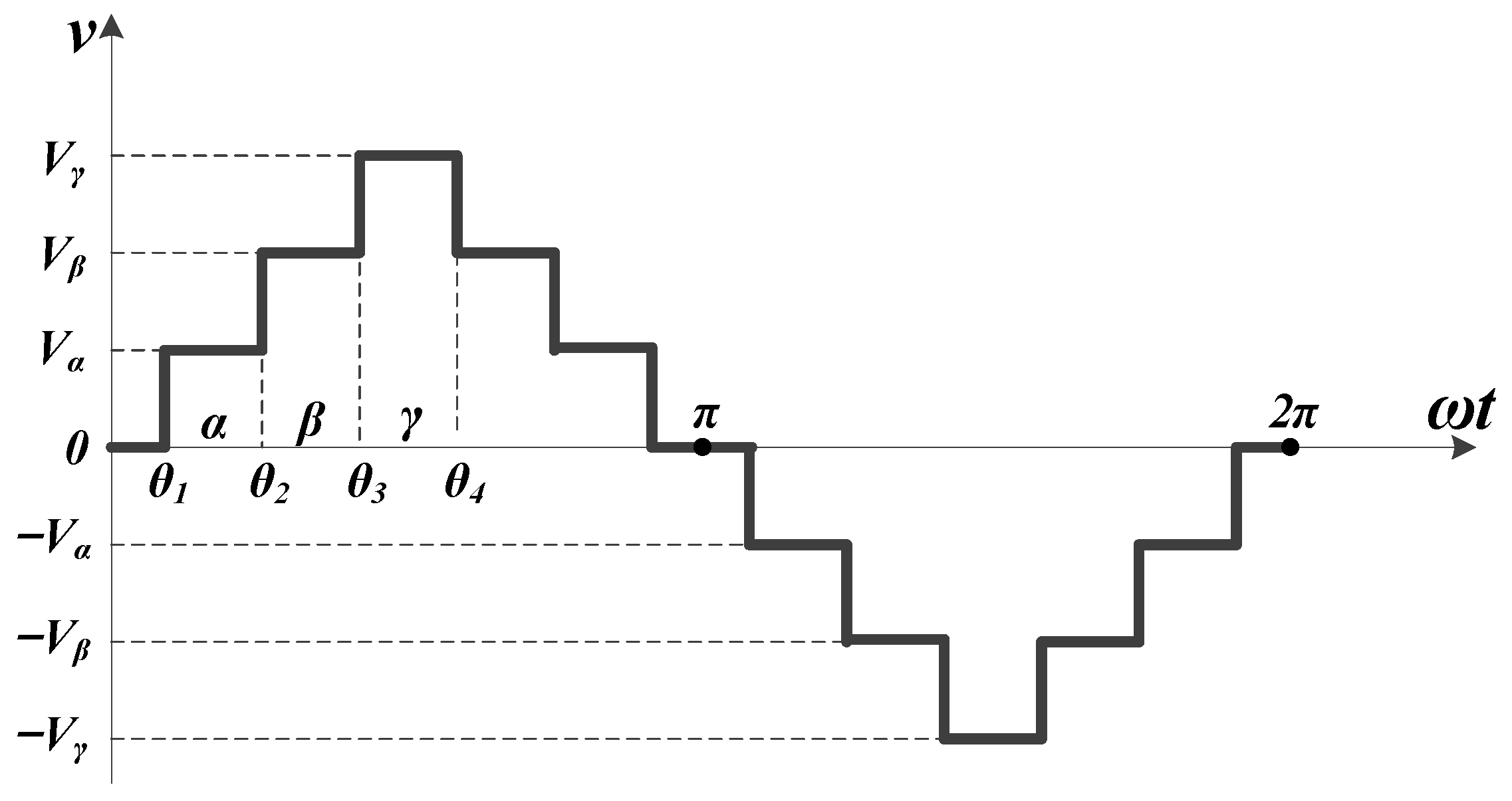

2. Seven-Level Modified Pack U-Cell Inverter

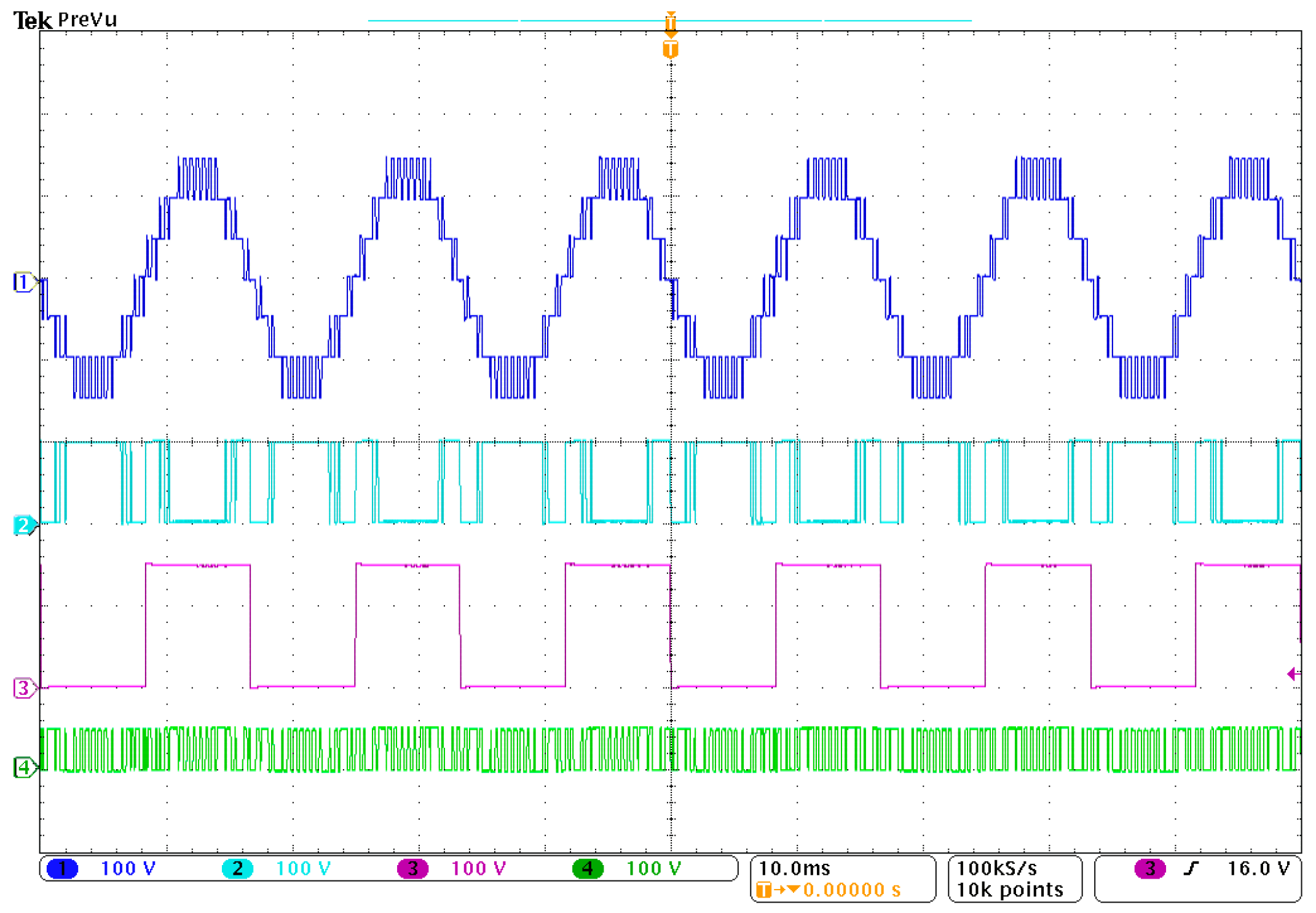

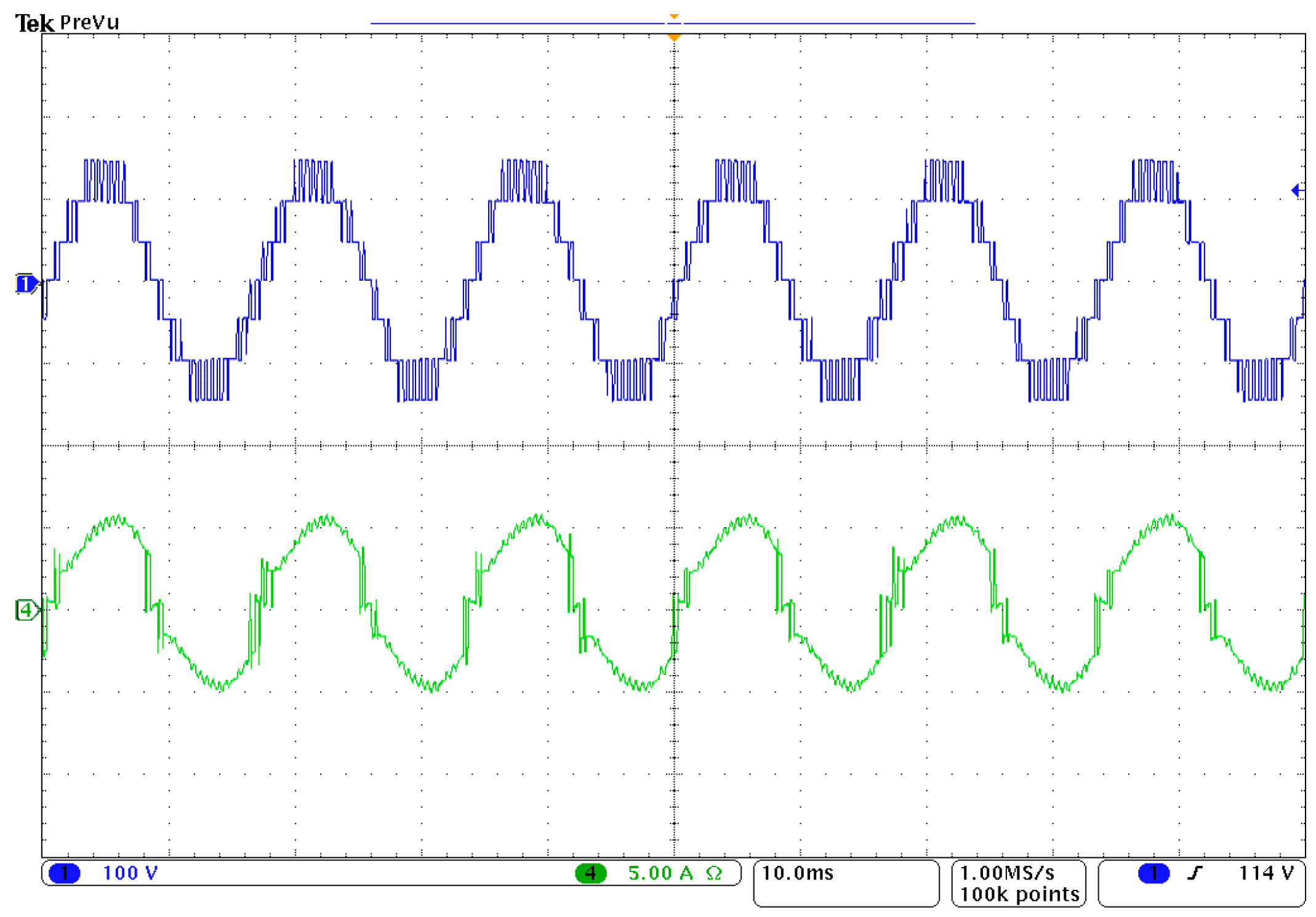

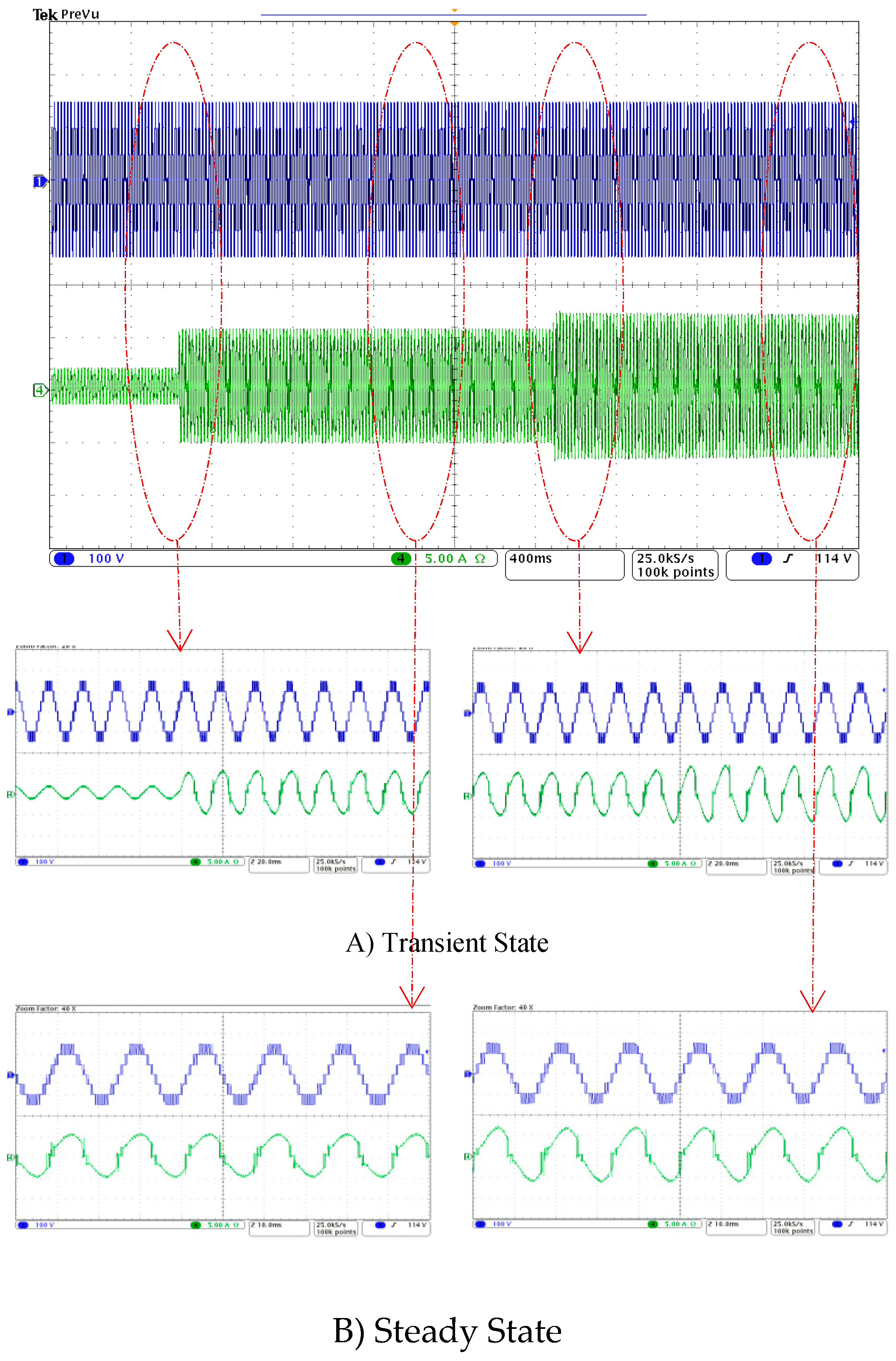

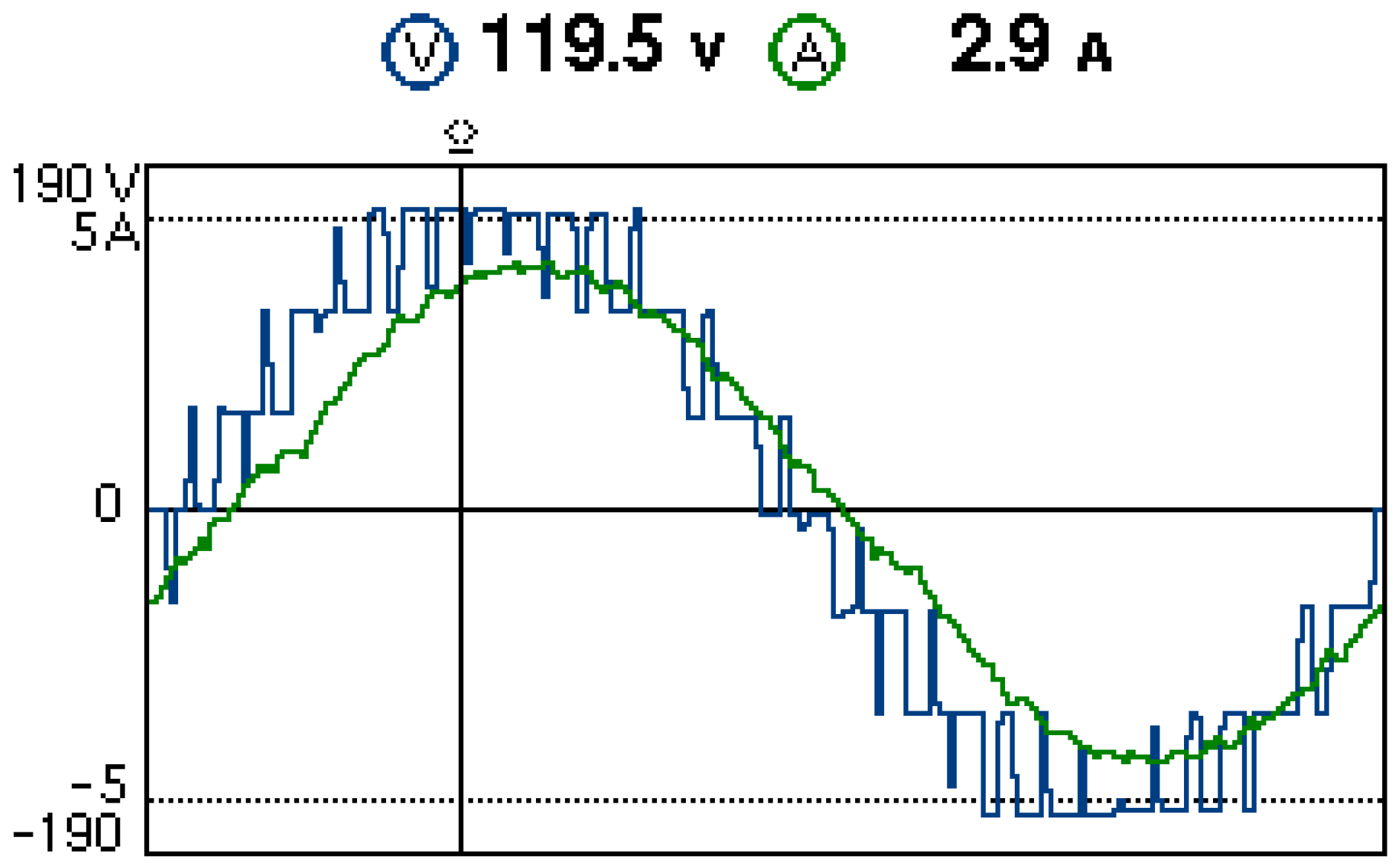

3. Design Consideration for Standalone Applications

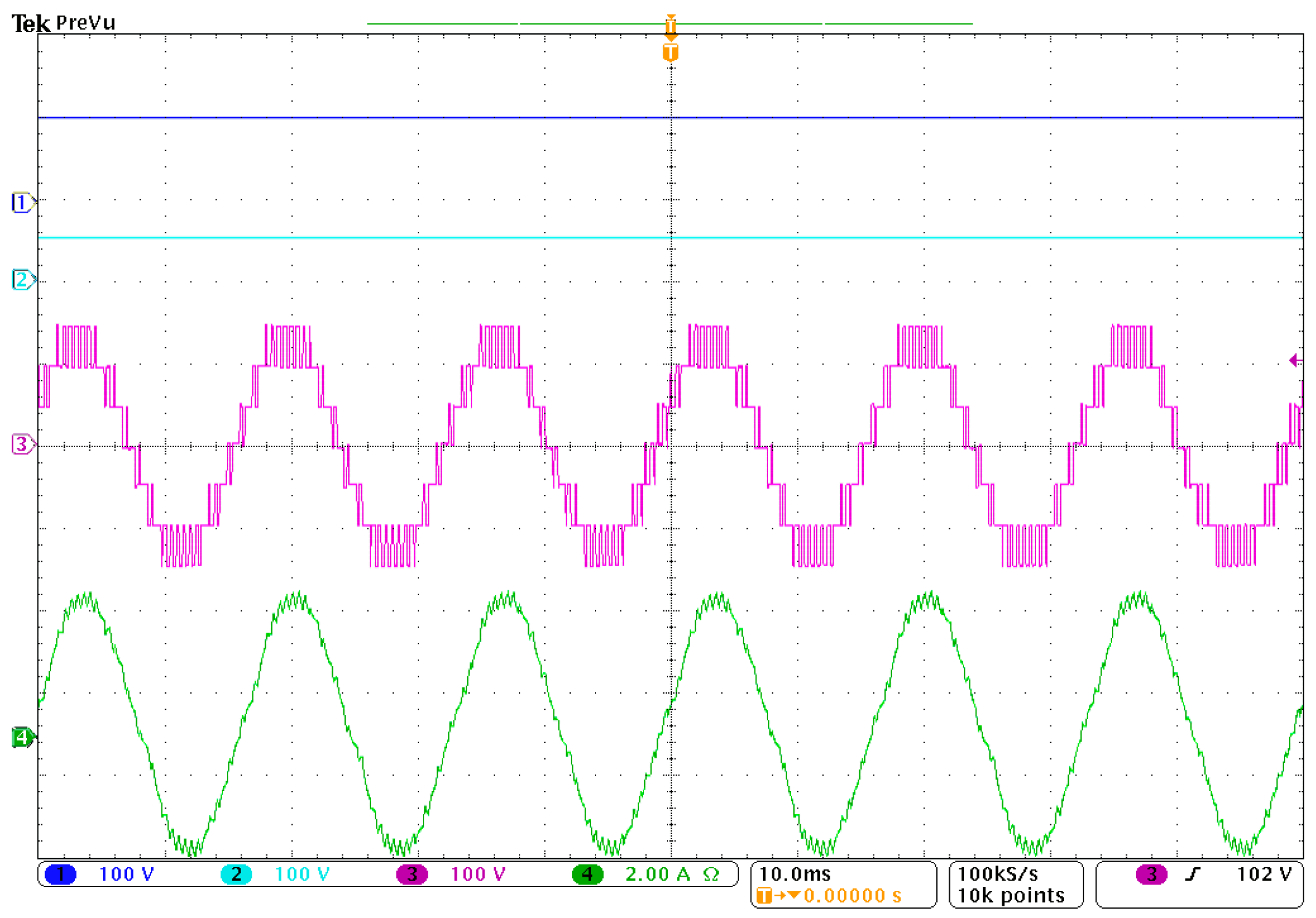

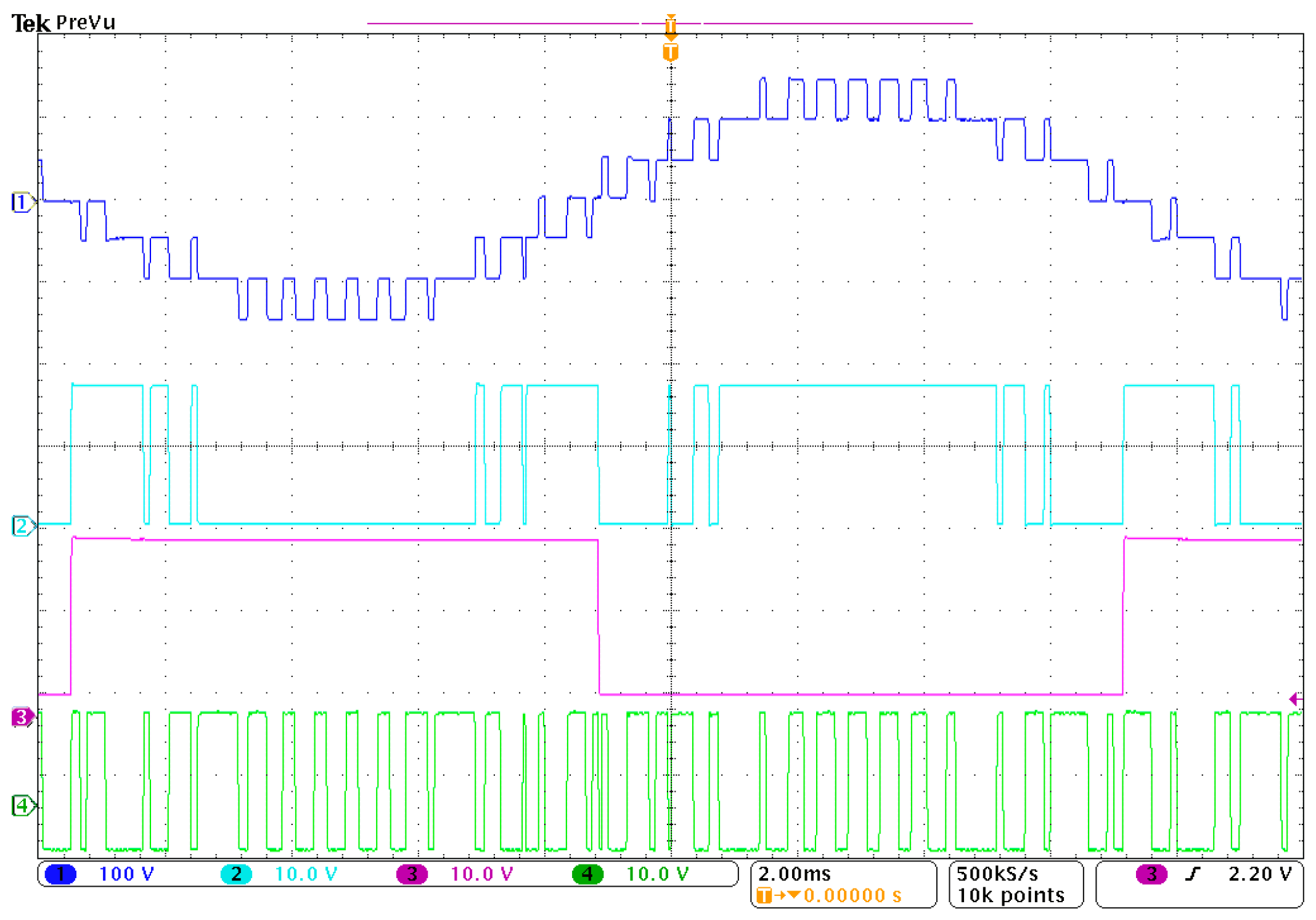

4. Experimental Results and Discussion

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Bose, B.K. Multi-Level Converters; Multidisciplinary Digital Publishing Institute: Basel, Switzerland, 2015. [Google Scholar]

- Mobarrez, M.; Bhattacharya, S.; Fregosi, D. Implementation of distributed power balancing strategy with a layer of supervision in a low-voltage DC microgrid. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 1248–1254. [Google Scholar]

- Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.A.M. The age of multilevel converters arrives. IEEE Ind. Electron. Mag. 2008, 2, 28–39. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point-clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, 5, 518–523. [Google Scholar] [CrossRef]

- Samadaei, E.; Gholamian, S.A.; Sheikholeslami, A.; Adabi, J. An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters with Reduced Components. IEEE Trans. Ind. Electron. 2016, 63, 7148–7156. [Google Scholar] [CrossRef]

- Babaei, E.; Gowgani, S.S. Hybrid multilevel inverter using switched capacitor units. IEEE Trans. Ind. Electron. 2014, 61, 4614–4621. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K.; Ounejjar, Y.; Addoweesh, K. Crossover Switches Cell (CSC): A New Multilevel Inverter Topology with Maximum Voltage Levels and Minimum DC Sources. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013. [Google Scholar]

- Schweizer, M.; Kolar, J.W. Design and implementation of a highly efficient three-level T-type converter for low-voltage applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Escalante, F.M.; Vannier, J.C.; Arzandé, A. Flying capacitor multilevel inverters and DTC motor drive applications. IEEE Trans. Ind. Electron. 2002, 49, 809–815. [Google Scholar] [CrossRef]

- Trabelsi, M.; Bayhan, S.; Metry, M.; Abu-Rub, H.; Ben-Brahim, L.; Balog, R. An effective Model Predictive Control for grid connected Packed U Cells multilevel inverter. In Proceedings of the 2016 IEEE Power and Energy Conference at Illinois (PECI), Urbana, IL, USA, 19–20 February 2016. [Google Scholar]

- Zhang, C.; Geng, H.; Li, S.; Yang, G.; Dong, L. Hybrid Communication Topology and Protocol for Distributed-Controlled Cascaded H-Bridge Multilevel STATCOM. IEEE Trans. Ind. Appl. 2017, 53, 576–584. [Google Scholar]

- Gowaid, I.A.; Adam, G.P.; Massoud, A.M.; Ahmed, S.; Williams, B.W. Hybrid and Modular Multilevel Converter Designs for Isolated HVDC-DC Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 188–202. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K. PUC5 Inverter—A Promising Topology for Single-Phase and Three-Phase Applications. In Proceedings of the IECON 2016-42nd Annual Conference of the IEEE Industrial Electronics Society, Florence, Italy, 23–26 October 2016. [Google Scholar]

- Vahedi, H.; Kanaan, H.Y.; Al-Haddad, K. PUC converter review: Topology, control and applications. In Proceedings of the IECON 2015-41st Annual Conference of the IEEE Industrial Electronics Society, Yokohama, Japan, 9–12 November 2015; pp. 4334–4339. [Google Scholar]

- Kumar, P.R.; Kaarthik, R.S.; Gopakumar, K.; Leon, J.I.; Franquelo, L.G. Seventeen-level inverter formed by cascading flying capacitor and floating capacitor H-bridges. IEEE Trans. Power Electron. 2015, 30, 3471–3478. [Google Scholar] [CrossRef]

- Kumar, R.; Singh, B. Single Stage Solar PV Fed Brushless DC Motor Driven Water Pump. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1377–1385. [Google Scholar] [CrossRef]

- Vahedi, H.; Labbe, P.; Al-Haddad, K. Sensor-Less Five-Level Packed U-Cell (PUC5) Inverter Operating in Stand-Alone and Grid-Connected Modes. IEEE Trans. Ind. Informat. 2016, 12, 361–370. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K. Method and System for Operating a Multilevel Inverter. U.S. Patent US9923484B2, 20 March 2018. [Google Scholar]

- Sulake, N.; Devarasetty Venkata, A.; Choppavarapu, S. FPGA Implementation of a Three-Level Boost Converter-fed Seven-Level DC-Link Cascade H-Bridge inverter for Photovoltaic Applications. Electronics 2018, 7, 282. [Google Scholar] [CrossRef]

- Kang, J.-W.; Hyun, S.-W.; Ha, J.-O.; Won, C.-Y. Improved Neutral-Point Voltage-Shifting Strategy for Power Balancing in Cascaded NPC/H-Bridge Inverter. Electronics 2018, 7, 167. [Google Scholar] [CrossRef]

- Lee, S.; Kim, J. Optimized Modeling and Control Strategy of the Single-Phase Photovoltaic Grid-Connected Cascaded H-bridge Multilevel Inverter. Electronics 2018, 7, 207. [Google Scholar] [CrossRef]

- Vahedi, H.; Sharifzadeh, M.; Al-Haddad, K. Modified Seven-Level Pack U-Cell Inverter for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1508–1516. [Google Scholar] [CrossRef]

- Vahedi, H.; Al-Haddad, K. Real-Time Implementation of a Seven-Level Packed U-Cell Inverter with a Low-Switching-Frequency Voltage Regulator. IEEE Trans. Power Electron. 2016, 31, 5967–5973. [Google Scholar] [CrossRef]

- Wu, B. High-Power Converters and AC Drives; Wiley-IEEE Press: Hoboken, NJ, USA, 2006. [Google Scholar]

| Switching State | T1 | T2 | T3 | T4 | T5 | T6 | Vab |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 1 | 0 | 1 | 0 | V1 + V2 |

| 2 | 1 | 0 | 0 | 0 | 1 | 1 | V1 |

| 3 | 0 | 0 | 1 | 1 | 1 | 0 | V2 |

| 4 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

| 5 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 6 | 1 | 1 | 0 | 0 | 0 | 1 | −V2 |

| 7 | 0 | 1 | 1 | 1 | 0 | 0 | −V1 |

| 8 | 0 | 1 | 0 | 1 | 0 | 1 | V2 + V1 |

| First DC bus voltage (V1) | 100 V |

| Second DC bus voltage (V2) | 50 V |

| Load Voltage Frequency (fgrid) | 60 Hz |

| Switching Frequency (fPWM) | 2 KHz |

| AC Load Resistor (Rl) | 40 Ω |

| AC Load Inductor (Ll) | 20 mH |

| Rectifier Side Resistor (Rdc) | 20 Ω |

| Rectifier Side Inductor (Ldc) | 60 mH |

| Single-Phase AC Universal Motor | 120 V, 3 A |

| T1 & T4 | 600 Hz |

| T2 & T5 | 60 Hz |

| T3 & T6 | 1920 Hz |

| Topologies | Active Switches | DC Sources |

|---|---|---|

| seven-level CHB with Equal DC Sources | 12 | 3 |

| seven-level CHB with Unequal DC Sources | 8 | 2 |

| seven-level MPUC | 6 | 2 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shojaei, A.A.; Najafi, B.; Vahedi, H. Standalone Operation of Modified Seven-Level Packed U-Cell (MPUC) Single-Phase Inverter. Electronics 2019, 8, 268. https://doi.org/10.3390/electronics8030268

Shojaei AA, Najafi B, Vahedi H. Standalone Operation of Modified Seven-Level Packed U-Cell (MPUC) Single-Phase Inverter. Electronics. 2019; 8(3):268. https://doi.org/10.3390/electronics8030268

Chicago/Turabian StyleShojaei, Ali Asghar, Bahram Najafi, and Hani Vahedi. 2019. "Standalone Operation of Modified Seven-Level Packed U-Cell (MPUC) Single-Phase Inverter" Electronics 8, no. 3: 268. https://doi.org/10.3390/electronics8030268

APA StyleShojaei, A. A., Najafi, B., & Vahedi, H. (2019). Standalone Operation of Modified Seven-Level Packed U-Cell (MPUC) Single-Phase Inverter. Electronics, 8(3), 268. https://doi.org/10.3390/electronics8030268