1. Introduction

The greenhouse effect, resulting in climate change, has become a major problem, and ecofriendly technologies for producing clean energy are paramount to alleviating greenhouse gas emissions. Commonly-used rechargeable batteries including lead-acid, Ni-Cd, Ni-MH, and Li-ion batteries have been applied in smartphones, laptops, electric screwdrivers, and other portable instruments as well as in electric forklifts and other electric vehicles. Compared with other secondary batteries, Li-ion batteries have the highest power and energy density [

1]; therefore, Li-ion cells inside a battery pack are a suitable choice for electric vehicles [

1,

2,

3].

The Lithium iron phosphate (LiFePO

4) is suitable for the positive electrode material in batteries because the strong P–O covalent bonds in the LiFePO

4 lattices do not decompose easily. The LiFePO

4 battery possesses excellent thermal stability; even under high-temperature or overcharge conditions, they rarely overheat because the LiFePO

4 lattice does not easily collapse and oxidize. Moreover, LiFePO

4 batteries are suitable for powering electric vehicles because they offer multicycle charge/discharge and nontoxicity [

4,

5,

6]. However, the energy density of LiFePO

4 battery is lower than LiMn

2O

4 and LiCoO

2 batteries.

The constant-voltage (CV) and constant-current (CC) outputs of rapid chargers are necessary functions for the charge of large-capacity LiFePO

4 battery pack (LBP). To accomplish CV and CC charges, the voltage feedback controller (VFC) and current feedback controller (CFC) must be designed based on the frequency responses of charge loops. The battery electrical model is a critical role because a suitable model can present a practical frequency response. The suitable electrical model for a Li-ion battery include the R

int model, the resistance–capacitance (RC) model, the Thevenin model, the modified Thevenin model, and the Partnership for a New Generation of Vehicles (PNGV) battery model [

7,

8,

9]. The PNGV battery model [

10,

11,

12] was adopted in this study because its parameters can be estimated using the pulse-current charge method to obtain the battery voltage–time characteristic, and the formula for the electric charge can be adopted to calculate the model parameter [

10].

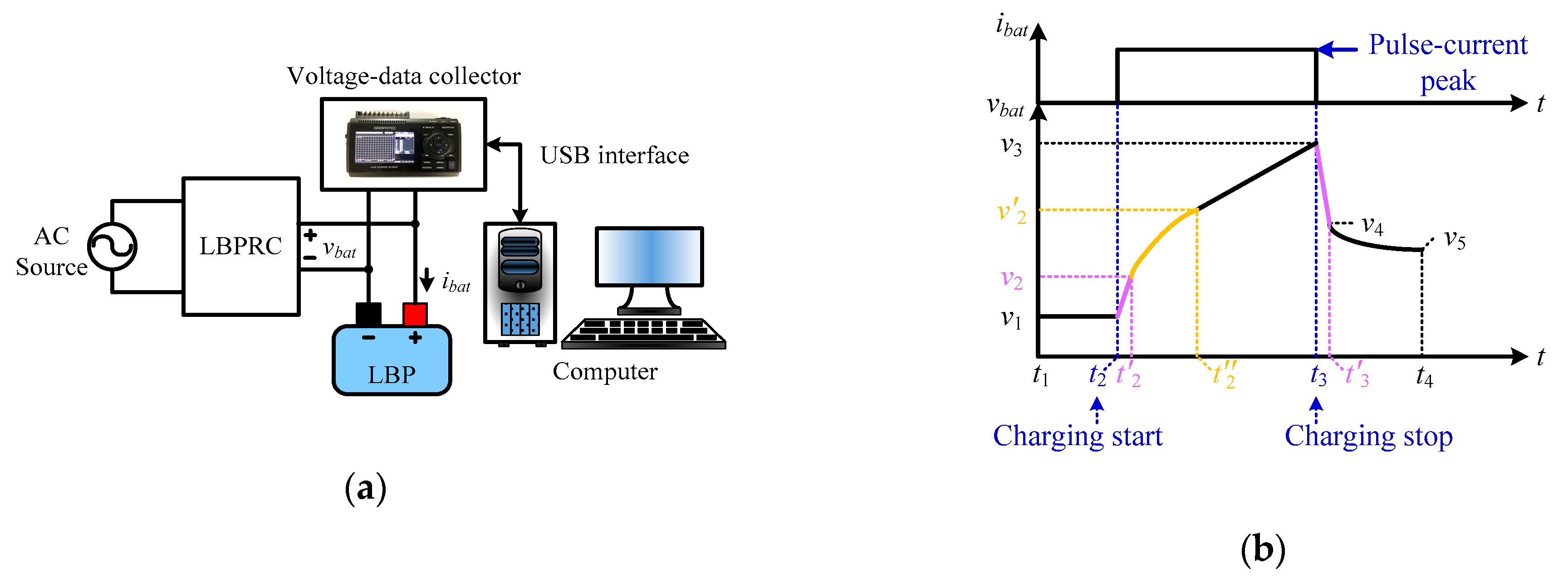

In this study, the developed LBP rapid charger (LBPRC) comprised a safety-standard circuit, a power factor corrector, and a DC–DC converter. The topology of the DC–DC converter was a phase-shifted full-bridge with parallel current-doubler rectification (PSFB-PCDR) incorporating the VFC and CFC to achieve the CV or CC output mode. In addition, a three-terminal switch (TTS) model was applied to simplify the PSFB-PCDR [

13,

14,

15]. Moreover, studies [

16,

17,

18,

19] have mentioned several charge strategies for rechargeable batteries. In [

16], the power stage topology of the battery charger was a boost converter, which could step up the low input voltage from the photovoltaic cell, and using the control technologies of the maximum power point tracking and the pulse-charge scheme, the fast maximum power point tracking could be achieved during a narrow charge period. In [

17], the battery charge combined the bridgeless power factor correction (PFC) with the PSFB converter; this power topology design could easily achieve the series or parallel combination of battery charger for electric vehicle applications. Moreover, the CC–CC–CV charge strategy was applied; this charge method should be effective to extend the LiFePO

4 battery lifespan. In [

18], a two-switch buck converter was used as the power stage topology, which could be applied in an electrically controlled pneumatic brake system; the CC–CV charge strategy was implemented to charge the LiFePO

4 battery. In [

19], the series resonant converter with the synchronous rectification was the power stage topology of battery charger; the charge strategy adopted the CC–CV method. From [

16,

17,

18,

19], comparisons of power converter topologies and charge strategies are listed in

Table 1.

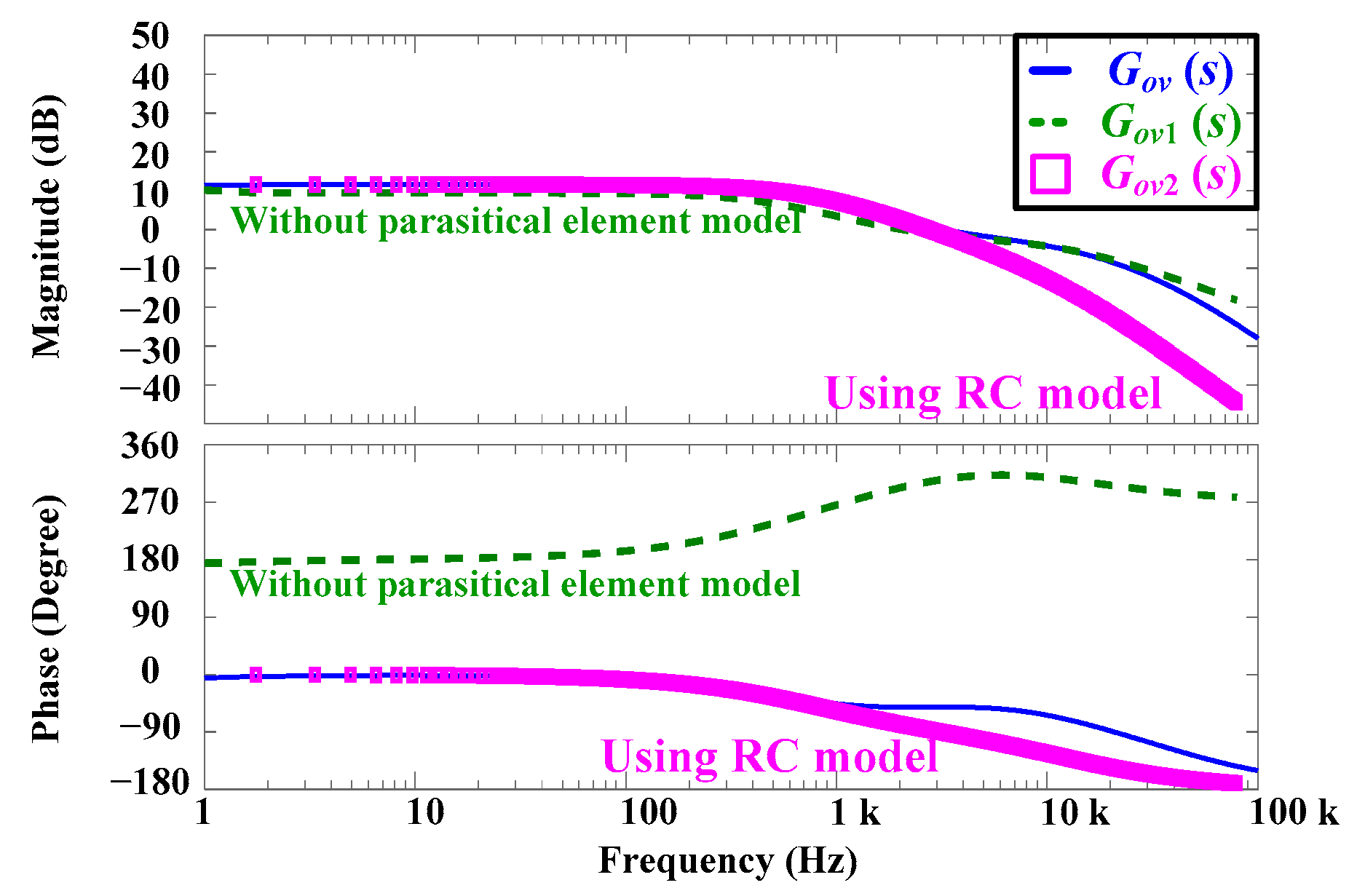

Some previous studies [

20,

21,

22] adopted the simple R

int model or the RC battery model to establish the system small-signal model; however, this simple, one-order battery model cannot reflect the practical frequency response and the break frequency, and therefore, the pole-zero compensation and the dynamic characteristic improvement could not be performed precisely. In this study, the high-order transfer function (TF) was established to ameliorate the deficiencies of the previous studies [

20,

21,

22], and the scheme of current overshoot mitigation using a new proportional shifting proportional-integral (PSPI) control can be achieved.

Table 2 presents a comparison of the developed method in the present study with other charger technologies and control methods.

This paper is divided into seven sections.

Section 2 discusses the PNGV battery model with parameter estimation. In

Section 3, the PSFB-PCDR employs the TTS model incorporating PNGV battery model to establish the system matrix. Frequency response simulations are provided in

Section 4. The CV and CC feedback controllers designed on the basis of these simulations are presented in

Section 5, and measurements and experimental results are presented in

Section 6. The concluding remarks and primary contributions of this study are given in

Section 7.

3. Small-Signal System Matrix

Figure 4a depicts the PSFB-PCDR circuit, including the DC input source

Vinps, power switches

Qa to

Qd, a blocking capacitance

Cb, a transformer

T1, rectification diodes

Df1 to

Df4, current-doubler inductances “

Lcdr1 to

Lcdr4”, and an output capacitance

Co. The positive and negative electrodes of the LBP are respectively connected to the PSFB-PCDR outlets

o1 and

o2.

Figure 4b presents the operating timing diagram of PSFB-PCDR that includes the driving signals

va to

vd for

Qa to

Qd and the primary-side voltage

vtp across

T1; the

Tsw is the operating switching period for

va to

vd; the

dy represents the PSFB-PCDR operating duty cycle ratio.

In

Figure 4, the TTS model can replace the circuit inside the a-frame, as illustrated in

Figure 5a. This model has a dependent voltage source

vr, two current sources (

ir1 and

ir2), and a resistance

Reqs. The

Vinps can be reflected to the

T1 secondary side becoming

vr, as follows:

where

n is the

T1 turns ratio, it equals to the formula

Np/

Ns1 =

Np/

Ns2.

The rising and falling slopes of the

T1 input current indicate that they are affected by the PSFB-PCDR operating switching frequency

fsw and transformer leakage inductance

Lk. According to the method from the [

15], using an equivalent resistance

Reqs can model the slope change. Therefore, the

Reqs is given by

Because of fsw, Lk and n are fixative values in the design, and the derivation of the system transfer function will focus on the LPBRC output voltage and current to the operating duty cycle; therefore, using (7) to represent the dynamic influence of Lk can be acceptable.

The PSFB-PCDR secondary-side operations can be regarded as the buck converter, and the

Lcdr1 to

Lcdr4 have the same inductance value; therefore, the four inductances can be treated as parallel connections, and they can be expressed as an inductance

Lcdr. As a result, the output inductance

Lo equals to

Lcdr/4 [

13,

14,

26]. Moreover, the

Co contains an equivalent series resistance

Resr.

A CV or CC power replenishes the LBP by way of the power cable; the wire resistance-inductance would influence the gain and phase of the system frequency response. Therefore, the model considers the wire resistance

Rc and inductance

Lc, which lie between the PSFB-PCDR outlet and LBP. The illustration in

Figure 5b is an equivalent circuit.

In

Figure 5b, the

Rc connects with the

Roir in series; hence,

Rc +

Roir equal to

Rx. The final equivalent circuit, depicted in

Figure 5c, is in accordance with these conditions. Using Kirchhoff’s voltage and current laws and the mesh-current method, the loop equations can be obtained as follows:

The LBPRC voltage can be expressed as:

Substitution of (6) and

vLo =

Lo(

dip/

dt) in (8),

vLc =

Lc(

dibat/

dt) in (9), and

iCt =

Ct(

dvct/

dt) in (11), the state-space representations can be expressed as follows:

The state-space variables can accede to a DC value plus a small-signal perturbation; therefore, substitution of

ip =

Ip +

,

ibat =

Ibat +

,

vCo =

VCo +

,

vCt =

VCt +

, and

vCx =

VCx +

into (13)–(17) can yield the small-signal system matrix of PSFB-PCDR as follows:

where

x’

1=

/

dt,

x’

2 =

/

dt,

x’

3 =

/

dt,

x’

4 =

/

dt, and

x’

5 =

/

dt. The calculations for the elements in matrices

A,

B,

C, and

E are listed in

Table 6.

6. Experimental Results

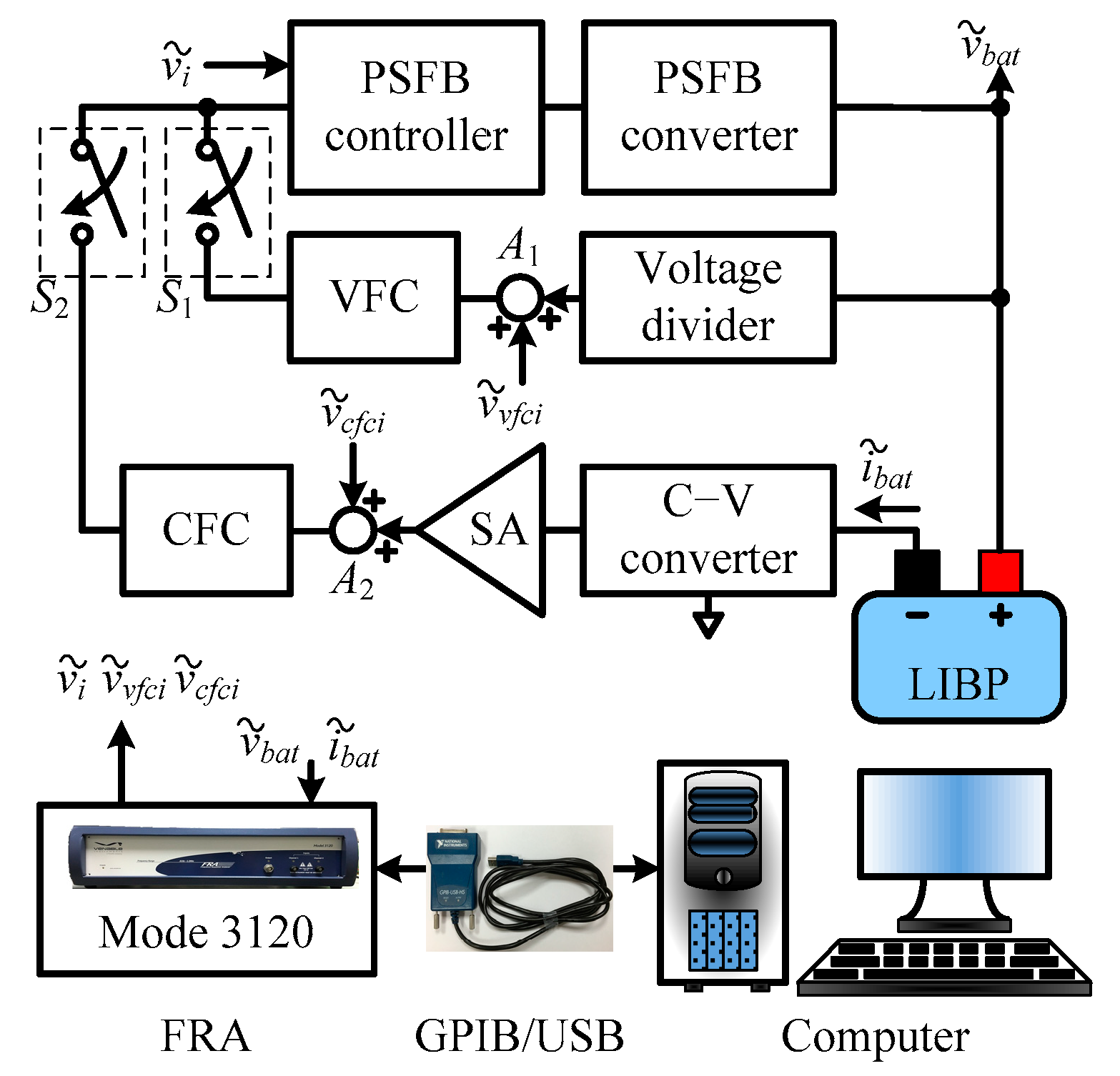

The measurement system of frequency response for the LBPRC is depicted in

Figure 20. This system comprised a computer, a USB/GPIB interface (National Instruments Inc., Austin, TX, USA), and a frequency response analyzer (FRA) MODEL3120 (Veneable Corp., Austin, TX, USA). The FRA setting parameter and data can be controlled and transmitted through the USB/GPIB interface. Therefore, the fluctuant small signals

,

, and

generating by the FRA can be respectively output to the PSFB controller and adders (

A1 and

A2). Subsequently, the fluctuant charge voltage

and current

can be recorded and transmitted to the FRA. Finally, the Bode plot is presented on the computer monitor.

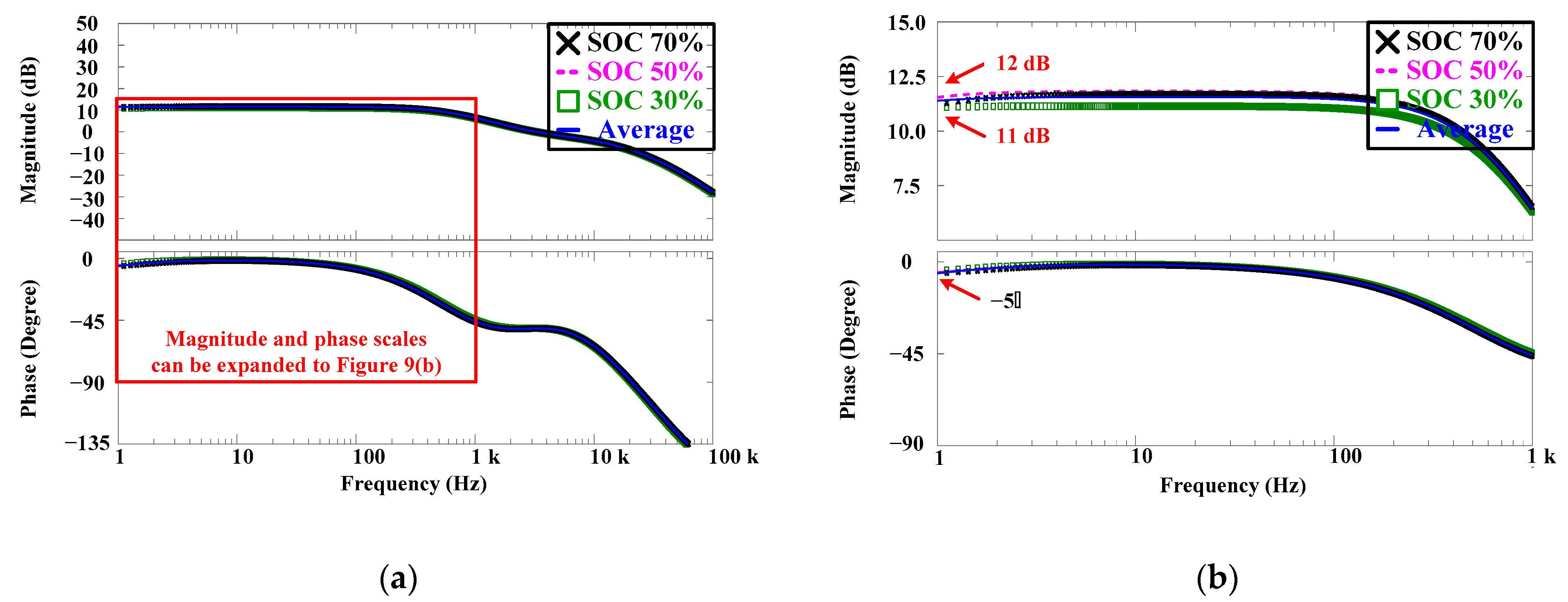

Frequency response measurement of open-loop charge voltage: As indicated in

Figure 20, when both

S1 and

S2 were turned off, the FRA output was

; the fluctuant

could then be measured and input to the FRA. The Bode plot of

Gov was displayed in

Figure 21a. The low-frequency gain was 10 dB (simulation: 11.4 dB), and the bandwidth was 250 Hz (simulation: 237 Hz). At gain of 0 dB, the frequency and phase were 1.6 kHz (simulation: 1.7 kHz) and −58° (simulation: −49.9°), respectively. Moreover, for the break frequencies, the

fopc1 = 100 Hz had a pole (simulation: 98.04 Hz), the

fozc1 = 1.5 kHz had a zero (simulation: 1.05 Hz), and the

fopc2 = 12 kHz had a pole (simulation: 9.8 kHz). The gain and phase slopes in the different bands were listed in

Table 8.

Frequency response measurement of open-loop charge current: As indicated in

Figure 20, when both

S1 and

S2 were turned off, the FRA output was

; the fluctuant

could then be measured and input to FRA. The Bode plot of

Goc was displayed in

Figure 21b. The low-frequency gain was 35 dB (simulation: 35.6 dB), and the bandwidth was 190 Hz (simulation: 200 Hz). At gain of 0 dB, the frequency and phase were 52 kHz (simulation: 50 kHz) and −130° (simulation: −140°), respectively. Moreover, for the break frequencies, the

fopv1 = 100 Hz had a pole (simulation: 98.04 Hz), the

fozv1 = 3.5 kHz had a zero (simulation: 1.05 kHz), and

fopv2 = 15 kHz had a pole (simulation: 9.8 kHz). The gain and phase slopes in the different bands were listed in

Table 8. These measurements demonstrate that the proposed equivalent models are suitable for establishing the small-signal transfer functions of LBPRC.

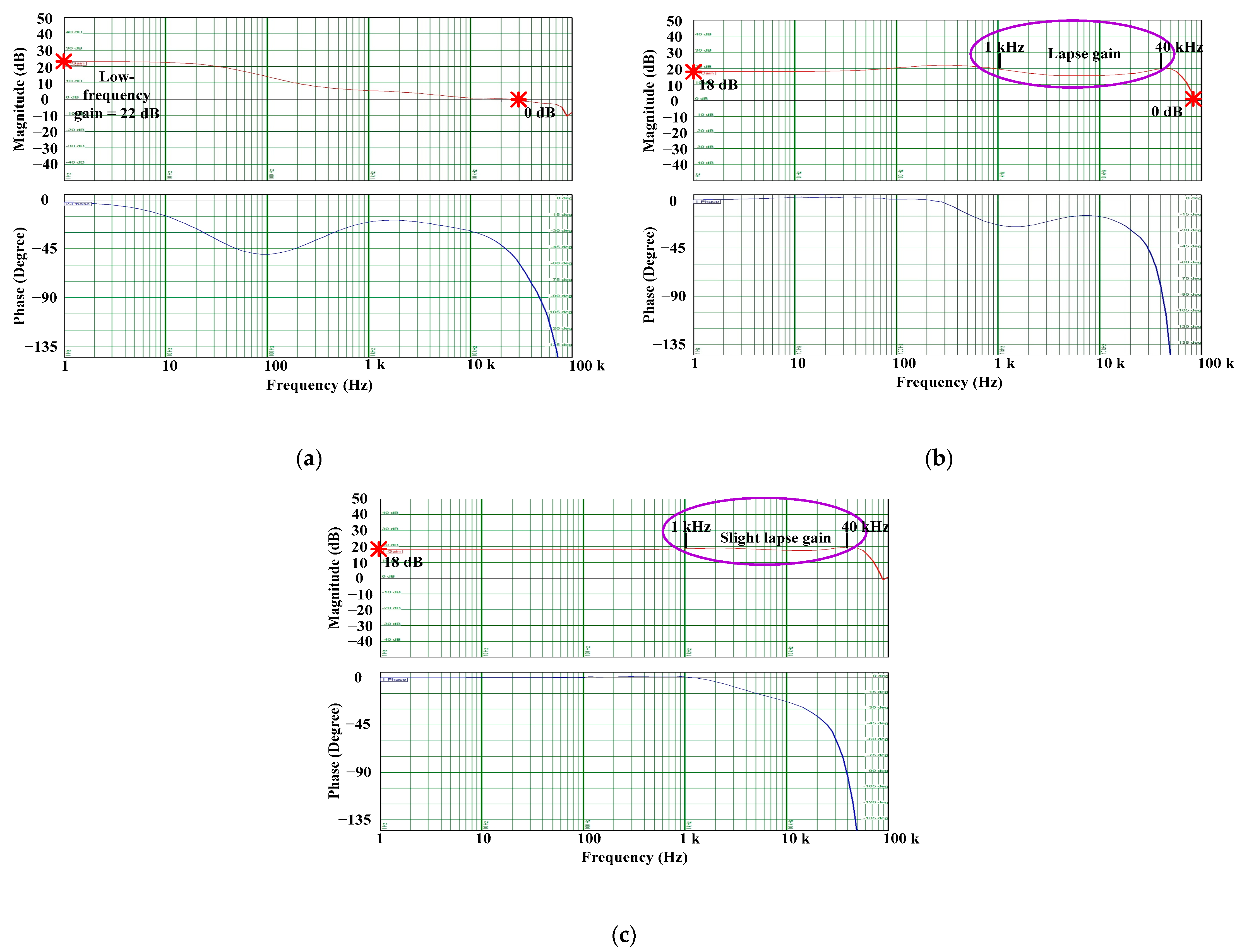

Frequency response measurement of closed-loop charge voltage: As shown in

Figure 20, with the

S1 turned on and the

S2 turned off, the FRA generated

, which was input to

A1, the

could then be measured by the FRA. The Bode plot of

Gfbv is displayed in

Figure 22a. The low-frequency gain was 22 dB (simulation: 22.7 dB). At the gain 0 dB, its frequency was 30 kHz (simulation: 40 kHz).

Frequency response measurement of closed-loop charge current: As shown in

Figure 20, with the

S2 turned on and the

S1 turned off, the FRA produced

, which was input to

A2; the

could then be measured by the FRA, and the Bode plot of

Gfbc was displayed in

Figure 22b. The low-frequency gain was 18 dB (simulation: 18.6 dB). At the gain 0 dB, the frequency was 80 kHz (simulation: 50 kHz). The gain exhibited a lapse from 1 to 40 kHz, which could influence the system response speed. Therefore, the

fzc should be adjusted to 5 kHz to heave a lapse gain; the subsequent Bode plot is displayed in

Figure 22c.

Waveform of start-up current using PI control and ZBFS:

Figure 23,

Figure 24 ,

Figure 25,

Figure 26 and

Figure 27 present the waveforms of the charge voltage

Vbat and current

Ibat during the charge start-up phase. At the charge rate of 0.5 C and SOC level of 30% (

Figure 23a), the LBP started to charge from a

Vbat level of 26.92 V; the target value of average charge current was maintained at 17.5 A (0.5C). During the start-up phase, a large current overshoot occurred because the zero break frequency

fzc was set to 49 Hz. The current overshoot peak was 34 A, which exceeded the operating CC of 16.5 A (i.e., 34 – 17.5). As illustrated in

Figure 23b, the time scale of the waveform window was curtailed to 10 ms/division (ms/div.), and the following several circumstances were observed:

- (1)

A prolonged start-up time of 30 ms was observed before the LBPRC operated in the CC charge mode.

- (2)

A low-frequency current ripple of 60 Hz was observed (

Figure 23); this was because an AC power source served as the input source of the LBPRC, with a power factor correction providing a DC voltage of 400 V mixing the low-frequency ripple to the PSFB-PCDR. However, the low-frequency current ripple did not damage the LBP in the charge state.

- (3)

The average charge current was 17.5 A, and the current overshoot peak was 34 A.

As illustrated in

Figure 23c, when the charge start voltage was 27.05 V (SOC 50%), the start-up time was 34 ms, average charge current was 17.5 A, and current overshoot peak was 29 A. As shown in

Figure 23d, when the charge start voltage was 27.23 V (SOC 70%), the start-up time was 40 ms, average charge current was 17.5 A, and current overshoot peak was 28 A.

However, using the ZBFS method, the

fzc of CFC can be shifted to 5 kHz to accelerate the response speed of the charge current loop, and the waveforms of the charge voltage and current are presented in

Figure 24. In

Figure 24a,b, the time scales of the waveform windows were 100 and 10 ms/div., respectively. The LBP started to charge from a

Vbat level of 26.92 V (SOC 30%); the current overshoot peak could be reduced to 23 A, the start-up time was cut to 12 ms, which was lower than in

Figure 23b. Notably, the current ripple peak and frequency were 1 A and 60 Hz, respectively; the low-frequency ripple was the same as that in

Figure 23b. Hence, applying the proposed ZBFS method to the LBPRC did not influence system stability. As illustrated in

Figure 24c, when the charge start voltage was 27.05 V (SOC 50%), the start-up time was 12 ms, average charge current was 17.5 A, and current overshoot peak was 22 A. As illustrated in

Figure 24d, when the charge start voltage was 27.23 V (SOC 70%), the start-up time was 12 ms, average charge current was 17.5 A, and current overshoot peak was 21 A. Therefore, the

fzc shifting effectively reduces the charge current overshoot, and does not cause system instability.

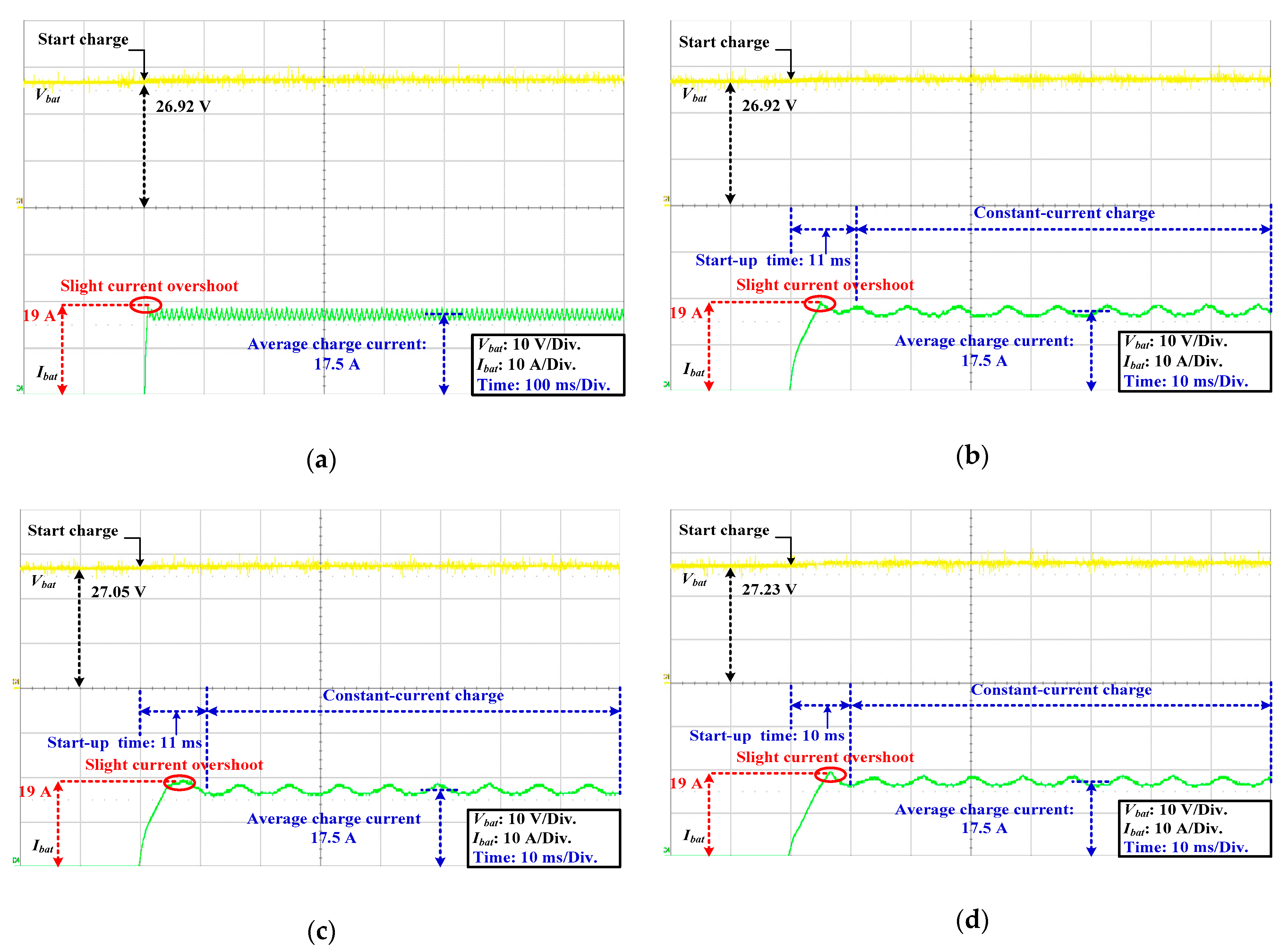

Waveform of current overshoot mitigation using PSPI control: The start-charge voltage and current when the LBPRC incorporates the CFC with the PSPI control are presented in

Figure 25. As illustrated in

Figure 25a,b, the time scale of the waveform window was 100 and 10 ms/div., respectively. The LBP started to charge from a

Vbat level of 26.92 V (SOC 30%), the current overshoot peak was reduced to 19 A, and the start-up time was cut to 11 ms; they were lower than those in

Figure 23 and

Figure 24. As illustrated in

Figure 25c, when the charge start voltage was 27.05 V (SOC 50%), the start-up time was 11 ms, average charge current was 17.5 A, and current overshoot peak was 19 A. As illustrated in

Figure 25d, when the charge start voltage was 27.23 V (SOC 70%), the start-up time was 10 ms, average charge current was 17.5 A, and current overshoot peak was 19 A. Compared with the PI control, ZBFS method, and PSPI control, the control method incorporating the PSPI control technology into the CFC was determined to be more effective since the current overshoot peak could be reduced to 19 A, thereby approximating the average charge current of 17.5 A; moreover, the start-up time could be curtailed to 10 ms.

Waveform of 1C charge using PSPI control: At the charge rate of 1C (CC of 35 A) in

Figure 26a,b, the time scales of the waveform windows were 100 and 10 ms/div., respectively. The charge start voltage was the minimum cut-off voltage 22 V, no current overshoot was observed, and the average charge current was the CC 35 A; therefore, the proposed PSPI control was also effective for the charge rate of 1C.

CV and CC charge profiles:

Figure 27 presents the LBP charge profile using the developed LBPRC.

Figure 27a presented the CC–CV charge strategy; during the CC 35 A charge, the battery voltage increased gradually from 22 to 27.2 V; then, LBPRC took over as the CV output mode to charge the LBP, and the charge current gradually decreased. This experiment demonstrated that LBPRC could implement the CV charge when the LBP SOC was increased from low (20%) to high.

In

Figure 27b, the single CC 35 A charges the LBP, hence the LBP voltage increased gradually from 22 to 29.2 V; the total charge time was about 52 min. This experiment demonstrated that the LBP could be charged from a low SOC of 20% to a high LBP of 83% (LBP voltage is 29.2 V) using the CC charge strategy. Both experiments confirmed that the LBPRC design was implemented using the VFC and CFC, both CV and CC charge functions could replenish the LBP. According to

Figure 27b, the maximum output power of the LBPRC was 1022 W (i.e., 29.2 V × 35 A) and the charge current was 35 A (1C); therefore, the LBPRC rapid charge could be achieved for the LBP.

Moreover, the power rating of LBPRC was approximately 1 kW, and its charge current at the 1C rate was 35 A. Thus, the proposed PSFB-PCDR topology has several benefits for LBPRC applications, including zero-voltage switching, high conversion efficiency, and low-frequency current ripple reduction. The PSFB-PCDR is a commonly used topology for high-power DC–DC converter applications; the circuit component cost can be reduced in mass production to make it cost-effective.

LBPRC conversion efficiency: In this study, the power stage of the LBPRC was composed of a PFC and a PSFB-PCDR. To measure the LBPRC conversion efficiency, the LBPRC inlet inputted a single-phase AC power source, whose output voltage and frequency were 230 V

rms and 60 Hz, respectively.

Figure 28 reports the LBPRC conversion efficiencies with different loads; the maximum efficiency was 88.8% when the output power was at 525 W; the minimum efficiency was 86.1% at 315 W. When the LBPRC operated at the maximum output power of 1050 W, the conversion efficiency was 86.7%.

In

Figure 8, the maximum efficiency of the LBPRC, 88.8%, was obtained when PFC and PSFB-PCDR efficiencies were 95% and 93%, respectively. Therefore, the maximum LBPRC efficiency could be calculated as 88.8% (95% × 93% = 88%). Under this operating condition, power switches (

Qa to

Qd) were operated in zero-voltage switching, hence the single-stage PSFB-PCDR efficiency can reach 93%; however, because of the PSFB-PCDR secondary side used diode rectification, power losses of the diodes were high. The synchronous rectification can replace the diode rectification to promote LBPRC conversion efficiency.

Comparison of performance index:

Figure 29 illustrates five performance indexes for three CFC control methods. The PSPI control method achieved excellent performance indices, including the start-up current overshoot reducing, a short setting time, the small steady-state errors, a short rising time, and a short start-up time. For the ZBFS control method, four performance indices were between those observed for the PSPI and PI control methods. Finally, the PI control method integrated with the CFC was the poorest combination because four performance indices were extremely poor. Moreover, because the three control methods can implement the PI control during the steady-state operation, they have small steady-state errors.

LBPRC prototype:

Figure 30 is a photo of the practical charge system. The input power of the LBPRC prototype comes from the AC source, and its output side connects to the LBP. To analyze the frequency response, the FRA is required and the Bode plot measurements can be displayed on the computer monitor. In addition, the experimental waveforms can be measured and displayed by the oscilloscope.