3.1. Oscillating Mechanism of an Inverter-Based RC Oscillator

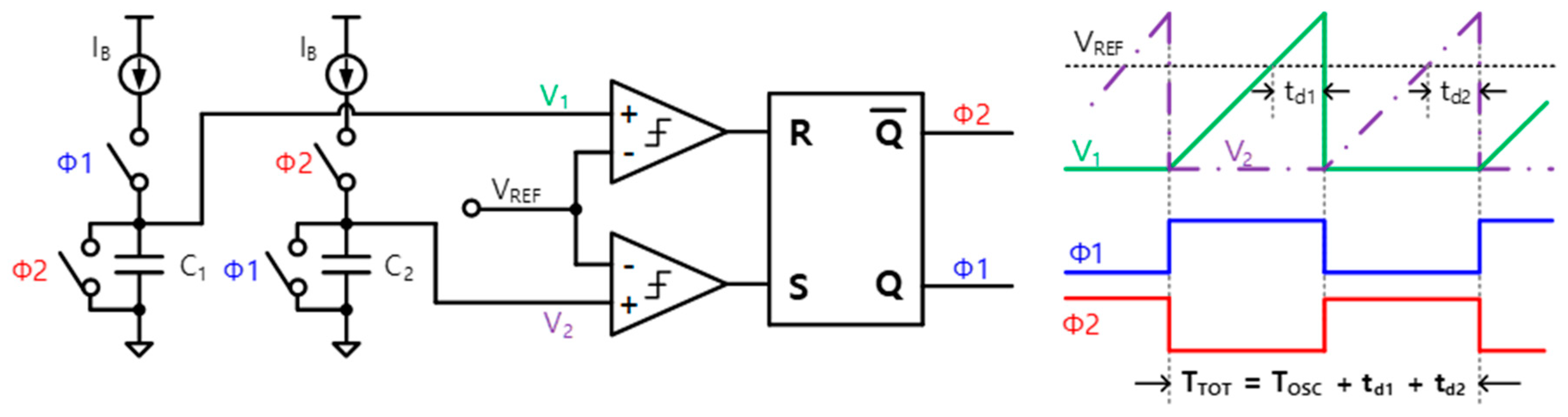

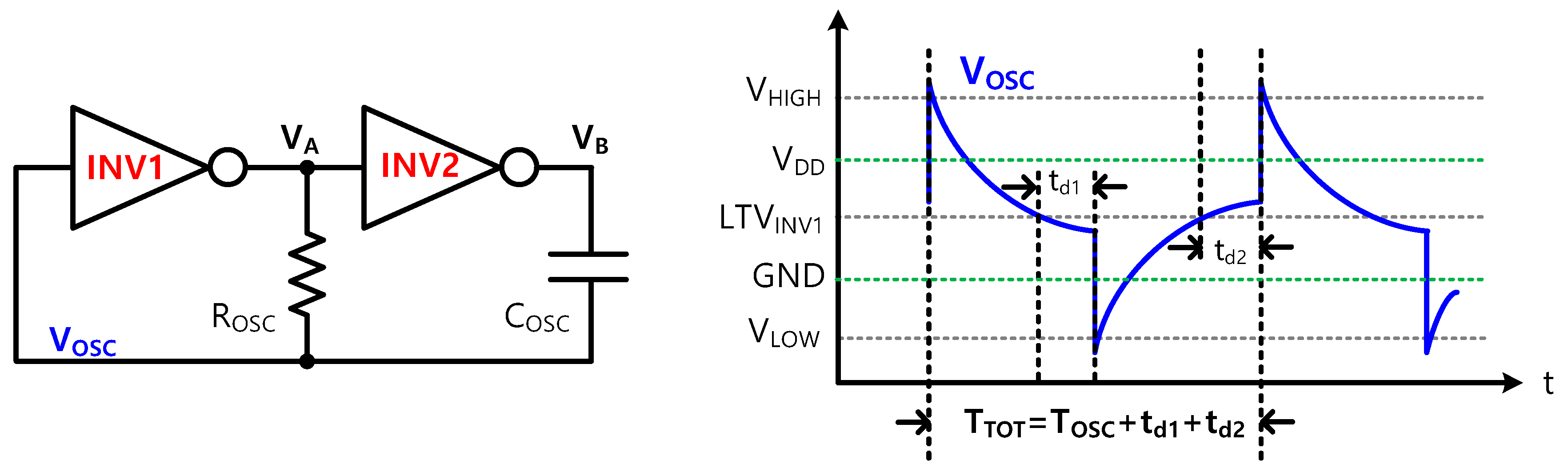

A simple example of the structure and waveform of an inverter-based RC oscillator is shown in

Figure 4. In practice, the gain of the inversion stages (

INV1 and

INV2 in

Figure 4) should be large enough to allow for oscillation, and the proposed oscillator uses multiple inverters to allow for high gain [

7]. When the

,

, and

nodes are, respectively, high, low, and high,

gradually decreases as

discharges

. When

equals the LTV of INV1, where the input and output voltages are the same,

and

change to logical high and low states, respectively. Since the charge on the capacitor should be the same, the voltage change at the

node lowers the

equally, making

equal to

. Next, since the

node voltage decreases while

stays in the high state,

is charged through

, and the

node voltage increases. Similarly, when the charging

passes the

level, the

node voltage rises to

, due to the logic changes in the following inverters. The timing diagram in

Figure 4 shows the charge and discharge cycles of the

node, where t

d1 and t

d2 are the circuit delays of the inverter chain.

The discharge curve of

is represented by the following equation:

The charging equation of

is:

Therefore, ignoring the circuit delay, the ideal period of the inverter-based RC oscillator is calculated as being:

If

is equal to half of

, the ideal oscillation period

is

, and the ideal duty cycle is 50% [

7].

Taking circuit delay into consideration, the practical period of the oscillator is as follows:

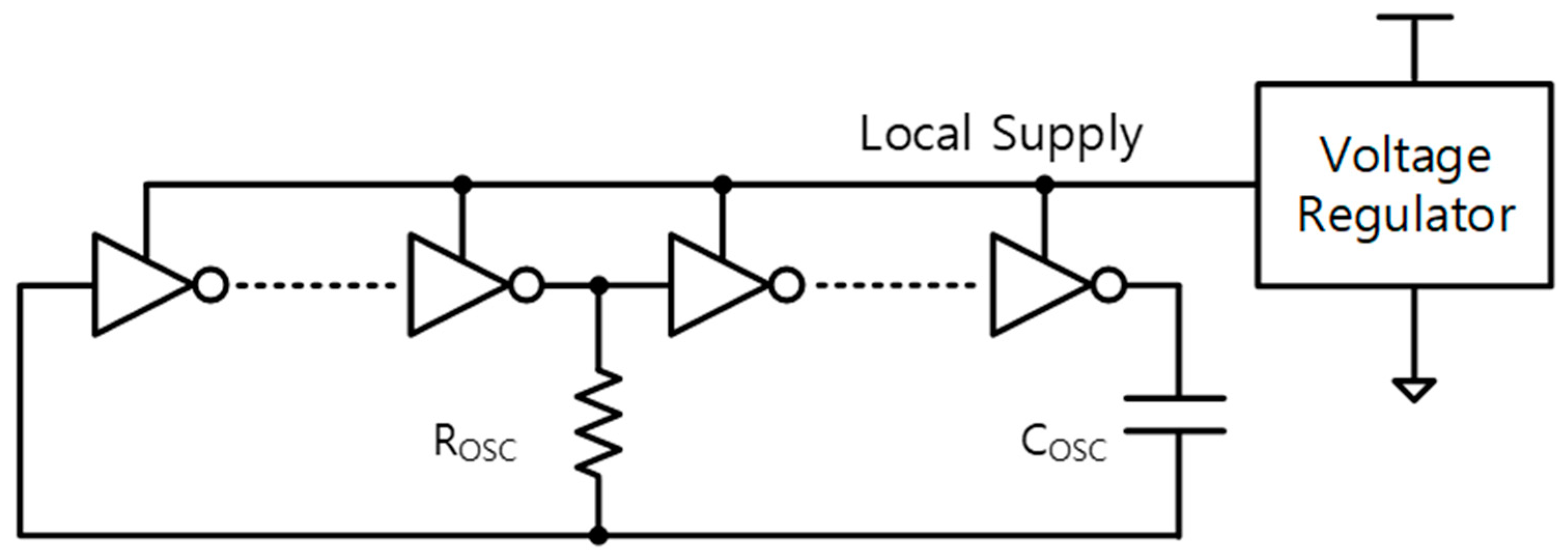

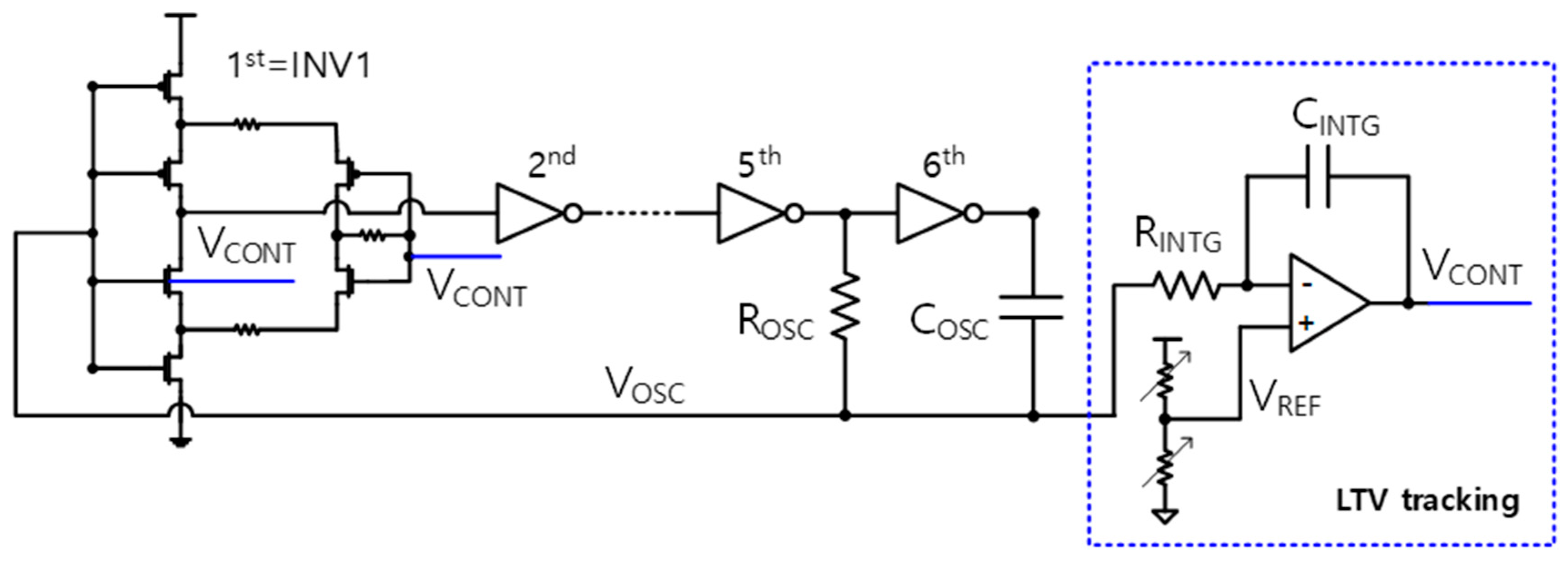

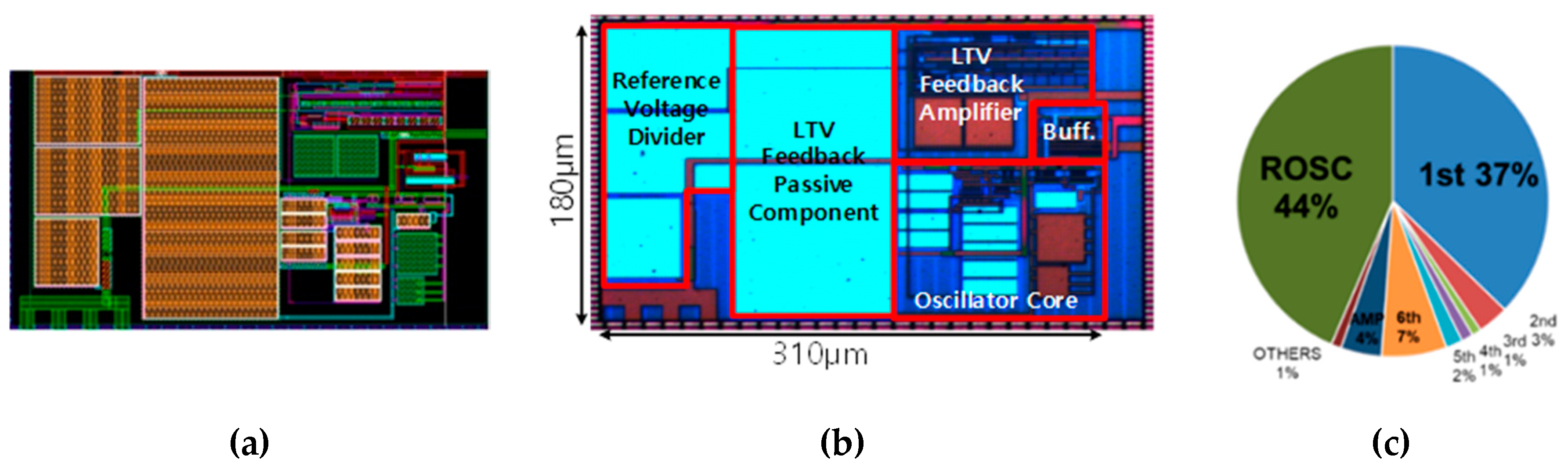

3.2. Architecture of Proposed Oscillator

Figure 5 shows the structure of the proposed inverter-based, on-chip RC oscillator. The inverter chain implemented is as small as possible to ensure low power operation. The second to sixth inverters have a standard structure, but the first-stage inverter (

INV1 in

Figure 5) has been reconfigured to control its LTV. The

from the resistive divider and

are inputs to the LTV tracking feedback, and its output—

—controls

. Charging and discharging at the

node causes an oscillation due to the inverter logic switching, so the entire inverter chain can be seen to function as a comparator. INV1 is the most sensitive to noise and circuit fluctuations, as the slew rate at its input (

) is slower than that of the other nodes. Also, transistor noise in INV1 has a significant effect on circuit delay variation. Thus, because of this sensitivity, INV1 is considered to be the main comparator and its LTV is regarded as the reference voltage for comparison.

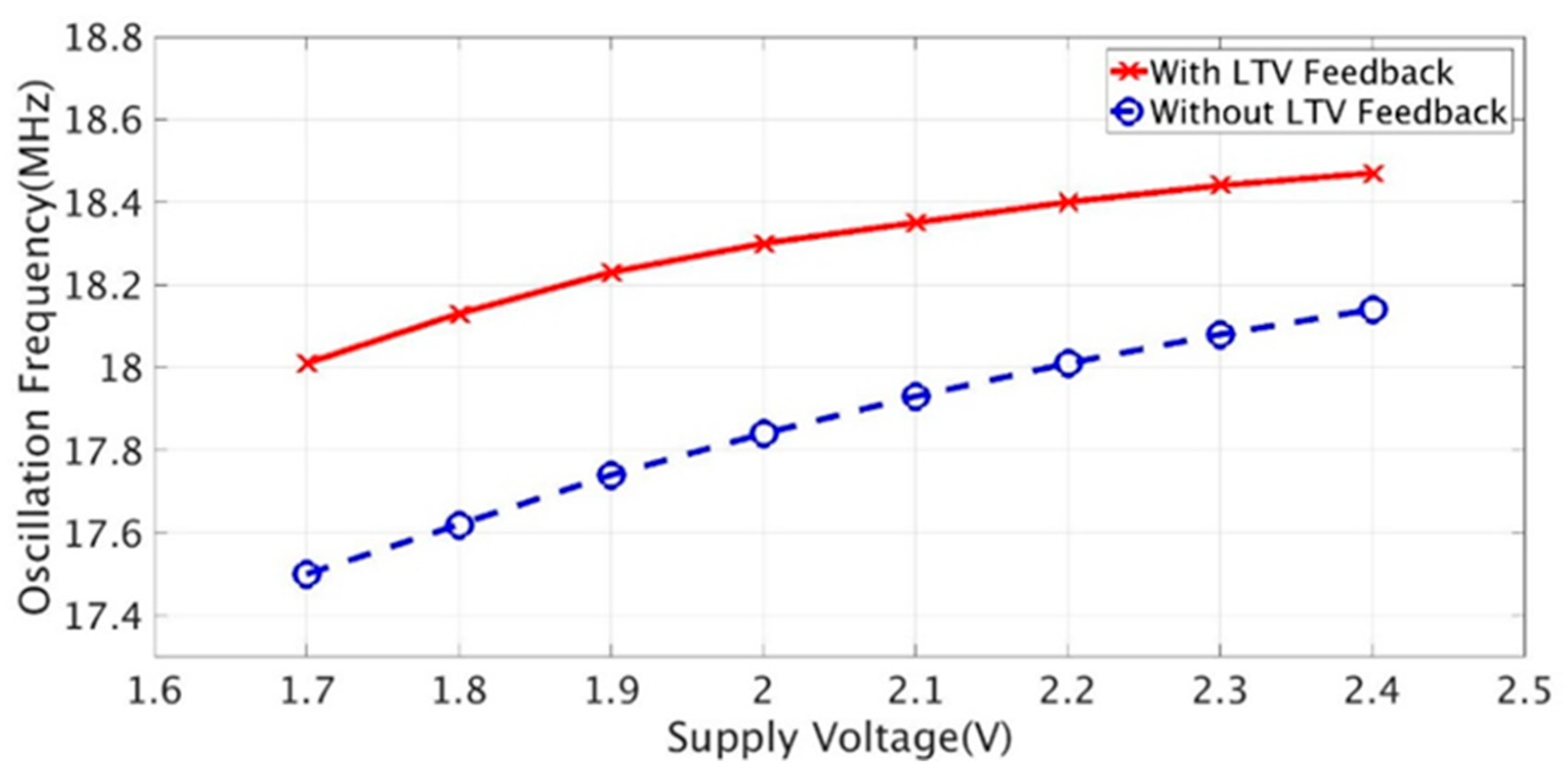

From Equation (5), the operating frequency of the inverter-based RC oscillator without circuit delay is a function of

.

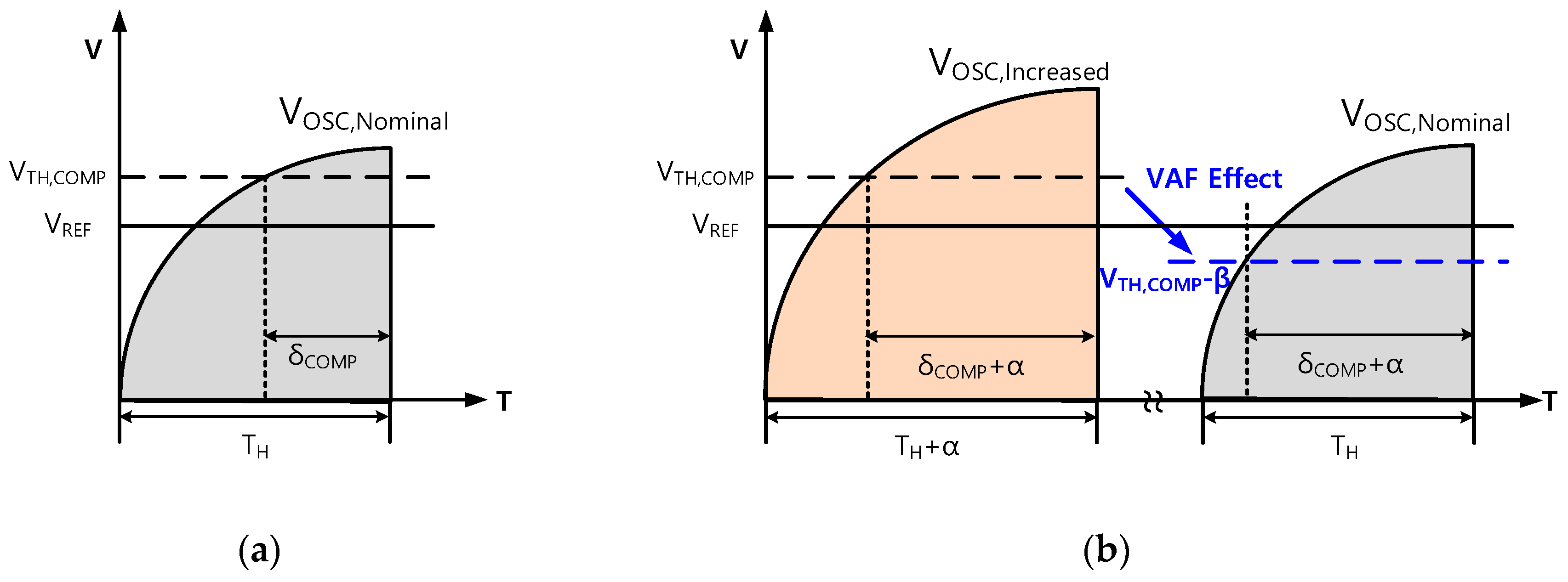

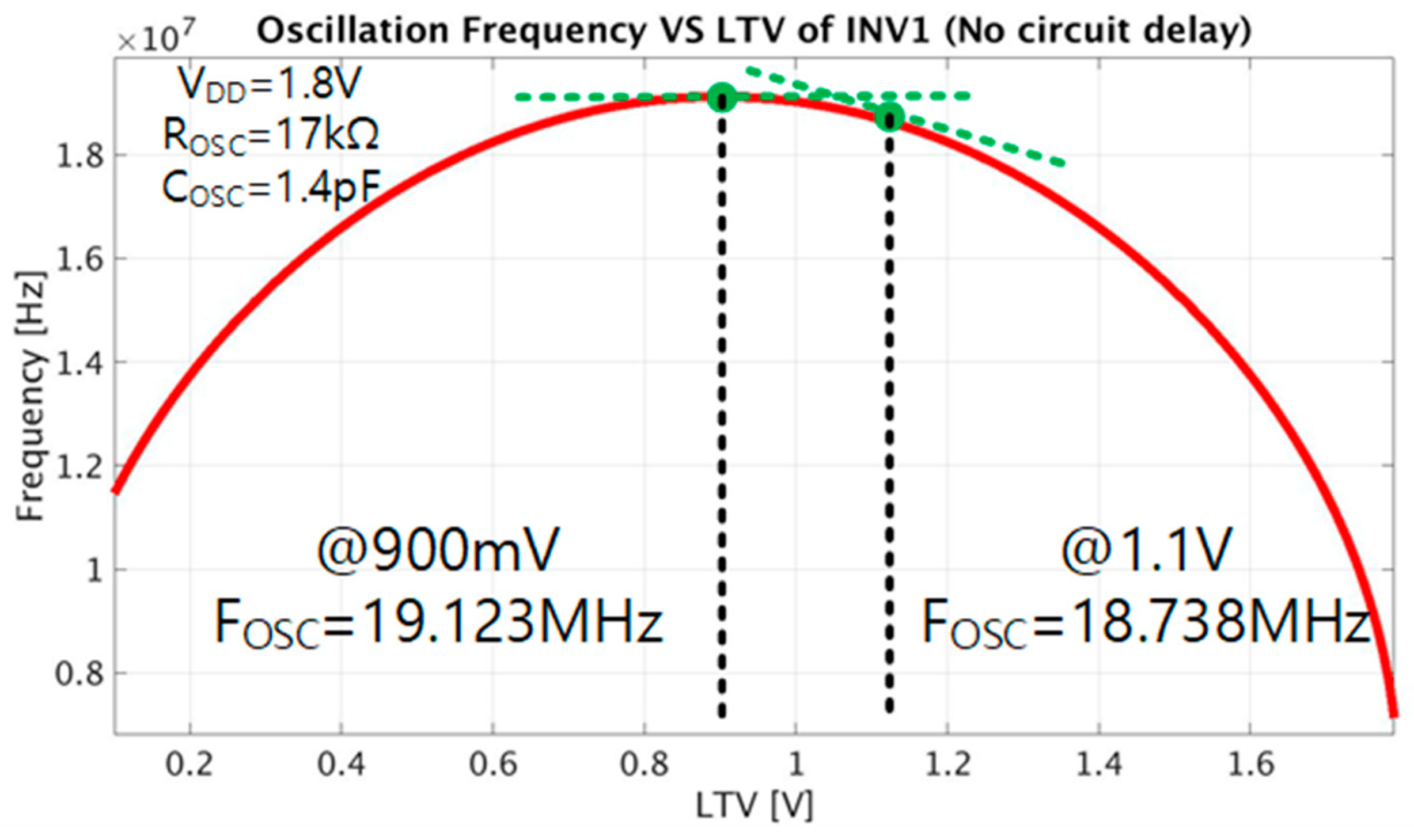

Figure 6 illustrates

(

) of the oscillator as a function of

with

= 1.8 V,

= 17 kΩ, and

= 1.4 pF.

is an inverted U-shaped curve with a maximum of 19.123 MHz when INV1 LTV is 900 mV, which is half of

.

In a practical oscillator, the frequency contains a circuit delay component as expressed in Equation (6), and delay variations degrade the oscillator’s stability. Thus, in order to reduce the influence of these variations, a method is required to detect delay changes and to maintain a constant frequency. As shown in

Figure 3, the VAF scheme senses delay variation by comparing graph areas, and the reference voltage of the comparator is changed to maintain a constant frequency.

The suggested LTV tracking technique utilizes the VAF concept for control to reduce the effects of circuit delay variations. The proposed oscillator works by comparing the graph area configured by and , to estimate the delay variation. For example, if the circuit delay increases, the graph area grows while the area under is unchanged. In addition, as demonstrated in Equation (6), this increased delay causes a decrease in oscillation frequency.

In order to achieve good frequency stability, an operating frequency compensation mechanism that responds to circuit delay variations is required.

Figure 6 shows that the oscillation frequency of an inverter-based RC oscillator is determined by the

, unless the passive components (

and

) change. Thus, the proposed LTV tracking scheme allows for the oscillator to have a constant operating frequency by adjusting the

from

(the feedback loop output).

If the nominal value of

is 900 mV (half of the 1.8 V supply), the oscillation frequency variation for the LTV change is close to zero, as indicated by the horizontal tangent line in

Figure 6. Furthermore, increasing or decreasing the LTV to around 900 mV only lowers the oscillator frequency relative to the maximum value, so the oscillator cannot cope with longer circuit delay situations. Therefore, because the integrator of the LTV tracking loop makes the DC voltage of

equal to

, the proposed scheme raises the

by setting the resistive divider output to 1.1V, in order to control the oscillator frequency against any variations of

.

In this approach, the oscillator cannot sustain a 50% duty cycle, but the sensitivity of the operating frequency to

is increased (see the increased tangent line slope in

Figure 6). When maintaining negative feedback, the increase/decrease of the LTV relative to 1.1 V causes frequency decrease/increase. Considering frequency controllability alone, LTV’s larger than 1.1V can be used, but this will increase power consumption. The proposed structure enables high-frequency operation by connecting the chip supply to the inverter chain, rather than to the regulated supply, and the large voltage swing at the

node reduces the comparator noise of the inverter chain [

2].

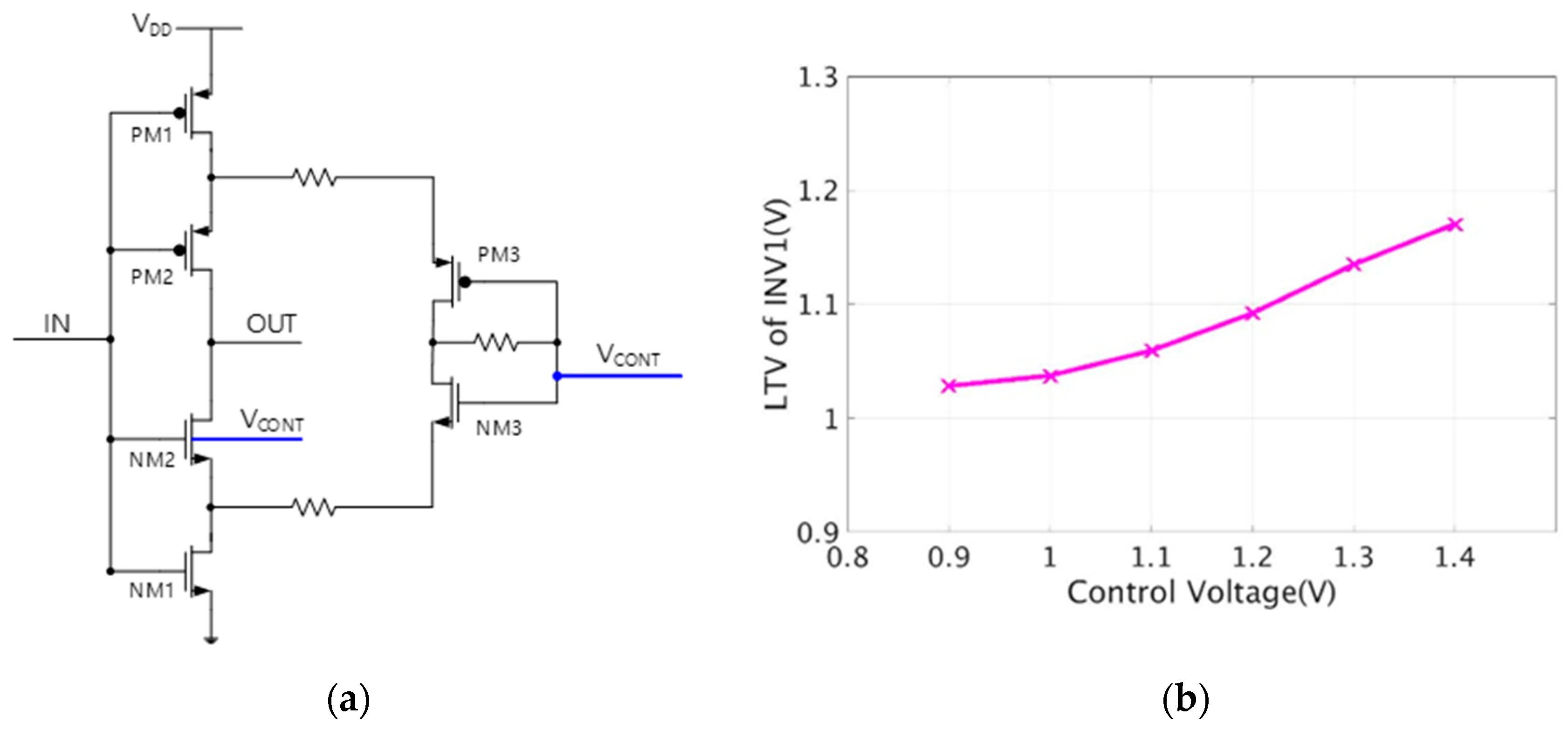

3.3. The First-Stage Inverter

In a basic inverter structure consisting of one NMOS transistor and one PMOS transistor, it is not easy to change the LTV of the inverters, except for the supply voltage control. Therefore, a structural change of the inverter is required to control

.

Figure 7a shows the proposed INV1 schematic for LTV control, where

stands for the output of the feedback loop. Since the input DC voltage from LTV tracking feedback (

) is 1.1 V for oscillation frequency control, the

value is set so that

becomes 1.1 V. Transistors PM2 and NM2 are stacked in the output path, and the substrate of NM2 is connected to

. PM3 and NM3, with

as inputs, are connected to the main inverter path, forming an auxiliary path through a resistor connected to each source node.

Changing the supply voltage to adjust the inverter’s LTV further lowers the frequency stability of the inverter chain-based RC oscillator. Also, to maintain the supply voltage, a large chip area is required to change the LTV, using the driving current from multiple connected transistors with switches. However, the proposed method controls

relative to 1.1 V, by controlling the pull-down strength with

while using a simple structure. An increased

reduces the current drive capability of the NMOS pull-down path [

9], resulting in a higher

. Thus, the oscillation frequency decreases according to Equation (5), as illustrated in

Figure 6. In addition, because a decreased

leads to a lower

, an increase/decrease in

causes a decrease/increase in oscillator frequency.

Figure 7b shows the change in

when the control voltage

varies from 0.9 V to 1.4 V. Since the nominal voltage of

is set to 1.1 V, the positive

turns on the PN diode between the substrate node and the source node of NM2 in

Figure 7a. The increase in

causes the drain-source current of NM2 to be reduced, by increasing its substrate-source diode current while the drain-source current of NM1 is constant. In this situation,

increases because the reduced

weakens the inverter pull-down strength. Consequently,

is controlled by

which determines the current capability. Furthermore, the auxiliary path consisting of PM3 and NM3 increases the sensitivity of INV1 to the control voltage. This is because the additional structure not only helps the LTV tracking loop settle the output, but also adjusts the amount of INV1 pull-down current.

In [

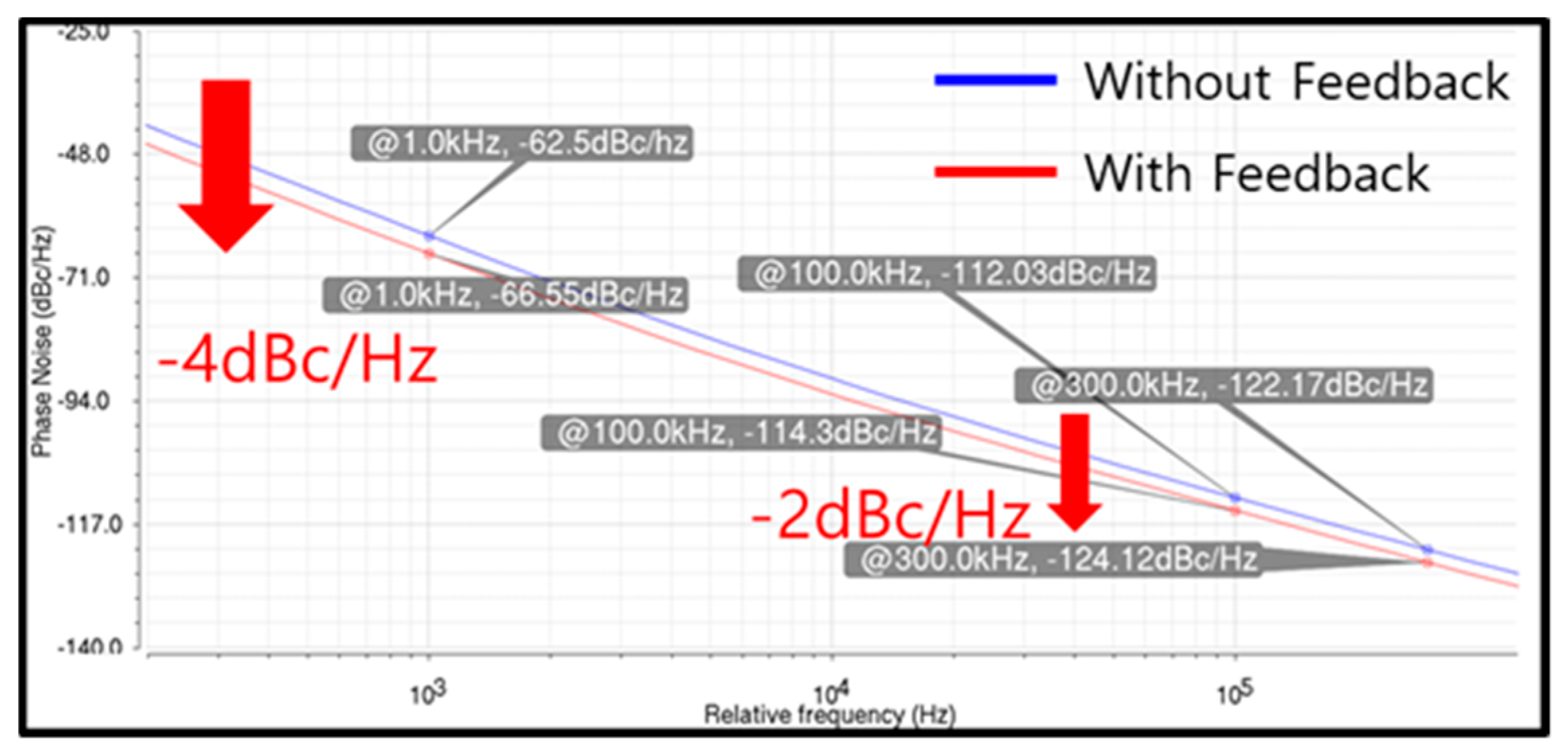

5], the authors introduced an on-chip relaxation oscillator flicker noise suppression method, by modeling the relaxation oscillator as a voltage-controlled oscillator (VCO) and applying the VAF technique. Since the VAF loop creates a high-pass filter, closed-loop transfer function for phase noise, the low-frequency offset phase noise is reduced.

The suggested inverter-based RC oscillator is also a VCO, the frequency of which is controlled by

LTVINV1, and we use the VAF concept for the negative feedback structure. The proposed LTV tracking feedback decreases flicker noise in the oscillator, because the noise transfer function in [

5] can be applied.

Figure 8 shows the noise transfer model, especially for the oscillator phase noise.

The phase noise of the VCO part is formulated as follows:

Unlike the phase noise transfer function in [

5], Equation (7) requires a voltage scaling factor

. This is because multiplying the output of the integrator

by

produces

, which controls the frequency of the oscillator. Equation (7)—with a high-pass, closed-loop transfer function characteristic—has zero and pole at f

z and f

p, which are described in the following equations:

Adjusting from 1 V to 1.4 V changes the from 1.183 V to 1.02 V, resulting in a value of 0.41 (absolute value without polarity). Under this condition, the calculated is 41.8 106 rad/secV, and the scaling factor γ is 0.38 V/MHz. Since and are 1.26 MΩ, and 1.93 pF, respectively, the simulated is 652.864 kHz, which is large enough to suppress the low frequency offset phase noise.