Hybrid PWM Strategy for Power Efficiency Improvement of 5-Level TNPC Inverter and Current Distortion Compensation Method

Abstract

1. Introduction

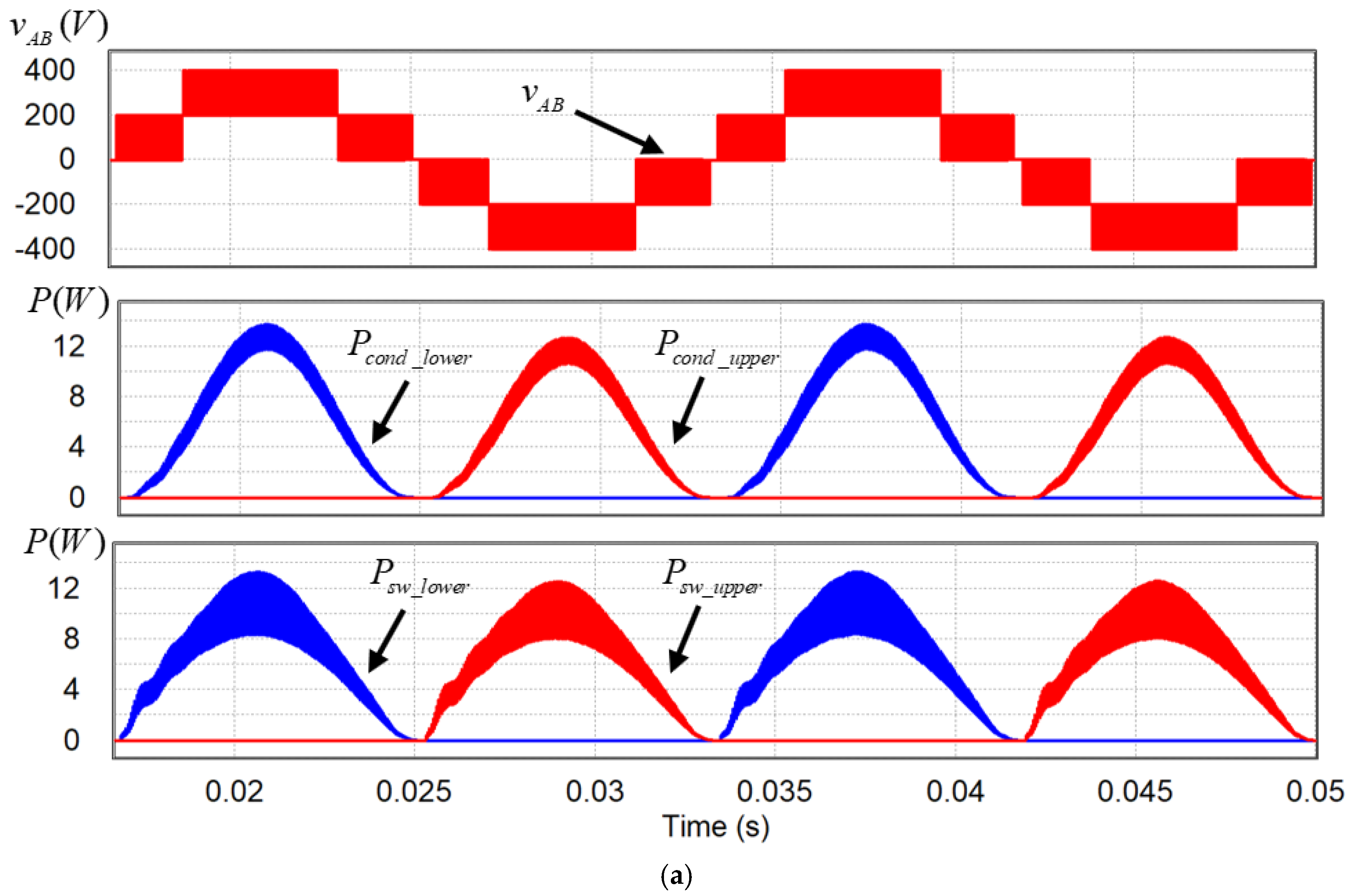

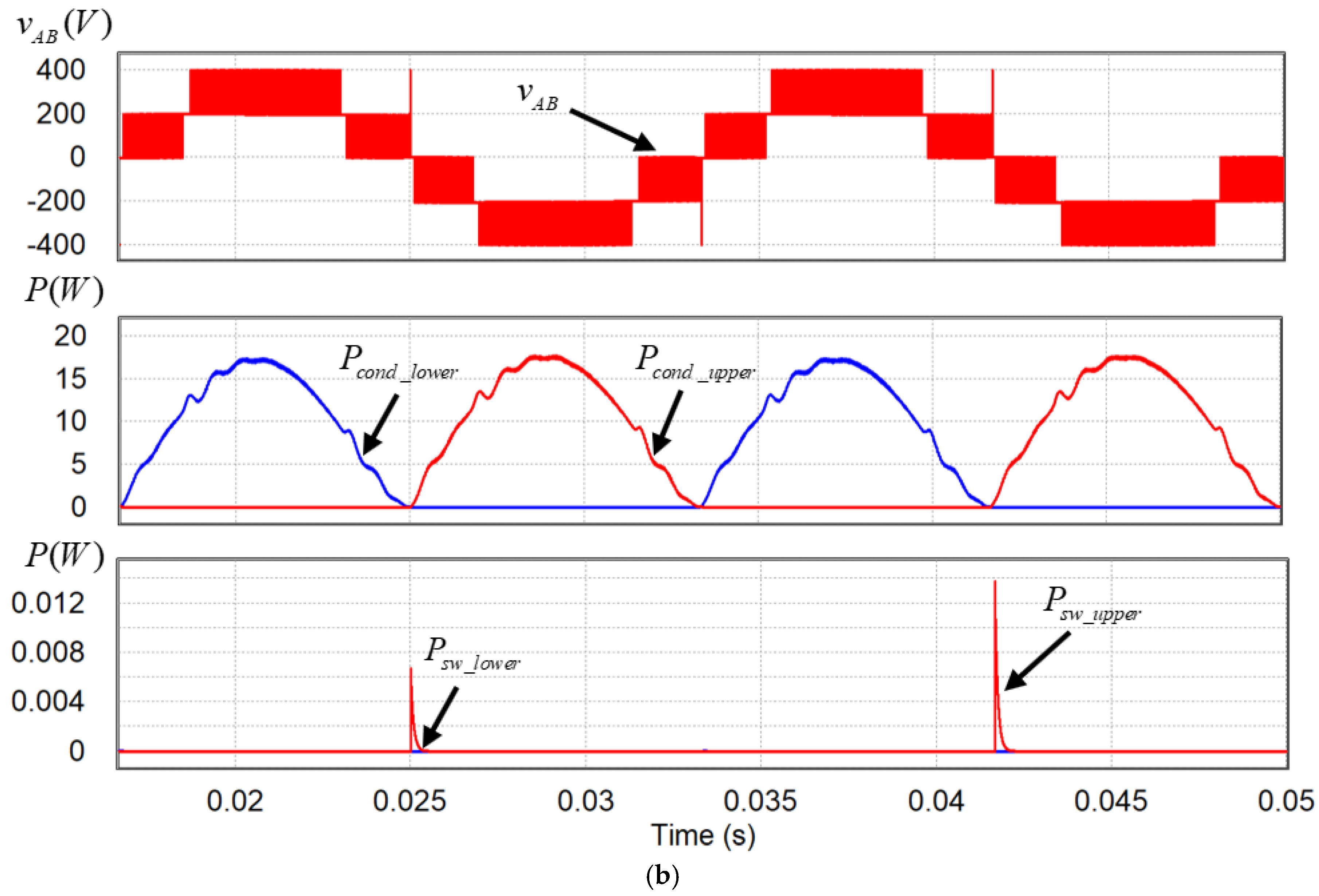

2. PWM Strategy for 5-LEVEL H-Bridge TNPC Inverter

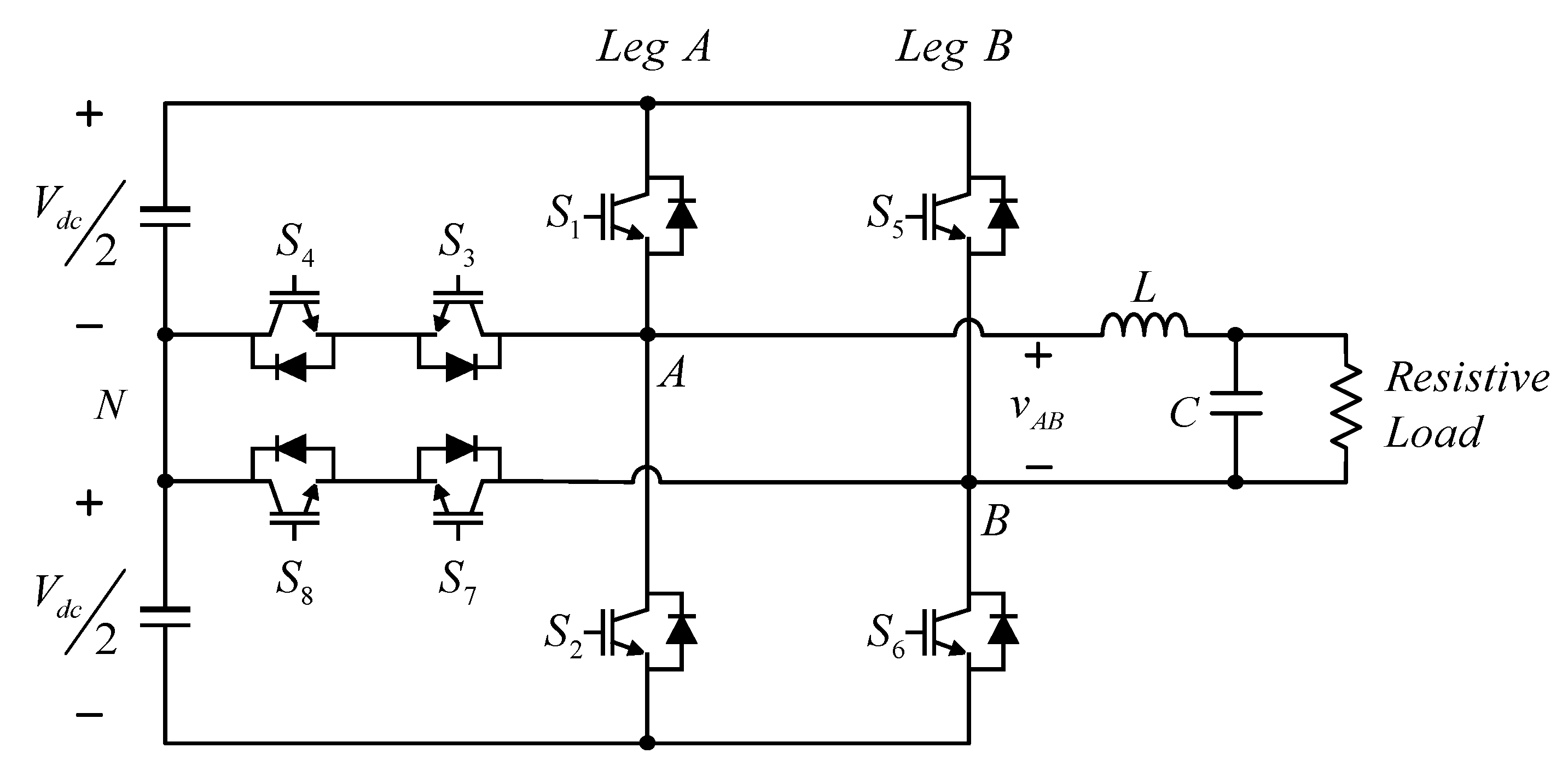

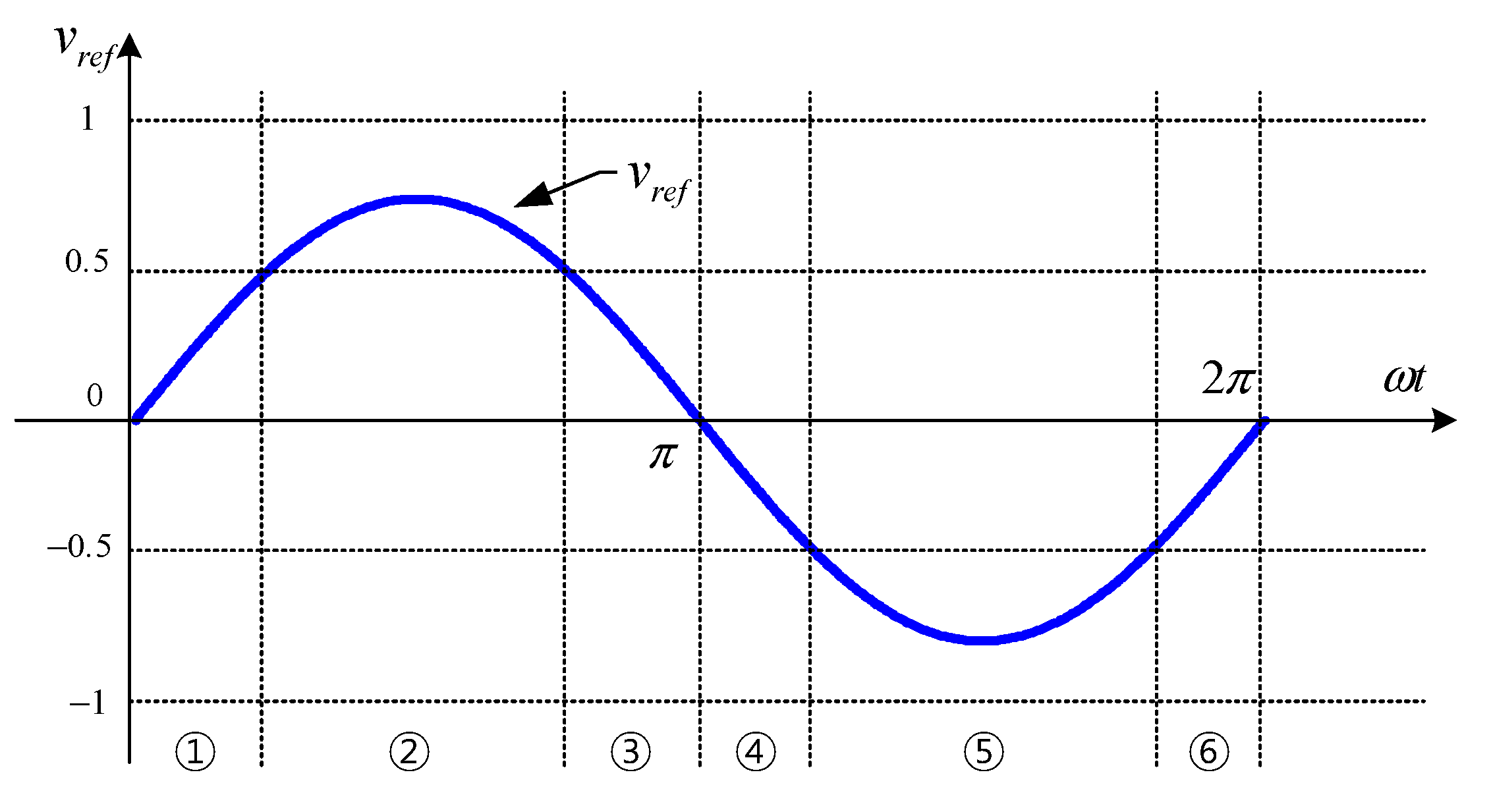

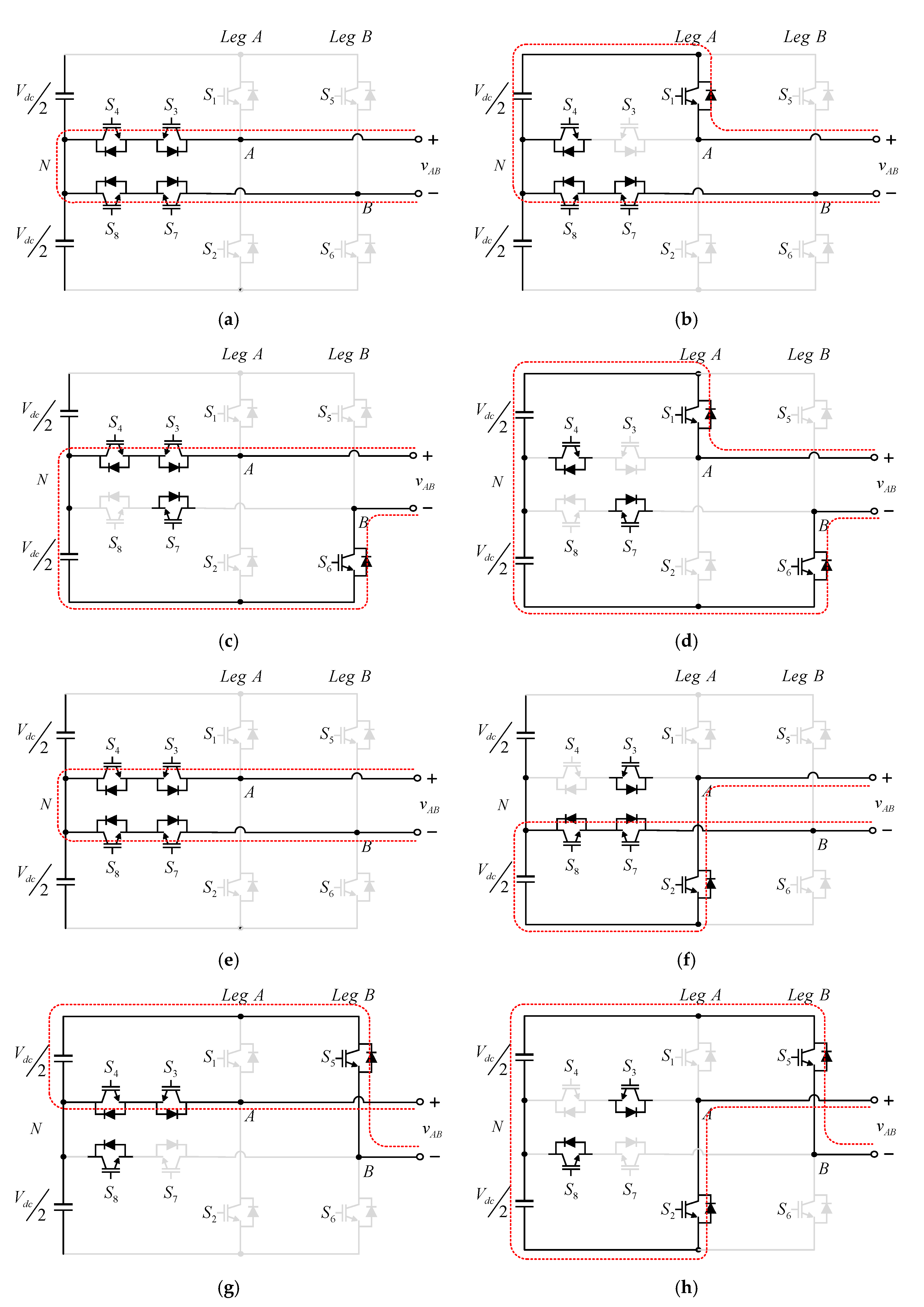

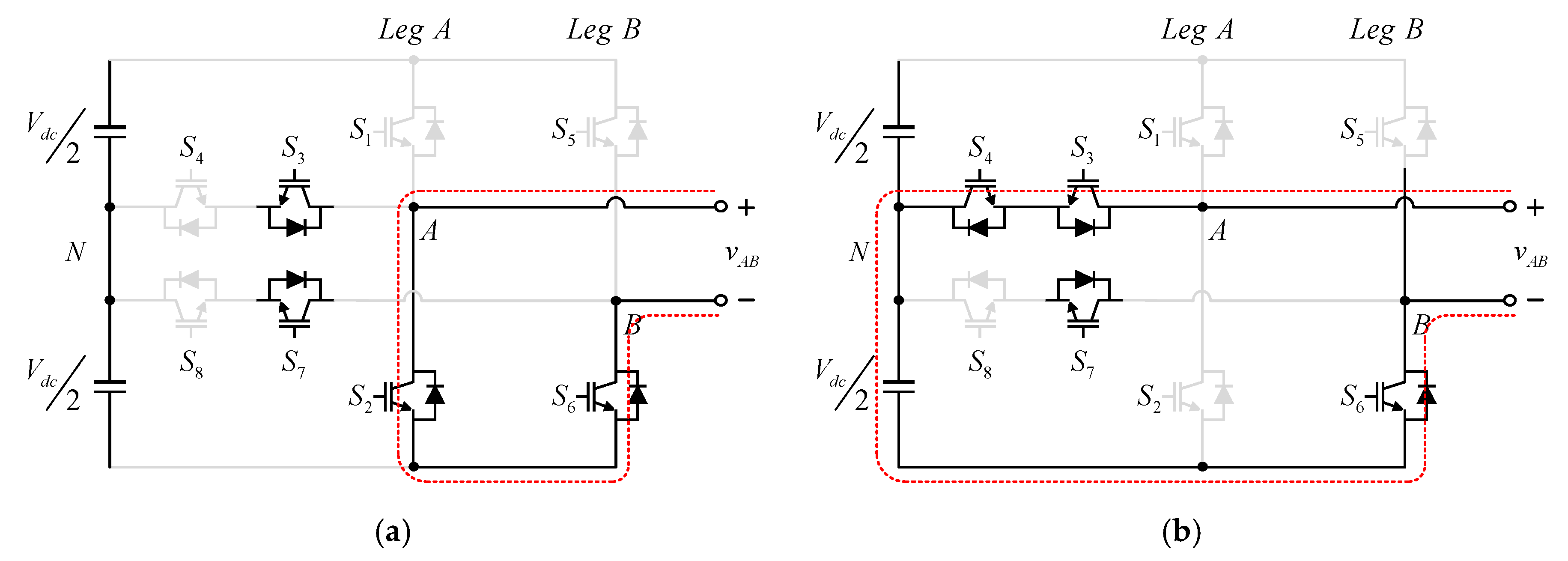

2.1. TNPC Inverter Configuration and the Conventional PWM Strategy

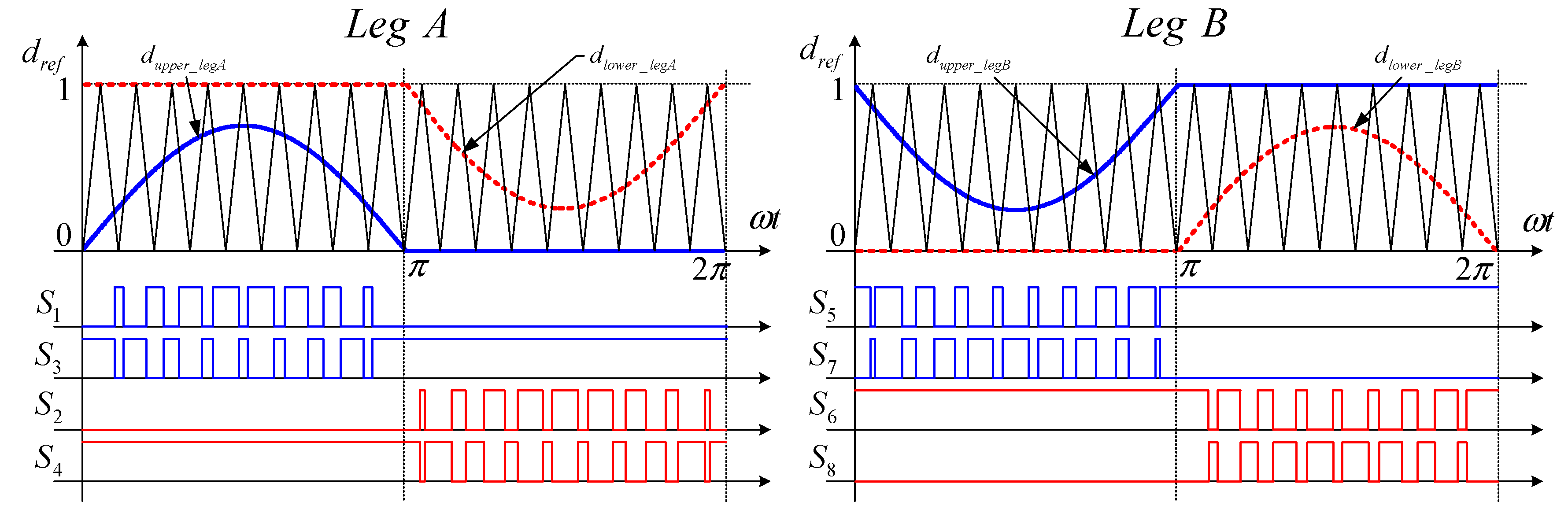

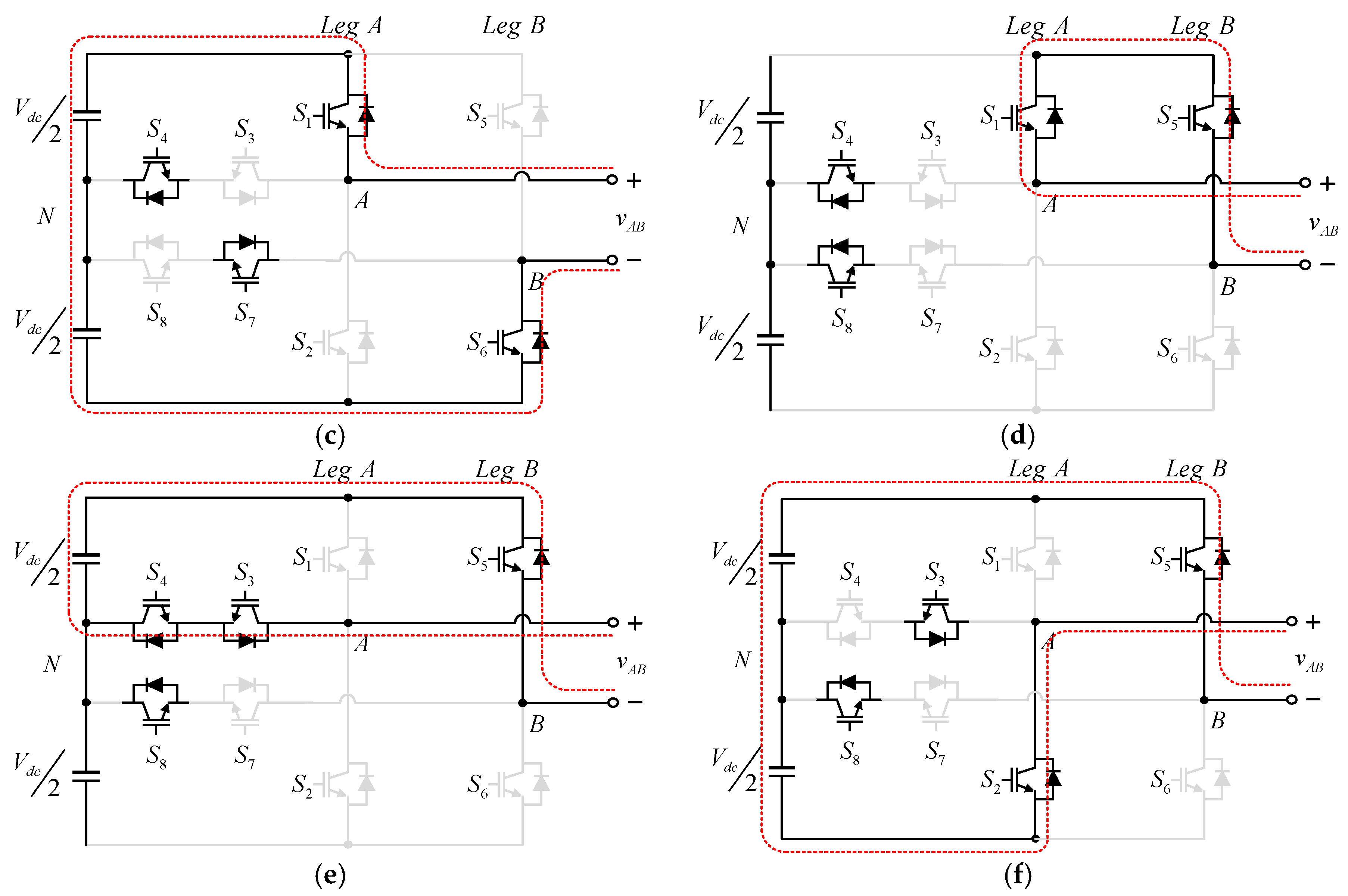

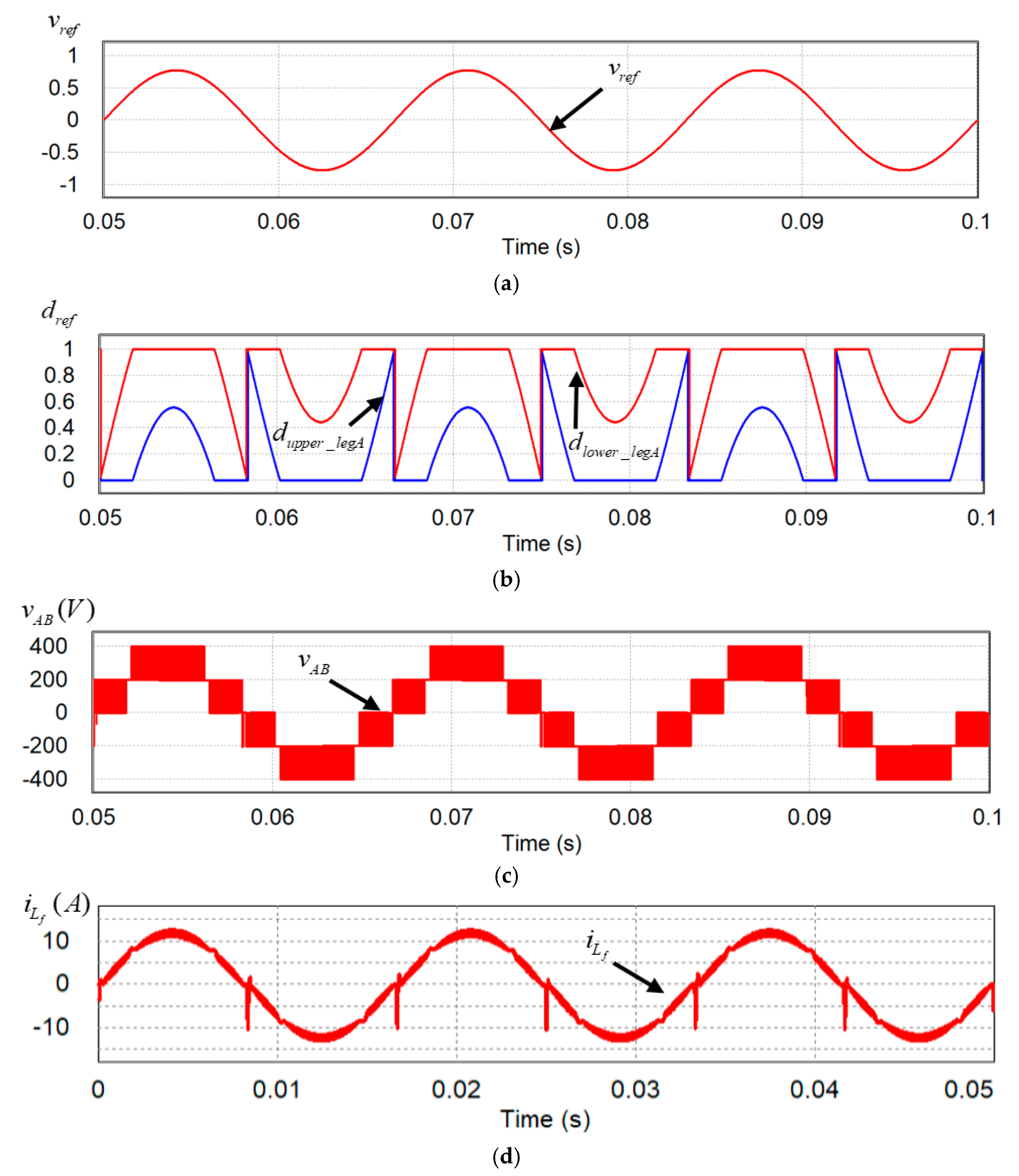

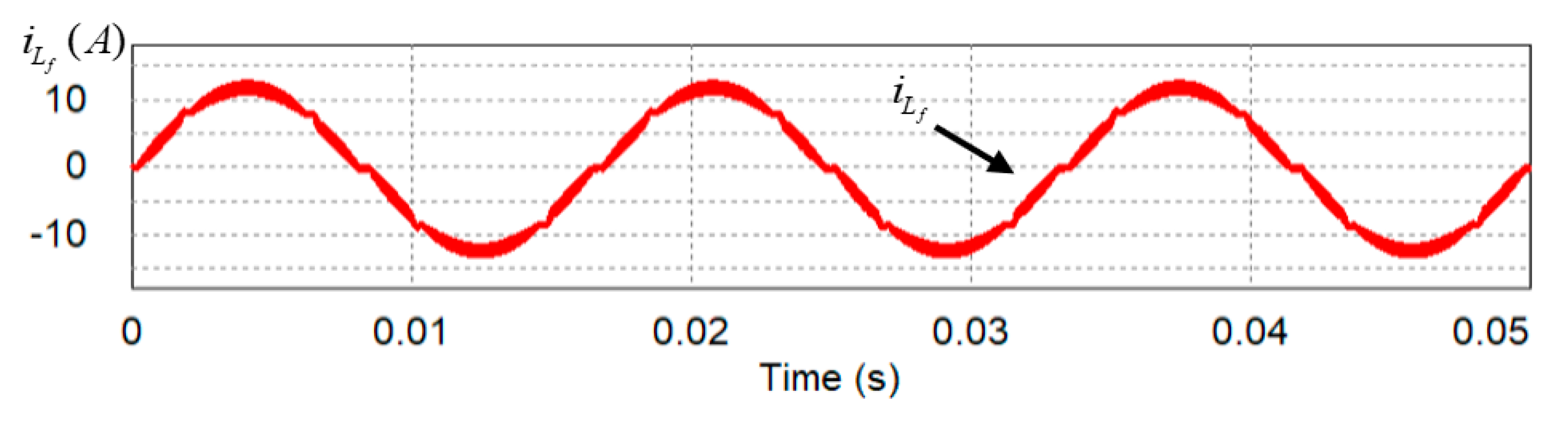

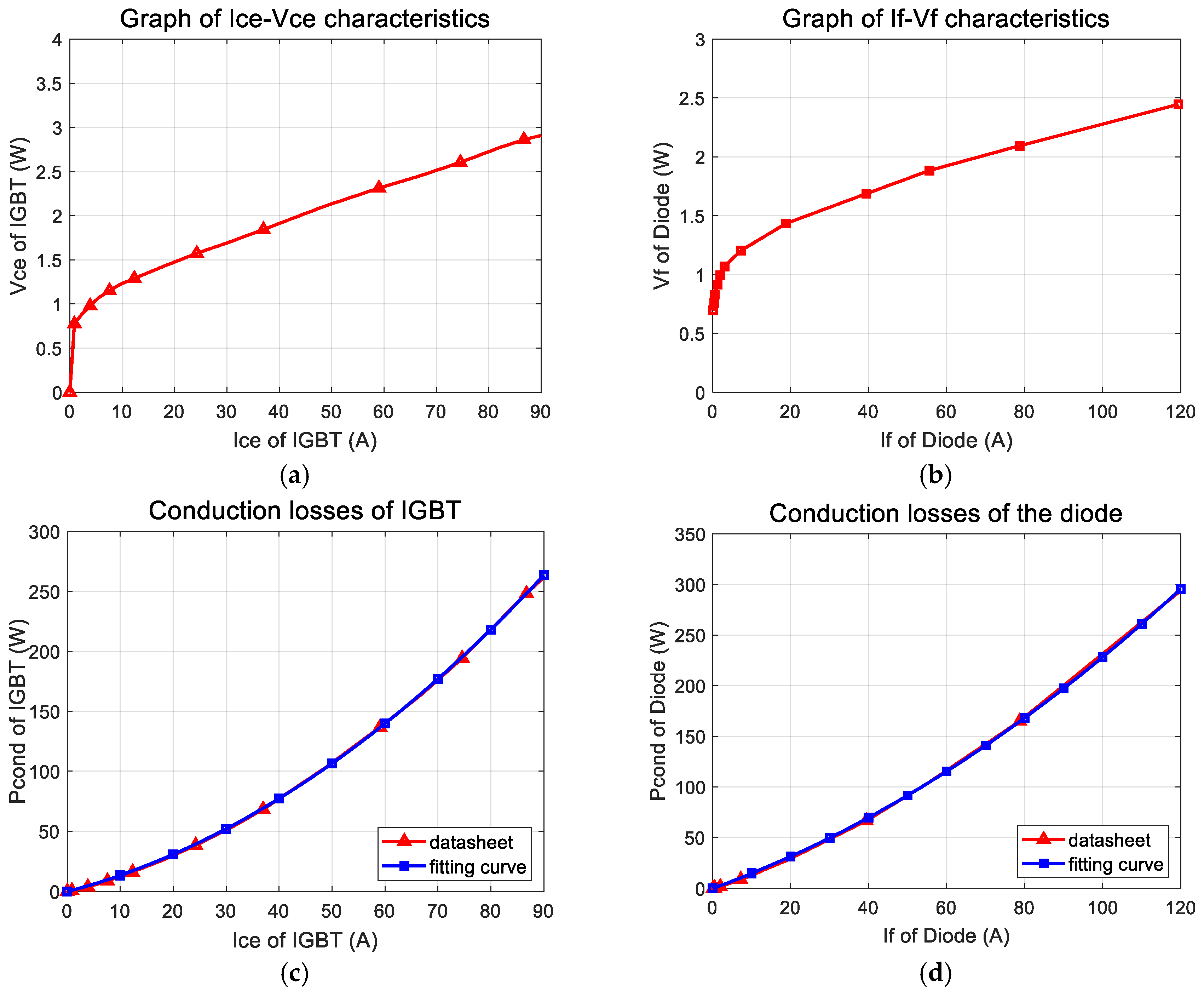

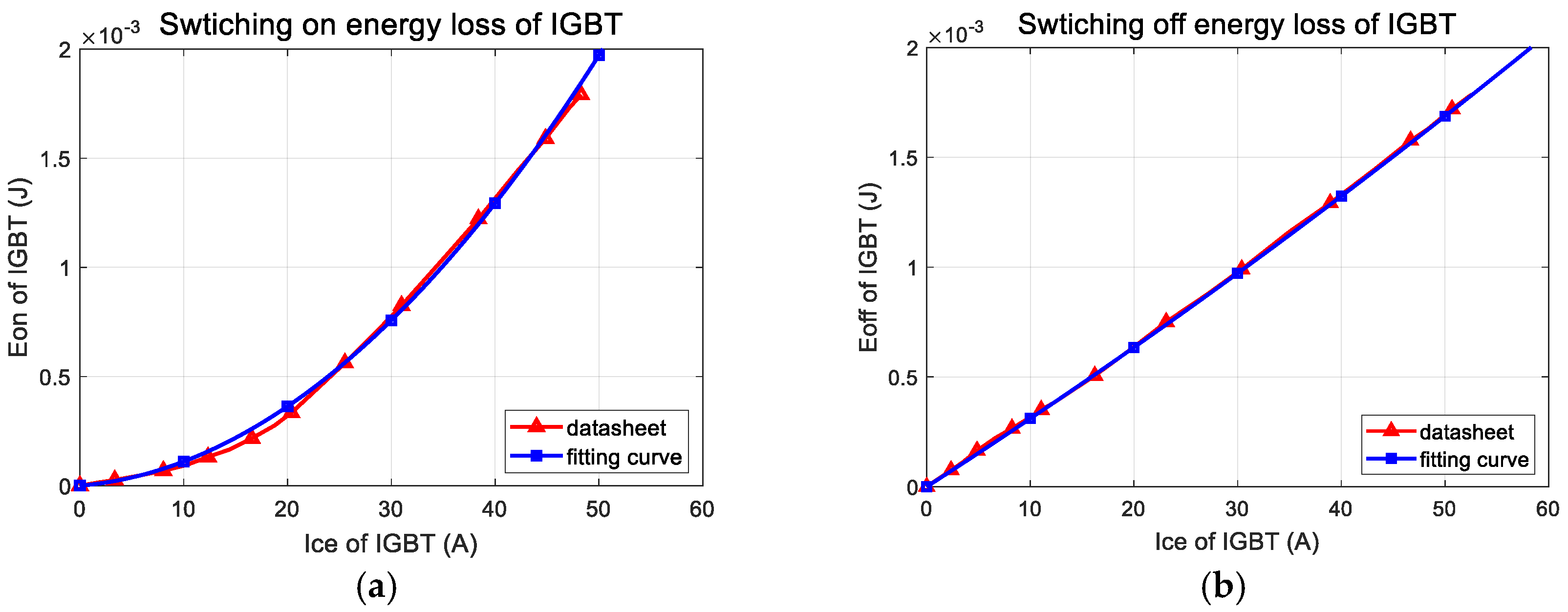

2.2. The Proposed PWM Strategy and Compensation Method

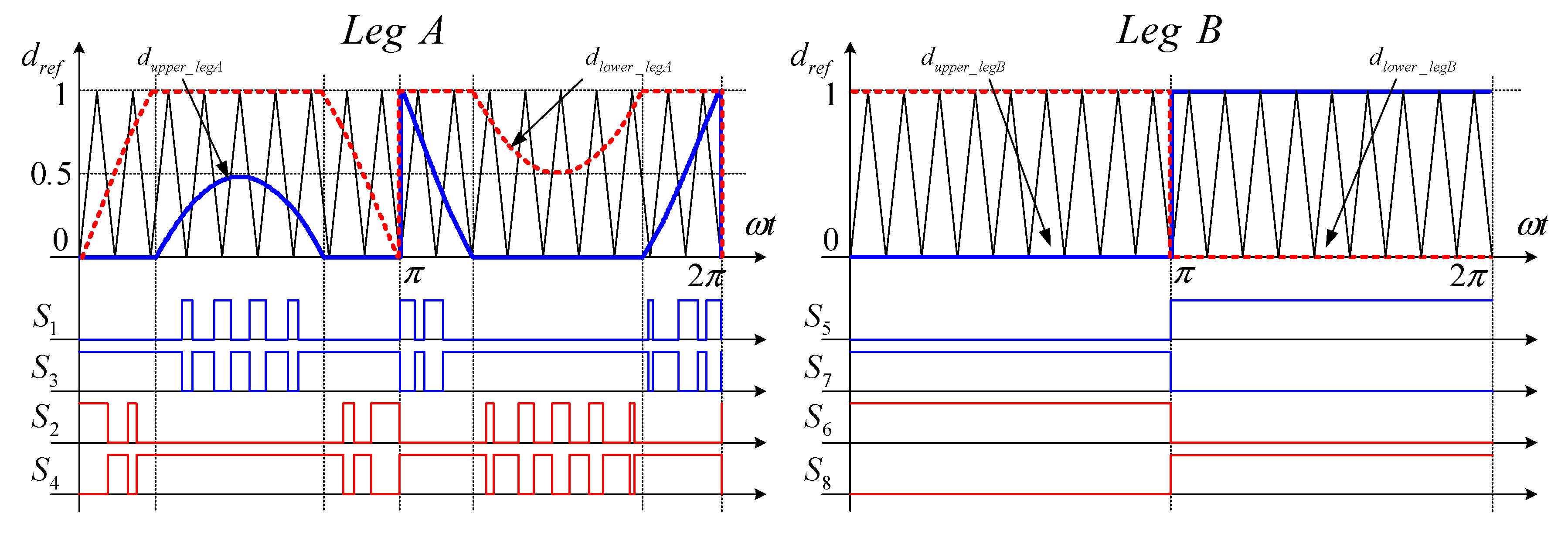

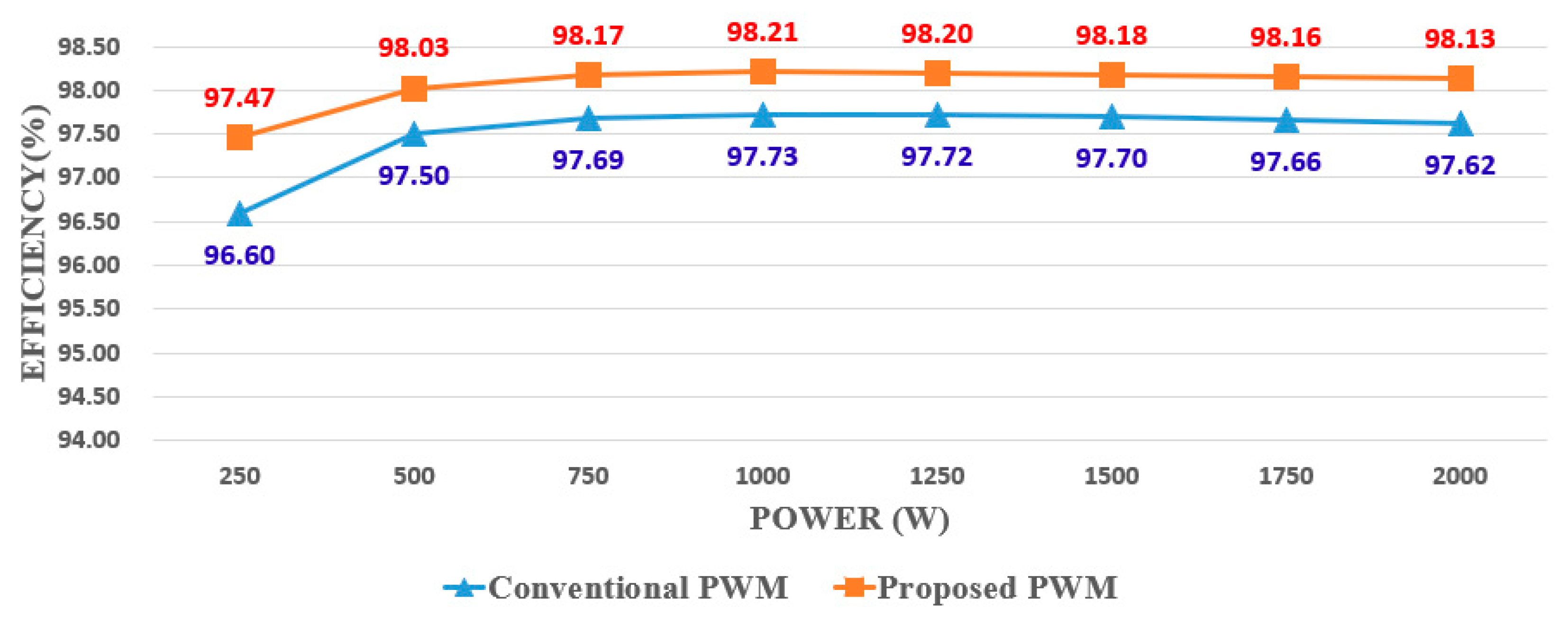

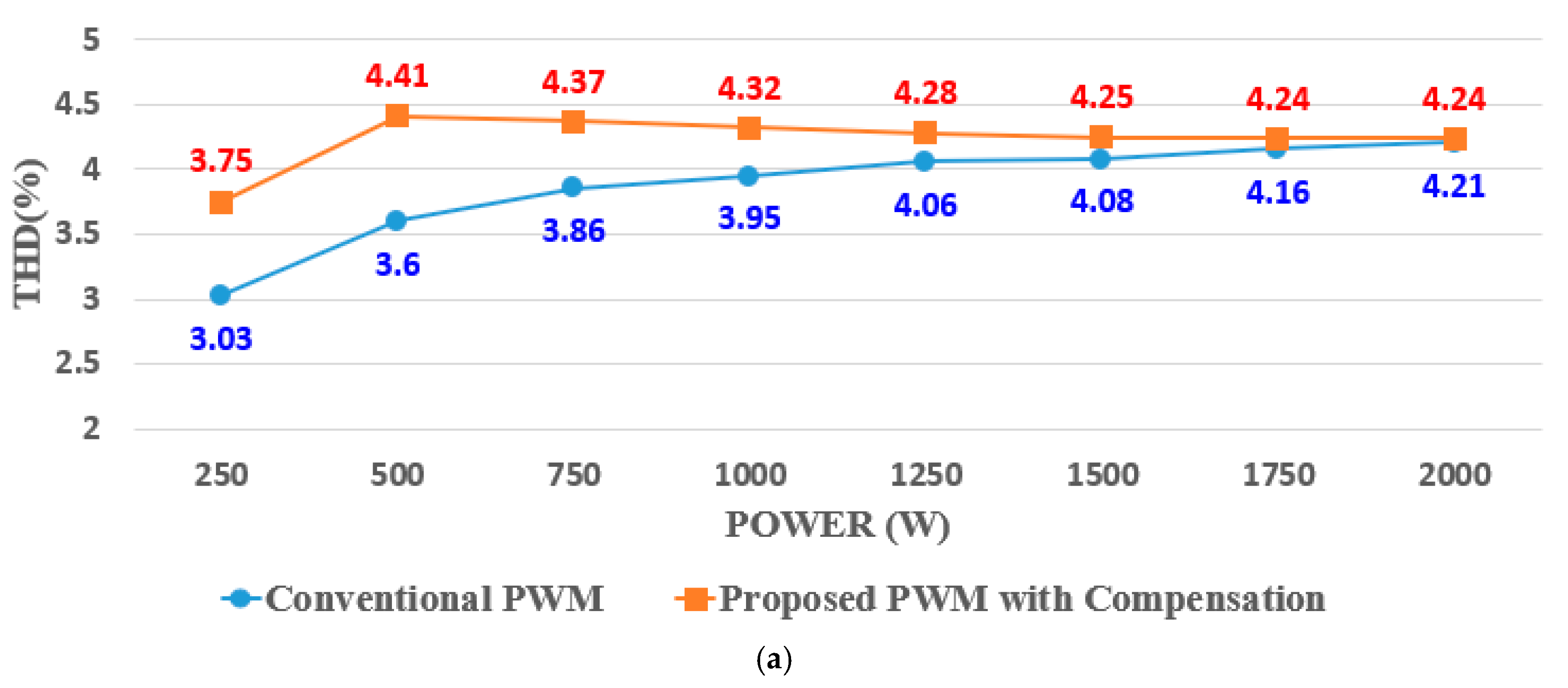

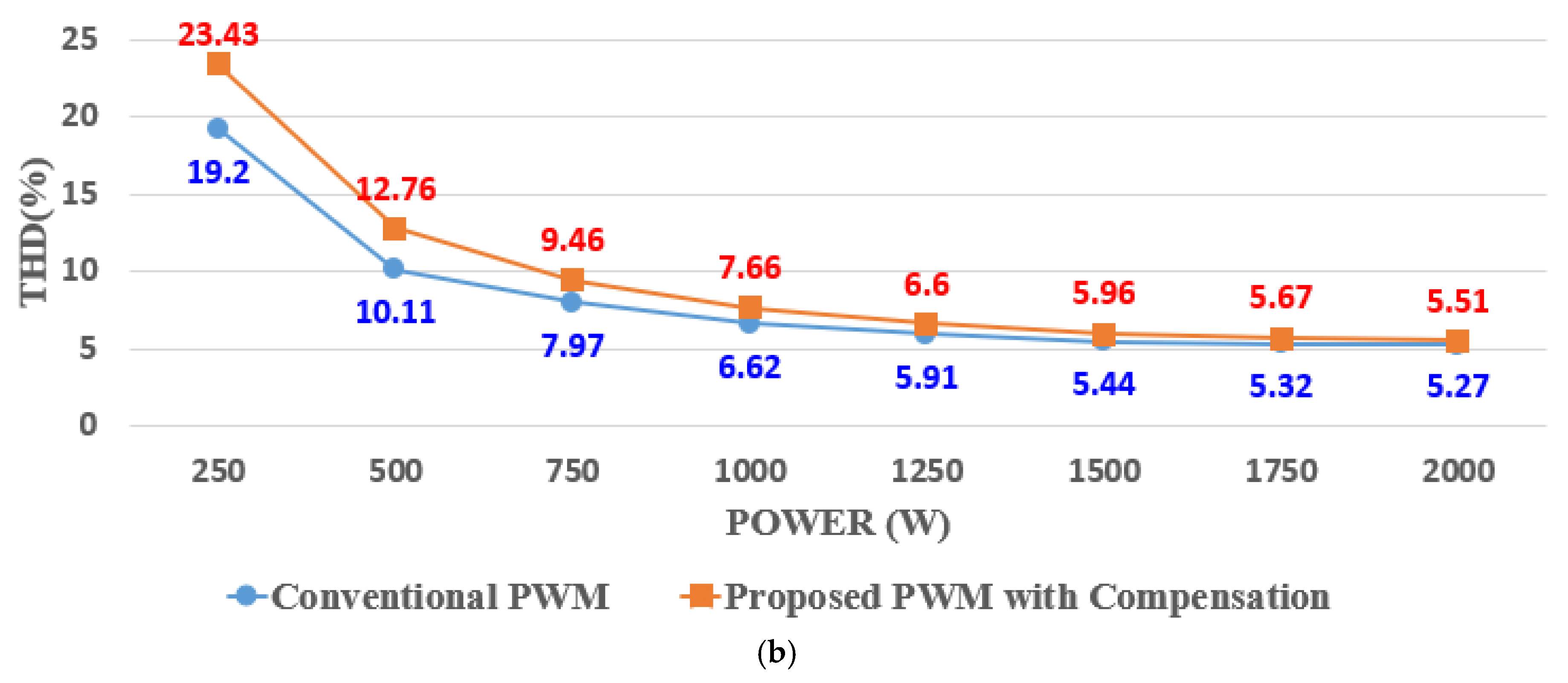

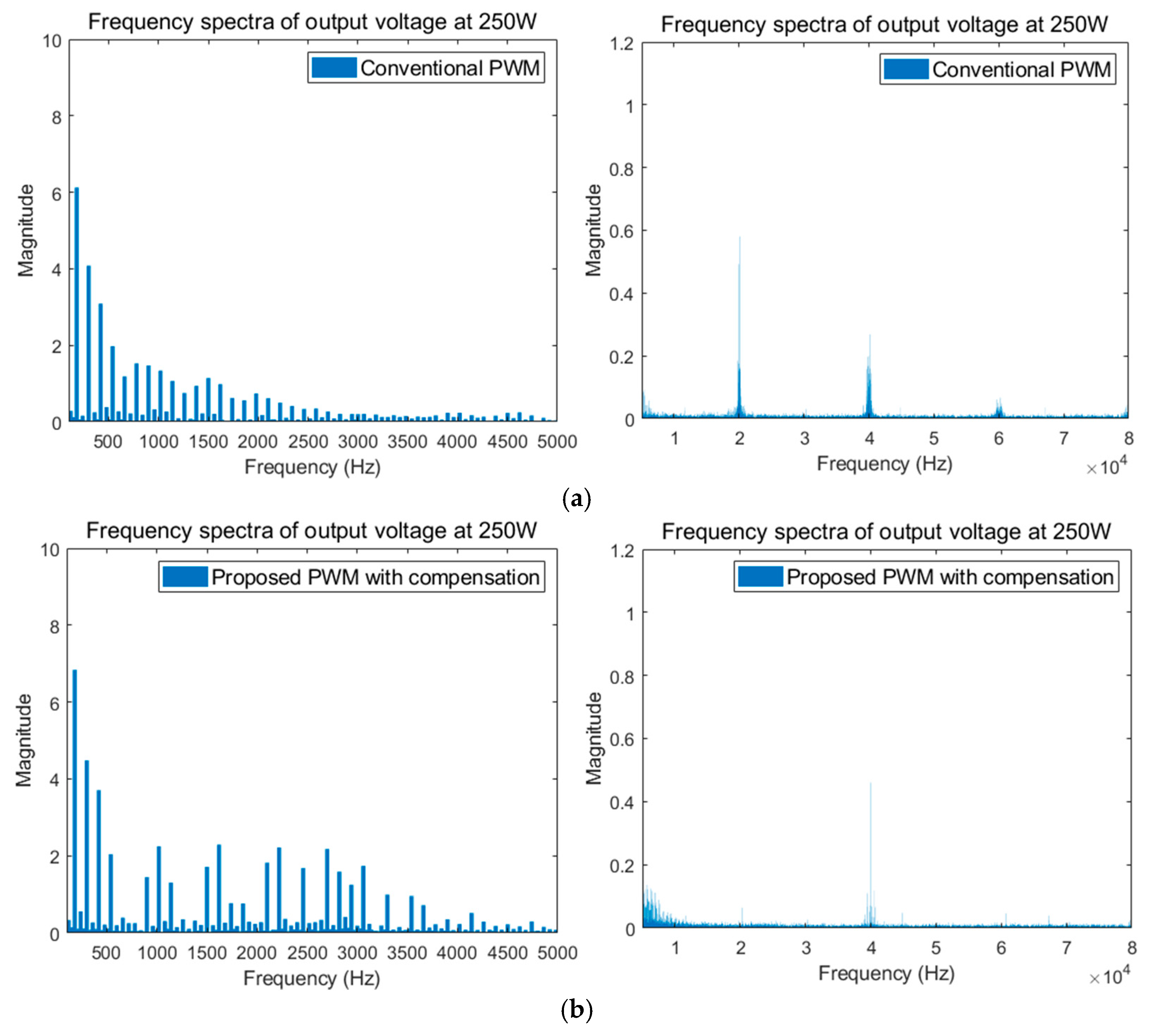

3. Simulation Results

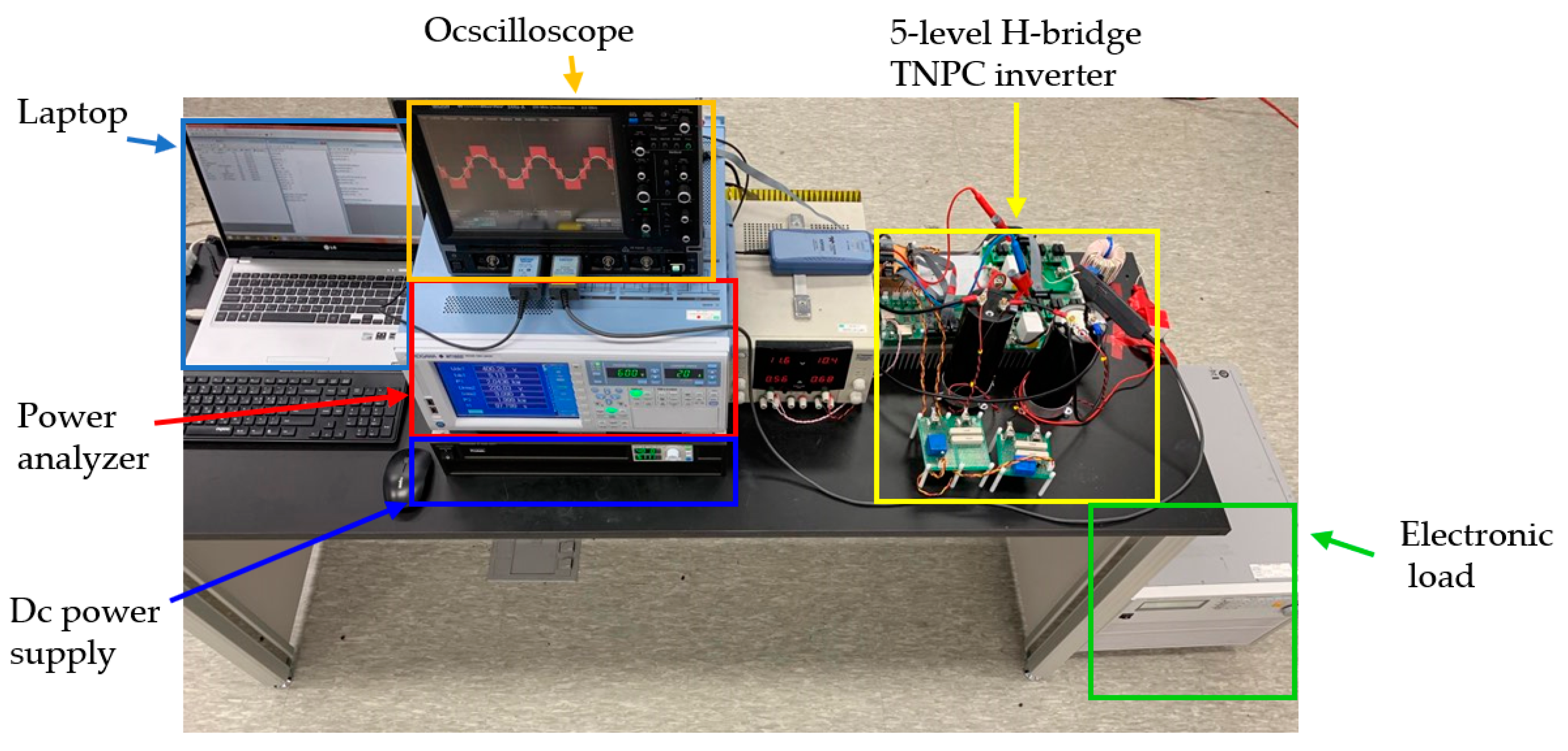

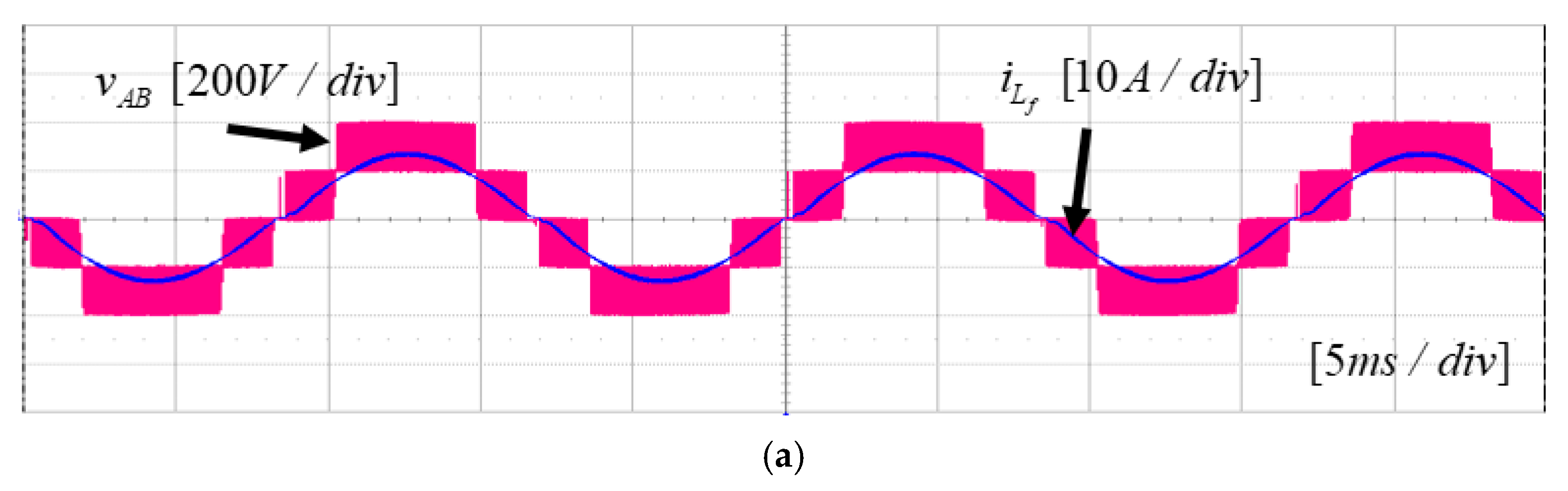

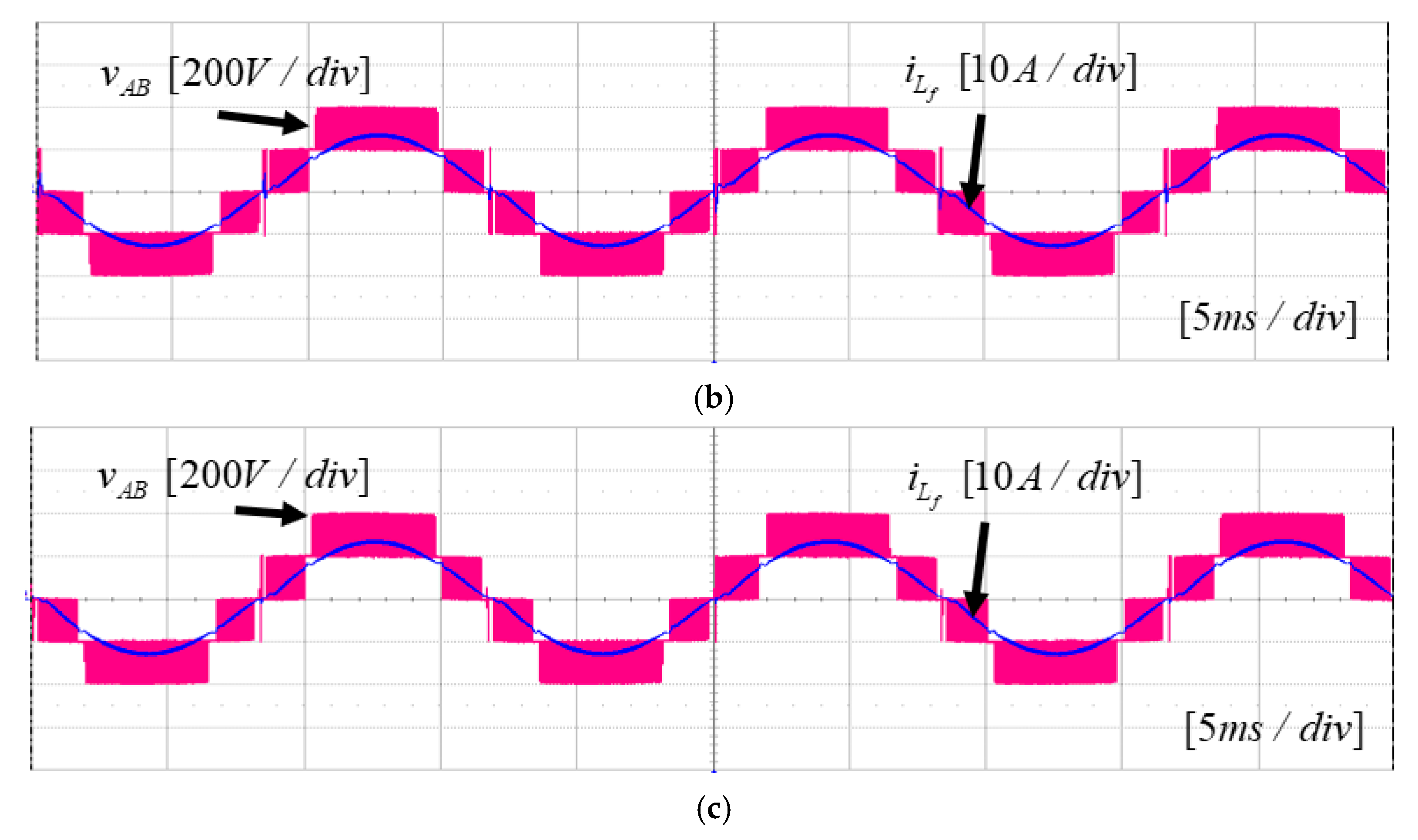

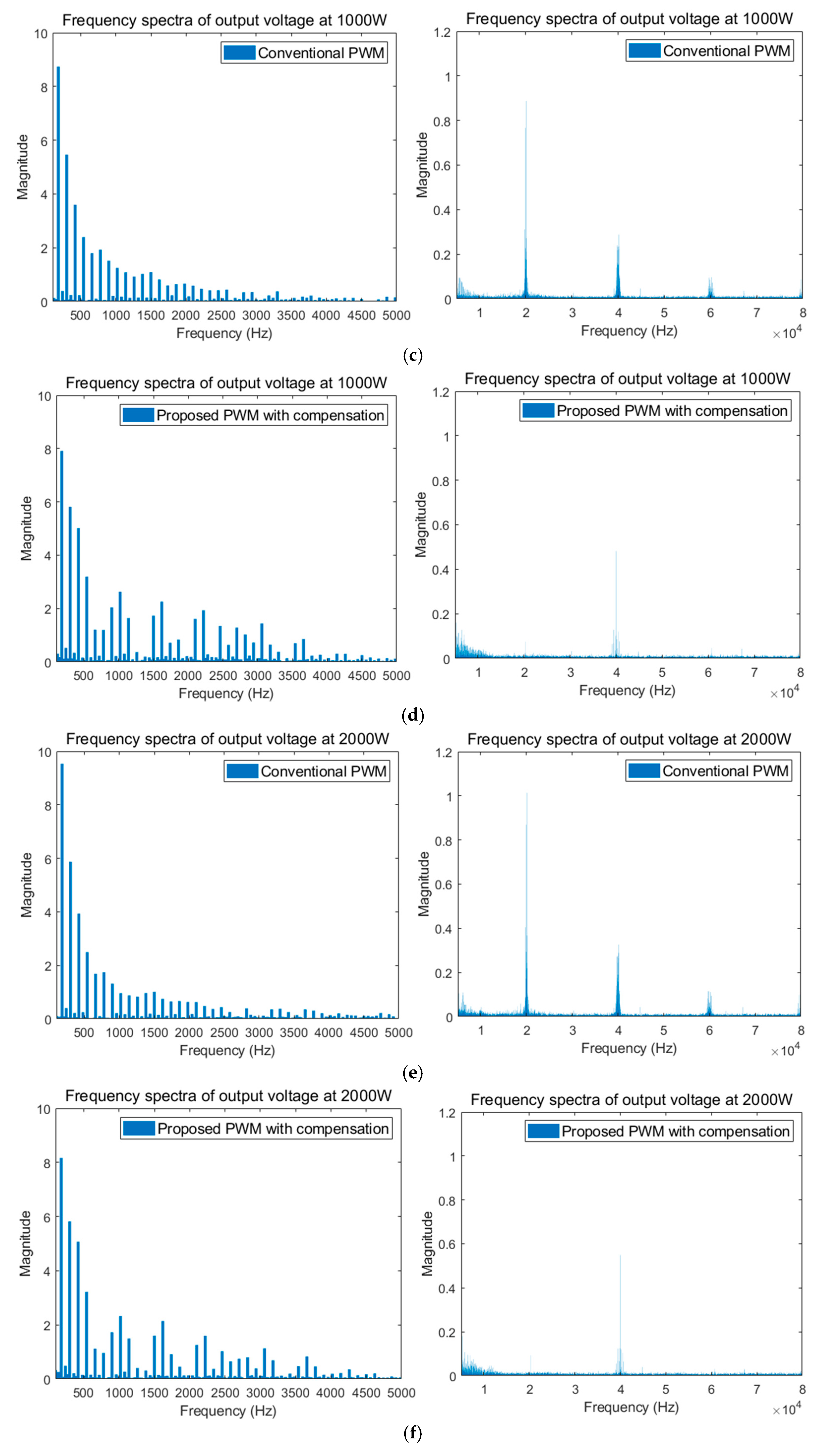

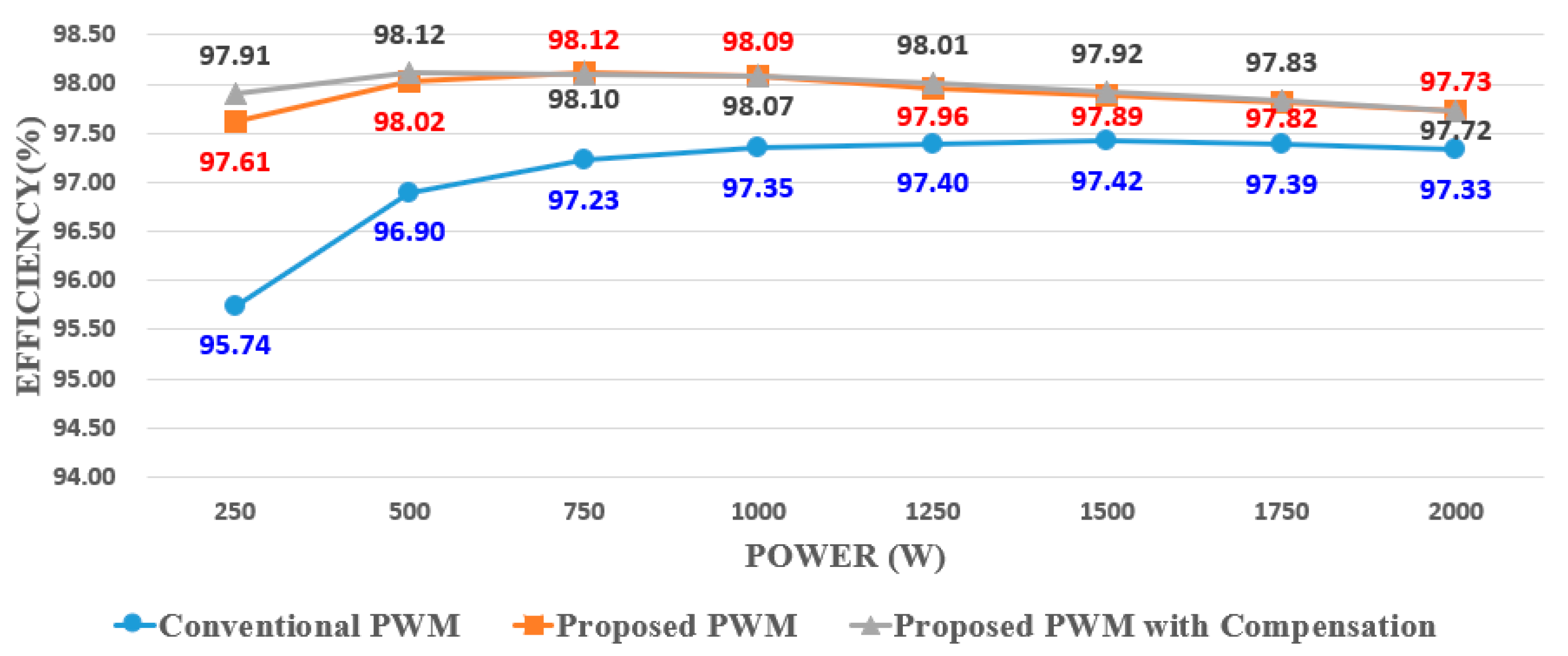

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Okamoto, T.; Ishida, Y.; Kato, Y.; Miyazaki, S. Development of low voltage 2 level IGBT inverter and converter for industrial applications. In Proceedings of the 8th International Conference on Power Electronics—ECCE Asia, Jeju, Korea, 30 May–3 June 2011; pp. 2466–2473. [Google Scholar]

- Luo, C.; Wang, X.; Jiang, T.; Feng, R.; Xin, H.; Li, H. Experimental study of a SiC MOSFET based single phase inverter in UPS applications. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6. [Google Scholar]

- Wang, R.; Wang, F.; Boroyevich, D.; Burgos, R.; Lai, R.; Ning, P.; Rajashekara, K. A High Power Density Single-Phase PWM Rectifier with Active Ripple Energy Storage. IEEE Trans. Power Electron. 2011, 26, 1430–1443. [Google Scholar] [CrossRef]

- Golestan, S.; Monfared, M.; Freijedo, F.D.; Guerrero, J.M. Design and Tuning of a Modified Power-Based PLL for Single-Phase Grid-Connected Power Conditioning Systems. IEEE Trans. Power Electron. 2012, 27, 3639–3650. [Google Scholar] [CrossRef]

- Bojoi, R.I.; Limongi, L.R.; Roiu, D.; Tenconi, A. Enhanced Power Quality Control Strategy for Single-Phase Inverters in Distributed Generation Systems. IEEE Trans. Power Electron. 2011, 26, 798–806. [Google Scholar] [CrossRef]

- Dasgupta, S.; Sahoo, S.K.; Panda, S.K. Single-Phase Inverter Control Techniques for Interfacing Renewable Energy Sources with Microgrid—Part I: Parallel-Connected Inverter Topology with Active and Reactive Power Flow Control Along with Grid Current Shaping. IEEE Trans. Power Electron. 2011, 26, 717–731. [Google Scholar] [CrossRef]

- Dasgupta, S.; Sahoo, S.K.; Panda, S.K.; Amaratunga, G.A.J. Single-Phase Inverter-Control Techniques for Interfacing Renewable Energy Sources with Microgrid—Part II: Series-Connected Inverter Topology to Mitigate Voltage-Related Problems Along with Active Power Flow Control. IEEE Trans. Power Electron. 2011, 26, 732–746. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Ahmed, M.; Mekhilef, S. A three-phase three-level voltage source inverter with a three-phase two-level inverter as a main circuit. In Proceedings of the 2008 4th IET Conference on Power Electronics, Machines and Drives, York, UK, 2–4 April 2008; pp. 640–644. [Google Scholar]

- Hinga, P.K.; Ohnishi, T.; Suzuki, T. A new PWM inverter for photovoltaic power generation system. In Proceedings of the 1994 Power Electronics Specialist Conference (PESC’94), Taipei, Taiwan, 20–25 June 1994; Volume 391, pp. 391–395. [Google Scholar]

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Dodo, Y.; Sato, Y.; Ito, T.; Mochidate, S. A study for improvement in power density of flying capacitor multilevel inverters for grid-connected applications. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 469–473. [Google Scholar]

- Ji, S.; Reusch, D.; Lee, F.C. High-Frequency High Power Density 3-D Integrated Gallium-Nitride-Based Point of Load Module Design. IEEE Trans. Power Electron. 2013, 28, 4216–4226. [Google Scholar] [CrossRef]

- Kotecha, R.M.; Zhang, Y.; Rashid, A.; Vrotsos, T.; Mantooth, H.A. A physics-based compact device model for GaN HEMT power devices. In Proceedings of the 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Fayetteville, AR, USA, 7–9 November 2016; pp. 108–113. [Google Scholar]

- Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J.; Costinett, D. Understanding the limitations and impact factors of wide bandgap devices’ high switching-speed capability in a voltage source converter. In Proceedings of the 2014 IEEE Workshop on Wide Bandgap Power Devices and Applications, Knoxville, TN, USA, 13–15 October 2014; pp. 7–12. [Google Scholar]

- Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Wang, F.F.; Zhang, Z. Overview of silicon carbide technology: Device, converter, system, and application. CPSS Trans. Power Electron. Appl. 2016, 1, 13–32. [Google Scholar] [CrossRef]

- Funaki, T.; Sasagawa, M.; Nakamura, T. Multi-chip SiC DMOSFET half-bridge power module for high temperature operation. In Proceedings of the 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Orlando, FL, USA, 5–9 February 2012; pp. 2525–2529. [Google Scholar]

- Agelidis, V.G.; Baker, D.M.; Lawrance, W.B.; Nayar, C.V. A multilevel PWM inverter topology for photovoltaic applications. In Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE’97), Guimaraes, Portugal, 7–11 July 1997; Volume 582, pp. 589–594. [Google Scholar]

- Valderrama, G.E.; Guzman, G.V.; Pool-Mazún, E.I.; Martinez-Rodriguez, P.R.; Lopez-Sanchez, M.J.; Zuñiga, J.M.S. A Single-Phase Asymmetrical T-Type Five-Level Transformerless PV Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 140–150. [Google Scholar] [CrossRef]

- Liu, L. Mixed single-phase three-level NPC inverter with hybrid modulation technology. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 2873–2880. [Google Scholar]

- Yang, J.H.; Le, T.V.; Ibadullaev, A.; Park, S.J. A study of TNPC type single-phase 5-level inverter for energy storage system. In Proceedings of the 2016 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC Asia-Pacific), Busan, Korea, 1–4 June 2016; pp. 346–350. [Google Scholar]

- Drofenik, U.; Kolar, J.W. A general scheme for calculating switching-and conduction-losses of power semiconductors in numerical circuit simulations of power electronic systems. In Proceedings of the 2005 International Power Electronics Conference (IPEC’05), Niigata, Japan, 4–8 April 2005; pp. 4–8. [Google Scholar]

| Parameters | Description | Parameters | Description |

|---|---|---|---|

| Dc-link capacitor voltage | Output voltage of the inverter | ||

| Voltage between pole A and neutral point | Voltage between pole B and neutral point | ||

| Voltage reference | Switching device “x” | ||

| Modulation index | Phase of the voltage reference | ||

| Phase for current distortion compensation |

| Polarity of | Switching Function | Output Voltage | State |

|---|---|---|---|

| (0, 0, 1, 1, 0, 0, 1, 1) | 0 | A-1 | |

| (1, 0, 0, 1, 0, 0, 1, 1) | A-2 | ||

| (0, 0, 1, 1, 0, 1, 1, 0) | A-3 | ||

| (1, 0, 0, 1, 0, 1, 1, 0) | A-4 | ||

| (0, 0, 1, 1, 0, 0, 1, 1) | 0 | A-5 | |

| (0, 1, 1, 0, 0, 0, 1, 1) | A-6 | ||

| (0, 0, 1, 1, 1, 0, 0, 1) | A-7 | ||

| (0, 1, 1, 0, 1, 0, 0, 1) | A-8 |

| Polarity of | Switching Function | Output Voltage | State |

|---|---|---|---|

| (0, 1, 1, 0, 0, 1, 1, 0) | 0 | B-1 | |

| (0, 0, 1, 1, 0, 1, 1, 0) | B-2 | ||

| (1, 0, 0, 1, 0, 1, 1, 0) | B-3 | ||

| (1, 0, 0, 1, 1, 0, 0, 1) | 0 | B-4 | |

| (0, 0, 1, 1, 1, 0, 0, 1) | B-5 | ||

| (0, 1, 1, 0, 1, 0, 0, 1) | B-6 |

| Parameters | Description | Values |

|---|---|---|

| Total dc-link capacitance | 1800 μF | |

| Inductance of output filter | 1 mH | |

| Capacitance of output filter | 2 μF | |

| Dc-link capacitor voltage | 400 V | |

| Rms value of output voltage | 220 V | |

| Rated power of the inverter | 2 kW | |

| Switching frequency of the conventional PWM strategy | 20 kHz | |

| Switching frequency of the proposed PWM strategy | 40 kHz |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, T.; Bu, H.; Cho, Y. Hybrid PWM Strategy for Power Efficiency Improvement of 5-Level TNPC Inverter and Current Distortion Compensation Method. Electronics 2019, 8, 76. https://doi.org/10.3390/electronics8010076

Lee T, Bu H, Cho Y. Hybrid PWM Strategy for Power Efficiency Improvement of 5-Level TNPC Inverter and Current Distortion Compensation Method. Electronics. 2019; 8(1):76. https://doi.org/10.3390/electronics8010076

Chicago/Turabian StyleLee, Taeyeong, Hanyoung Bu, and Younghoon Cho. 2019. "Hybrid PWM Strategy for Power Efficiency Improvement of 5-Level TNPC Inverter and Current Distortion Compensation Method" Electronics 8, no. 1: 76. https://doi.org/10.3390/electronics8010076

APA StyleLee, T., Bu, H., & Cho, Y. (2019). Hybrid PWM Strategy for Power Efficiency Improvement of 5-Level TNPC Inverter and Current Distortion Compensation Method. Electronics, 8(1), 76. https://doi.org/10.3390/electronics8010076