A High-Efficiency Low-Power Chip-Based CMOS Liquid Crystal Driver for Tunable Electro-Optic Eyewear

Abstract

1. Introduction

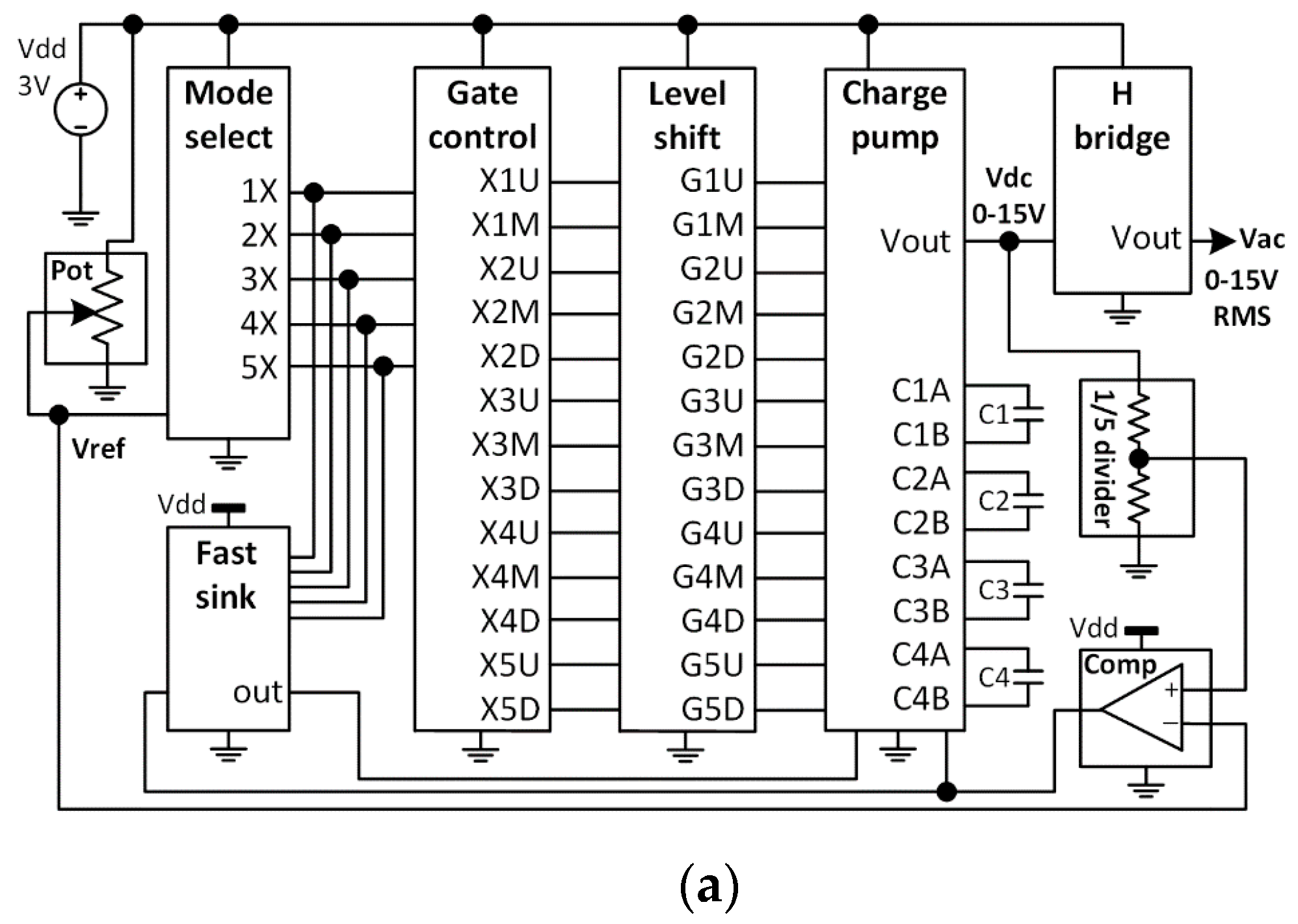

2. LC Device Driver Design

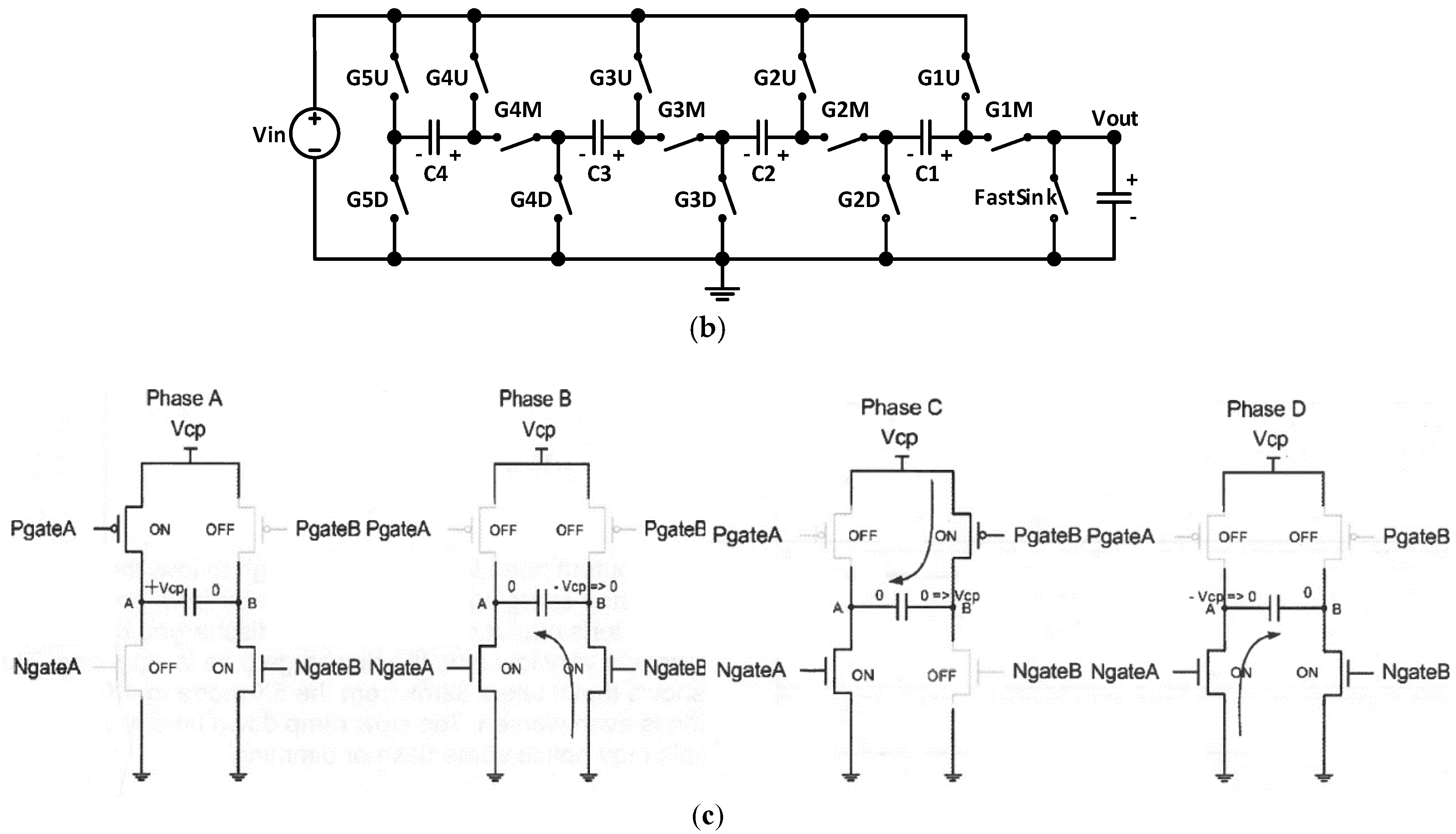

3. Design Features and Simulation Results

3.1. Bang-Bang Closed-Loop Output Regulator

3.2. Low-Power H-Bridge Inverter

3.3. Fast Charge Sinker

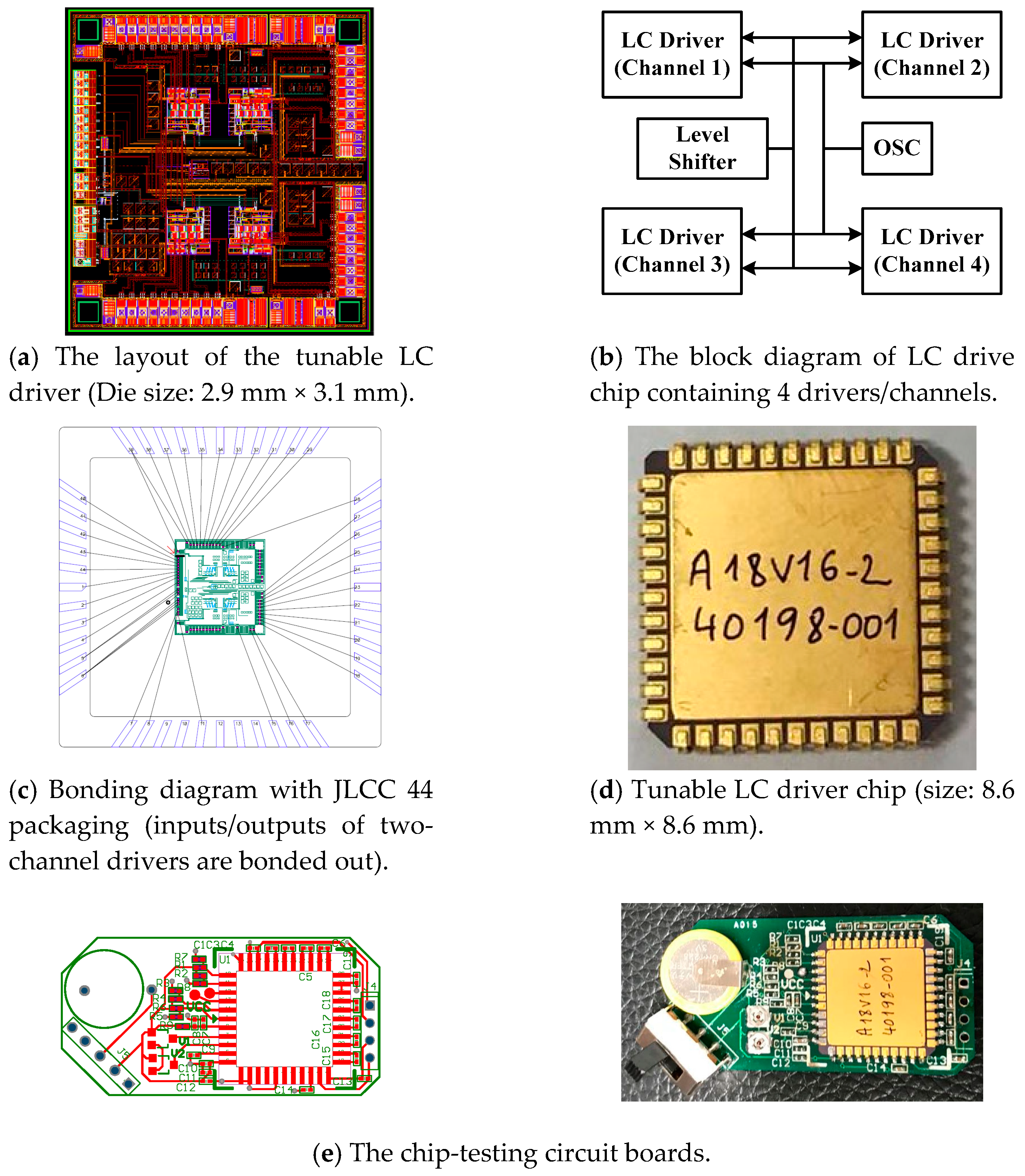

3.4. System Opitmization and Simulations

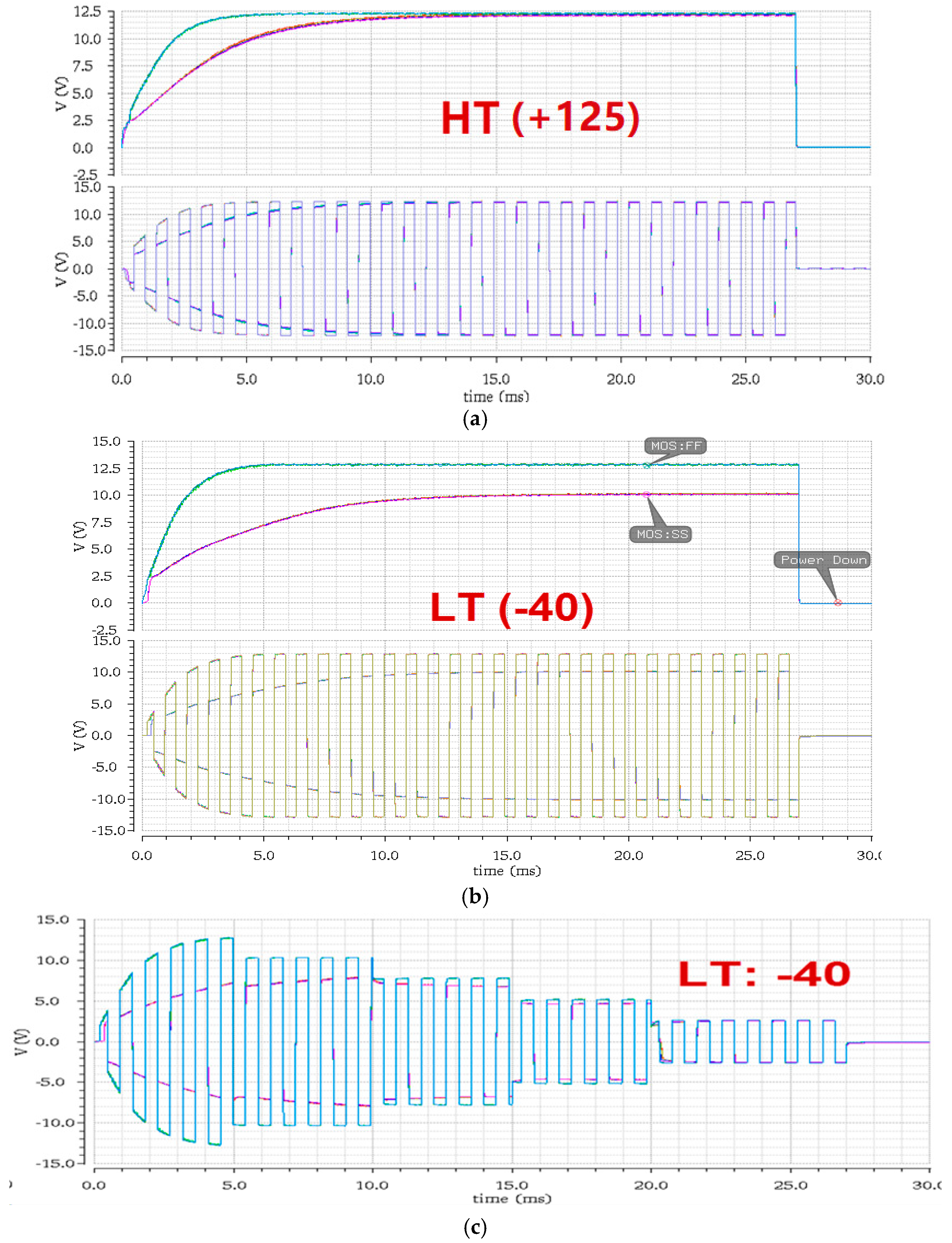

4. Implementation and Testing Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Li, G. Adaptive lens. Prog. Opt. 2010, 55, 199–283. [Google Scholar]

- Bailey, J.; Morgan, P.B.; Gleeson, H.F.; Jones, J.C. Switchable liquid crystal contact lenses for the correction of presbyopia. Crystals 2018, 8, 29. [Google Scholar] [CrossRef]

- Li, G.; Han, Z.; Lan, G. Adaptive Electro-optic lenses for vision correction and assessment, and eye imaging. Investig. Ophthalmol. Vis. Sci. 2012, 53, 3584. [Google Scholar]

- Riza, N.A.; Admin, M.J.; Riza, M.N. Eye vision testing system and eyewear using micromachines. Micromachines 2015, 6, 1690–1709. [Google Scholar] [CrossRef]

- Li, G. Adaptive electro-optic occluder with variable transmission and contrast. Investig. Ophthalmol. Vis. Sci. 2018, 59, 4124. [Google Scholar]

- Kramida, G. Resolving the vergence-accommodation conflict in head-mounted displays. IEEE Trans. Vis. Comput. Graph. 2016, 22, 1912–1931. [Google Scholar] [CrossRef]

- Suyama, S.; Date, M.; Takada, H. Three-dimensional display system with dual-frequency liquid-crystal varifocal lens. Jpn. J. Appl. Phys. 2000, 39, 480–484. [Google Scholar] [CrossRef]

- Wang, Y.J.; Chen, P.-J.; Liang, X.; Lin, Y. Augmented reality with image registration, vision correction and sunlight readability via liquid crystal devices. Sci. Rep. 2017, 7, 433. [Google Scholar] [CrossRef]

- Love, G.D.; Hoffman, D.M.; Hands, P.J.W.; Gao, J.; Kirby, A.K.; Banks, M.S. High-speed switchable lens enables the development of a volumetric stereoscopic display. Opt. Express 2009, 17, 15716–15725. [Google Scholar] [CrossRef]

- Yamaguchi, M. Full-parallax holographic light-field 3-D displays and ınteractive 3-D touch. Proc. IEEE 2017, 105, 947–959. [Google Scholar] [CrossRef]

- Lan, G.; Li, G. Design of high-performance adaptive objective lens with large optical depth scanning range for ultrabroad near infrared microscopic imaging. Biomed. Opt. Express 2015, 6, 3362–3377. [Google Scholar] [CrossRef] [PubMed]

- Li, G.; Penmatsa, V. Large-aperture harmonic diffractive adaptive liquid crystal lens for vision care. In Proceedings of the Bio-Optics: Design and Application (BODA) 2015, Vancouver, BC, Canada, 12–15 April 2015. [Google Scholar]

- Li, G.; Mathine, D.L.; Valley, P.; Äyräs, P.; Haddock, J.; Giridhar, M.S.; Schwiegerling, J.; Meredith, G.; Kippelen, B.; Honkanen, S.; et al. Switchable electro-optic diffractive lens with high efficiency for ophthalmic applications. Proc. Natl. Acad. Sci. USA 2006, 103, 6100–6104. [Google Scholar] [CrossRef] [PubMed]

- Li, G.; Valley, P.; Ayras, P.; Mathine, D.L.; Honkanen, S.; Peyghambarian, N. High-efficiency switchable flat diffractive ophthalmic lens with three-layer electrode pattern and two-layer via structures. Appl. Phys. Lett. 2007, 90, 111005. [Google Scholar] [CrossRef]

- Li, G.; Valley, P.; Giridhar, M.S.; Mathine, D.; Meredith, G.; Haddock, J.; Kippelen, B.; Peyghambarian, N. Large-aperture switchable thin diffractive lens with interleaved electrode pattern. Appl. Phys. Lett. 2006, 89, 141120. [Google Scholar] [CrossRef]

- Pan, F.; Samaddar, T. Charge Pump Circuit Design, 1st ed.; McGraw-Hill Education: New York, NY, USA, 2006. [Google Scholar]

- Feigl, S. Latest results on the HV-CMOS pixel sensor in the AMS H18 process. In Proceedings of the 2015 IEEE Sensors Conference, Busan, Korea, 1–4 November 2015. [Google Scholar]

- Musunuri, S.; Chapman, P.L.; Zou, J.; Liu, C. Design issues for monolithic DC-DC converters. IEEE Trans. Power Electron. 2005, 20, 639–649. [Google Scholar] [CrossRef]

- Eberle, W.; Zhang, Z.; Liu, Y.; Sen, P. A practical switching loss model for buck voltage regulators. IEEE Trans. Power Electron. 2009, 24, 700–713. [Google Scholar] [CrossRef]

- Aloisi, W.; Palumbo, G. Efficiency model of boost DC-DC PWM converters. Int. J. Circuit Theory Appl. 2005, 33, 419–432. [Google Scholar] [CrossRef]

- Hasan, A.; Gregori, S. Modeling of step-up DC-DC converters to formulate design guidelines for optimization. In Proceedings of the IEEE Canadian Conference on Electrical and Computer Engineering (CCECE), Quebec, QC, Canada, 3–6 May 2009; pp. 911–915. [Google Scholar]

- Greco, N.; Spina, N.; Fiore, V.; Ragonese, E.; Palmisano, G. A galvanically isolated DC-DC converter based on current-reuse hybrid-coupled oscillators. IEEE Trans. Circuits Syst. II 2017, 64, 56–60. [Google Scholar] [CrossRef]

- Liou, W.; Lin, S.C.; Lin, C.Y.; Sun, C.H. Monolithic low-EMI CMOS DC-DC boost converter for portable applications. IEEE Trans. VLSI Syst. 2014, 22, 420–424. [Google Scholar] [CrossRef]

- Mitrovic, N.; Enne, R.; Zimmermann, H. An integrated current sensing circuit with comparator function for a buck DC-DC converter in HV-CMOS. In Proceedings of the 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, Monaco, 11–14 December 2016. [Google Scholar]

- Tanzawa, T.; Tanaka, T. A dynamic analysis of the Dickson charge pump circuit. IEEE J. Solid-State Circuits 1997, 20, 1231–1240. [Google Scholar] [CrossRef]

- Wens, M.; Cornelissens, K.; Steyaert, M. A fully-integrated 0.18 mm CMOS DC-DC step-up converter, using a bondwire spiral inductor. In Proceedings of the IEEE European Solid-State Circuits Conference (ESSCIRC), Munich, Germany, 11–13 September 2007; pp. 268–271. [Google Scholar]

- Kossov, O. Comparative analysis of chopper voltage regulators with LC filter. IEEE Trans. Magn. 1968, 4, 712–715. [Google Scholar] [CrossRef]

- Du, S.; Liu, J.; Lin, J.; He, Y. A novel DC voltage control method for STATCOM based on hybrid multilevel H-bridge converter. IEEE Trans. Power Electron. 2013, 28, 101–111. [Google Scholar] [CrossRef]

- Sepahvand, H.; Liao, J.; Ferdowsi, M.; Corzine, K.A. Capacitor voltage regulation in single-DC-source cascaded H-bridge multilevel converters using phase-shift modulation. IEEE Trans. Ind. Electron. 2013, 60, 3619–3626. [Google Scholar] [CrossRef]

- Shaltout, A.; Gregori, S. Design trade-offs of integrated polygonal inductors for DC-DC power converters. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Baltimore, MD, USA, 28–31 May 2017; pp. 1–4. [Google Scholar]

- Cuk, S. A new zero-ripple switching DC-to-DC converter and integrated magnetics. IEEE Trans. Magn. 1983, 19, 57–75. [Google Scholar] [CrossRef]

- Grebene, A. Bipolar and MOS Analog Integrated Circuit Design; Wiley: Hoboken, NJ, USA, 2003. [Google Scholar]

- Baker, R.J. CMOS Circuit Design, Layout, and Simulation; Wiley IEEE Press: Hoboken, NJ, USA, 2010. [Google Scholar]

- Reinhard, D. Introduction to Integrated Circuit Engineering; Houghton Mifflin Co.: Boston, MA, USA, 1987. [Google Scholar]

- Cadence Design Systems. Available online: https://www.cadence.com/ (accessed on 8 November 2018).

- Annual Report—CMP: Circuits Multi-Projets. 2016. Available online: https://mycmp.fr/IMG/pdf/cmp_annualreport_2016.pdf (accessed on 8 November 2018).

- Li, G. Adaptive Lens for Vision Correction. U.S. Patent 8,587,734 B2, 8 March 2010. International Patent WO 102295A1, 8 March 2010. [Google Scholar]

- Khan, M.; Islam, M.; Deng, H. Design of a Re-configurable RFID Sensing Tag as a Generic Sensing Platform (GSP) Towards the Future Internet of Things (IoT). IEEE Internet Things J. 2014, 1, 300–310. [Google Scholar] [CrossRef]

- Khan, M.; Deng, H. Design and Prototyping a Smart Deep Brain Stimulator: An Autonomous Neuro-Sensing and Stimulating Electrode System. IEEE Intell. Syst. 2017, 32, 14–27. [Google Scholar] [CrossRef]

| VREF (DC) | Selected Mode | VAC (RMS) |

|---|---|---|

| 0.0 V < VREF ≤ 0.6 V | 1× | 0 V < VAC ≤ 3 V |

| 0.6 V < VREF ≤ 1.2 V | 2× | 3 V < VAC ≤ 6 V |

| 1.2 V < VREF ≤ 1.8 V | 3× | 6 V < VAC ≤ 9 V |

| 1.8 V < VREF ≤ 2.4 V | 4× | 9 V < VAC ≤ 12 V |

| 2.4 V < VREF ≤ 3.0 V | 5× | 12 V < VAC ≤ 15 V |

| Transistor | Charging Phase | Discharging Phase | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Mode | 1× | 2× | 3× | 4× | 5× | 1× | 2× | 3× | 4× | 5× |

| G1U | X | X | X | X | X | X | - | - | - | - |

| G1M | X | - | - | - | - | X | X | X | X | X |

| G2U | - | - | X | X | X | - | X | - | - | - |

| G2M | - | - | - | - | - | - | X | X | X | X |

| G2D | - | X | X | X | X | - | - | - | - | - |

| G3U | - | - | - | X | X | - | - | X | - | - |

| G3M | - | - | - | - | - | - | - | X | X | X |

| G3D | - | - | X | X | X | - | - | - | - | - |

| G4U | - | - | - | - | X | - | - | - | X | - |

| G4M | - | - | - | - | - | - | - | - | X | X |

| G4D | - | - | - | X | X | - | - | - | - | - |

| G5U | - | - | - | - | - | - | - | - | - | X |

| G5D | - | - | - | - | X | - | - | - | - | - |

| Parameter | Min | Typical | Max | Unit |

|---|---|---|---|---|

| Input voltage source | 2.7 | 3.0 | 3.3 | V |

| charge pump (CP) output | 0 | - | 15.0 | V |

| Working temperature | −40 | 23 | 125 | °C |

| Output frequency | - | 1 k | - | Hz |

| CP rump-up time | - | 3.2 | - | ms |

| CP rump-down time | - | 62.0 | - | µs |

| Total power consumption | - | 3.5 | - | mW |

| Power consumption per channel | - | 1.6 | - | mW |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Deng, H.; Li, G. A High-Efficiency Low-Power Chip-Based CMOS Liquid Crystal Driver for Tunable Electro-Optic Eyewear. Electronics 2019, 8, 14. https://doi.org/10.3390/electronics8010014

Deng H, Li G. A High-Efficiency Low-Power Chip-Based CMOS Liquid Crystal Driver for Tunable Electro-Optic Eyewear. Electronics. 2019; 8(1):14. https://doi.org/10.3390/electronics8010014

Chicago/Turabian StyleDeng, Hai, and Guoqiang Li. 2019. "A High-Efficiency Low-Power Chip-Based CMOS Liquid Crystal Driver for Tunable Electro-Optic Eyewear" Electronics 8, no. 1: 14. https://doi.org/10.3390/electronics8010014

APA StyleDeng, H., & Li, G. (2019). A High-Efficiency Low-Power Chip-Based CMOS Liquid Crystal Driver for Tunable Electro-Optic Eyewear. Electronics, 8(1), 14. https://doi.org/10.3390/electronics8010014