A Linearized Open-Loop MDAC with Memory Effect Compensation Technique for High-Speed Pipelined ADC Stage

Abstract

1. Introduction

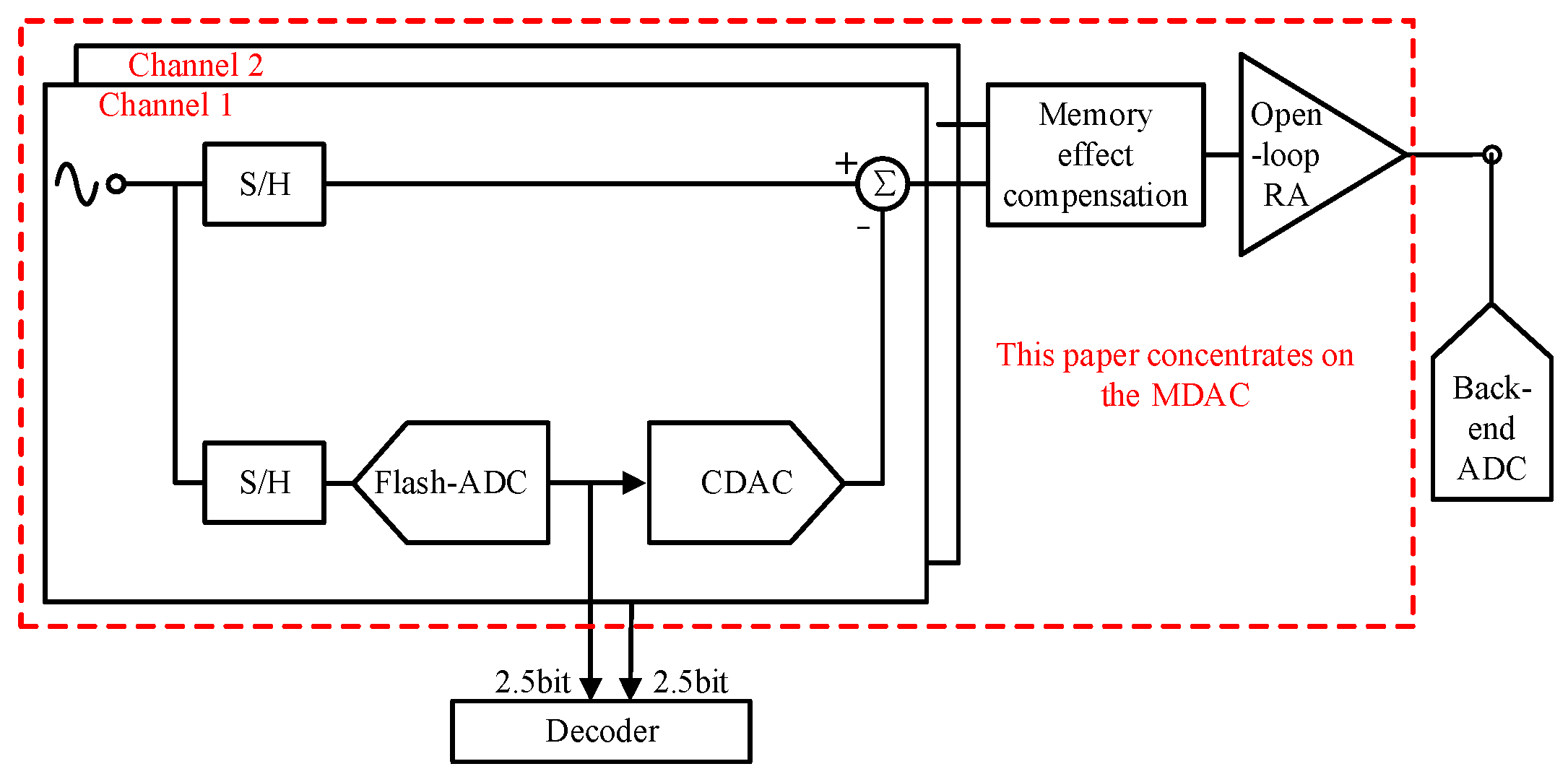

2. Architecture of the Proposed Pipelined ADC Stage

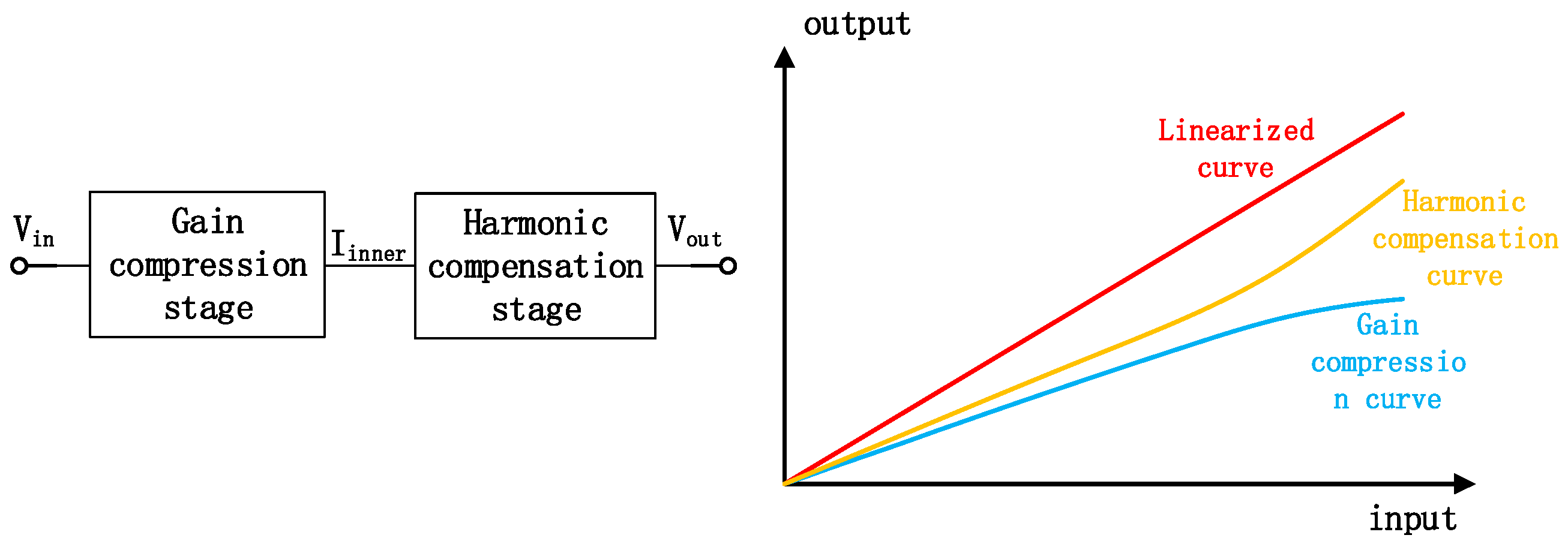

3. The Open-Loop Amplifier Linearized Through Harmonic Compensation

3.1. Performance Limitation of MDAC

3.2. Amplifier Linearity Analysis

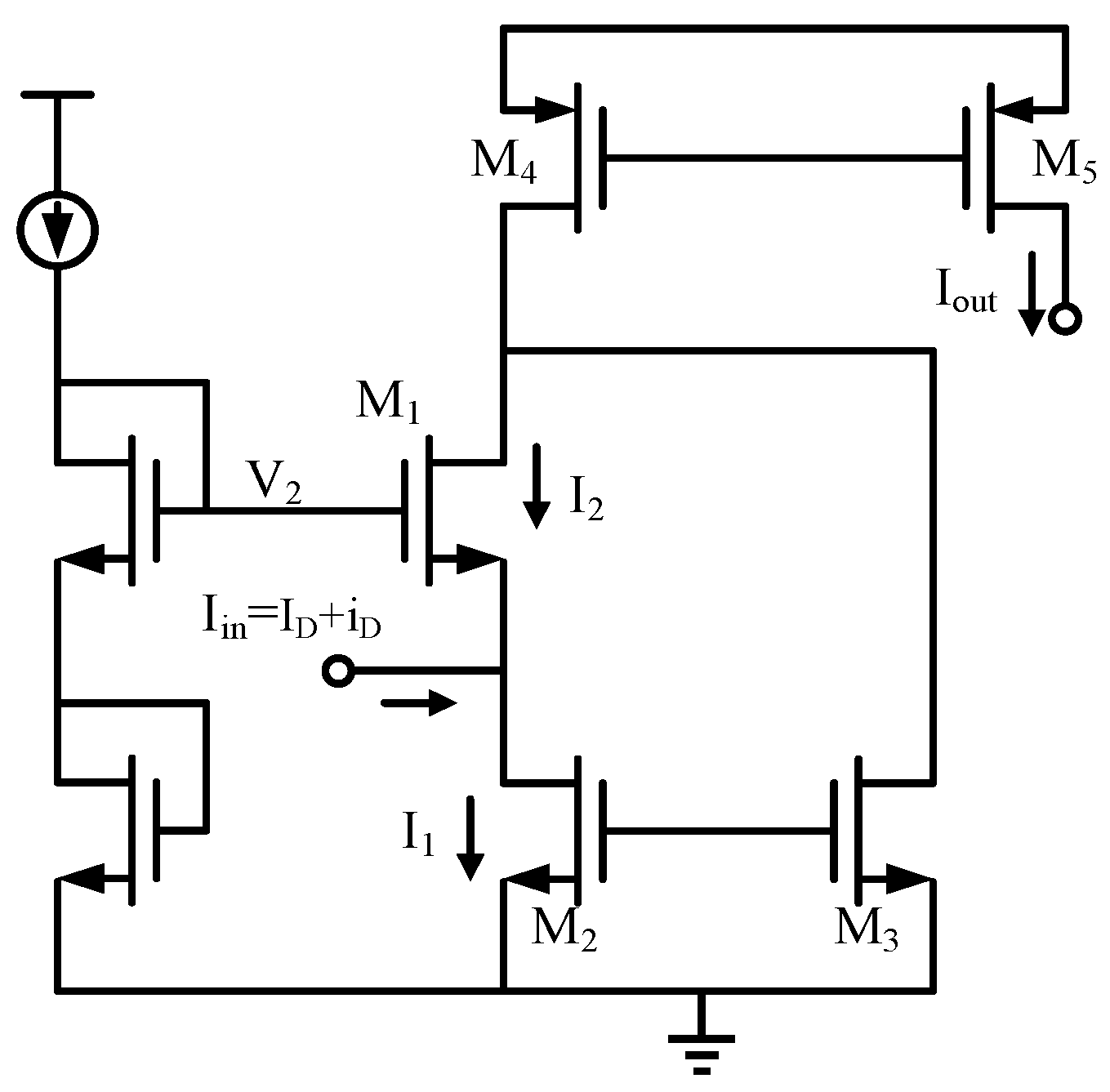

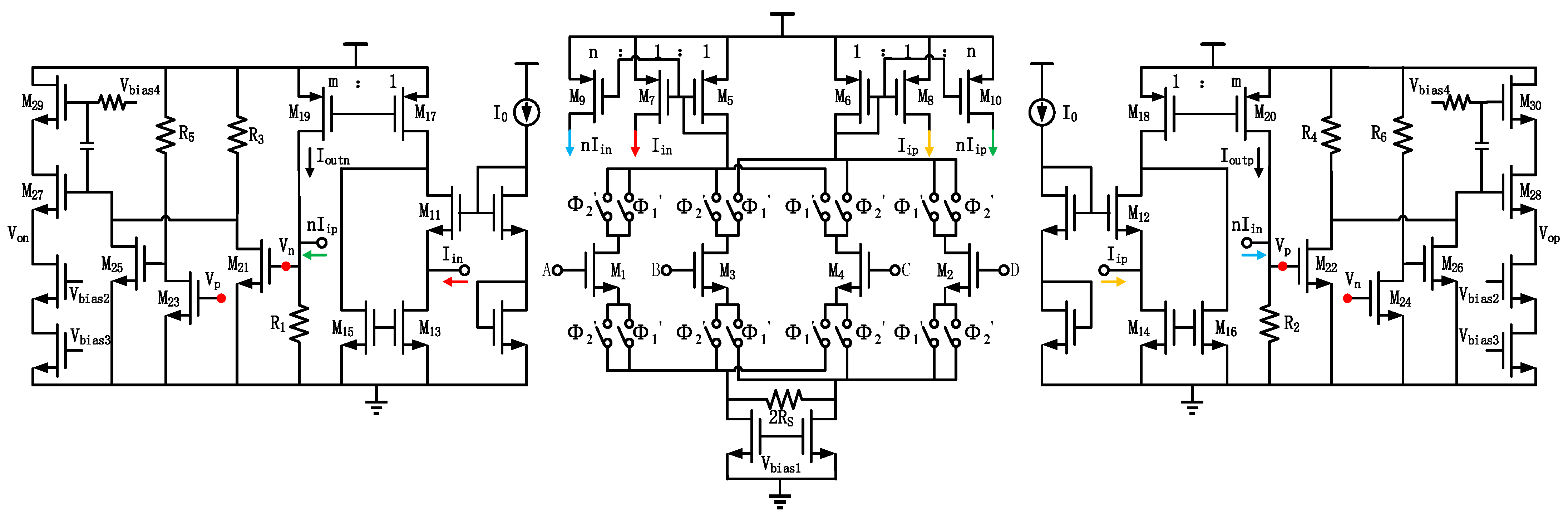

3.3. Current-Mode Harmonic Compensation Circuit Design

3.4. First-Stage Amplifier

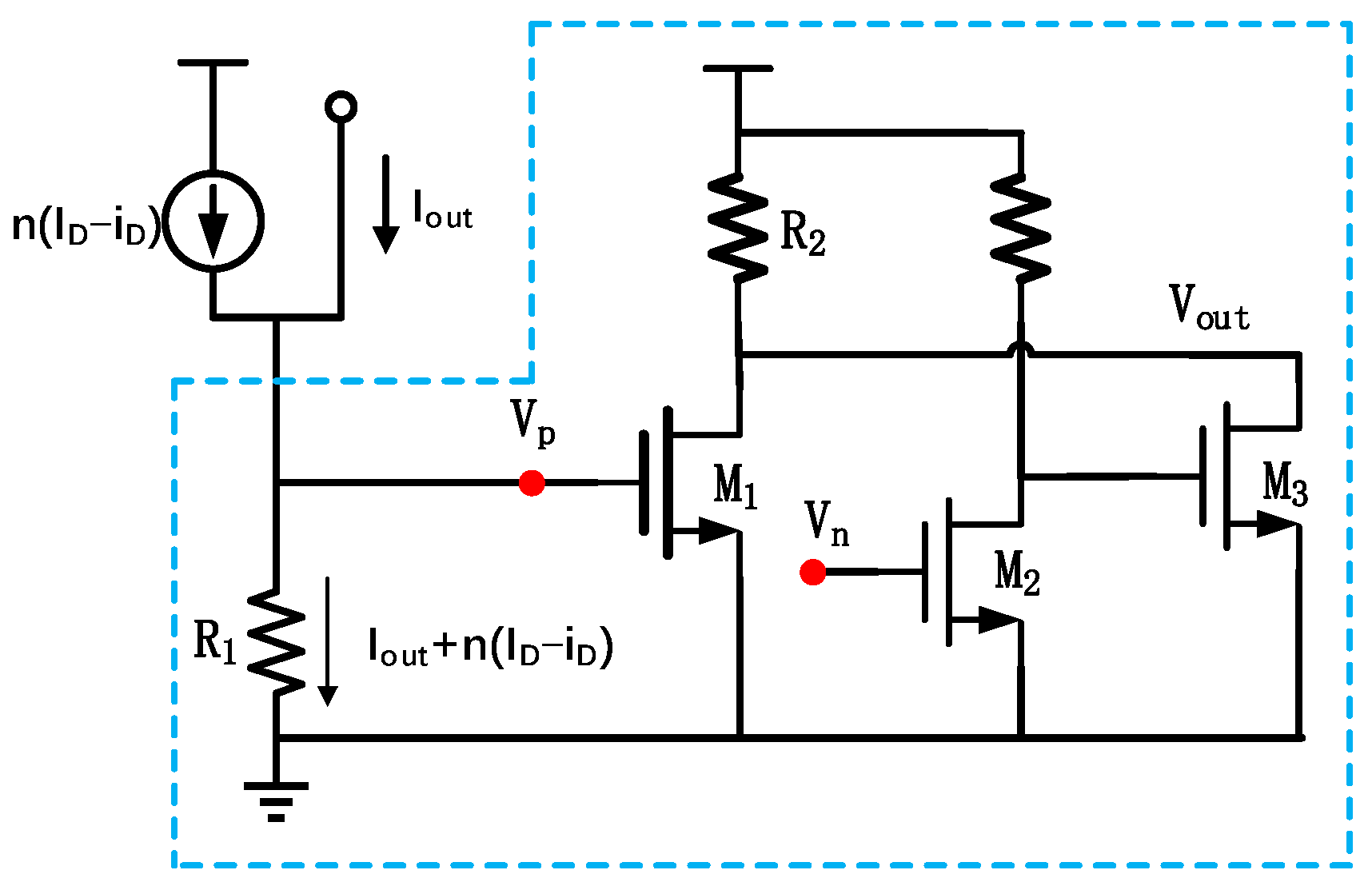

3.5. Open-Loop Amplifier with Current-Mode Harmonic Compensation

4. Memory Effect Compensation

4.1. Memory Effect Analysis

4.2. Memory Effect Compensation Scheme

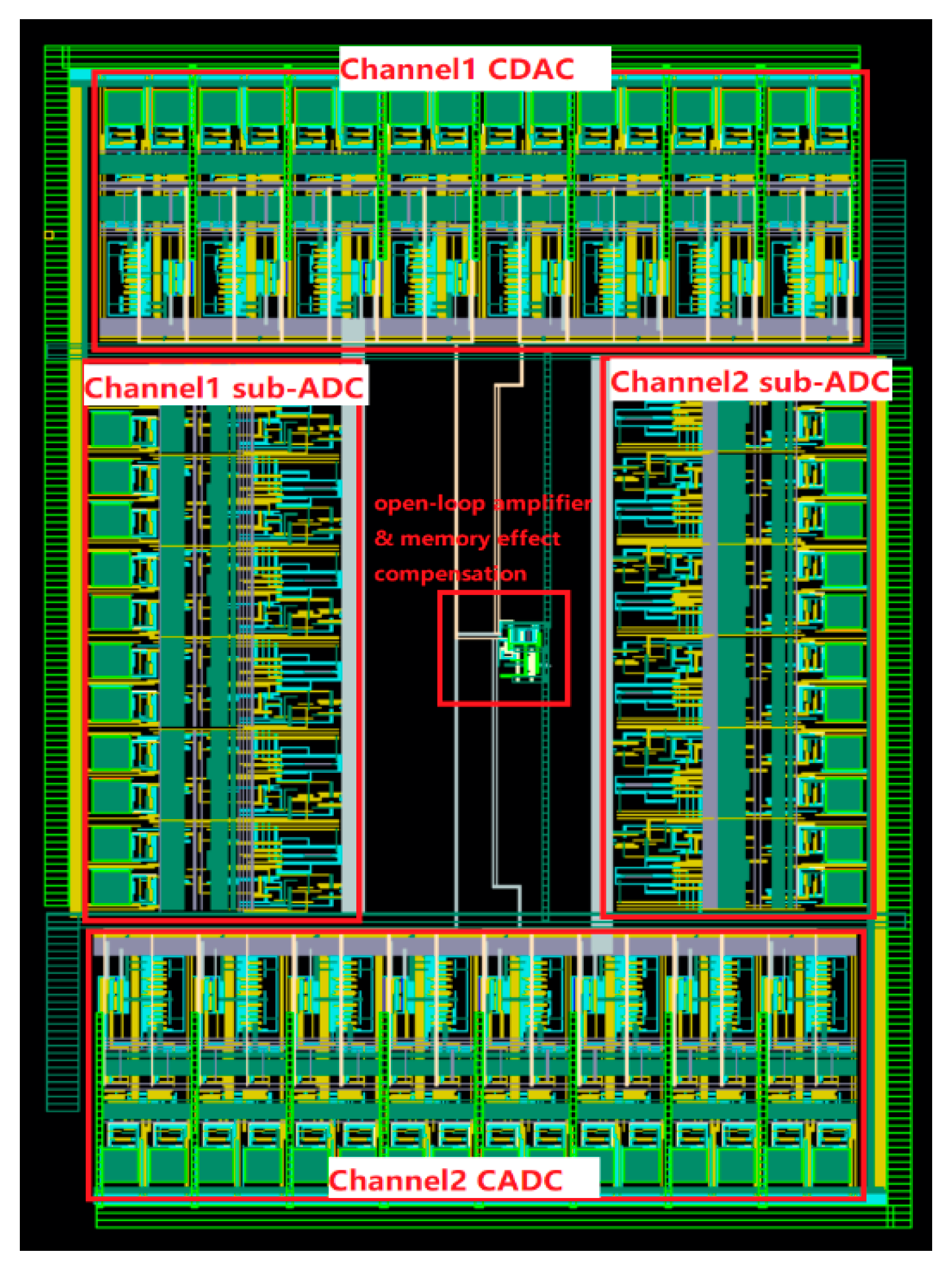

5. Simulation Results

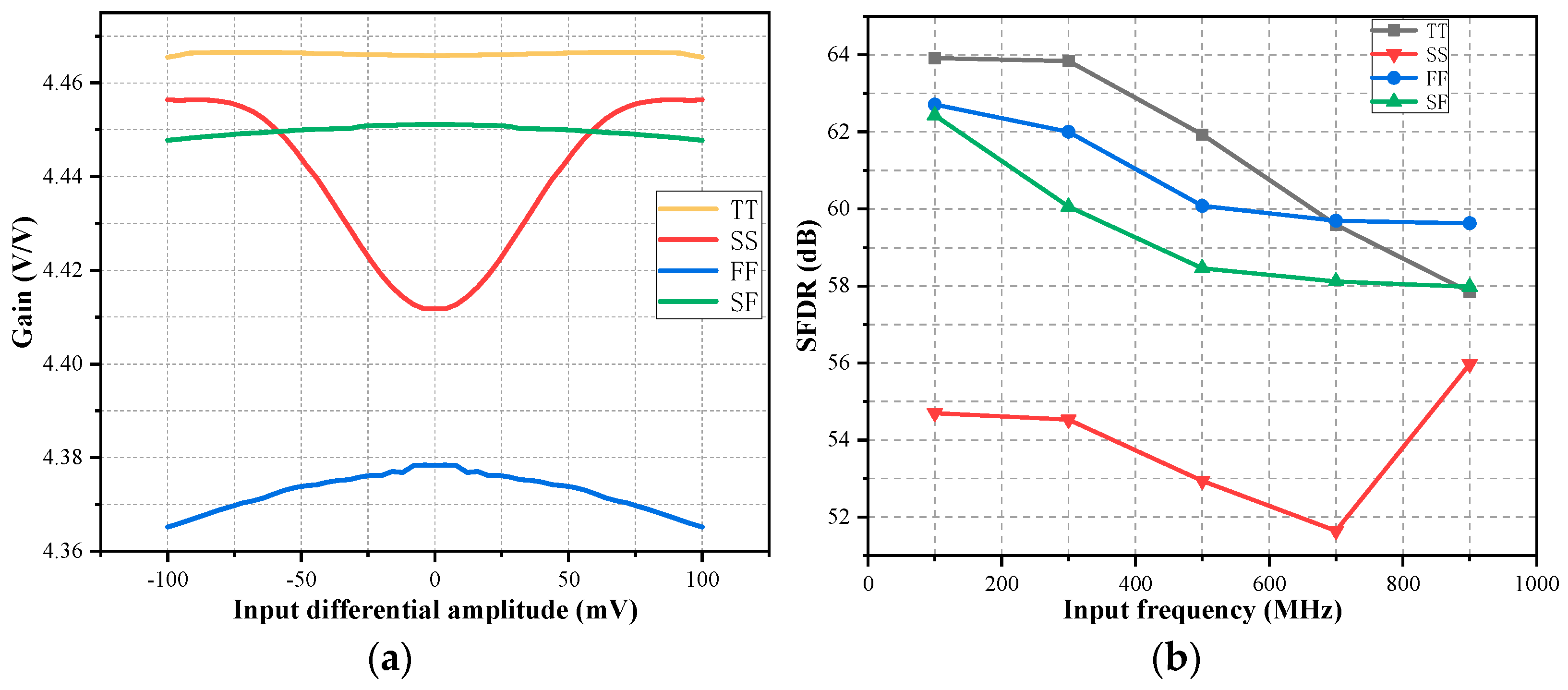

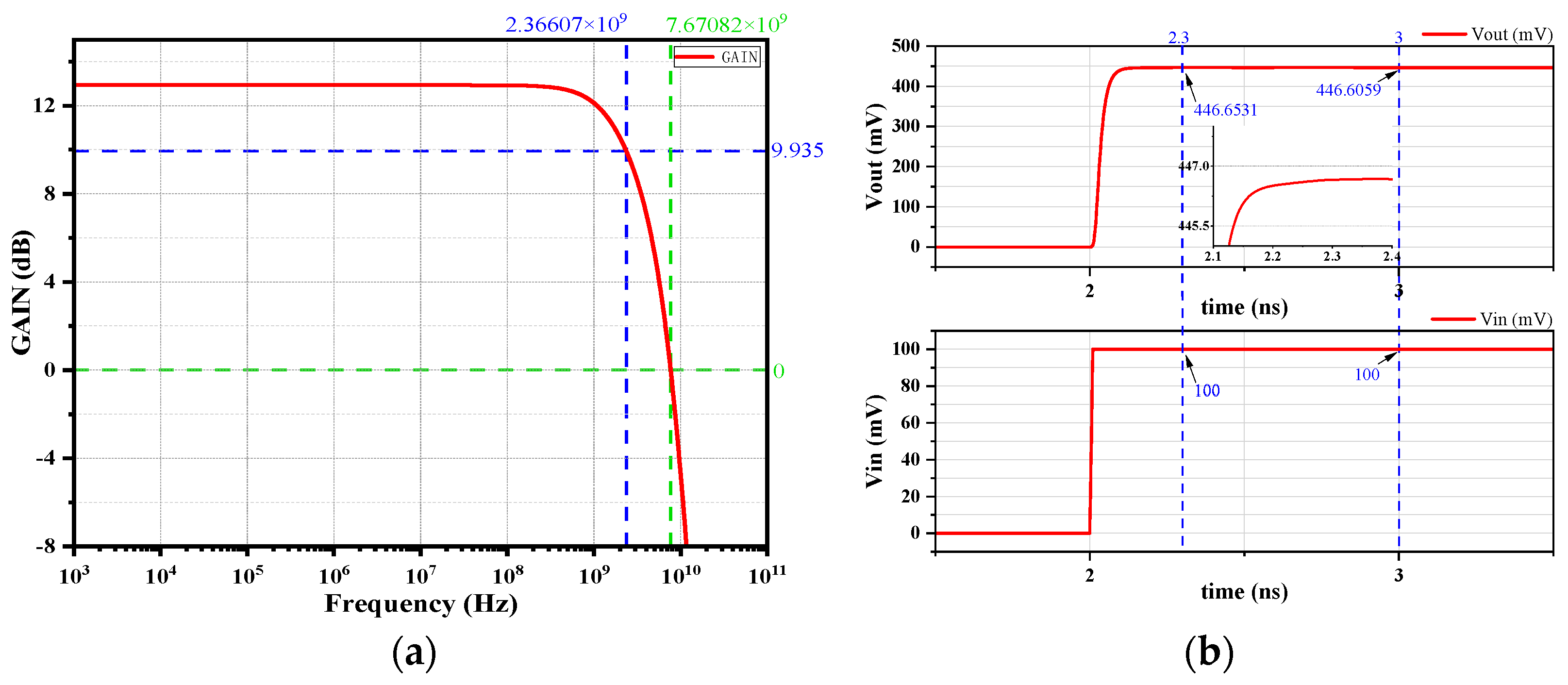

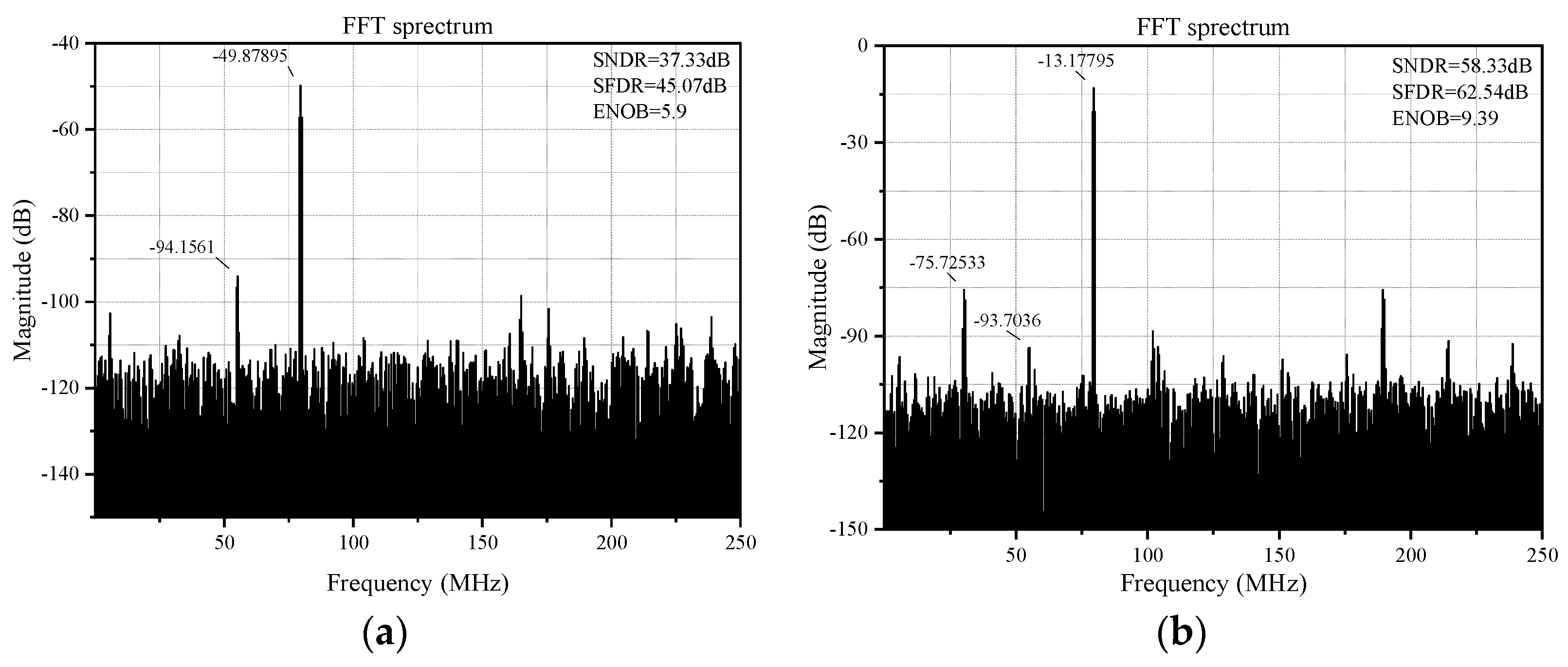

5.1. Simulation Results of the Open-Loop Amplifier

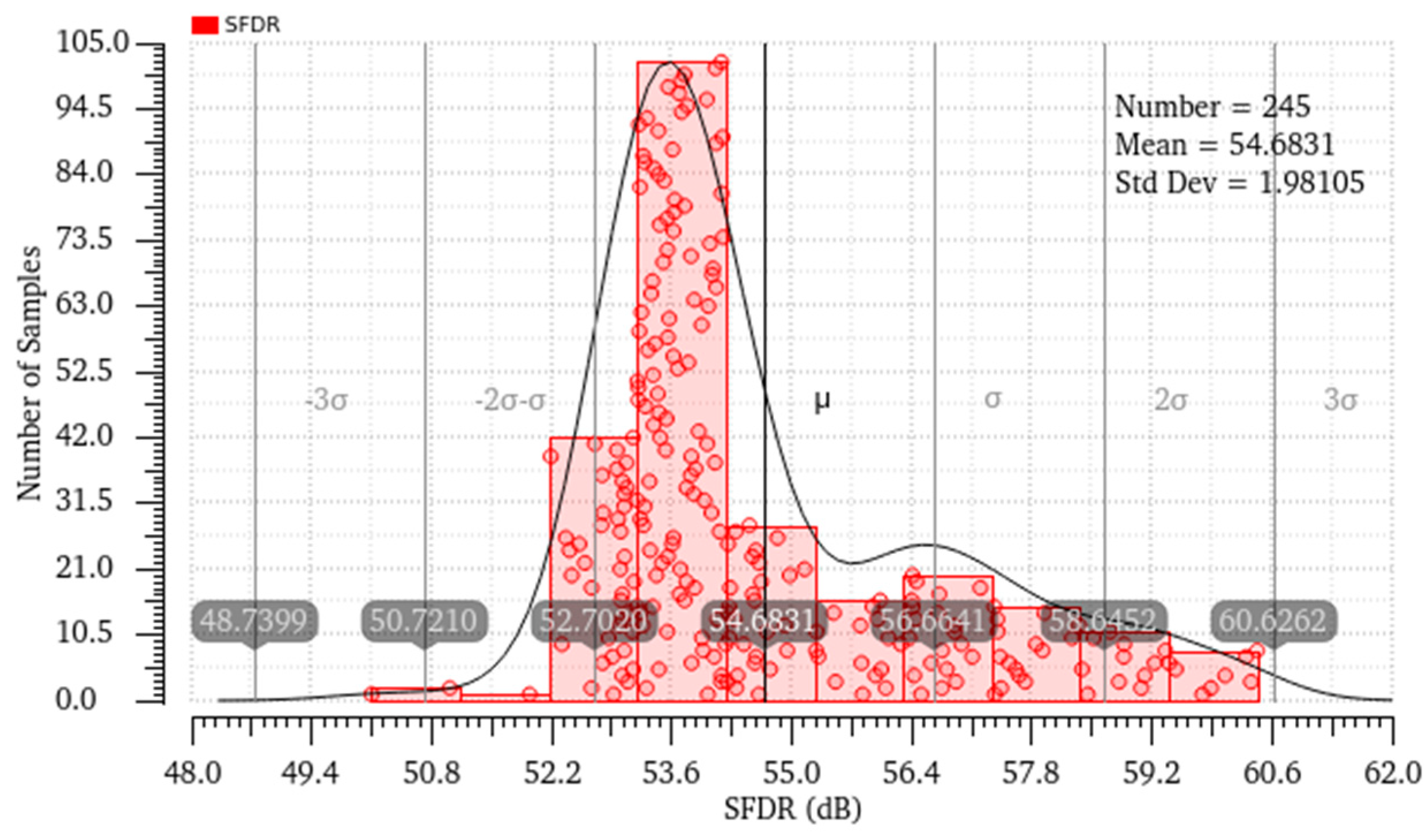

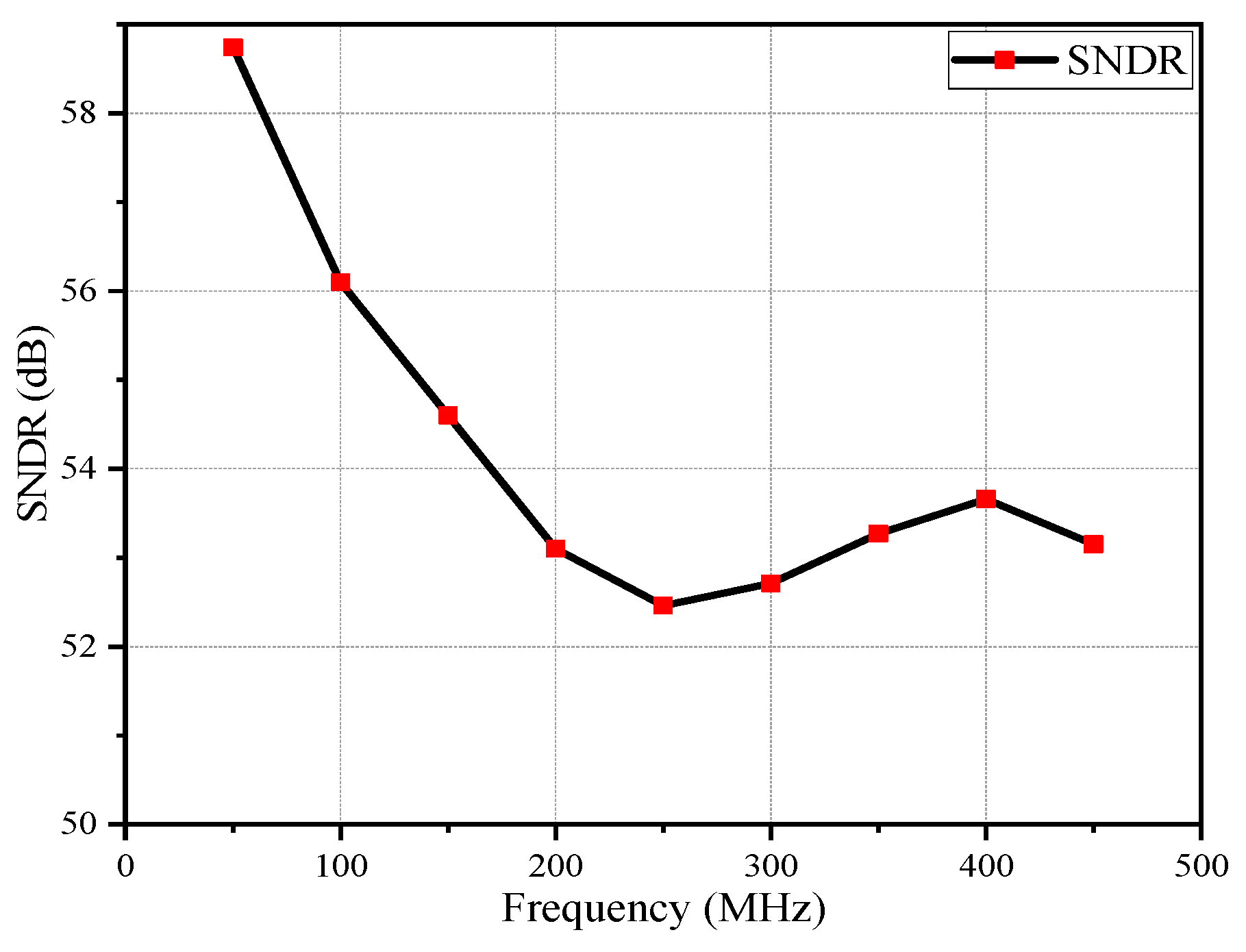

5.2. Simulation Results of the Memory Effect Compensation Circuit

5.3. Simulation Results Comparison

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Liu, M.; Li, D.; Zhu, Z. A Dual-Supply Two-Stage CMOS Op-amp for High-Speed Pipeline ADCs Application. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 650–654. [Google Scholar] [CrossRef]

- Feng, X.; Ma, S.; Zou, M.; Wu, T. A High Gain and Wide Bandwidth Dual-Power CMOS Op-amp for High-Speed ADCs Application. In Proceedings of the 2023 IEEE 15th International Conference on ASIC (ASICON), Nanjing, China, 24–27 October 2023; pp. 1–4. [Google Scholar] [CrossRef]

- Liu, Y.; Shen, Y.; Chen, M.; Xu, H.; Chen, X.; Liu, J.; Wang, Z.; Yu, F. A Single-Stage Gain-Boosted Cascode Amplifier with Three-Layer Cascode Feedback Amplifier for Front-End SHA in High-Linearity Pipelined ADC. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2024, 33, 47–51. [Google Scholar] [CrossRef]

- Zhang, C.; Wei, J.; Yang, Y.; Liu, M. A 12-bit 1.25 GS/s RF sampling pipelined ADC using a bandwidth-expanded residue amplifier with bias-free gain-boost technique. Microelectron. J. 2022, 130, 105611. [Google Scholar] [CrossRef]

- Lagos, J.; Hershberg, B.; Martens, E.; Wambacq, P.; Craninckx, J. A Single-Channel, 600-MS/s, 12-b, Ringamp-Based Pipelined ADC in 28-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 403–416. [Google Scholar] [CrossRef]

- Lagos, J.; Hershberg, B.; Martens, E.; Wambacq, P.; Craninckx, J. A 1Gsps, 12-bit, single-channel pipelined ADC with dead-zone-degenerated ring amplifiers. In Proceedings of the 2018 IEEE Custom Integrated Circuits Conference (CICC), San Diego, CA, USA, 8–11 April 2018; pp. 1–4. [Google Scholar]

- Zhang, H.; He, B.; Guo, X.; Wu, D.; Liu, X. A 1-GS/s 12-bit Single-Channel Pipelined ADC in 28-nm CMOS with Input-Split Fully Differential Ring Amplifier. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2023, 31, 1931–1938. [Google Scholar] [CrossRef]

- Jiang, W.; Zhu, Y.; Zhang, M.; Chan, C.-H.; Martins, R.P. A Temperature-Stabilized Single-Channel 1-GS/s 60-dB SNDR SAR-Assisted Pipelined ADC with Dynamic Gm-R-Based Amplifier. IEEE J. Solid-State Circuits 2019, 55, 322–332. [Google Scholar] [CrossRef]

- Park, Y.; Song, J.; Choi, Y.; Lim, C.; Ahn, S.; Kim, C. An 11-b 100-MS/s Fully Dynamic Pipelined ADC Using a High-Linearity Dynamic Amplifier. IEEE J. Solid-State Circuits 2020, 55, 2468–2477. [Google Scholar] [CrossRef]

- Kim, Y.-H.; Cho, S. A 1-GS/s 9-bit Zero-Crossing-Based Pipeline ADC Using a Resistor as a Current Source. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2570–2579. [Google Scholar] [CrossRef]

- Yu, L.; Miyahara, M.; Matsuzawa, A. A 9-bit 1.8 GS/s 44 mW Pipelined ADC Using Linearized Open-Loop Amplifiers. IEEE J. Solid-State Circuits 2016, 51, 2210–2221. [Google Scholar] [CrossRef]

- Park, C.; Chen, T.; Noh, K.; Zhou, D.; Prakash, S.; Alizadeh, M.N.; Karsilayan, A.I.; Chen, D.; Geiger, R.L.; Silva-Martinez, J. A 12-Bit 125-MS/s 2.5-Bit/Cycle SAR-Based Pipeline ADC Employing a Self-Biased Gain Boosting Amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3618–3629. [Google Scholar] [CrossRef]

- Dias, D.; Goes, J.; Costa, T. A PVT-Robust Open-loop Gm-Ratio ×16 Gain Residue Amplifier for >1 GS/s Pipelined ADCs. In Proceedings of the 2024 IEEE International Symposium on Circuits and Systems (ISCAS), Singapore, 19–22 May 2024; pp. 1–5. [Google Scholar] [CrossRef]

- Wu, C.; Yuan, J. A 12-Bit, 300-MS/s Single-Channel Pipelined-SAR ADC with an Open-Loop MDAC. IEEE J. Solid-State Circuits 2019, 54, 1446–1454. [Google Scholar] [CrossRef]

- Sehgal, R.; Van Der Goes, F.; Bult, K. A 13-mW 64-dB SNDR 280-MS/s Pipelined ADC Using Linearized Integrating Amplifiers. IEEE J. Solid-State Circuits 2018, 53, 1878–1888. [Google Scholar] [CrossRef]

- Bult, K.; Wallinga, H. A class of analog CMOS circuits based on the square-law characteristic of an MOS transistor in saturation. IEEE J. Solid-State Circuits 1987, 22, 357–365. [Google Scholar] [CrossRef]

- Borkar, B.D.; Tijare, A.D. VLSI implementation of current mode analog multiplier. In Proceedings of the 2015 International Conference on Communications and Signal Processing (ICCSP), Melmaruvathur, India, 2–4 April 2015; pp. 0531–0534. [Google Scholar] [CrossRef]

- Naderi, A.; Mojarrad, H.; Ghasemzadeh, H.; Khoei, A.; Hadidi, K. Four-quadrant CMOS analog multiplier based on new current squarer circuit with high-speed. In Proceedings of the IEEE EUROCON 2009, St. Petersburg, Russia, 18–23 May 2009; pp. 282–287. [Google Scholar] [CrossRef]

- Zhong, L.; Cheng, H.; Deng, H. A double sampling S/H circuit for dual-channel pipelined ADC based on op-sharing. In Proceedings of the 2013 International Conference on Anti-Counterfeiting, Security and Identification (ASID), Shanghai, China, 25–27 October 2013; pp. 1–5. [Google Scholar] [CrossRef]

- Kim, H.-J.; An, T.-J.; Myung, S.-M.; Lee, S.-H. Time-Interleaved and Circuit-Shared Dual-Channel 10 b 200 MS/s 0.18 μm CMOS Analog-to-Digital Convertor. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 21, 2206–2213. [Google Scholar] [CrossRef]

- Xia, B.; Valdes-Garcia, A.; Sanchez-Sinencio, E. A 10-bit 44-MS/s 20-mW Configurable Time-Interleaved Pipeline ADC for a Dual-Mode 802.11b/Bluetooth Receiver. IEEE J. Solid-State Circuits 2006, 41, 530–539. [Google Scholar] [CrossRef]

- Devarajan, S.; Singer, L.; Kelly, D.; Pan, T.; Silva, J.; Brunsilius, J.; Rey-Losada, D.; Murden, F.; Speir, C.; Bray, J.; et al. A 12-b 10-GS/s Interleaved Pipeline ADC in 28-nm CMOS Technology. IEEE J. Solid-State Circuits 2017, 52, 3204–3218. [Google Scholar] [CrossRef]

- Sehgal, R.; van der Goes, F.; Bult, K. A 12 b 53 mW 195 MS/s Pipeline ADC with 82 dB SFDR Using Split-ADC Calibration. IEEE J. Solid-State Circuits 2015, 50, 1592–1603. [Google Scholar] [CrossRef]

- Wang, X.; Shi, M.; Li, P.; Liu, J.; Huang, Z.; Chen, C.; Jiang, W. A 10b 1. In 25GS/s Residue Post-Amplified Pipelined-SAR ADC with Supply-and-Temperature Stabilized Open-Loop Residue Amplifier. In Proceedings of the 2023 IEEE International Symposium on Circuits and Systems (ISCAS), Monterey, CA, USA, 21–25 May 2023; pp. 1–5. [Google Scholar] [CrossRef]

- Yu, Q.; Pu, J.; Luo, J.; Huang, Z.; Wu, J.; Zhu, X.; Xiang, F.; Chen, L.; Li, J.; Li, Q.; et al. A 12b 8GS/s Time-Interleaved 2b/cycle Pipelined-SAR ADC with Layout-Customized Bootstrap and Super- Source-Follower Based Open-Loop Residue Amplifier. In Proceedings of the 2022 IEEE Asian Solid-State Circuits Conference (A-SSCC), Taipei, Taiwan, 6–9 November 2022; pp. 1–3. [Google Scholar] [CrossRef]

- Li, N.; Zhang, H.; Liu, B.; Pei, L.; Wang, J.; Qi, H.; Zhang, J.; Wang, X.; Zhang, H. A 10-Bit 500-MS/s Pipelined SAR ADC with Nonlinearity-Compensated Open-Loop Amplifier and Parallel Conversion Through Comparator Reusing. IEEE Trans. Circuits Syst. II Express Briefs 2024, 72, 354–358. [Google Scholar] [CrossRef]

- Fang, L.; Wen, X.; Fu, T.; Gui, P. A 12-Bit 1 GS/s RF Sampling Pipeline-SAR ADC with Harmonic Injecting Cross-Coupled Pair Achieving 7.5 fj/Conv-Step. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 3225–3236. [Google Scholar] [CrossRef]

| [11] | [8] | [14] | [27] | This Work | |

|---|---|---|---|---|---|

| Process | 65 nm | 28 nm | 65 nm | 28 nm | 45 nm |

| Supply (V) | 1.2 | 1 | 1.2 | 0.9 | 1.2 |

| Input amplitude (mV) | 800 | 1200 | 1600 | 1100 | 850 |

| Sampling rate (GS/s) | 1.8 | 1 | 0.3 | 1 | 1.8 |

| Output accuracy of residual amplifier (bit) | 7 | 9 | 7 | 11 | 8 |

| Power | 9.92 mW | 2.5 mW | 8.12 mW | 2.37 mW | 11.24 mW 1 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, J.; Meng, Q.; Guo, S.; Li, G.; Shao, J.; Li, S. A Linearized Open-Loop MDAC with Memory Effect Compensation Technique for High-Speed Pipelined ADC Stage. Electronics 2025, 14, 1753. https://doi.org/10.3390/electronics14091753

Wu J, Meng Q, Guo S, Li G, Shao J, Li S. A Linearized Open-Loop MDAC with Memory Effect Compensation Technique for High-Speed Pipelined ADC Stage. Electronics. 2025; 14(9):1753. https://doi.org/10.3390/electronics14091753

Chicago/Turabian StyleWu, Jie, Qiao Meng, Shaocong Guo, Gaojing Li, Jianxun Shao, and Sha Li. 2025. "A Linearized Open-Loop MDAC with Memory Effect Compensation Technique for High-Speed Pipelined ADC Stage" Electronics 14, no. 9: 1753. https://doi.org/10.3390/electronics14091753

APA StyleWu, J., Meng, Q., Guo, S., Li, G., Shao, J., & Li, S. (2025). A Linearized Open-Loop MDAC with Memory Effect Compensation Technique for High-Speed Pipelined ADC Stage. Electronics, 14(9), 1753. https://doi.org/10.3390/electronics14091753