Wafer-Level Amplitude Equalizer Based on an Integrated Passive Device Process with Two Resonance Points for Wavy In-Band Transmission

Abstract

1. Introduction

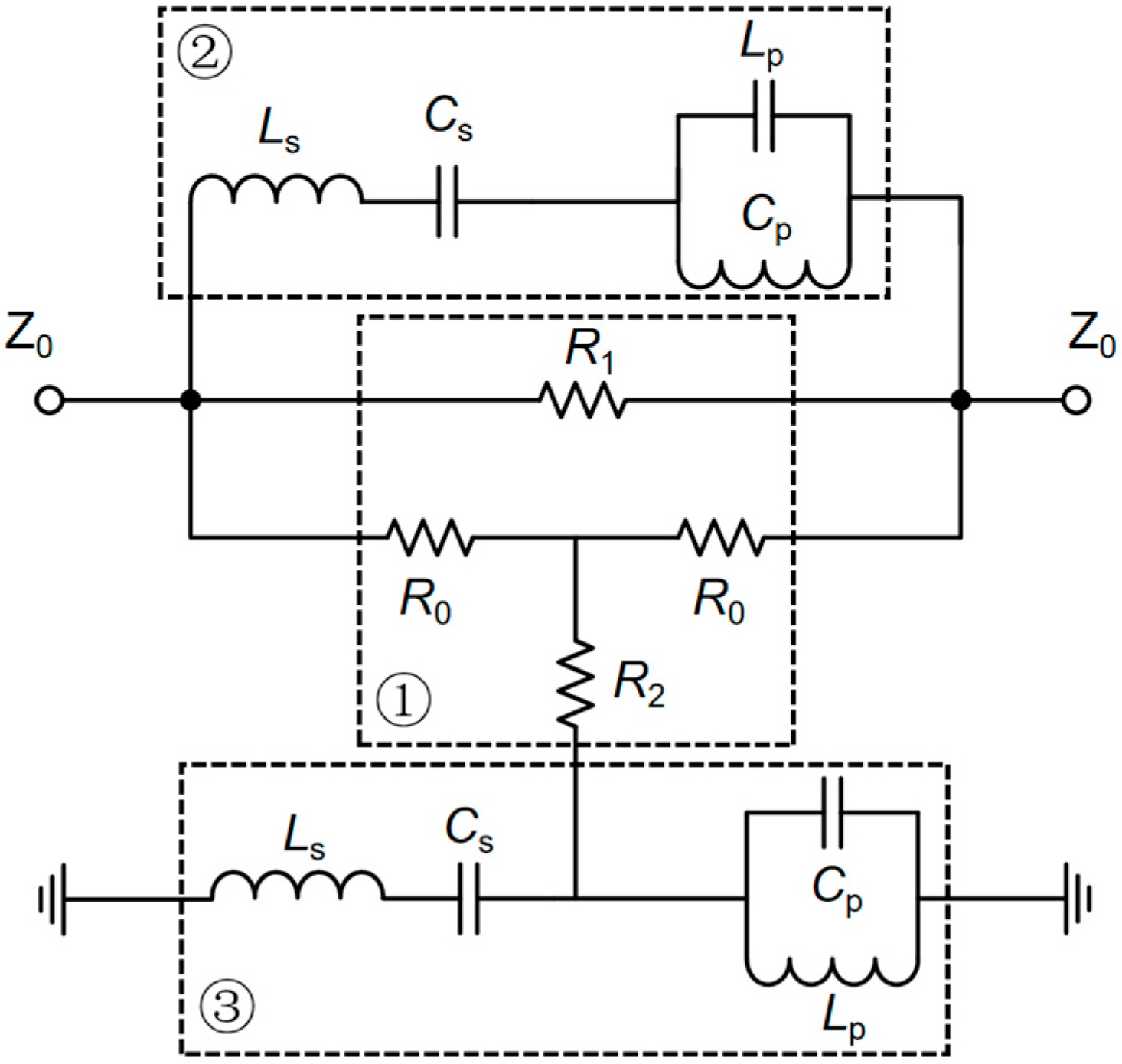

2. Circuit Design and Fabrication Process

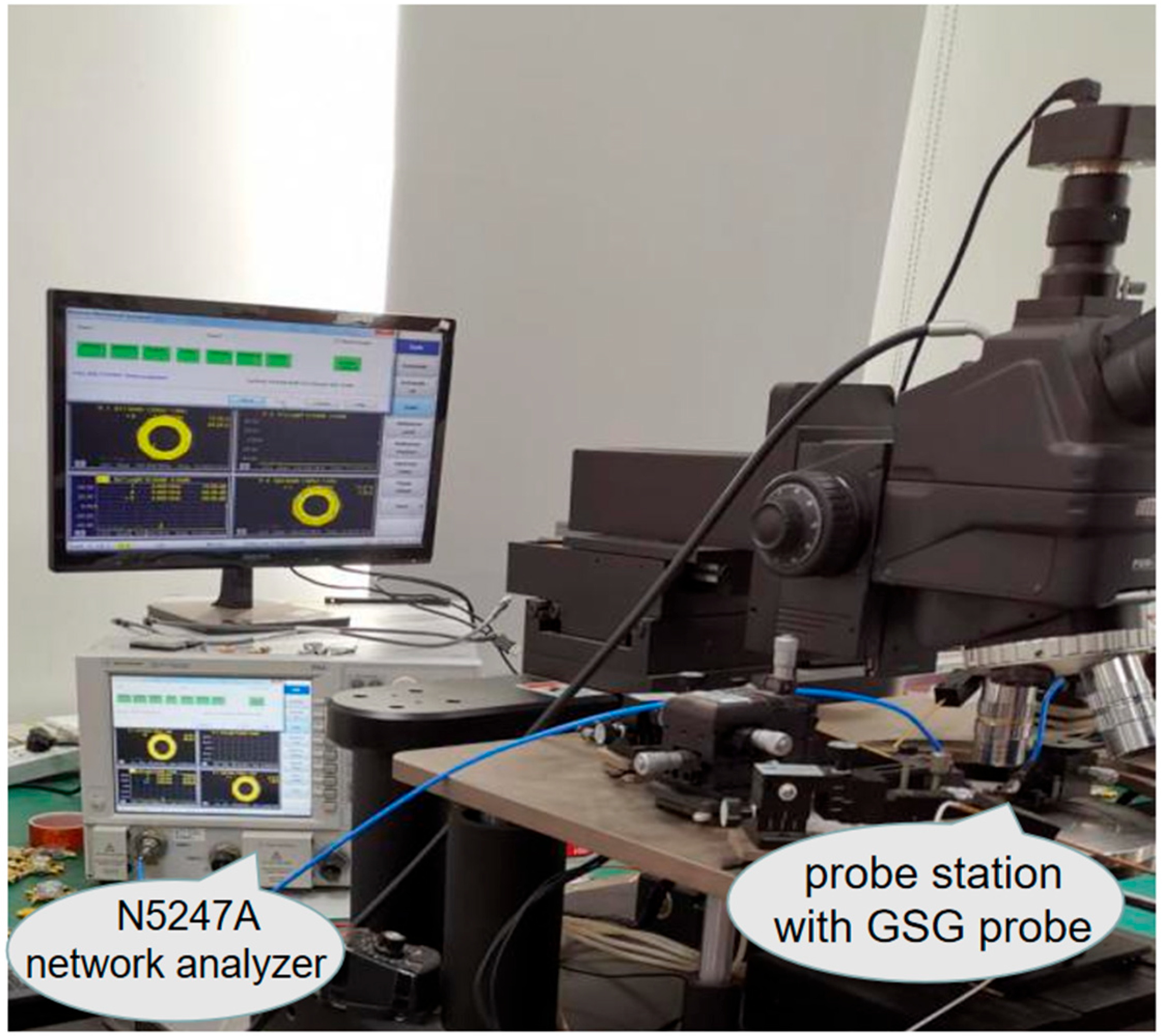

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sheikholeslami, A. Equalizer circuit [Circuit Intuitions]. IEEE Solid-State Circuits Mag. 2020, 12, 6–7. [Google Scholar] [CrossRef]

- Li, Q.; Yang, T. Dispersion analysis of shielded asymmetrical coplanar stripline and its broadband transition to microstrip. In Proceedings of the IEEE MTT-S International Wireless Symposium, Shanghai, China, 20–23 September 2020; pp. 1–3. [Google Scholar]

- Jain, N.; Brown, B. Dispersion characteristics of microstrip transmission line on glass microwave IC’s. IEEE Microw. Guid. Wave Lett. 1997, 7, 344–346. [Google Scholar] [CrossRef]

- Terman, F.E. Network theory, filters, and equalizers. Proc. IRE 1943, 31, 288–302. [Google Scholar] [CrossRef]

- Mellor, D.J. On the design of matched equalizers of prescribed gain versus frequency profiles. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest, San Diego, CA, USA, 21–23 June 1977; pp. 308–311. [Google Scholar]

- Lakshminarayanan, S.; Hofmann, K. A digitally controllable passive variable slope gain equalizer for wideband radio frequency system-on-chip applications. In Proceedings of the 32nd IEEE International System-on-Chip Conference, Singapore, 3–6 September 2019; pp. 461–465. [Google Scholar]

- Pang, X.; Xia, L.; Jiao, J. A gain equalizer based on grounded coplanar waveguide with sprial-shaped defected ground. In Proceedings of the IEEE 9th International Symposium on Microwave, Antenna, Propagation and EMC Technologies for Wireless Communications, Chengdu, China, 26–29 August 2022; pp. 15–19. [Google Scholar]

- Zhang, D.; Liu, Q.; Zhou, D.; Wang, S.; Zhang, Y. A gain equalizer based on dual-mode circular substrate integrated waveguide resonators. IEEE Microw. Wirel. Compon. Lett. 2017, 27, 539–541. [Google Scholar] [CrossRef]

- Xiao, X.; Li, W. A novel design and realization of microstrip lumped-like amplitude equalizer. In Proceedings of the IEEE International Conference on Microwave and Millimeter Wave Technology, Beijing, China, 5–8 June 2016; pp. 293–295. [Google Scholar]

- Li, S.; Ma, L.; Wang, L.; Wu, B.; Cheng, Y.; Lei, X.; Liu, F.; Cheng, G.J. An ultrawideband GaAs mmic microstrip directional coupler with high directivity and very flat coupling. IEEE Trans. Microw. Theory Tech. 2022, 70, 2271–2279. [Google Scholar] [CrossRef]

- Zhang, Y.; Xu, J.; He, C. A directivity-compensated wideband microstrip coupler based on capacitive-loading patches and reflectionless amplitude equalizers. IEEE Microw. Wirel. Compon. Lett. 2025, 35, 189–192. [Google Scholar] [CrossRef]

- Scheder, A.; Pfahler, T.; Bridier, A.; Vossiek, M. An ultra-wideband microstrip gain equalizer on thin-film ceramic for future millimeter wave applications up to and beyond 120 GHz. In Proceedings of the IEEE Wireless and Microwave Technology Conference, Clearwater, FL, USA, 15–16 April 2024; pp. 1–4. [Google Scholar]

- Han, L. A reconfigurable microwave equalizer with different maximum attenuations based on RF MEMS switches. IEEE Sens. J. 2016, 16, 17–18. [Google Scholar] [CrossRef]

- Wu, Y.; Yeng, I.; Yu, H. The improvement of CoZrTaB thin films on different substrates for flexible device applications. AIP Adv. 2021, 11, 025139. [Google Scholar] [CrossRef]

- Wu, Y.; Yu, H. A low-cost novel method to fabricate integrated magnetic core inductor embedded in organic substrate. IEEE Trans. Magn. 2022, 58, 1–5. [Google Scholar] [CrossRef]

- Xu, W.; Sinha, S.; Dastagir, T.; Wu, H.; Bakkaloglu, B.; Gardner, D.; Cao, Y.; Yu, H. Performance enhancement of on-chip inductors with permalloy magnetic rings. IEEE Electron Device Lett. 2010, 32, 69–71. [Google Scholar] [CrossRef]

- Li, K.; Wu, Y.; Lai, Z.; Yang, Q.; Wang, W. An Iterative extremely accurate generalized design methodology for TSV-based hybrid AlScN FBAR and IPD filtering chips. IEEE Trans. Microw. Theory Tech. 2025, 1–12. [Google Scholar] [CrossRef]

- Wei, Y.C.; Wang, C.; Gao, J.Y.; Meng, F.Y.; Wang, X.L.; Wu, Y.L. Lumped dual-band transformer with chebyshev and quasi-elliptic responses based on GaAs-IPD. IEEE Trans. Compon. Packag. Manuf. Technol. 2025, 15, 339–346. [Google Scholar] [CrossRef]

- Li, X.; Xing, M.; Liu, G.; Yang, X.; Dai, C.; Hou, M. Compact, reflectionless band-pass filter: Based on GaAs IPD process for highly reliable communication. Electronics 2021, 10, 2998. [Google Scholar] [CrossRef]

- Chu, H.N.; Jiang, M.J.; Ma, T.G. On-chip dual-band millimeter-wave power divider using GaAs-based IPD process. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 173–176. [Google Scholar] [CrossRef]

- Zoschke, K.; Wolf, M.J.; Topper, M.; Ehrmann, O.; Fritzsch, T.; Kaletta, K. Fabrication of application specific integrated passive devices using wafer level packaging technologies. IEEE Trans. Adv. Packag. 2007, 30, 359–368. [Google Scholar] [CrossRef]

- Li, C.C.; Hou, F.; Cao, Y.L.; Chen, W.; Liu, Q.; Qiu, L.F. Silicon-based 3-D self-packaged filtering power divider based on a multimode resonator. IEEE Microw. Wirel. Compon. Lett. 2025, 1–4. [Google Scholar] [CrossRef]

- Yang, X.; Sun, X.; Lu, Y. Silicon bridge for high-level RF microsystem package and mixed signals transmission. In Proceedings of the IEEE MTT-S International Microwave Workshop Series on Advanced Materials and Processes for RF and THz Applications, Chengdu, China, 13–15 November 2023; pp. 1–2. [Google Scholar]

- Zhang, A.; Xu, J.; Liu, Z. A microstrip linear-phase BPF using dual-band negative group delay equalizers. IEEE Microw. Wirel. Compon. Lett. 2024, 34, 387–390. [Google Scholar] [CrossRef]

| Component | Value | Component | Value |

|---|---|---|---|

| Ls | 2.654 nH | Cs | 0.597 pF |

| Lp | 0.663 nH | Cp | 2.389 pF |

| R0 | 50.0 Ω | R2 | 85.6 Ω |

| R1 | 29.2 Ω |

| Reference | Process | Design Method | Wafer -Level | Integration Form | Return Loss (dB) | Resonance Point | Size (mm2) | Operating Frequency (GHz) |

|---|---|---|---|---|---|---|---|---|

| [6] | SiGe BiCMOS | Microstrip lumped | Yes | On chip | ≤−10 | One | 0.429 | 0.2–1.85 |

| [7] | Al2O3 ceramic | Coplanar waveguide | No | Monolithic | ≤−11 | One | 30.4 | 6–9 |

| [8] | Al2O3 ceramic | Dual-mode SIW | No | Monolithic | / | Two | 186.2 | 13–13.5 |

| [9] | PCB | Microstrip Semi-lumped | No | Monolithic | / | One | 525 | 2–3 |

| [10] | GaAs IPD | Microstrip lumped | Yes | On chip | ≤−20 | One | / | 2–20 |

| This work | GaAs IPD | Microstrip lumped | Yes | Monolithic | ≤−15 | Two | 0.52 | 1–7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, X.; Xing, M.; Liu, G.; Li, X.; Sun, X.; Liu, W.; Lu, Y. Wafer-Level Amplitude Equalizer Based on an Integrated Passive Device Process with Two Resonance Points for Wavy In-Band Transmission. Electronics 2025, 14, 1715. https://doi.org/10.3390/electronics14091715

Yang X, Xing M, Liu G, Li X, Sun X, Liu W, Lu Y. Wafer-Level Amplitude Equalizer Based on an Integrated Passive Device Process with Two Resonance Points for Wavy In-Band Transmission. Electronics. 2025; 14(9):1715. https://doi.org/10.3390/electronics14091715

Chicago/Turabian StyleYang, Xiaodong, Mengjiang Xing, Gan Liu, Xiaozhen Li, Xiangyu Sun, Wenzhi Liu, and Yaobing Lu. 2025. "Wafer-Level Amplitude Equalizer Based on an Integrated Passive Device Process with Two Resonance Points for Wavy In-Band Transmission" Electronics 14, no. 9: 1715. https://doi.org/10.3390/electronics14091715

APA StyleYang, X., Xing, M., Liu, G., Li, X., Sun, X., Liu, W., & Lu, Y. (2025). Wafer-Level Amplitude Equalizer Based on an Integrated Passive Device Process with Two Resonance Points for Wavy In-Band Transmission. Electronics, 14(9), 1715. https://doi.org/10.3390/electronics14091715