A Newly Designed Double-Sided Cooling Wire-Bondless Power Module with Silicon Carbide MOSFETs and Ultra-Low Stray Inductance

Abstract

1. Introduction

2. Design and Optimisation of the Double-Sided Half-Bridge Module

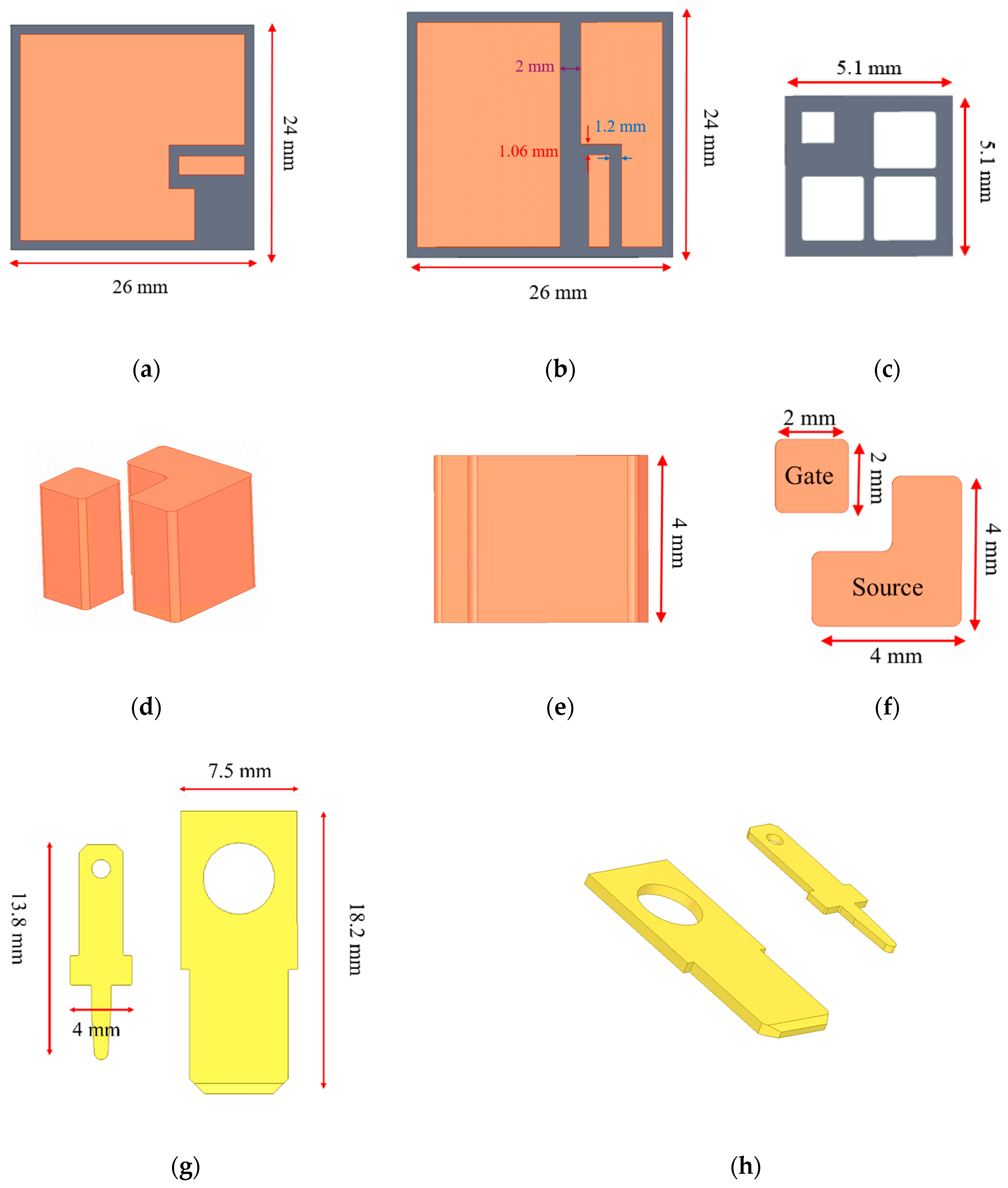

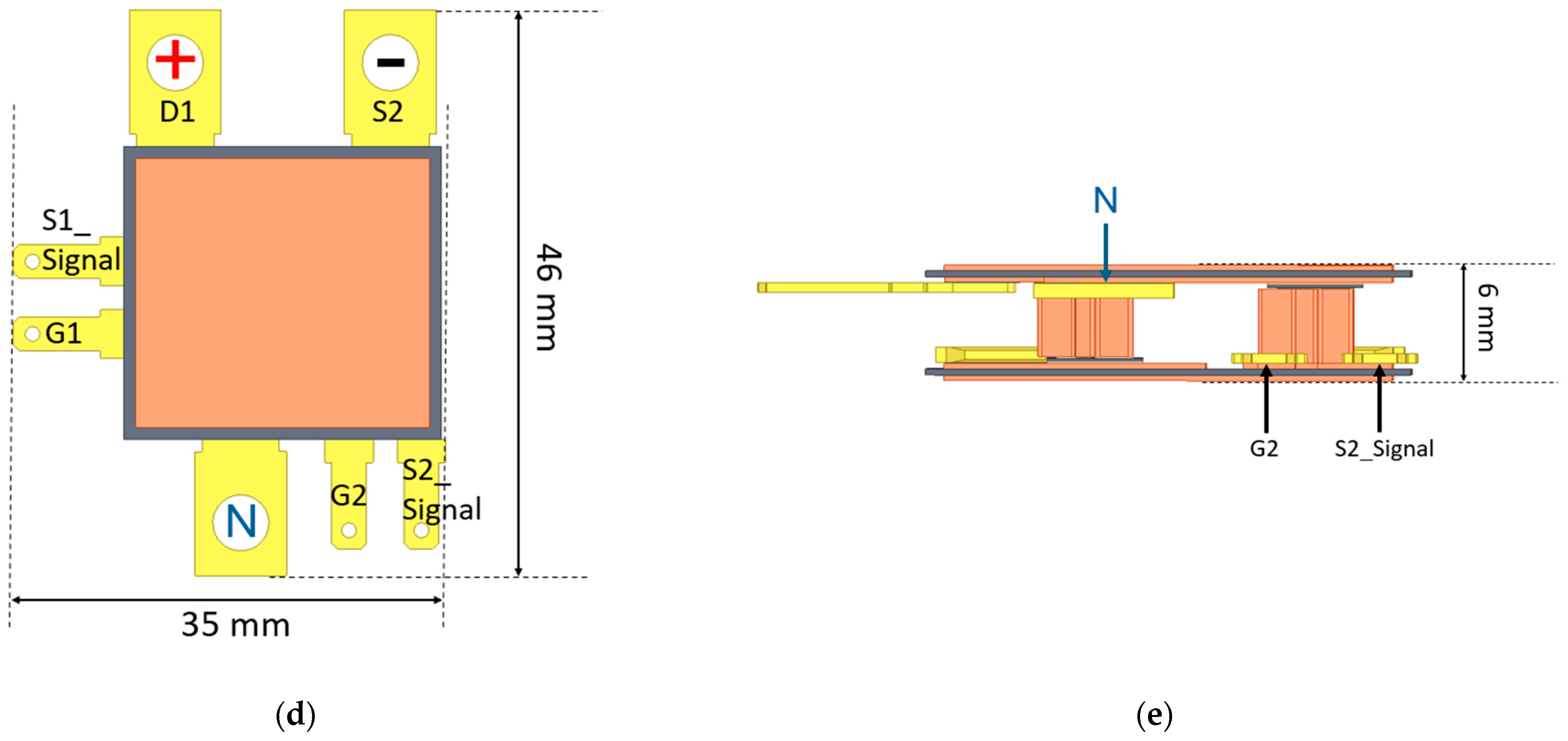

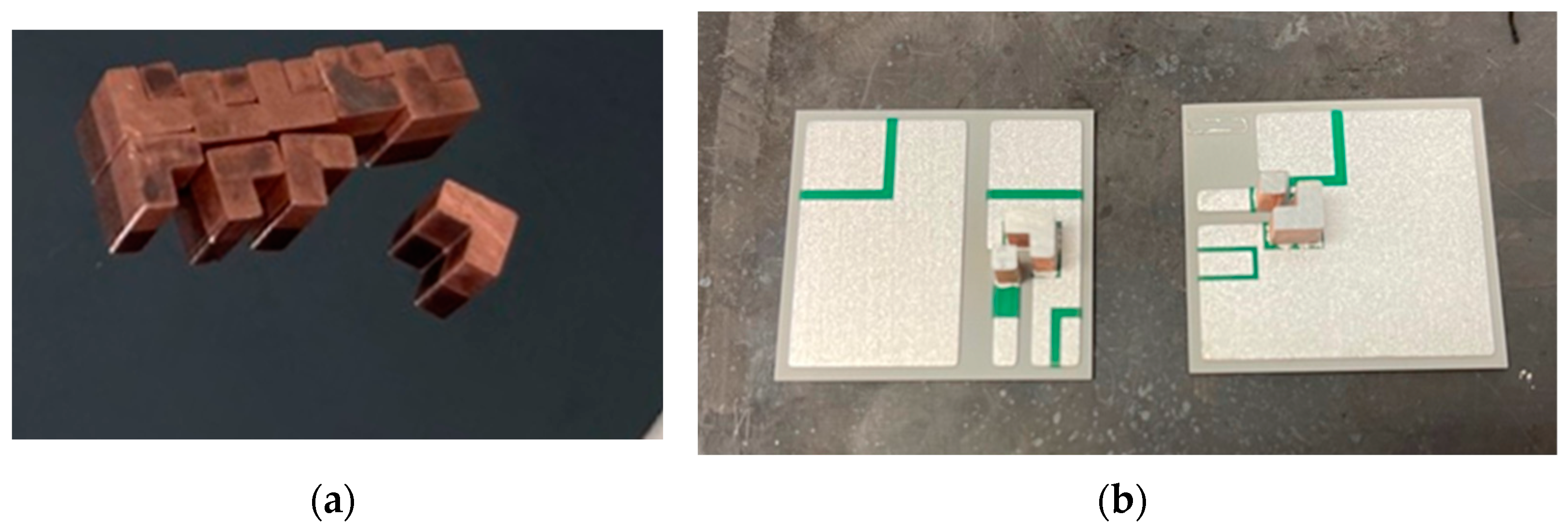

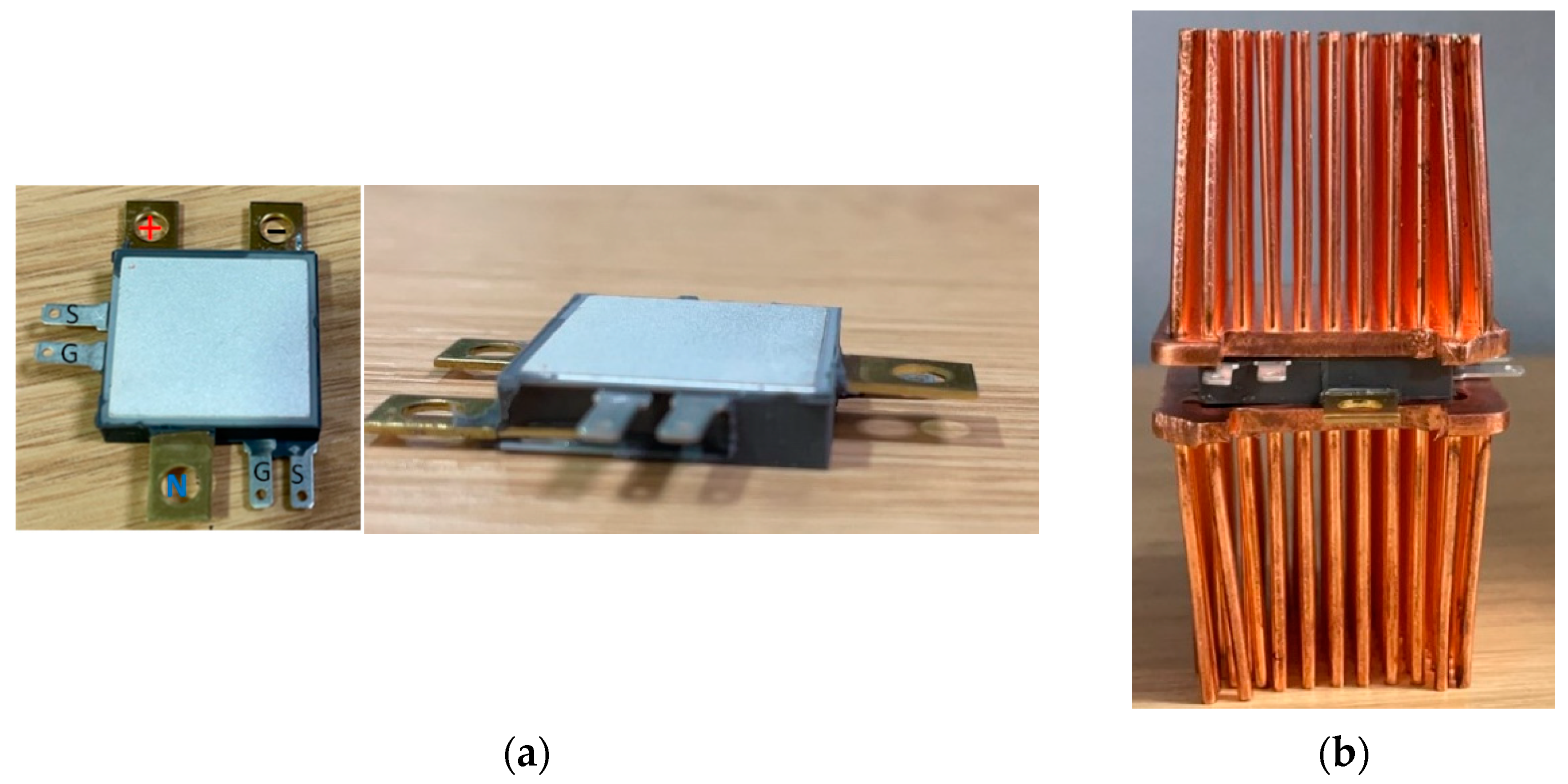

2.1. Layout of AMB Boards, Customised Copper Connectors, Bare Die, and Power and Signal Connectors

- Position the gate contact close to the die to minimise stray inductance;

- Arrange the current flow from the die to the source contact in the opposite direction to the current flow from the drain to the die to reduce stray inductance;

- Use Kelvin-source contacts for the gate signals to effectively minimise parasitic resistances and reduce false switching events.

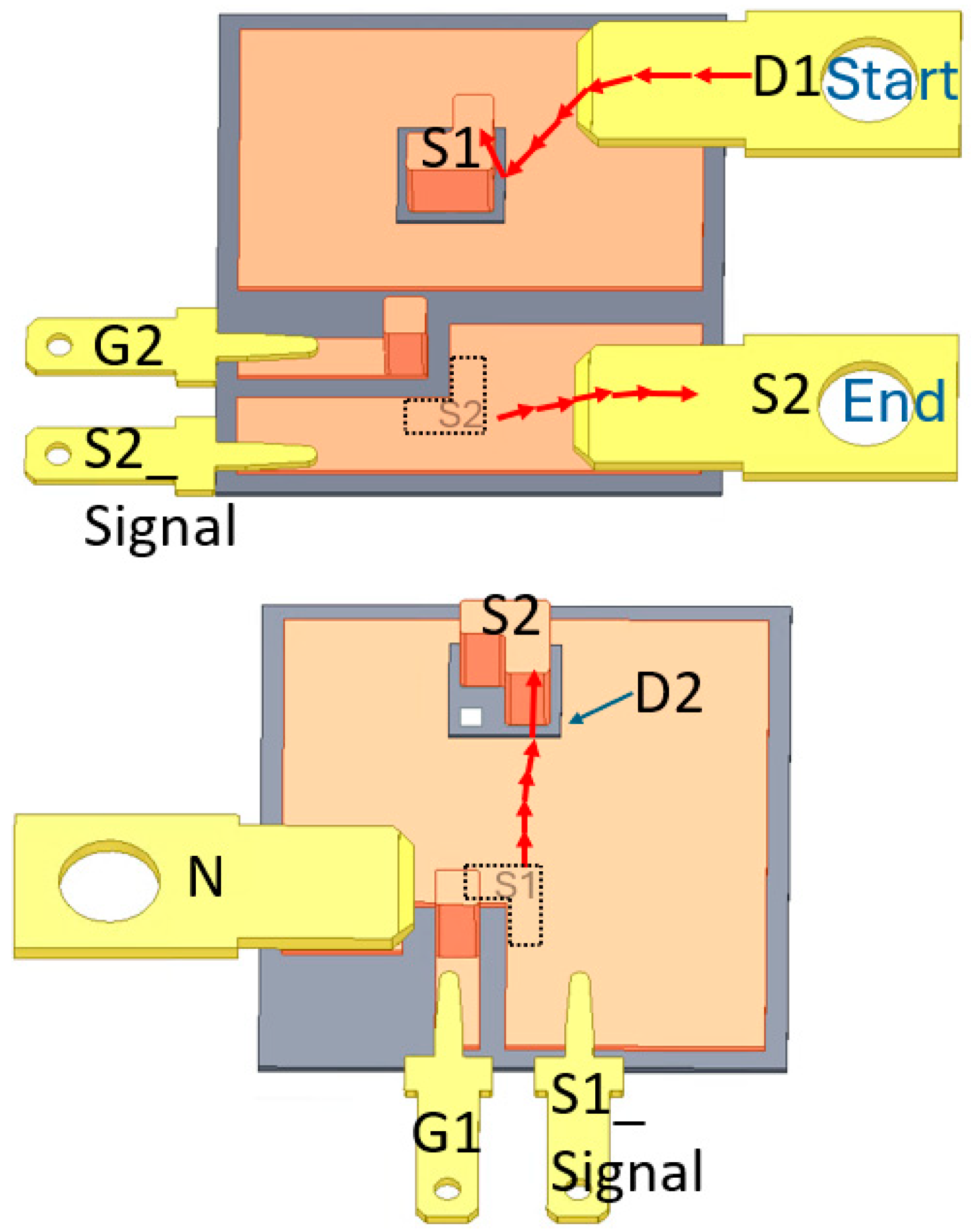

2.2. Assembling of the Double-Sided Half-Bridge Circuit

2.3. Insulation Consideration for the Proposed Power Module

3. Ansys Q3D and Icepak Simulation of the Double-Sided Half-Bridge Circuit

3.1. Simulation of the Positive to Negative Stray Inductance

3.2. Comparison Between the Thermal Performance of the Single-Side Cooling Design and Double-Sided Cooling Design

3.2.1. General Operating Condition

3.2.2. Extreme Operating Condition

4. Packaged Module of the Double-Sided Half-Bridge Circuit

5. Electrical Test of the Packaged Double-Sided Half-Bridge Converter

5.1. Double Pulse Test

5.2. Inductive Load Test

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tang, G.; Chai, T.C.; Zhang, X. Thermal Optimization and Characterization of Sic-Based High Power Electronics Packages with Advanced Thermal Design. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 854–863. [Google Scholar] [CrossRef]

- Zhang, Y.; Chen, G.; Hu, Y.; Gong, C.; Wang, Y. Cascaded Multilevel Inverter Based Power and Signal Multiplex Transmission for Electric Vehicles. CES Trans. Electr. Mach. Syst. 2020, 4, 123–129. [Google Scholar] [CrossRef]

- Reis, F.E.U.; Torrico-Bascope, R.P.; Tofoli, F.L.; Santos Bezerra, L.D. Bidirectional Three-Level Stacked Neutral-Point-Clamped Converter for Electric Vehicle Charging Stations. IEEE Access 2020, 8, 37565–37577. [Google Scholar] [CrossRef]

- Luciano, F.S.A.; Ruan, C.M.G.; Pierre, L.; Raoni, D.A.P.; Jeannin, P.-O.; Luciano, B.A.; Rocha, F.V. SIC Power Devices in Power Electronics: An Overview. In Proceedings of the 2017 Brazilian Power Electronics Conference (COBEP), Juiz de Fora, Brazil, 15 January 2017; pp. 1–8. [Google Scholar]

- Yu, S.; Wang, J.; Zhang, X.; Liu, Y.; Jiang, N.; Wang, W. The Potential Impact of Using Traction Inverters with SiC MOSFETs for Electric Buses. IEEE Access 2021, 9, 51561–51572. [Google Scholar] [CrossRef]

- Matsuoka, T.; Ohki, A.; Ohno, T.; Kawaguchi, Y. Comparison of GaN- and ZnSe-Based Materials for Light Emitters. J. Cryst. Growth 1994, 138, 727–736. [Google Scholar] [CrossRef]

- Shur, M. Wide Band Gap Semiconductor Technology: State-of-the-Art. Solid State Electron. 2019, 155, 65–75. [Google Scholar] [CrossRef]

- Shivakumar, S.; Yoon, J.; Sirkar, T. Gallium Nitride: A Strategic Opportunity for the Semiconductor Industry. Available online: https://www.csis.org/analysis/gallium-nitride-strategic-opportunity-semiconductor-industry?utm_source=chatgpt.com (accessed on 25 March 2025).

- Ke, H.; Mehrotra, U.; Hopkins, D.C. 3-D Prismatic Packaging Methodologies for Wide Band Gap Power Electronics Modules. IEEE Trans. Power Electron. 2021, 36, 13057–13066. [Google Scholar] [CrossRef]

- Paret, P.; Cousineau, J.E.; Narumanchi, S.; Lu, G.Q.; Ngo, K. Thermal and Mechanical Design of a High-Voltage Power Electronics Package. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021; pp. 50–54. [Google Scholar]

- Fernandes, B.G. Review of Power Electronics Packaging and the Use of Copper as Heat Sink; Torrey Hills Technologies, LLC: San Diego, CA, USA, 2013. [Google Scholar]

- Le Henaff, F.R.; Azzopardi, S.; Theolier, L.; Deletage, J.-Y. Silver Sintering Wire-Bonding Less Power Module for High Temperature Applications. In Proceedings of the Symposium de Génie Électrique 2014, Cachan, France, 8–10 July 2014. [Google Scholar]

- Gao, S.; Yang, Z.; Tan, Y.; Li, X.; Chen, X.; Sun, Z.; Lu, G.Q. Bonding of Large Substrates by Silver Sintering and Characterization of the Interface Thermal Resistance. IEEE Trans. Ind. Appl. 2019, 55, 1828–1834. [Google Scholar] [CrossRef]

- Wang, M.; Mei, Y.; Li, X.; Burgos, R.; Boroyevich, D.; Lu, G.Q. Pressureless Silver Sintering on Nickel for Power Module Packaging. IEEE Trans. Power Electron. 2019, 34, 7121–7125. [Google Scholar] [CrossRef]

- Yan, H.; Liang, P.; Mei, Y.; Feng, Z. Brief Review of Silver Sinter-Bonding Processing for Packaging High-Temperature Power Devices. Chin. J. Electr. Eng. 2020, 6, 25–34. [Google Scholar] [CrossRef]

- Chen, H.; Hossain, M.M.; Gonzalez Castillo, D.; Li, X.; Wallace, A.; Chen, Y.; Mantooth, H.A. Design and Optimization of SiC MOSFET Wire Bondless Power Modules. In Proceedings of the 2020 IEEE 9th International Power Electronics and Motion Control Conference, IPEMC 2020 ECCE Asia, Nanjing, China, 29 November–2 December 2020; pp. 725–728. [Google Scholar]

- Seal, S.; Wallace, A.K.; Dearien, A.M.; Farnell, C.; Mantooth, H.A. A Wire Bondless SiC Switching Cell with a Vertically Integrated Gate Driver. IEEE Trans. Power Electron. 2020, 35, 9692–9701. [Google Scholar] [CrossRef]

- Chen, Y.; Lei, G.; Lu, G.Q.; Mei, Y.H. High-Temperature Characterizations of a Half-Bridge Wire-Bondless SiC MOSFET Module. IEEE J. Electron Devices Soc. 2021, 9, 966–971. [Google Scholar] [CrossRef]

- Zhang, H.; Ang, S.S.; Mantooth, H.A.; Krishnamurthy, S. A High Temperature, Double-Sided Cooling SiC Power Electronics Module. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 28 October 2013; pp. 2877–2883. [Google Scholar]

- Charboneau, B.C.; Wang, F.; Van Wyk, J.D.; Boroyevich, D.; Liang, Z.; Scott, E.P.; Tipton, C.W. Double-Sided Liquid Cooling for Power Semiconductor Devices Using Embedded Power Packaging. In Proceedings of the Fourtieth IAS Annual Meeting, Conference Record of the 2005 Industry Applications Conference, Hong Kong, China, 2–6 October 2005; pp. 1138–1143. [Google Scholar]

- Wang, M.; Mei, Y.; Liu, W.; Xie, Y.; Fu, S.; Li, X.; Lu, G.Q. Reliability Improvement of a Double-Sided IGBT Module by Lowering Stress Gradient Using Molybdenum Buffers. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1637–1648. [Google Scholar] [CrossRef]

- Rong, X.; Wu, R.; Mawby, P. Simulation and Testing of a Newly Designed Half Bridge Module with Silicon Carbide MOSFET. In Proceedings of the 12th International Conference on Power Electronics, Machines and Drive, Brussels, Belgium, 23 October 2023; Volume 2023, pp. 462–469. [Google Scholar]

- Marcinkowski, J. Dual-Sided Cooling of Power Semiconductor Modules. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 20 May 2014; pp. 1–7. [Google Scholar]

- Liu, M.; Coppola, A.; Alvi, M.; Anwar, M. Comprehensive Review and State of Development of Double-Sided Cooled Package Technology for Automotive Power Modules. IEEE Open J. Power Electron. 2022, 3, 271–289. [Google Scholar] [CrossRef]

- Li, Y.; Zhu, S.; Ma, Y.; Wang, Y.; Jiao, M.; Wu, C.; Zhao, Z.; Yu, J. Highly Integrated Power Unit Based on Double Side Cooling Module. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 16 May 2017; pp. 1–6. [Google Scholar]

- Brian, P.; Srikanth, K.; Aicha, E.; Fred, B. Evaluation of Direct Bond Aluminum Susbtrates for Power Electronic Applications in Extreme Environments. In Proceedings of the IMAPS/ACerS 8th International CICMT Conference and Exhibition, Erfurt, Germany, 16 April 2012. [Google Scholar]

- Wang, X. Silicon Nitride and Electric Vehicles. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Shenzhen, China, 3–7 May 2021; pp. 1–4. [Google Scholar]

- Wolfspeed. CAB400M12XM3 1200 V SiC Power Module Data Sheet; Wolfspeed: Durham, UK, 2024. [Google Scholar]

- Infineon. FF400R07A01E3_S6 DoubleSideCooledModule; Infineon: Munich, Germany, 2020. [Google Scholar]

- Zeng, Z.; Ou, K.; Wang, L.; Yu, Y. Reliability-Oriented Automated Design of Double-Sided Cooling Power Module: A Thermo-Mechanical-Coordinated and Multi-Objective-Oriented Optimization Methodology. IEEE Trans. Device Mater. Reliab. 2020, 20, 584–595. [Google Scholar] [CrossRef]

| Type of the Half-Bridge Power Module | Voltage Rating (V) | Cooling Type | Dies in Parallel | Stray Inductance (nH) | SiC or IGBT |

|---|---|---|---|---|---|

| Proposed Power module | 1200 | Double sided | 1 | 4.7 2.4 (2 die in parallel) 0.9 (5 die in parallel) | SiC |

| Infineon FF400R07A01E3_S6 | 700 | Double-sided | 2 | 15 | IGBT |

| Wolfspeed CAB400M12XM3 | 1200 | Single-Sided | 5 | 6.7 | SiC |

| AMB Board Size (L × W × H) (mm) | Heat Sink Size Including Pin Fin (L × W × H) (mm) | Cooling Water Flowing Speed and Temperature | Total Loss Estimated (W) | |

|---|---|---|---|---|

| Single-Sided Cooling | 39 × 26 × 0.92 | 45 × 33 × 13 | 0.5 m/s 20 °C initial temperature | 156.5 (General) 323.5 (Extreme) |

| Double-Sided Cooling | 26 × 24 × 0.92 (×2) | 24 × 22 × 13 (×2) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Rong, X.; Wu, R.; Mawby, P. A Newly Designed Double-Sided Cooling Wire-Bondless Power Module with Silicon Carbide MOSFETs and Ultra-Low Stray Inductance. Electronics 2025, 14, 1520. https://doi.org/10.3390/electronics14081520

Rong X, Wu R, Mawby P. A Newly Designed Double-Sided Cooling Wire-Bondless Power Module with Silicon Carbide MOSFETs and Ultra-Low Stray Inductance. Electronics. 2025; 14(8):1520. https://doi.org/10.3390/electronics14081520

Chicago/Turabian StyleRong, Xiaoyun, Ruizhu Wu, and Phil Mawby. 2025. "A Newly Designed Double-Sided Cooling Wire-Bondless Power Module with Silicon Carbide MOSFETs and Ultra-Low Stray Inductance" Electronics 14, no. 8: 1520. https://doi.org/10.3390/electronics14081520

APA StyleRong, X., Wu, R., & Mawby, P. (2025). A Newly Designed Double-Sided Cooling Wire-Bondless Power Module with Silicon Carbide MOSFETs and Ultra-Low Stray Inductance. Electronics, 14(8), 1520. https://doi.org/10.3390/electronics14081520