Investigation of Source/Drain Height Variation and Its Impacts on FinFET and GAA Nanosheet FET

Abstract

1. Introduction

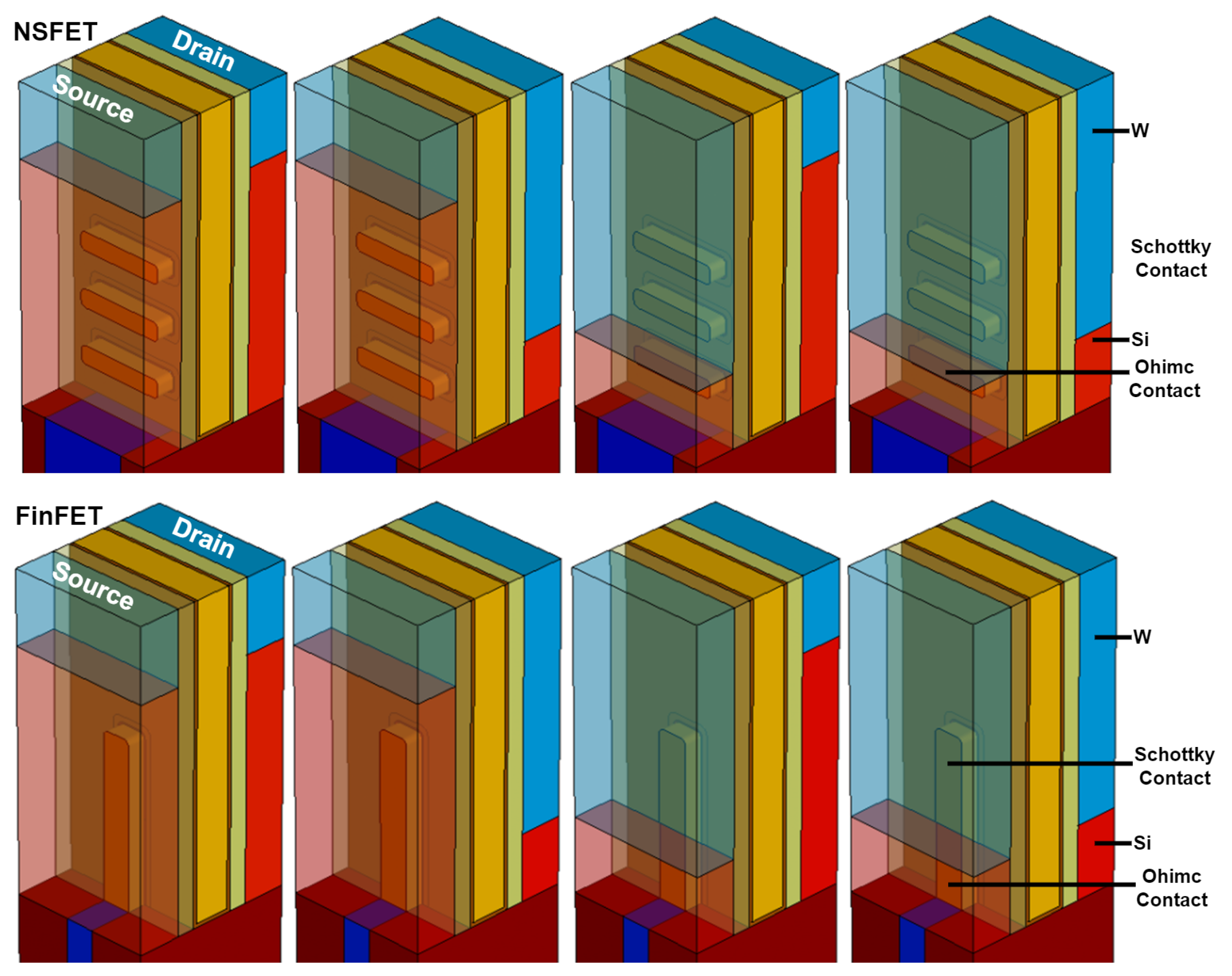

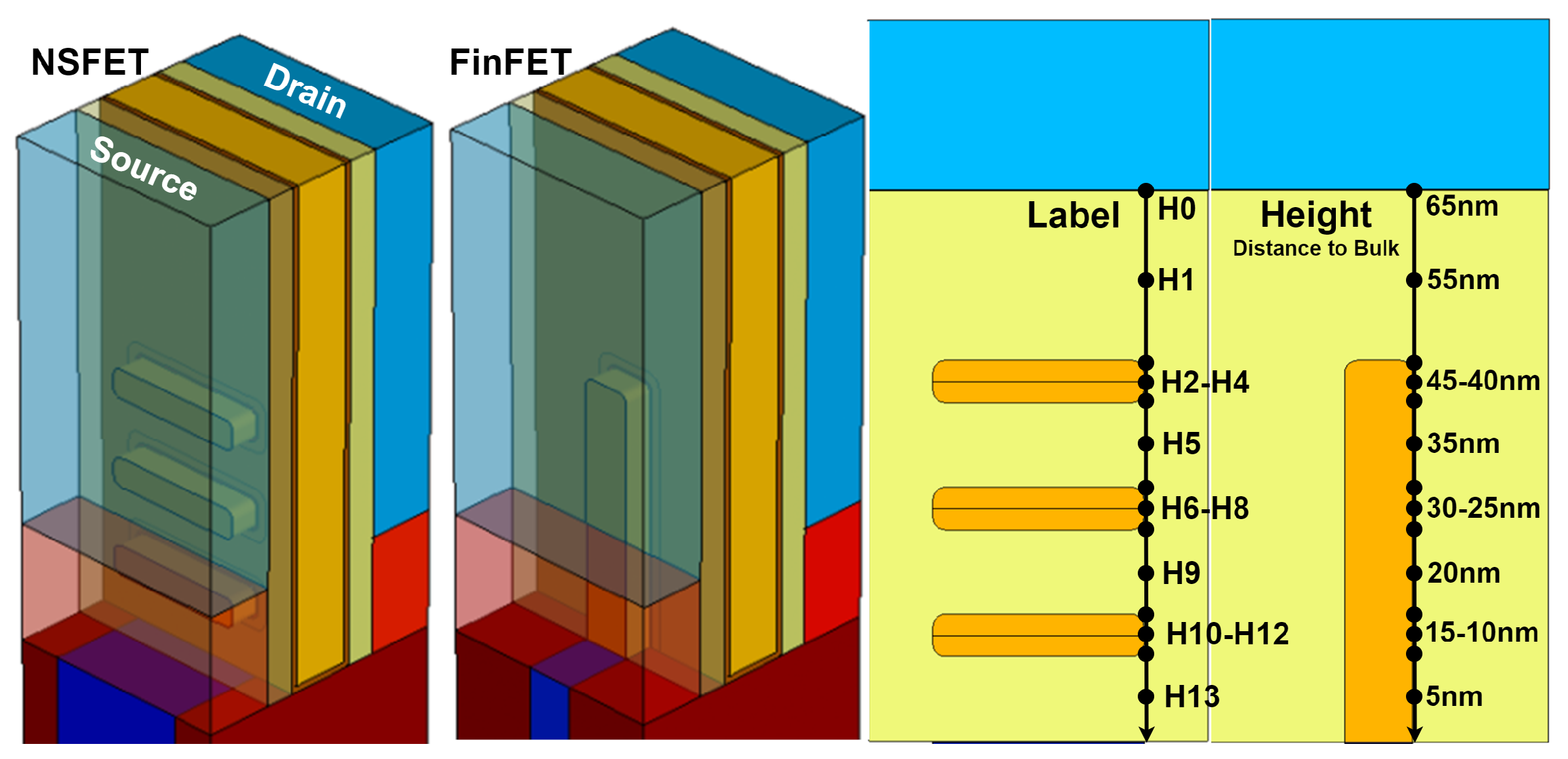

2. Device Structure and Simulation Condition

3. The Impact of Source/Drain Height Variations on Electrical Performance

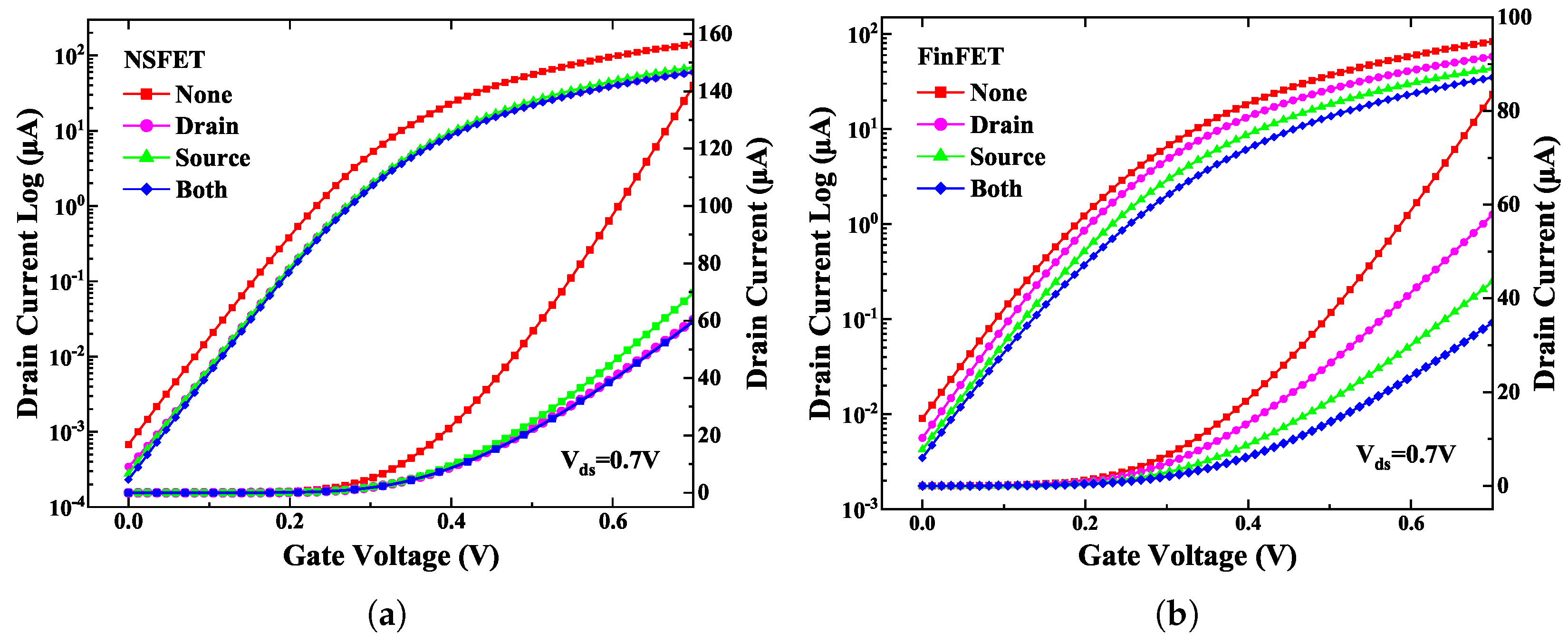

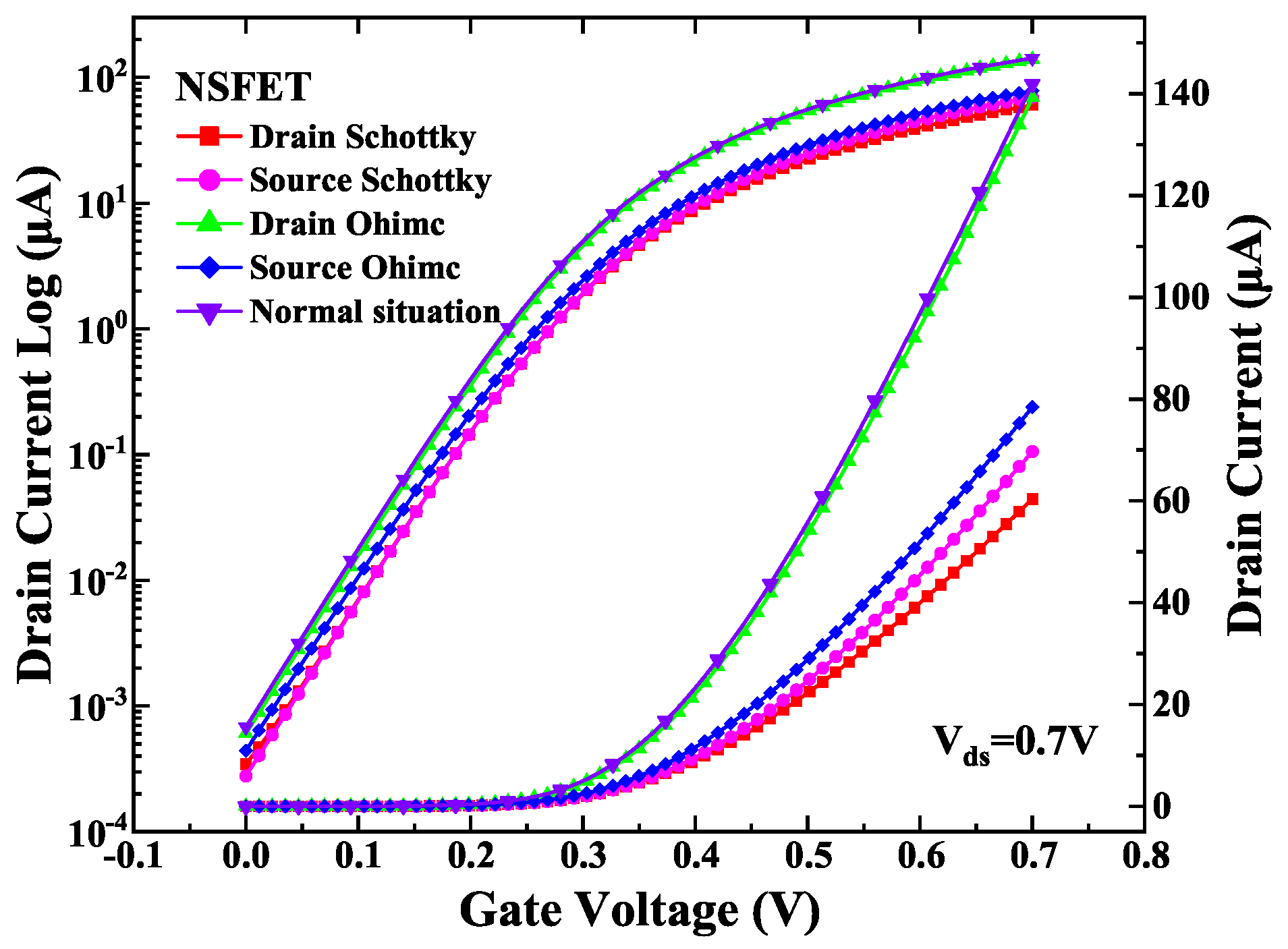

3.1. The Impact of Height Variations of Different Electrodes on Device Electrical Characteristics

3.2. The Impact of Varying Degrees of Height Changes on Device Electrical Characteristics

4. Circuit-Level Benchmark Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Xie, Q.; Lin, X.; Wang, Y.; Dousti, M.J.; Shafaei, A.; Ghasemi-Gol, M.; Pedram, M. 5 nm FinFET Standard Cell Library Optimization and Circuit Synthesis in Near-and Super-Threshold Voltage Regimes. In Proceedings of the 2014 IEEE Computer Society Annual Symposium on VLSI, Tampa, FL, USA, 9–11 July 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 424–429. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Hikavyy, A.; Kim, M.S.; Tao, Z.; Wostyn, K.; Chew, S.A.; De Keersgieter, A.; Mannaert, G.; Rosseel, E.; et al. Gate-all-around mosfets based on vertically stacked horizontal si nanowires in a replacement metal gate process on bulk si substrates. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Pittsburgh, PA, USA, 11–13 July 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 1–2. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. 5 nm FinFET Stacked nanosheet gate-all-around transistor to enable scaling beyond finfet. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; IEEE: Piscataway, NJ, USA, 2017; pp. T230–T231. [Google Scholar]

- Champac, V.; Garcia Gervacio, J.; Champac, V.; Garcia Gervacio, J. Designing with FinFETs and Process Variation Impact. In Timing Performance of Nanometer Digital Circuits Under Process Variations; Springer: Berlin/Heidelberg, Germany, 2018; pp. 143–163. [Google Scholar]

- Pande, N.; Zhou, C.; Lin, M.H.; Fung, R.; Wong, R.; Wen, S.; Kim, C.H. Characterizing electromigration effects in a 16 nm FinFET process using a circuit based test vehicle. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; IEEE: Piscataway, NJ, USA, 2019; pp. 5.3.1–5.3.4. [Google Scholar]

- Kumari, N.A.; Prithvi, P. Performance evaluation of GAA nanosheet FET with varied geometrical and process parameters. Silicon 2022, 14, 9821–9831. [Google Scholar] [CrossRef]

- Kim, S.; Lee, K.; Kim, S.; Kim, M.; Lee, J.H.; Kim, S.; Park, B.G. Investigation of device performance for fin angle optimization in FinFET and gate-all-around FETs for 3 nm-node and beyond. IEEE Trans. Electron. Devices 2022, 69, 2088–2093. [Google Scholar] [CrossRef]

- Kim, S.; Kim, M.; Ryu, D.; Lee, K.; Kim, S.; Lee, J.; Lee, R.; Kim, S.; Lee, J.H.; Park, B.G. Investigation of electrical characteristic behavior induced by channel-release process in stacked nanosheet gate-all-around MOSFETs. IEEE Trans. Electron. Devices 2020, 34, 2648–2652. [Google Scholar] [CrossRef]

- Wei, T.C.; Narang, V.; Thean, A. Electrical characterization of FEOL bridge defects in advanced nanoscale devices using TCAD simulations. In Proceedings of the 2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 16–19 July 2018; pp. 1–4. [Google Scholar]

- Dibaj, R.; Al-Khalili, D.; Shams, M. Gate Oxide Short Defect Model in FinFETs. J. Electron. Test. 2018, 34, 351–362. [Google Scholar] [CrossRef]

- Bhat, T.S.; Shintri, S.; Chen, B.; Lo, H.C.; Peng, J.; Qi, Y.; Willeman, M.; Mishra, S.K.; Yuksek, N.; Gao, W.Z. Abnormal silicon-germanium (SiGe) epitaxial growth in FinFETs. IEEE Trans. Semicond. Manuf. 2020, 33, 291–294. [Google Scholar] [CrossRef]

- Li, X.; Dube, A.; Ye, Z.; Sharma, S.; Kim, Y.; Chu, S. Selective epitaxial Si: P film for nMOSFET application: High phosphorous concentration and high tensile strain. ECS Trans. 2018, 64, 959. [Google Scholar] [CrossRef]

- Wang, Y.; Zheng, S.; Zhang, S.; Wang, J.; Lu, G.; Wen, G. Study on Different Failure Mechanisms of MOSFET Caused by Different Oxide Defects in 14 nm FinFET IC. In Proceedings of the 2024 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 15–18 July 2024; pp. 1–4. [Google Scholar]

- Wang, D.; Sun, X.; Liu, T.; Chen, K.; Yang, J.; Wu, C.; Xu, M.; Zhang, W. Investigation of Source/Drain Recess Engineering and Its Impacts on FinFET and GAA Nanosheet FET at 5 nm Node. Electronics 2023, 12, 770. [Google Scholar] [CrossRef]

- Pelosi, M. From FinFET to Nanosheet Si-SiGe GAAFET: Fabrication Process Simulation and Analysis. Ph.D. Thesis, Politecnico di Torino, Turin, Italy, 2021. [Google Scholar]

- International Roadmap for Devices and Systems More Moore. 2020. Available online: https://irds.ieee.org/editions/2020 (accessed on 1 March 2025).

- Tsen, C.J.; Chung, C.C.; Liu, C.W. Self-heating mitigation of treefets by interbridges. IEEE Trans. Electron. Devices 2022, 69, 4123–4128. [Google Scholar] [CrossRef]

- Mertens, H.; Ritzenthaler, R.; Pena, V.; Santoro, G.; Kenis, K.; Schulze, A.; Litta, E.D.; Chew, S.A.; Devriendt, K.; Demuynck, S.; et al. Vertically stacked gate-all-around si nanowire transistors: Key process optimizations and ring oscillator demonstration. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 37.4.1–37.4.4. [Google Scholar]

| Parameter | Symbol | Value |

|---|---|---|

| Gate Length | 12 nm | |

| Spacer Length | 5 nm | |

| Inner Spacer Length | 1 nm | |

| S/D Length | 12 nm | |

| S/D Height | 65 nm | |

| Nano-Sheet Width | 25 nm | |

| Nano-Sheet Thickness | 5 nm | |

| Nano-Sheet Distance | 10 nm | |

| Fin Width | 8.3 nm | |

| Fin Height | 45 nm | |

| Equivalent Oxide Thickness | 0.7 nm | |

| Channel Doping | ||

| LDD Doping | ||

| S/D Doping | ||

| Bulk Doping | ||

| Substrate Doping | ||

| Gate Work Function | 4.41 eV |

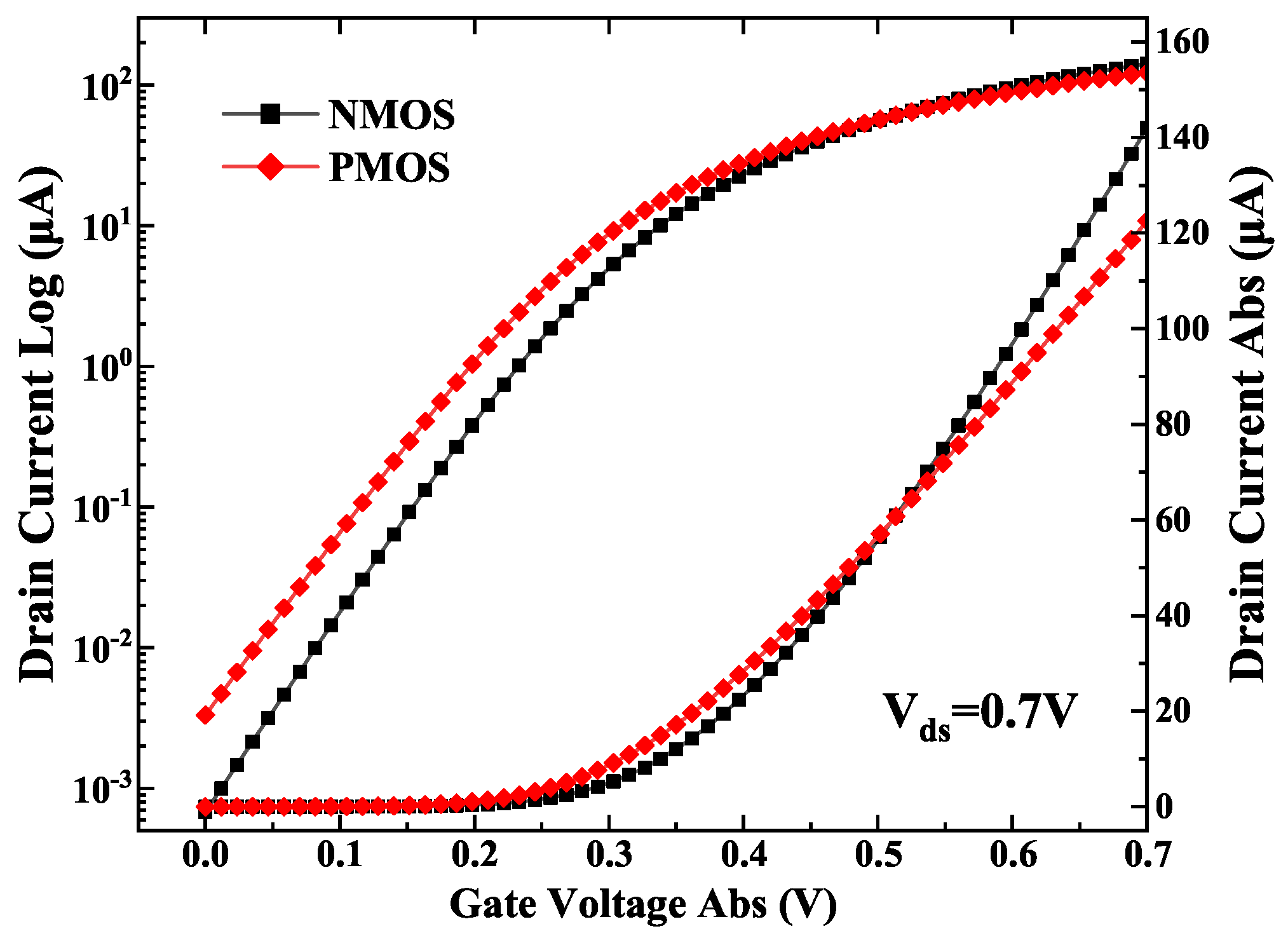

| Device Types | Formula | Value |

|---|---|---|

| NSFET | 375 | |

| FinFET | 373.5 |

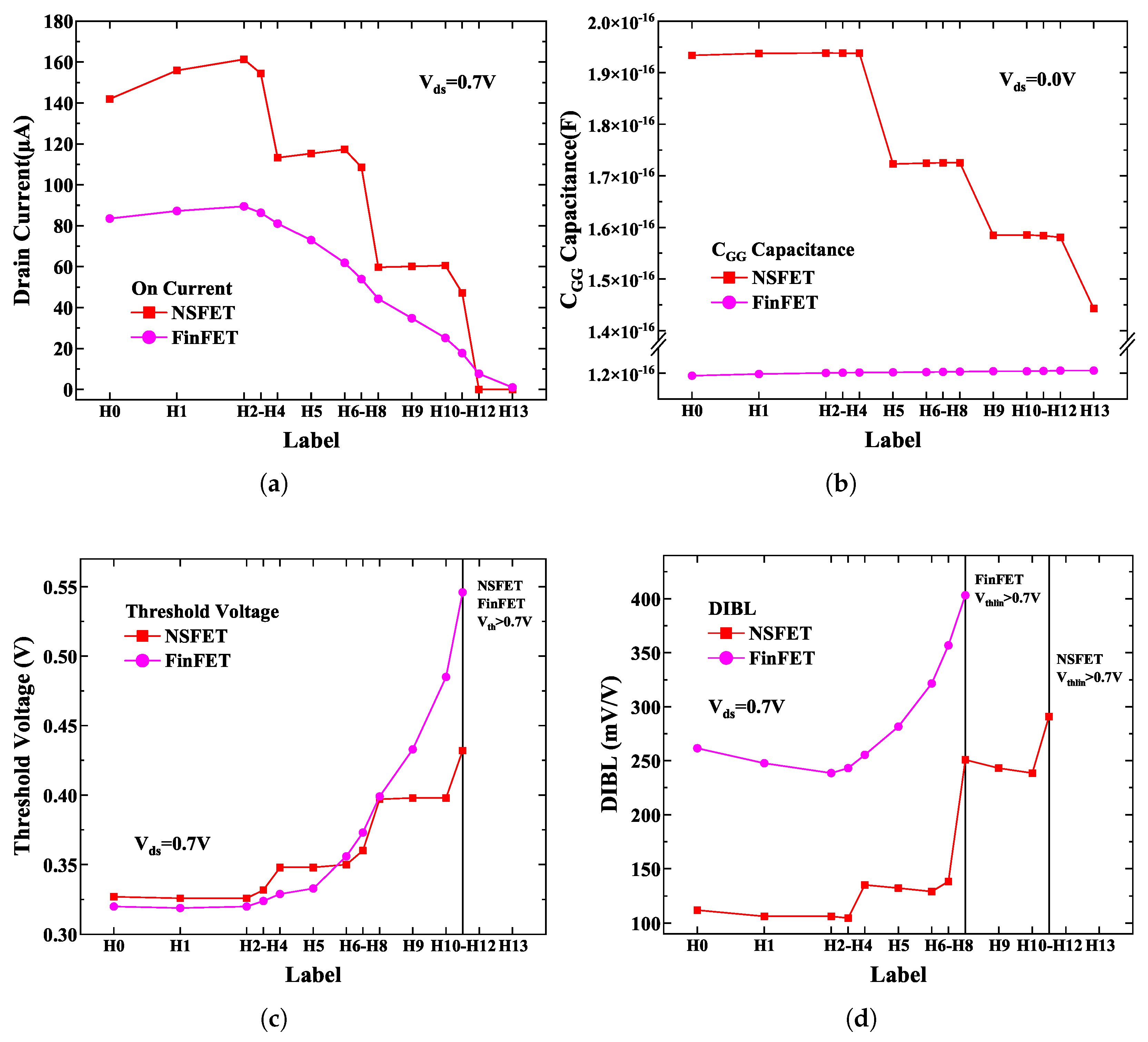

| Label | (nm) | (A) | ( F) | (V) | DIBL (mV/V) | ||||

|---|---|---|---|---|---|---|---|---|---|

| NSFET | FinFET | NSFET | FinFET | NSFET | FinFET | NSFET | FinFET | ||

| H0 | 65.0 | 141.95 | 83.51 | 1.934 | 1.195 | 0.327 | 0.320 | 112.0 | 261.5 |

| H1 | 55.0 | 155.88 | 87.21 | 1.937 | 1.199 | 0.326 | 0.319 | 106.2 | 247.7 |

| H2 | 45.0 | 161.30 | 89.48 | 1.938 | 1.201 | 0.326 | 0.320 | 106.2 | 238.5 |

| H3 | 42.5 | 154.39 | 86.35 | 1.938 | 1.201 | 0.332 | 0.324 | 104.6 | 243.1 |

| H4 | 40.0 | 113.26 | 81.04 | 1.938 | 1.201 | 0.348 | 0.329 | 135.4 | 255.4 |

| H5 | 35.0 | 115.32 | 73.00 | 1.723 | 1.202 | 0.348 | 0.333 | 132.3 | 281.5 |

| H6 | 30.0 | 117.29 | 61.89 | 1.725 | 1.202 | 0.350 | 0.356 | 129.2 | 321.5 |

| H7 | 27.5 | 108.60 | 53.95 | 1.725 | 1.203 | 0.360 | 0.373 | 138.5 | 356.9 |

| H8 | 25.0 | 59.76 | 44.33 | 1.726 | 1.203 | 0.397 | 0.399 | 250.8 | 403.1 |

| H9 | 20.0 | 60.13 | 34.85 | 1.585 | 1.204 | 0.398 | 0.433 | 243.1 | × |

| H10 | 15.0 | 60.60 | 25.20 | 1.585 | 1.204 | 0.398 | 0.485 | 238.5 | × |

| H11 | 12.5 | 47.22 | 17.75 | 1.584 | 1.204 | 0.432 | 0.546 | 290.8 | × |

| H12 | 10.0 | 7.71 | 1.581 | 1.205 | × | × | × | × | |

| H13 | 5.0 | 1.01 | 1.443 | 1.205 | × | × | × | × | |

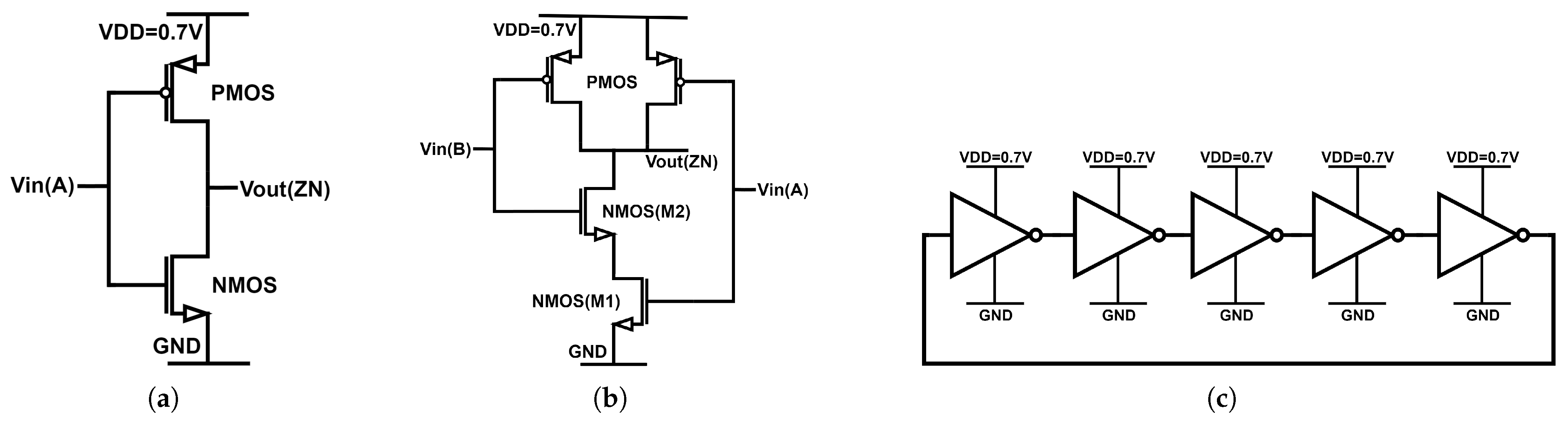

| Label | Case 0 | Case 1 | Case 2 | Case 3 | Case 4 | Case 5 |

|---|---|---|---|---|---|---|

| Device Type | NSFET | NSFET | NSFET | FinFet | FinFet | NSFET |

| Height (nm) | 65 (H0) | 35 (H5) | 20 (H9) | 10 (H12) | 5 (H13) | 5 (H13) |

| On Current (A) | 141.9 | 115.3 | 60.1 | 7.7 | 1.0 |

| Cell: INV = 0.7 V | ||||

|---|---|---|---|---|

| Label | On Current (A) | (V) | (V) | Voltage Offect |

| Case 0 | 141.9 | 0.70 | 0 | 0 |

| Case 1 | 115.3 | 0.70 | 0 | 0 |

| Case 2 | 60.1 | 0.70 | 0 | 0 |

| Case 3 | 7.7 | 0.70 | 0.1229 | 17.6% |

| Case 4 | 1.0 | 0.70 | 0.6419 | 91.7% |

| Case 5 | 0.70 | 0.6985 | 99.8% | |

| Cell: NAND = 0.7 V | ||||

|---|---|---|---|---|

| Label | On Current (A) | (V) | (V) | Voltage Offect |

| Case 0 (M1) | 141.9 | 0.70 | 0.0059 | 0.8% |

| Case 1 (M1) | 115.3 | 0.70 | 0.0085 | 1.2% |

| Case 2 (M1) | 60.1 | 0.70 | 0.0695 | 9.9% |

| Case 3 (M1) | 7.7 | 0.70 | 0.2429 | 34.7% |

| Case 4 (M1) | 1.0 | 0.70 | 0.5987 | 85.5% |

| Case 5 (M1) | 0.70 | 0.6961 | 99.4% | |

| Case 0 (M2) | 141.9 | 0.70 | 0.0058 | 0.8% |

| Case 1 (M2) | 115.3 | 0.70 | 0.0146 | 2.1% |

| Case 2 (M2) | 60.1 | 0.70 | 0.0711 | 10.2% |

| Case 3 (M2) | 7.7 | 0.70 | 0.2648 | 37.8% |

| Case 4 (M2) | 1.0 | 0.70 | 0.5991 | 85.6% |

| Case 5 (M2) | 0.70 | 0.6962 | 99.4% | |

| Cell: 5-Stage RO = 0.5/0.7 V | |||

|---|---|---|---|

| Label | On Current (A) | 0.5 V (ps) | 0.7 V (ps) |

| Case 0 | 141.9 | 8.32 | 5.94 |

| Case 1 | 115.3 | 8.95 | 6.42 |

| Case 2 | 60.1 | 11.2 | 7.53 |

| Case 3 | 7.7 | Functional Failure | 10.57 |

| Case 4 | 1.0 | Functional Failure | Functional Failure |

| Case 5 | Functional Failure | Functional Failure | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ma, M.; Li, C.; Ma, J.; Yang, W.; Li, H.; You, H.; Deen, M.J. Investigation of Source/Drain Height Variation and Its Impacts on FinFET and GAA Nanosheet FET. Electronics 2025, 14, 1091. https://doi.org/10.3390/electronics14061091

Ma M, Li C, Ma J, Yang W, Li H, You H, Deen MJ. Investigation of Source/Drain Height Variation and Its Impacts on FinFET and GAA Nanosheet FET. Electronics. 2025; 14(6):1091. https://doi.org/10.3390/electronics14061091

Chicago/Turabian StyleMa, Mingyu, Cong Li, Jianghao Ma, Wangjun Yang, Haokun Li, Hailong You, and M. Jamal Deen. 2025. "Investigation of Source/Drain Height Variation and Its Impacts on FinFET and GAA Nanosheet FET" Electronics 14, no. 6: 1091. https://doi.org/10.3390/electronics14061091

APA StyleMa, M., Li, C., Ma, J., Yang, W., Li, H., You, H., & Deen, M. J. (2025). Investigation of Source/Drain Height Variation and Its Impacts on FinFET and GAA Nanosheet FET. Electronics, 14(6), 1091. https://doi.org/10.3390/electronics14061091