Fault-Tolerant Control of a Multiphase Series Capacitor Buck Converter in a Master–Slave Configuration for Powering a Particle Accelerator Electromagnet

Abstract

1. Introduction

- (a)

- The load is decoupled from the power grid through the incorporation of an intermediate low-voltage (24 V) battery pack. In this way, it is possible to independently dimension the upstream and downstream parts of the converters. In addition, a better ride-through capability is obtained.

- (b)

- The battery pack enables the recovery of part of the magnet’s energy.

- (c)

- Interleaved pulse width modulation (PWM) reduces the output voltage and current ripples. This helps the system to reach the stringent ppm requirements set for the output current ripple.

- (d)

- Its modularity and the incorporation of redundant DC/DC units make maintenance easier.

2. Operational Requirements of the IT Magnet Powering Application

3. The Effects of Open-Switch Faults in DC/DC Buck Sub-Converters

3.1. Conventional Buck Configuration

3.2. Series Capacitor Buck Configuration

4. Voltage and Current Regulation Approaches for Interleaved Multiphase DC/DC Converters

4.1. Cascaded Closed-Loop Control Approaches

4.2. Master–Slave Closed-Loop Control Approach

5. Proposed Fault-Tolerant Solution

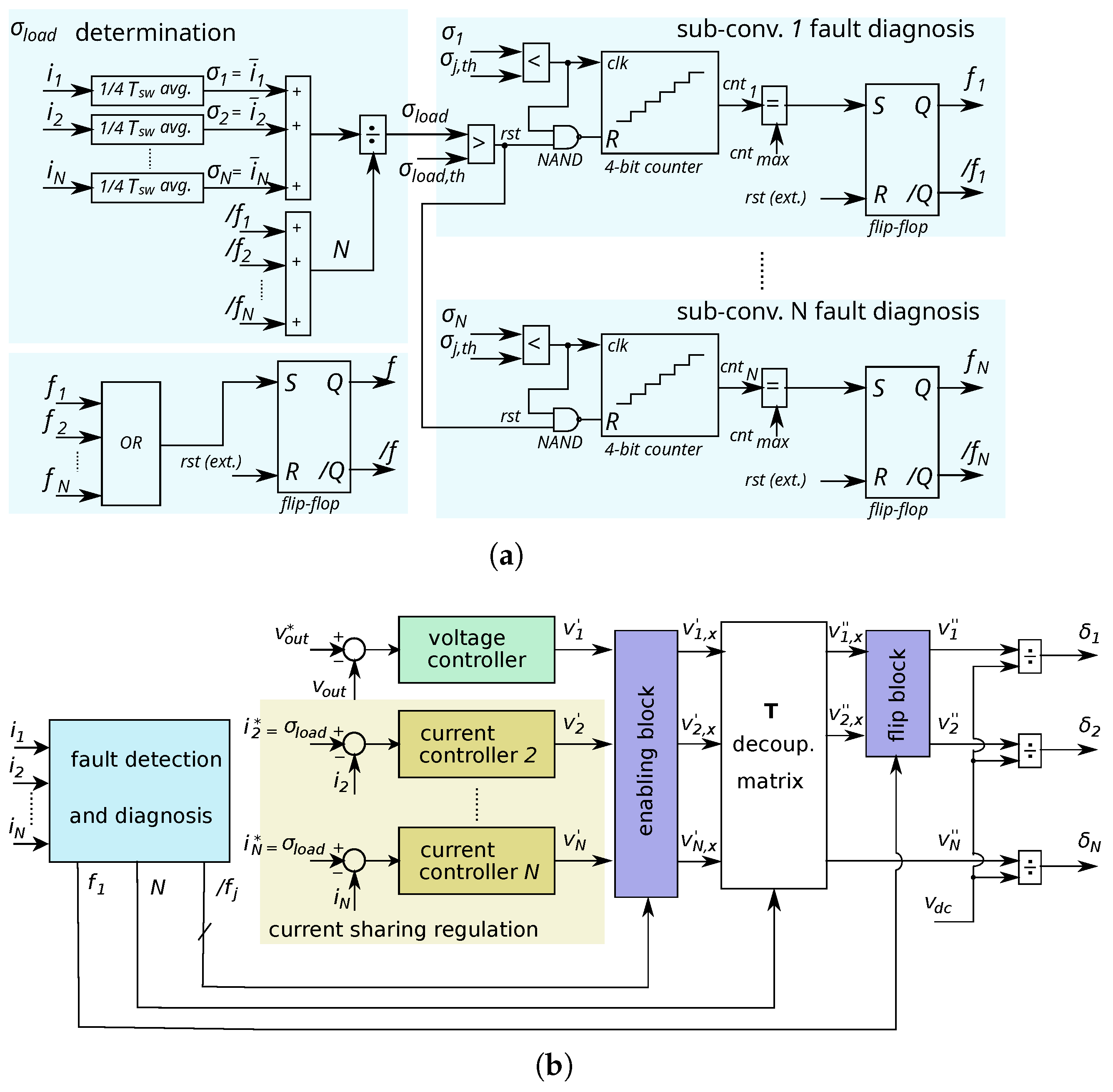

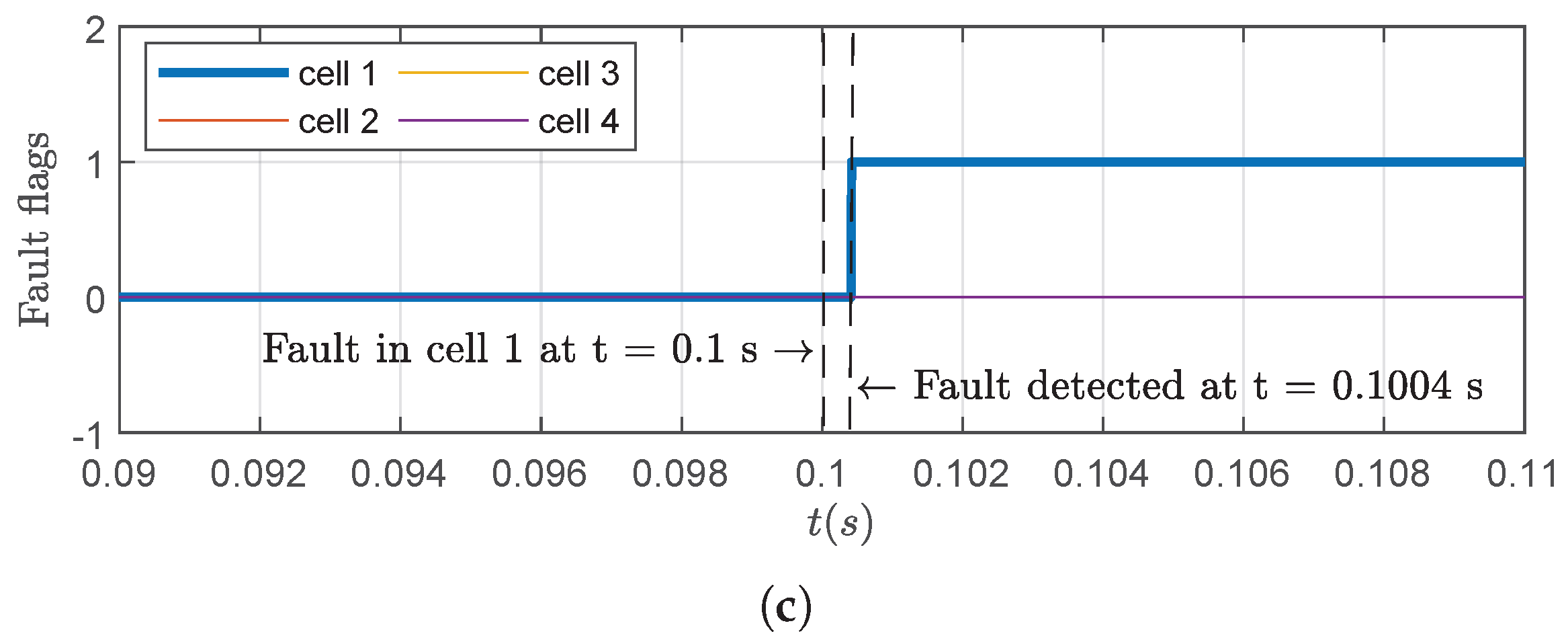

5.1. Open-Circuit Fault Detection and Diagnosis Algorithm Based on the per Sub-Converter Current Analysis

5.2. Post-Fault Controller Reconfiguration

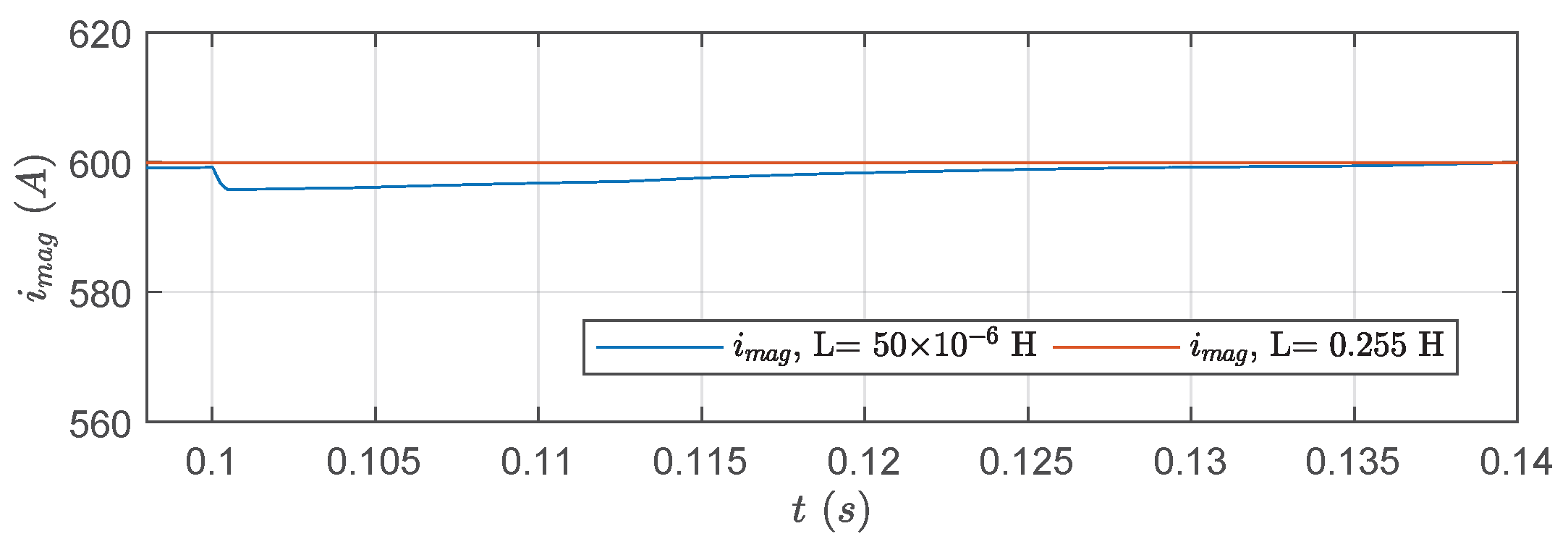

5.3. Dynamics and Stability Considerations of the Controller Under Post-Fault Operating Conditions

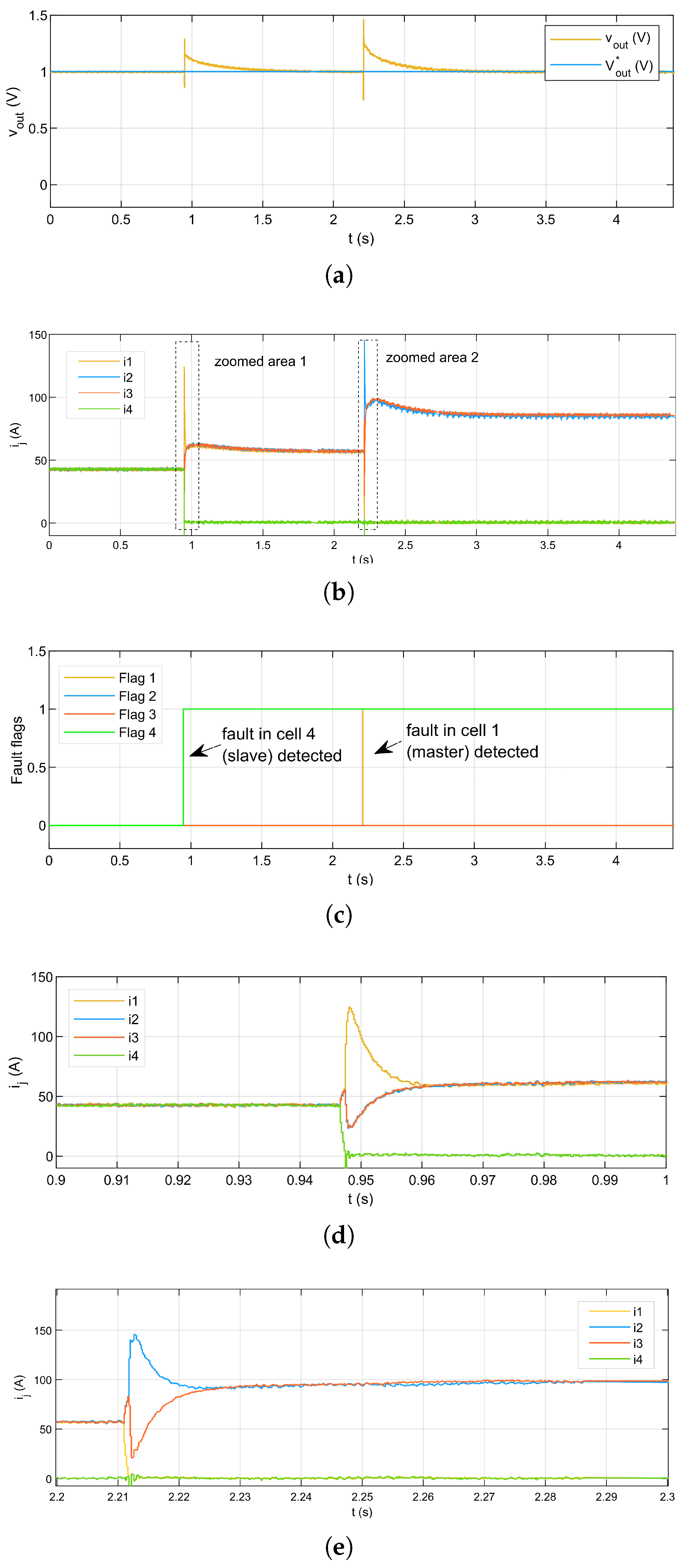

5.4. Simulation Results

6. Experimental Results

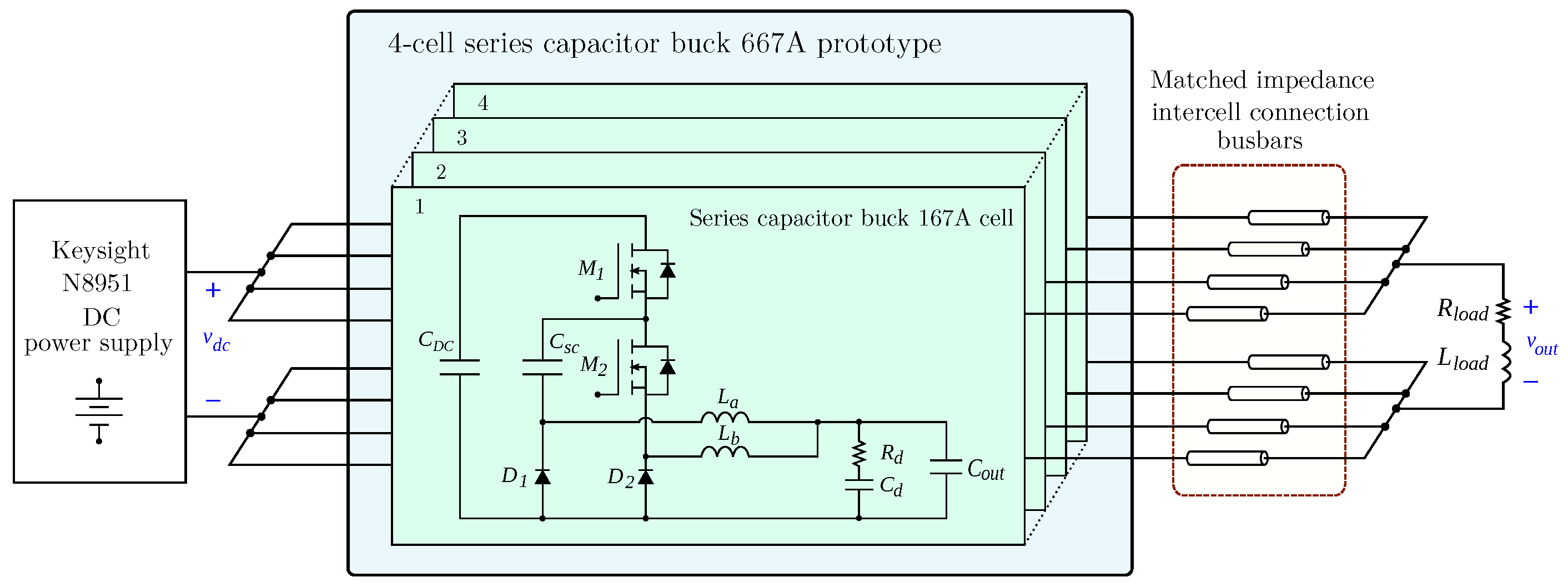

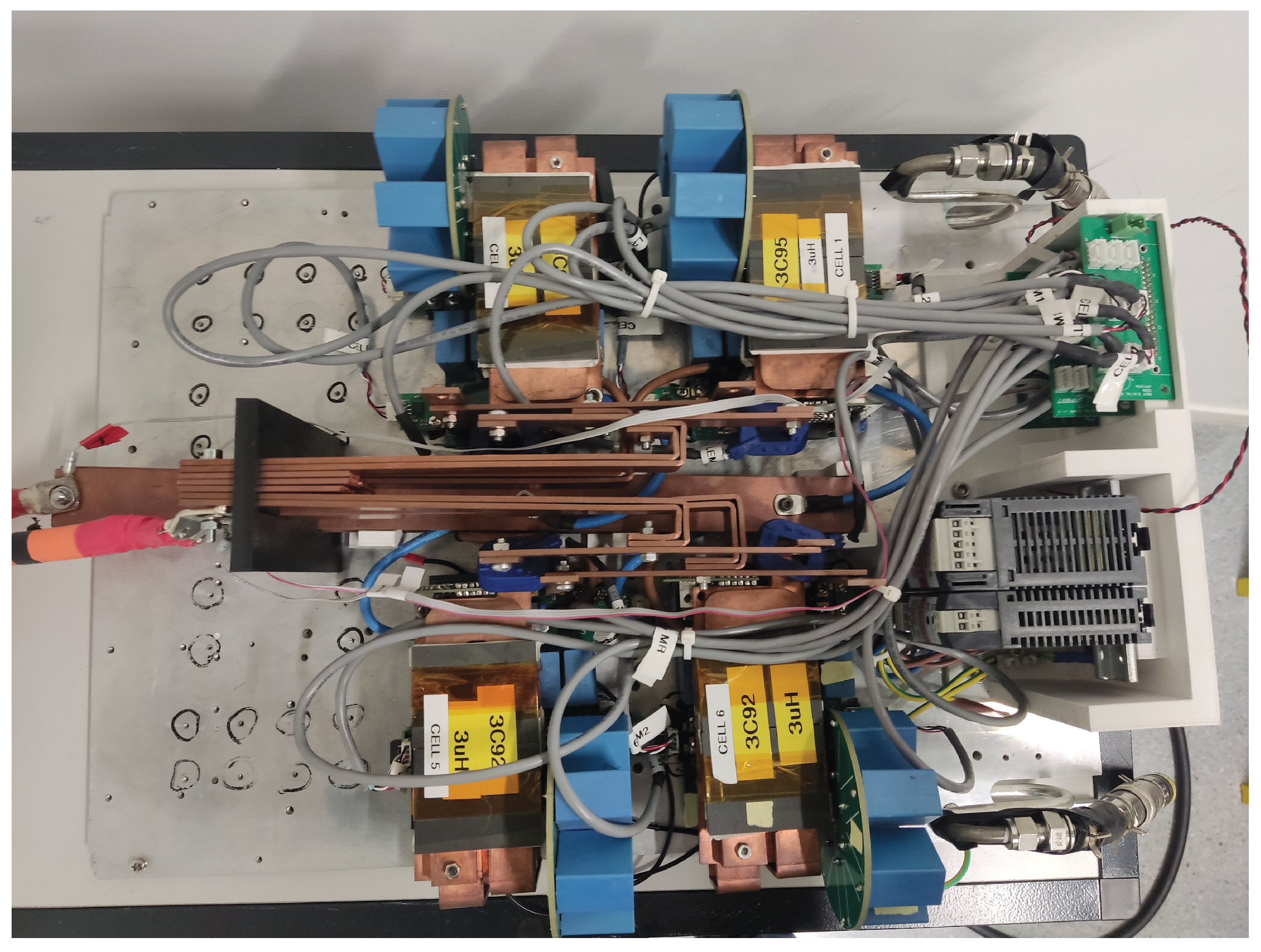

6.1. Experimental Platform Description

6.2. Fault Detection Performance Under Healthy Conditions

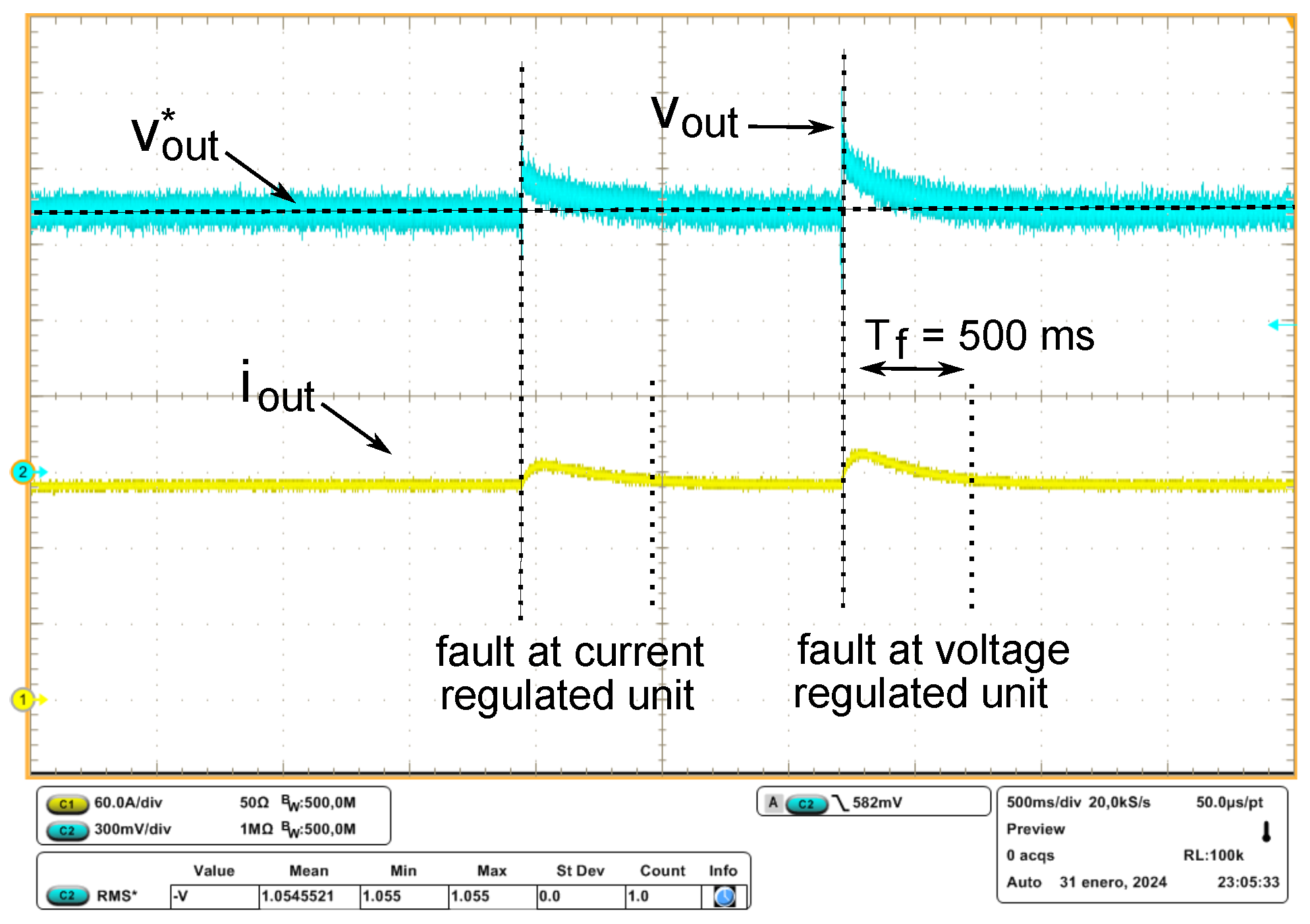

6.3. Fault Detection, Diagnosis, and Control Reconfiguration During Faults

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Coulinge, E.; Pittet, S.; Dujic, D. Design Optimization of Two-Quadrant High-Current Low-Voltage Power Supply. IEEE Trans. Power Electron. 2020, 35, 11602–11611. [Google Scholar] [CrossRef]

- Coulinge, E. High-Current Low-Voltage Power Supply for Superconducting Magnets. Ph.D. Thesis, École Pollytechnique Fédérale de Lausanne, Lausanne, Switzerland, 2020. [Google Scholar]

- Ibarra, E.; Arias, A.; Martínez de Alegría, I.; Otero, A.; de Mallac, L. Digital control of multiphase Series Capacitor Buck converter prototype for the powering of HL-LHC Inner Triplet magnets. IEEE Trans. Ind. Electron. 2021, 69, 10014–10024. [Google Scholar] [CrossRef]

- Wassinger, N.; Maestri, S.; Garcia Retegui, R.; Funes, M.; Antoszczuk, P.; Pittet, S. MOSFET selection for a 18ka modula power converter for HL-LHC inner triplet. Power Electron. Devices Compon. 2023, 6, 100048. [Google Scholar] [CrossRef]

- Cao, D.; Zhang, D.; Kolar, J.; Huber, J. Conceptualization of a cryogenic 250-A power supply for high-temperature-superconducting (HTS) magnets of future particle accelerators. In Proceedings of the International Conference on Power Electronics-ECCE Asia, Jeju, Republic of Korea, 22–25 May 2023; pp. 688–696. [Google Scholar]

- Asimakopoulos, P.; Papastergiou, K.; Thiringer, T.; Bongiorno, M.; Le Godec, G. On Vce method: In situ temperature estimation and aging detection of high-current IGBT modules used in magnet power supplies for particle accelerators. IEEE Trans. Ind. Electron. 2019, 66, 551–560. [Google Scholar] [CrossRef]

- Asimakopoulos, P.; Papastergiou, K.; Thiringer, T.; Bongiorno, M.; Le Godec, G. IGBT power stack integrity assessment method for high-power magnet supplies. IEEE Trans. Power Electron. 2019, 34, 11228–11240. [Google Scholar] [CrossRef]

- Redondo, L.; Kandratsyeu, A.; Barnes, M. Marx Generator Prototype for Kicker Magnets Based on SiC MOSFETs. IEEE Trans. Plasma Sci. 2018, 46, 3334–3339. [Google Scholar] [CrossRef]

- Toscani, A.; Santoro, D.; Delmonte, N.; Cova, P.; Concari, C.; Lanza, A. CHARM facility remotely controlled platform at CERN: A new fault-tolerant redundant architecture. Microelectron. Reliab. 2020, 115, 113950. [Google Scholar] [CrossRef]

- Qingchuan, H.; Wenhua, C.; Jun, P.; Ping, Q. A prognostic method for predicting failure of dc/dc converter. Microelectron. Reliab. 2017, 74, 27–33. [Google Scholar] [CrossRef]

- Ferreira Costa, L.; Liserre, M. Failure analysis of the dc-dc converter. A comprehensive survey of faults and solutions for improving reliability. IEEE Power Electron. Mag. 2018, 5, 42–51. [Google Scholar] [CrossRef]

- Henn, J.; Ludecke, C.; Laumen, M.; Beushausen, S.; Kalker, S.; van der Broeck, C.; Engelmann, G.; de Doncker, R. Intelligent gate drivers for future power converters. IEEE Trans. Power Electron. 2022, 37, 3484–3503. [Google Scholar] [CrossRef]

- Picot-Digoix, M.; Richardeau, F.; Blaquiere, J.; Vinnac, S.; Azzopardi, S.; Le, T. Quasi-flying gate concept used for short-circuit detection on SiC power MOSFETs based on a dual-port gate driver. IEEE Trans. Power Electron. 2023, 38, 6934–6938. [Google Scholar] [CrossRef]

- Ravyts, S.; Van den Broeck, G.; Hallemans, L.; Dalla Vecchia, M.; Driesen, J. Fuse-based short-circuit protection of converter controlled low-voltage DC grids. IEEE Trans. Power Electron. 2020, 35, 11694–11708. [Google Scholar] [CrossRef]

- Wu, J.; Wang, H.; Ma, M.; Chen, Q.; Liang, J. Mode analysis and fault-tolerant method of open-circuit fault for a three-level dual active bridge DC-DC converter. Microelectron. Reliab. 2023, 150, 115100. [Google Scholar] [CrossRef]

- Kumar, G.; Elangovan, D. Review on fault-diagnosis and fault-tolerance for DC-DC converters. IET Power Electron. 2020, 13, 1–13. [Google Scholar] [CrossRef]

- Poon, J.; Jain, P.; Spanos, C.; Panda, S.K.; Sanders, S. Fault prognosis for power electronics systems using adaptive parameter identification. IEEE Trans. Ind. Appl. 2017, 53, 2862–2870. [Google Scholar] [CrossRef]

- Pazouki, E.; Sozer, Y.; De Abreu-Garcia, A. Fault diagnosis and fault-tolerant control operation of nonisolated DC-DC converters. IEEE Trans. Ind. Appl. 2018, 54, 310–320. [Google Scholar] [CrossRef]

- Tang, S.; Yin, X.; Wang, D.; Zhang, C.; Shuai, Z.; Yang, X.; Shen, Z.J.; Wang, J. Detection and identification of power switch failures for fault-tolerant operation of flying capacitor Buck-boost converters. Microelectron. Reliab. 2018, 88–90, 1236–1241. [Google Scholar] [CrossRef]

- Kirshenboim, O.; Vekslender, T.; Peretz, M. Closed-Loop Design and Transient-Mode Control for a Series-Capacitor Buck Converter. IEEE Trans. Power Electron. 2019, 34, 1823–1837. [Google Scholar] [CrossRef]

- Chen, Z.; Zhang, C.; Wu, Y.; Chen, Y.; Zhang, C. Series-Capacitor-Based Buck PFC Converter With High Power Factor and Ultrahigh Step-Down Conversion Ratio. IEEE Trans. Ind. Electron. 2019, 66, 6895–6905. [Google Scholar] [CrossRef]

- Bui, D.; Cha, H.; Nguyen, V. Asymmetrical PWM series-capacitor high-conversion-ratio DC-DC converter. IEEE Trans. Power Electron. 2021, 36, 8628–8633. [Google Scholar] [CrossRef]

- Otero-Olavarrieta, A.; Matallana, A.; Martínez de Alegría, I.; Ibarra, E.; Arias, A.; de Mallac, L.; Pittet, S. Hardware design of a high-current, high step-down ratio Series Capacitor Buck converter prototype for slow-ramped powering of High-Luminosity Large Hadron Collider inner triplet superconducting electromagnets. Appl. Energy 2024, 371, 123730. [Google Scholar] [CrossRef]

- Konstantopoulou, K.; Hurte, J.; Fleiter, J.; Ballarino, A. Electro-magnetic performance of MgB2 cables for the high current transmission lines at CERN. IEEE Trans. Appl. Supercond. 2019, 29, 1–5. [Google Scholar] [CrossRef]

- Younsi, M.; Bendali, M.; Azib, T.; Larouci, C.; Marchand, C.; Coquery, G. Current-sharing control techinique of interleaved buck converter for automotive applications. In Proceedings of the IET International Conference on Power Electronics, Machines and Drives (PEMD), Manchester, UK, 8–10 April 2014; pp. 1–6. [Google Scholar]

- Utkin, V.; Guldner, J.; Shi, J. Sliding Mode Control in Electro-Mechanical Systems; CRC Press: Boca Raton, FL, USA, 2009. [Google Scholar]

- Repecho, V.; Biel, D.; Ramos-Lara, R.; Garcia Vega, P. Fixed-switching frequency interleaved sliding mode eight-phase synchronous Buck converter. IEEE Trans. Power Electron. 2018, 33, 676–688. [Google Scholar] [CrossRef]

- Ribeiro, E.; Marques Cardoso, A.; Boccatelli, C. Open-circuit fault diagnosis in interleaved DC-DC converters. IEEE Trans. Power Electron. 2014, 29, 3091–3102. [Google Scholar] [CrossRef]

- Gleissner, M.; Bakran, M. Design and control of fault-tolerant nonisolated multiphase multilevel DC-DC converters for automotive power systems. IEEE Trans. Ind. Appl. 2016, 52, 1785–1795. [Google Scholar]

- Khojet El Khil, S.; Jlassi, I.; Estima, J.; Mrabet-Bellaaj, N.; Marques Cardoso, A. Detection and isolation of open-switch and current sensor faults in PMSM drives, through stator current analysis. In Proceedings of the IEEE International Symposium on Diagnostic for Electrical Machines, Power Electronics and Drives (SDEMPED), Tinos, Greece, 29 August–1 September 2017; pp. 373–379. [Google Scholar]

- Campos-Delgado, D.; Pecina-Sanchez, J.; Espinoza-Trejo, D.; Arce-Santana, E. Diagnosis of open-switch faults in variable speed drives by stator current analysis and pattern recognition. IET Electr. Power Appl. 2013, 7, 509–522. [Google Scholar] [CrossRef]

| Parameter | Symbol | Value | Units |

|---|---|---|---|

| Number of interleaved SC cells | N | 4 | - |

| Rated total output current | 667 | A | |

| Output current variation rate during transients | 16 | A/s | |

| Maximum output voltage (emergency operation) | 10 | V | |

| Rated output voltage (typical value) * | 4 | V | |

| Maximum output power (emergency operation) | 6.67 | kW | |

| Rated output power (typical value) * | 2.67 | kW |

| Power System Parameters | |||

| Number of cells (N) | 4 | Switching freq. () | 50 kHz |

| Controller frequency () | 50 kS/s | Input voltage () | 24 V |

| DC-link capacitor () | 100 μF | Series capacitor () | 400 μF |

| Output capacitor () | 4.7 mF | Per-cell induc. (, ) | 3.5 μH |

| Load inductor parameters | Control parameters | ||

| Inductance () | 50 μH | Voltage (sim.) | 50 ms |

| Load resistance () | 5 m | Voltage (exp.) | 1 s |

| Current | 5 ms | ||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Ibarra, E.; Arias, A.; Martínez de Alegría, I.; Otero-Olavarrieta, A.; Matallana, A.; de Mallac, L. Fault-Tolerant Control of a Multiphase Series Capacitor Buck Converter in a Master–Slave Configuration for Powering a Particle Accelerator Electromagnet. Electronics 2025, 14, 924. https://doi.org/10.3390/electronics14050924

Ibarra E, Arias A, Martínez de Alegría I, Otero-Olavarrieta A, Matallana A, de Mallac L. Fault-Tolerant Control of a Multiphase Series Capacitor Buck Converter in a Master–Slave Configuration for Powering a Particle Accelerator Electromagnet. Electronics. 2025; 14(5):924. https://doi.org/10.3390/electronics14050924

Chicago/Turabian StyleIbarra, Edorta, Antoni Arias, Iñigo Martínez de Alegría, Alberto Otero-Olavarrieta, Asier Matallana, and Louis de Mallac. 2025. "Fault-Tolerant Control of a Multiphase Series Capacitor Buck Converter in a Master–Slave Configuration for Powering a Particle Accelerator Electromagnet" Electronics 14, no. 5: 924. https://doi.org/10.3390/electronics14050924

APA StyleIbarra, E., Arias, A., Martínez de Alegría, I., Otero-Olavarrieta, A., Matallana, A., & de Mallac, L. (2025). Fault-Tolerant Control of a Multiphase Series Capacitor Buck Converter in a Master–Slave Configuration for Powering a Particle Accelerator Electromagnet. Electronics, 14(5), 924. https://doi.org/10.3390/electronics14050924