A Comprehensive Numerical Analysis of a 2.45 GHz Energy Harvesting Rectenna System and a Proposal for a Figure of Merit for Rectenna Systems †

Abstract

1. Introduction

2. Methods

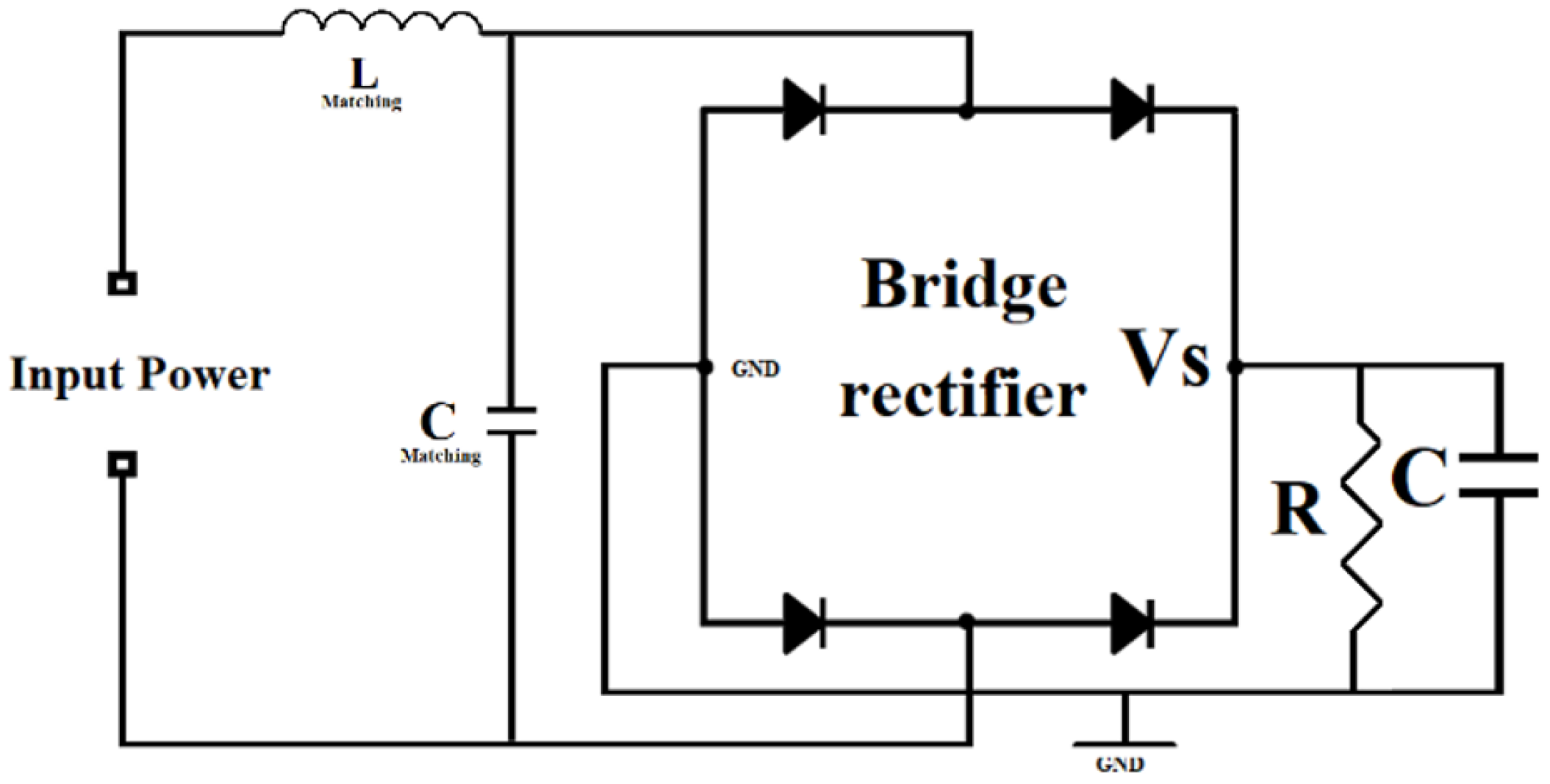

2.1. Bride Rectifier Topologies

2.1.1. Schottky Diode Full-Wave Bridge Rectifier

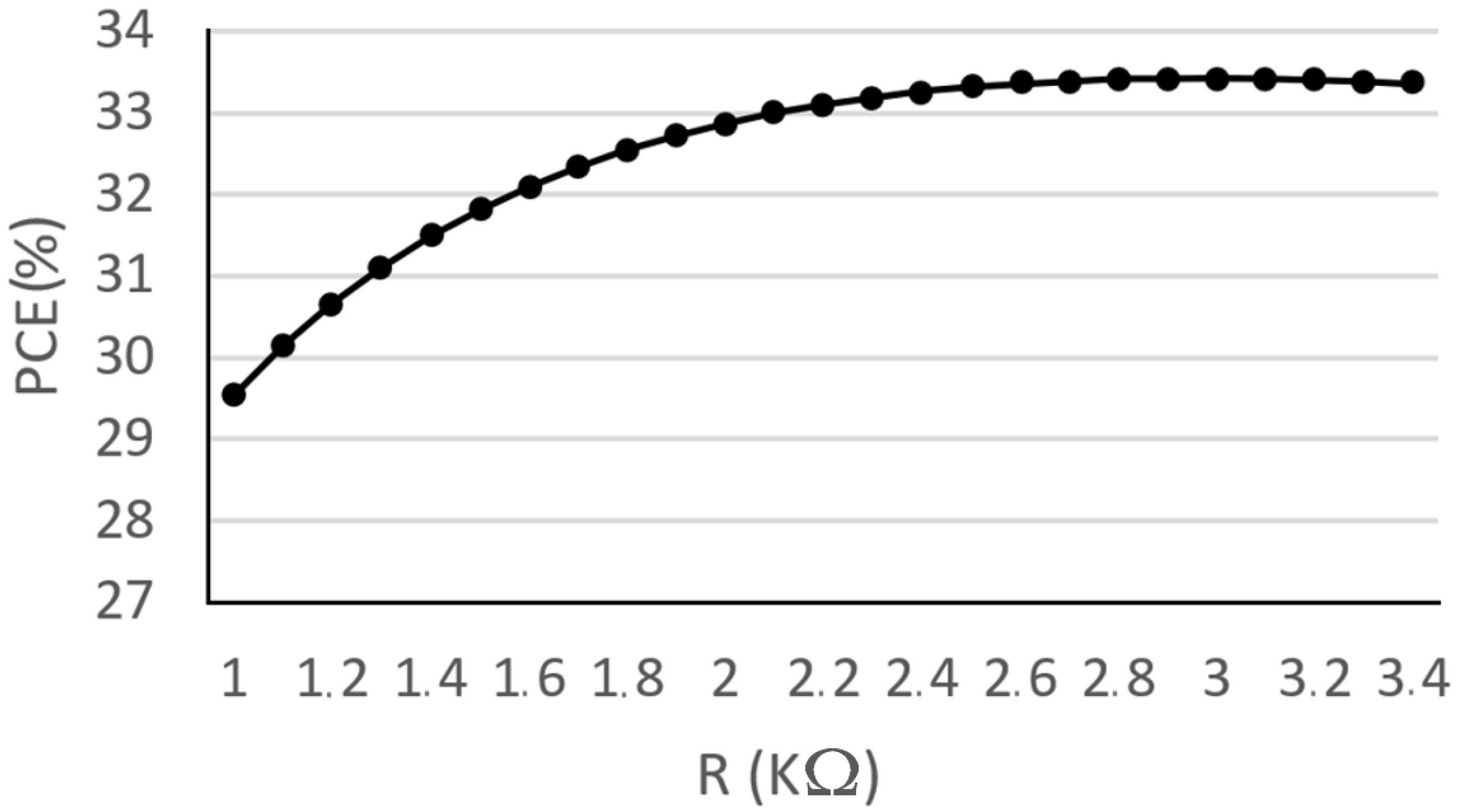

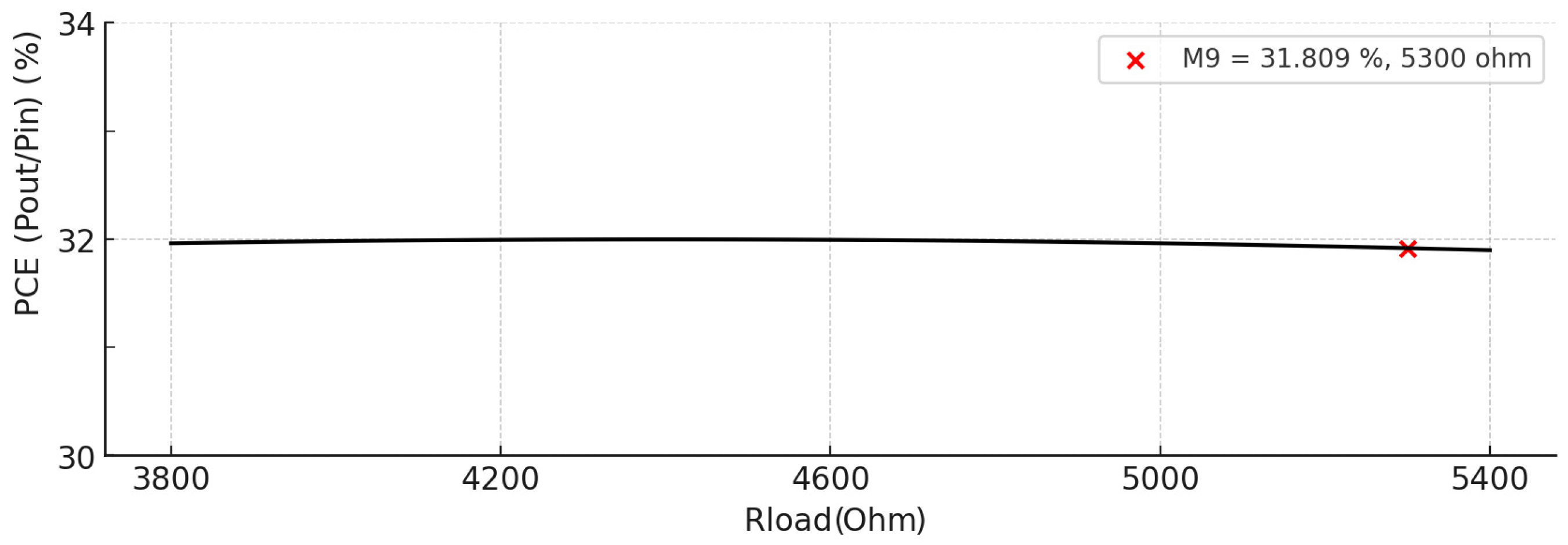

- A simulation was conducted for a bridge rectifier configuration and voltage regulator (Figure 2). This baseline topology served to first identify the ideal R load value in order to obtain the maximum PCE (Pin/Pout). The SPICE model parameters of the HSMS2850 [21] and SMS7630 [22] diode components were incorporated by referring to their corresponding datasheets.

- Simulations and evaluations of different impedance-matching configurations were carried out by using either discrete components or microstrip lines.

- The bridge rectifier printed circuit board was realized.

- A detailed theoretical calculation of the PCE (power conversion efficiency) was compared to the simulation results in order to explain and break down the power conversion phases.

2.1.2. Schottky Diode Voltage Doubler Rectifier

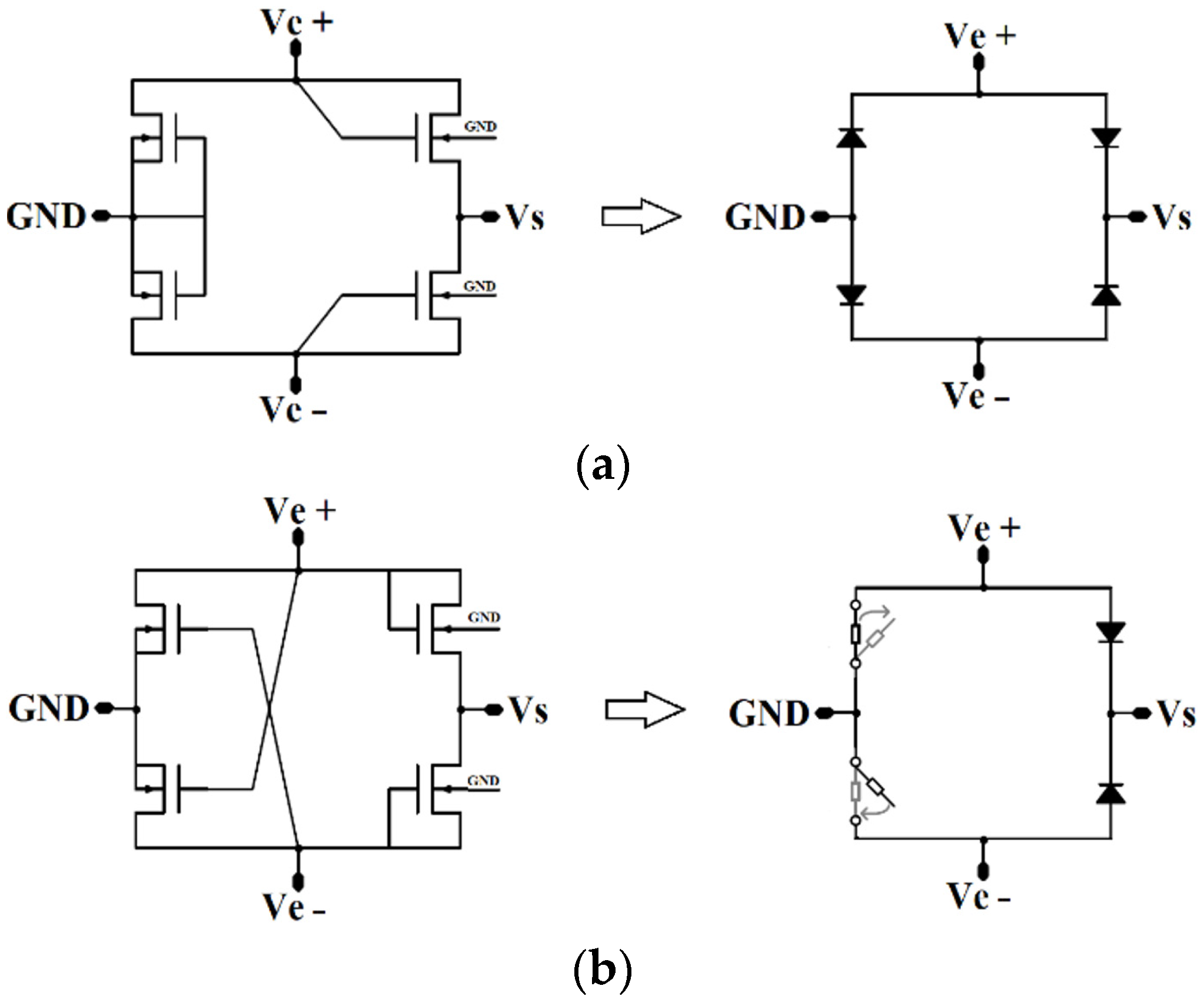

2.1.3. CMOS Technology Bridge Rectifier

2.2. Figure of Merit Approach

- Expert consensus and definition of comparison criteria.

- Data collection and benchmarking.

- Exploratory data analysis (EDA) and preprocessing.

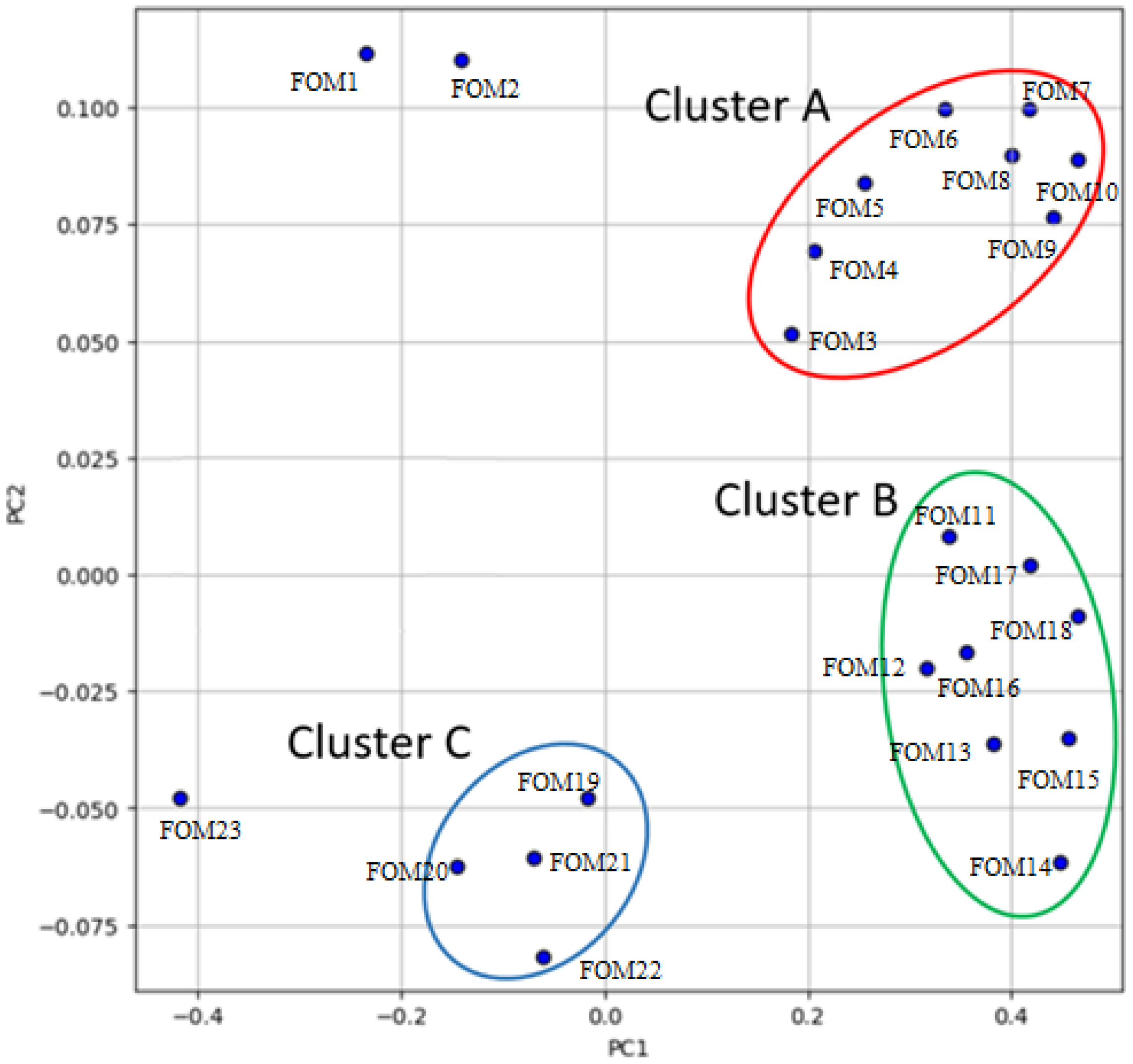

- Application of PCA (principal component analysis).

- Results and loading analysis.

- FOM development guidelines and validation.

2.2.1. Expert Consensus and Definition of Comparison Criteria

2.2.2. Data Collection and Benchmarking

2.2.3. Exploratory Data Analysis and Preprocessing

- Identify missing measurements or data that were impossible to collect.

- Fill the missing data with every criterion mean, making sure not to affect their overall variance.

- Normalize by transforming all collected data into a common scale (for example, Min–Max scaling) to mitigate the influence of variance scales in the modeling.

- Subtract the mean of each criterion from the dataset to center the data on zero.

2.2.4. Application of Principal Component Analysis

- A total of 70% is used as a training panel to build the PCA model [24] (described below).

- A total of 30% is used to validate the FOM (described in Section 2.2.6).

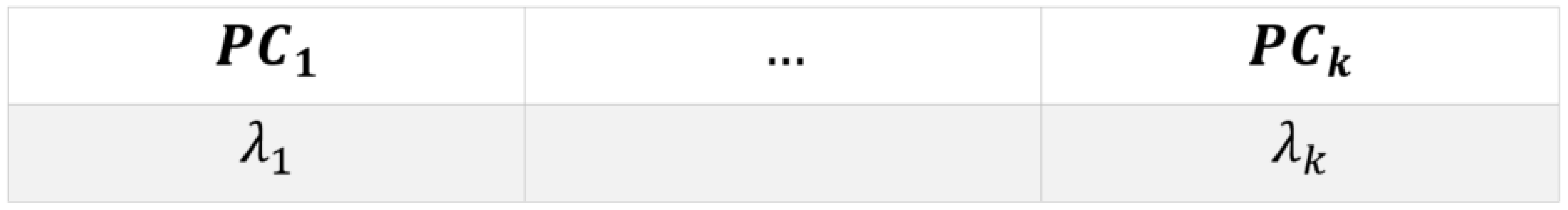

Eigenvalue Decomposition

Dimensionality Reduction

2.2.5. Results and Loading Analysis

2.2.6. Figure of Merit Development Guidelines and Validation

Figure of Merit Development

Figure of Merit Validatio

3. Results and Discussion of Rectenna System Topologies and Technologies Analysis

3.1. Diode Bridge Rectifier

3.1.1. Diode Bridge Rectifier Baseline Simulation

3.1.2. Impedance Matching with Discrete Component Selection for the Bridge Rectifier

3.1.3. Impedance Matching Microstrip Selection for the Bridge Rectifier

3.1.4. Comparison of Impedance Matching Types

3.1.5. Bridge Rectifier Printed Circuit Board Realization

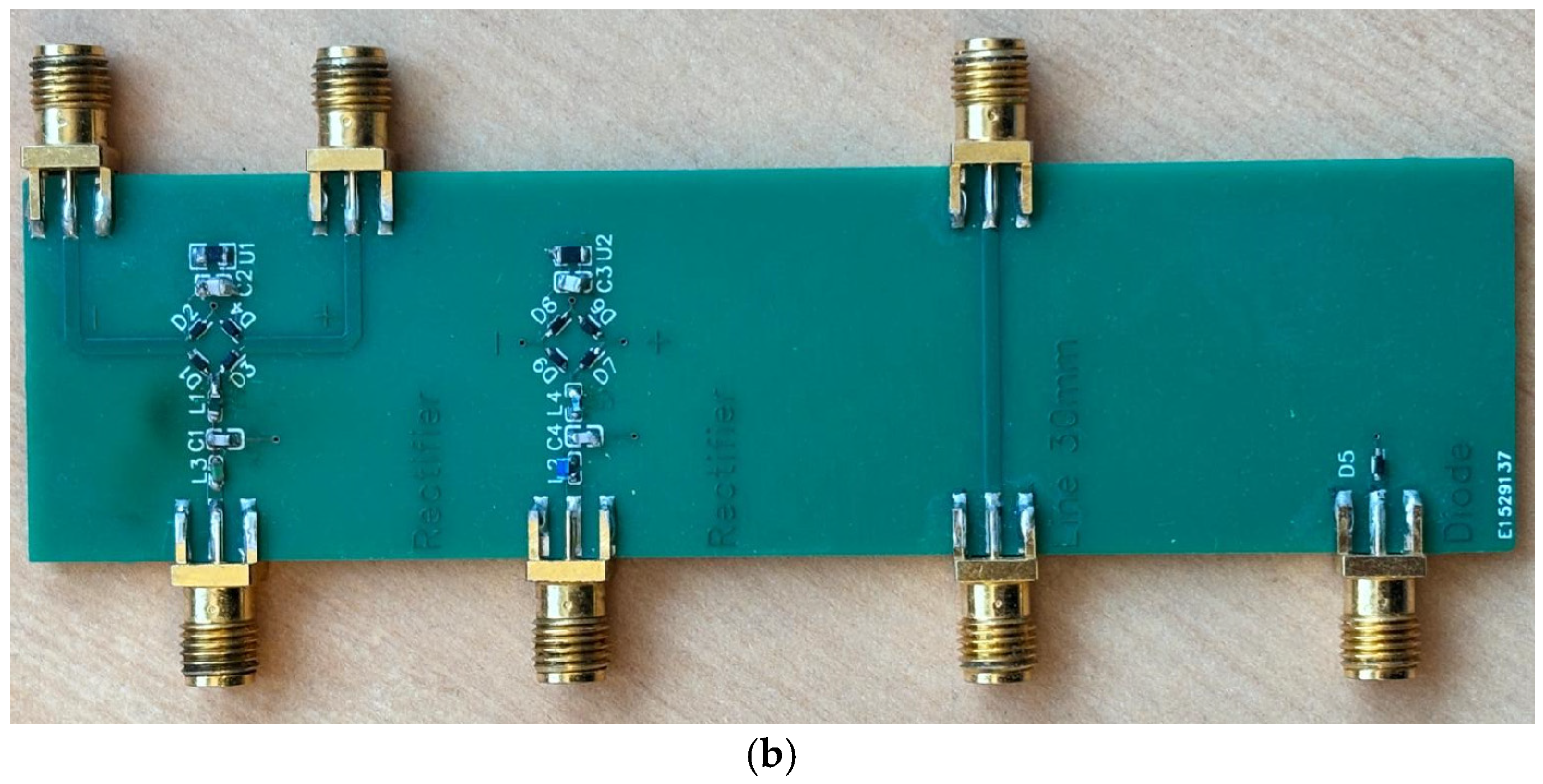

- Addressing matching issues: After adding the microstrip line dimensions and the SMA connectors, we had to fine-tune the input matching by adjusting the original LC impedance matching network, replacing it with an LCL structure to maintain the same level of impedance matching.

- Layout visualization: The final circuit layout was designed using EasyEDA (Figure 10).

- Component placement and microstrip inclusion: The layout included a full diode bridge with SMA connector outputs. A second diode bridge without output SMA connectors was used in case the SMA connectors introduced parasitic effects during measurements. Additionally, a separate 30 mm transmission line segment was added to measure the linear losses associated with the microstrip lines if needed. Finally, a single diode was positioned at the bottom of the layout for individual characterization. The PCB dimensions were 3 cm × 23.6 cm and the rectifier dimensions were 3 cm × 0.7 cm.

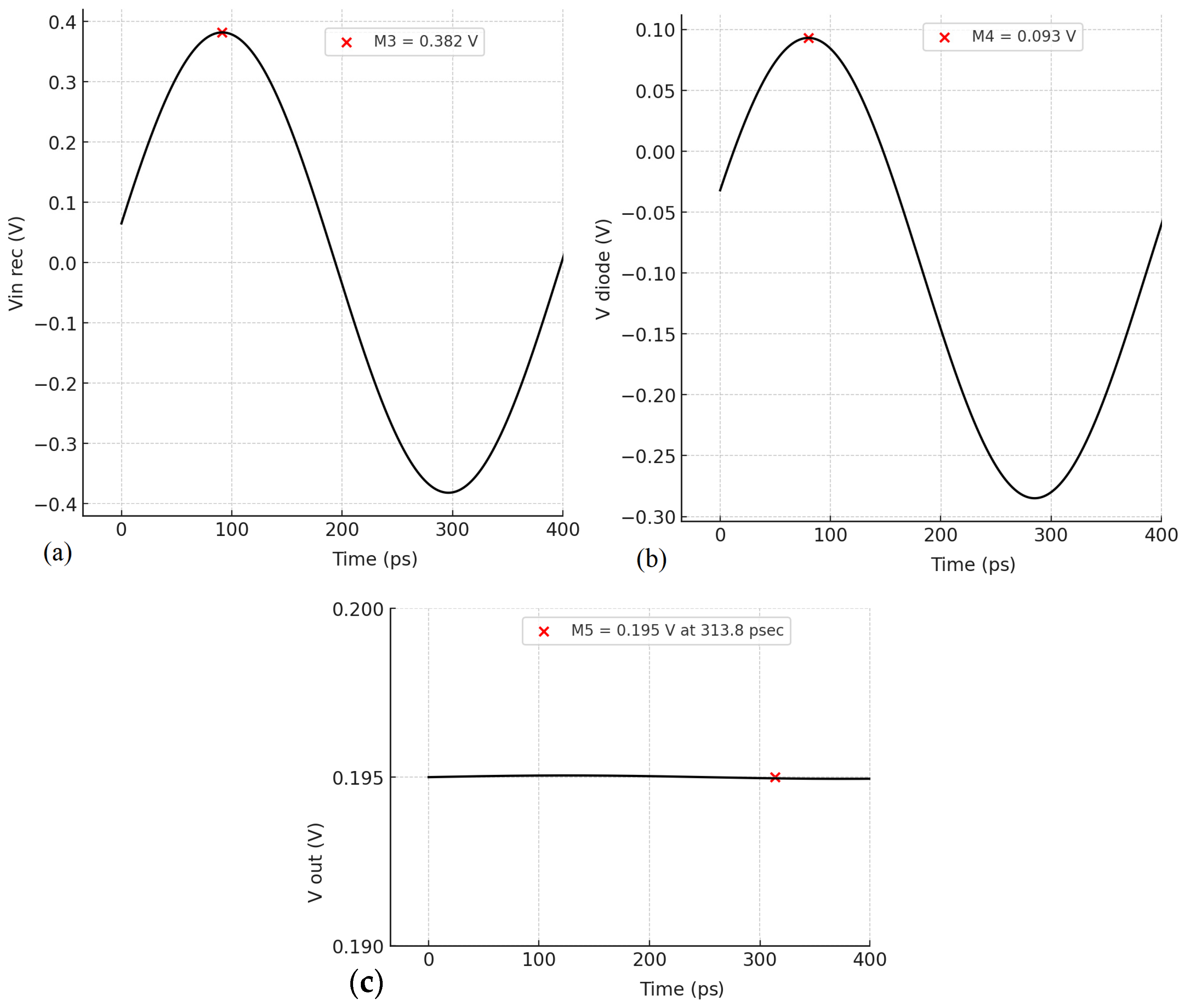

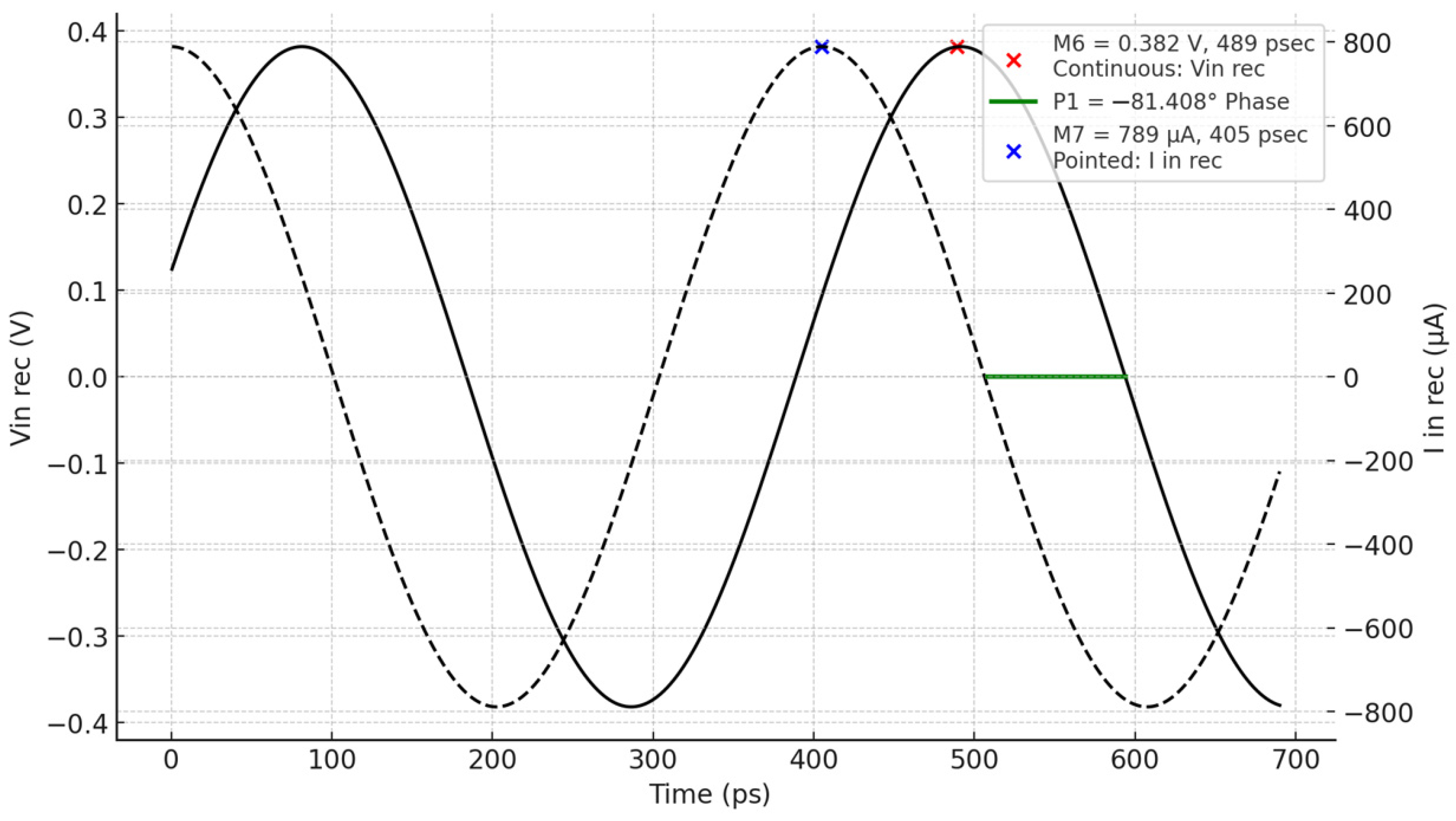

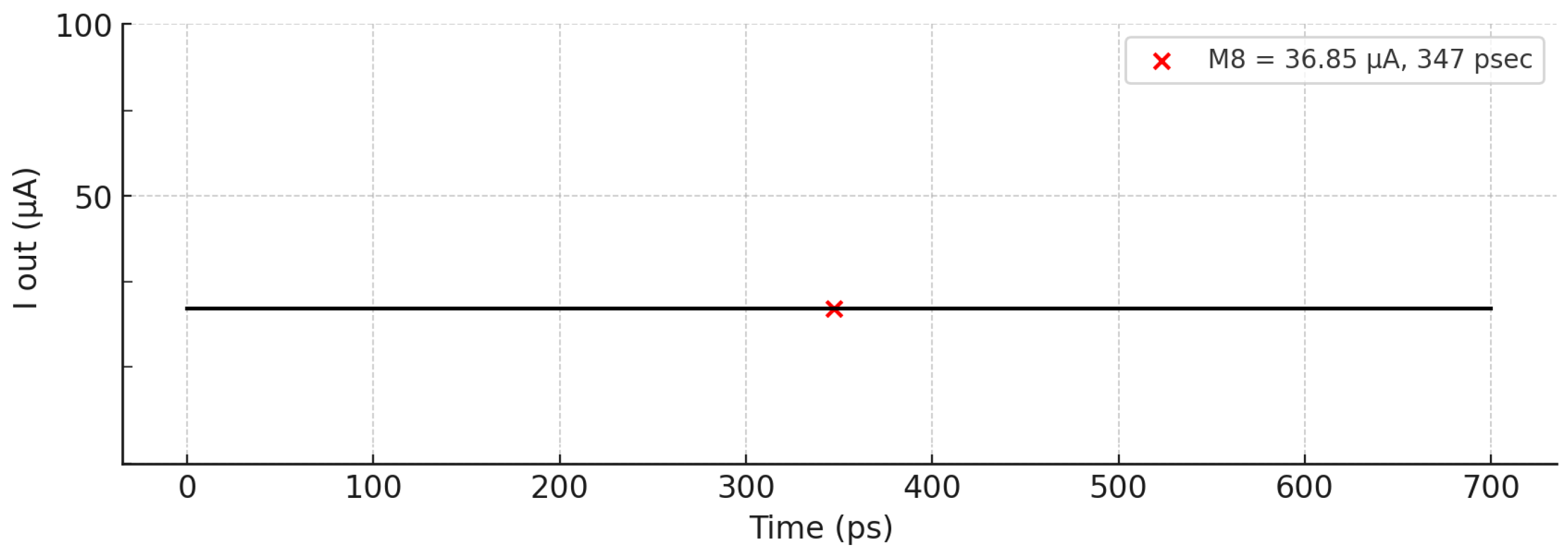

3.1.6. Theoretical Calculation

- is the peak input voltage;

- is the diode peak voltage;

- is the output current at load R.

- is the RMS value of the input voltage, ;

- is the RMS value of the input current, ;

- is the power factor, accounting for the phase shift between the voltage and current.

3.2. Schottky Diode Voltage Doubler Rectifier Results

3.3. CMOS Technology Bridge Rectifier Results

3.3.1. Transistor Characterization

3.3.2. Half-Wave Rectifier Analysis

3.3.3. Full-Wave Bridge Rectifier Analysis

3.4. Comparison of the Different Simulated Circuits and Their Results with the Existing Literature

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sze, S.M. Semiconductor Devices; Pioneering Papers; World Scientific: Singapore; Teaneck, NJ, USA, 1991; pp. 377–380. [Google Scholar]

- Fleming, J.A. Instrument for Converting Alternating Electric Current into Continuous Currents. Patent No. 803,684, 7 November 1905. [Google Scholar]

- Pearson, G.L.; Brattain, W.H. History of semiconductor research. Proc. IRE 1955, 43, 1794–1806. [Google Scholar] [CrossRef]

- Sze, S.M. Physics of Semiconductor Devices, 2nd ed.; Wiley: New York, NY, USA, 1981. [Google Scholar]

- Bougas, I.D.; Papadopoulou, M.S.; Psannis, K.; Sarigiannidis, P.; Goudos, S.K. State-of-the-Art Technologies in RF Energy Harvesting Circuits—A Review. In Proceedings of the 2020 3rd World Symposium on Communication Engineering, Thessaloniki, Greece, 9–11 October 2020. [Google Scholar] [CrossRef]

- Wang, C.; Yang, B.; Shinohara, N. Study and Design of a 2.45-GHz Rectifier Achieving 91% Efficiency at 5-W Input Power. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 76–79. [Google Scholar] [CrossRef]

- Rotenberg, S.A.; Podilchak, S.K.; Re, P.D.H.; Mateo-Segura, C.; Goussetis, G.; Lee, J. Efficient Rectifier for Wireless Power Transmission Systems. IEEE Trans. Microw. Theory Tech. 2020, 68, 1921–1932. [Google Scholar] [CrossRef]

- Bouchair, D.; Boukerroum, F. Performance Analysis of Various Rectifier Topologies for 2.45 GHz RF Energy Harvesting Applications. In Proceedings of the 2023 International Conference on Advances in Electronics, Control and Communication Systems (ICAECCS), Blida, Algeria, 6–7 March 2023; pp. 1–6. [Google Scholar] [CrossRef]

- Halimi, M.A.; Surender, D.; Khan, T. Design of a 2.45 GHz operated Rectifier with 81.5% PCE at 13 dBm Input Power for RFEH/WPT Applications. In Proceedings of the IEEE Indian Conference on Antennas and Propagation, Jaipur, India, 13–16 December 2021. [Google Scholar] [CrossRef]

- Khan, D.; Bassim, M.; Shehzad, K.; Ain, Q.U.; Verna, D.; Asif, M.; Oh, S.J.; Pun, Y.G.; Yoo, S.; Hwang, K.C.; et al. A 2.45 GHZ high efficiency CMOS RF energy harvester with adaptive path control. Electronics 2020, 9, 1107. [Google Scholar] [CrossRef]

- Ghaleb, A.A.A.; Adam, I.; Yasin, M.N.M.; Zambak, M.F.; Yunus, R.N.A.R. A Dualband RF Rectifier for ISM and 5G Applications. In Proceedings of the 2024 IEEE 1st International Conference on Communication Engineering and Emerging Technologies (ICoCET), Kepala Batas, Penang, Malaysia, 2–3 September 2024; pp. 1–4. [Google Scholar] [CrossRef]

- Sedeek, A.; Tammam, E.; Hasaneen, E.-S. Design of an efficient 2.45 GHz RF rectifier for energy harvesting from low RF power density environment. In Proceedings of the 2020 International Conference on Innovative Trends in Communication and Computer Engineering (ITCE), Aswan, Egypt, 8–9 February 2020; pp. 268–271. [Google Scholar] [CrossRef]

- Khan, D.; Oh, S.J.; Shehzad, K.; Verma, D.; Khan, Z.H.N.; Pu, Y.G. A CMOS RF Energy Harvester with 47% Peak Efficiency Using Internal Threshold Voltage Compensation. IEEE Microw. Wirel. Compon. Lett. 2019, 29, 415–417. [Google Scholar] [CrossRef]

- Pandey, A.; Srivastava, A.; Pandey, A.; Sharma, A.; Kumar, R. Highly Efficient 2.45 GHz Rectifier Circuit for RF Energy Harvesting Applications. In Proceedings of the 2023 5th International Conference on Smart Systems and Inventive Technology (ICSSIT), Tirunelveli, India, 23–25 January 2023; pp. 200–203. [Google Scholar] [CrossRef]

- Sung, G.-M.; Chou, H.-Y.; Chen, Z.-W. Radio Frequency Energy Harvesting IC for ISM-915 MHz and 2.45 GHz Wireless Transmitter. In Proceedings of the 2021 IEEE International Future Energy Electronics Conference (IFEEC), Taipei, Taiwan, 16–19 November 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Xu, P.; Flandre, D.; Bol, D. Analysis, Modeling, and Design of a 2.45-GHz RF Energy Harvester for SWIPT IoT Smart Sensors. IEEE J. Solid State Circuits 2019, 54, 2717–2729. [Google Scholar] [CrossRef]

- Coskuner, E.; Garcia-Garcia, J.J. Metamaterial impedance matching network for ambient rf-energy harvesting operating at 2.4 GHz and 5 GHz. Electronics 2021, 10, 1196. [Google Scholar] [CrossRef]

- Vital, D.; Bhardwaj, S.; Volakis, J.L. Textile-Based Large Area RF-Power Harvesting System for Wearable Applications. IEEE Trans. Antennas Propag. 2020, 68, 2323–2331. [Google Scholar] [CrossRef]

- Sidibe, A.; Takacs, A.; Dragomirescu, D.; Charlot, S. Flexible Printed Rectenna Based on a 2.45 GHz CPW Rectifier for Energy Harvesting Applications. In Proceedings of the 2023 53rd European Microwave Conference (EuMC), Berlin, Germany, 19–21 September 2023; pp. 677–680. [Google Scholar] [CrossRef]

- Lau, W.W.Y.; Siek, L. 2.45GHz wide input range CMOS rectifier for RF energy harvesting. In Proceedings of the 2017 IEEE Wireless Power Transfer Conference (WPTC), Taipei, Taiwan, 10–12 May 2017; pp. 1–4. [Google Scholar] [CrossRef]

- AVAGO Technologies. HSMS-285x Series Surface Mount Zero Bias Schottky Detector Diodes; Datasheet; AVAGO Technologies: Singapore, 2009; p. 3. [Google Scholar]

- SKYWORKS. Surface-Mount Mixer and Detector Schottky Diodes Datasheet; Datasheet; SKYWORKS: Sydney, Australia, 2021; p. 4. [Google Scholar]

- Song, F.; Guo, Z.; Mei, D. Feature Selection Using Principal Component Analysis. In Proceedings of the 2010 International Conference on System Science, Engineering Design and Manufacturing Informatization, Yichang, China, 12–14 November 2010. [Google Scholar] [CrossRef]

- Vaswani, N.; Chi, Y.; Bouwmas, T. Rethinking PCA for Modern Data Sets: Theory, Algorithms, and Applications. Proc. IEEE 2018, 106, 1274–1276. [Google Scholar] [CrossRef]

- Koubar, G.; Haddad, F.; Nessakh, B.; Sadek, S.; Rahajandraibe, W. 2.45GHz Low-Power Diode Bridge Rectifier Design. In Proceedings of the 2023 International Conference on Microelectronics (ICM), Abu Dhabi, United Arabe Emirates, 17–20 December 2023. [Google Scholar] [CrossRef]

- ROGERS Corporation. RO4000® Series High Frequency Circuit Materials; Datasheet; ROGERS Corporation: Chandler, AZ, USA, 2022; p. 3. [Google Scholar]

- Koubar, G.; Haddad, F.; Sadek, S.; Rahajandraibe, W. Low power CMOS bridge Rectenna. In Proceedings of the 2022 IEEE Conference on Antenna Measurements and Applications (CAMA), Guangzhou, China, 14–17 December 2022. [Google Scholar] [CrossRef]

| Group A: Power conversion efficiency | M1: Antenna gain M2: Matching network efficiency (Pin/Pavailable) M3: Power conversion efficiency (Pout/Pin) M4: Power factor (Pout/Pavailable) M5: Start-up power (Pin) |

| Group B: Voltage performance | M6: Output voltage (Vout) M7: Start-up voltage (Vin) |

| Group C: Current dynamics and energy storage | M8: Forward vs. reverse current time ratio M9: Isolation between AC input and DC output |

| Group D: Signal quality | M10: Harmonic distortion levels M11: Ripple factor in DC output |

| Group E: Operational stability and reliability | M12: Operating bandwidth M13: Thermal stability |

| Dataset Matrix | M1 | (…) | M13 |

|---|---|---|---|

| Circuit 1 | (…) | (…) | (…) |

| (…) | (…) | (…) | (…) |

| Circuit N | (…) | (…) | (…) |

| Input Power (dBm) | PCE (%) | |

|---|---|---|

| HSMS2850 | −5 | 53 |

| SMS7630 | −5 | 60 |

| HSMS2850 | −15 | 24 |

| SMS7630 | −15 | 33.5 |

| Input Power (dBm) | PCE (RO4350B Line) (%) | PCE (Discrete Components) (%) | |

|---|---|---|---|

| HSMS2850 | −5 | 40 | 49 |

| SMS7630 | −5 | 52 | 57 |

| HSMS2850 | −15 | 16 | 23 |

| SMS7630 | −15 | 29 | 33 |

| Frequency = 2.45 GHz | Topology 1 | Topology 2 | Topology 3 |

|---|---|---|---|

| Input power = −5 dBm | W = 110 µm, C = 10 pF, R = 650 Ω | ||

| PCE (%) | 28 | 40 | 69 |

| Input power = −26 dBm | W = 110 µm, C = 19.95 fF, R = 12.5 KΩ | ||

| PCE (%) | 13 | 17.8 | 43.6 |

| Reference | Input Power (Pin) (dBm) | PCE (%) |

|---|---|---|

| [6] | 37 | 91 |

| [7] | 27 | 75 |

| [8] | 15 | 77 |

| [9] | 13 | 81 |

| [10] | 6 | 45 |

| [11] | 5 | 70 |

| [12] | 3.5 | 74 |

| [13] | 1 | 47 |

| [14] | 0.8 | 52 |

| [15] | 0 | 30 |

| [16] | −3 | 48 |

| [17] | −5 | 41 |

| This work (diode bridge rectifier) | −5 | 57 |

| This work (diode voltage doubler) | −5 | 66 |

| This work (CMOS bridge rectifier) | −5 | 69 |

| [10] | −6 | 20 |

| [18] | −10 | 35 |

| [19] | −10 | 37 |

| [20] | −12 | 59 |

| This work (SMS7630 diode bridge rectifier) | −15 | 33 |

| This work (diode voltage doubler) | −15 | 41.5 |

| [17] | −15 | 27 |

| This work (CMOS bridge rectifier) | −26 | 43 |

| Circuit | Advantages | Disadvantages | PCE |

|---|---|---|---|

| Diodes: full-wave bridge rectifier | High output current and controller ripples | High consumption due to the higher number of diodes (four) | + |

| Diodes: voltage doubler | High voltage output | Risk of ripples on the output | ++ |

| CMOS: full-wave bridge rectifier | Compact design | High cost | +++ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Koubar, G.; Haddad, F.; Gadacha, A.; Sadek, S.; Rahajandraibe, W. A Comprehensive Numerical Analysis of a 2.45 GHz Energy Harvesting Rectenna System and a Proposal for a Figure of Merit for Rectenna Systems. Electronics 2025, 14, 716. https://doi.org/10.3390/electronics14040716

Koubar G, Haddad F, Gadacha A, Sadek S, Rahajandraibe W. A Comprehensive Numerical Analysis of a 2.45 GHz Energy Harvesting Rectenna System and a Proposal for a Figure of Merit for Rectenna Systems. Electronics. 2025; 14(4):716. https://doi.org/10.3390/electronics14040716

Chicago/Turabian StyleKoubar, Gabriel, Fayrouz Haddad, Amine Gadacha, Sawsan Sadek, and Wenceslas Rahajandraibe. 2025. "A Comprehensive Numerical Analysis of a 2.45 GHz Energy Harvesting Rectenna System and a Proposal for a Figure of Merit for Rectenna Systems" Electronics 14, no. 4: 716. https://doi.org/10.3390/electronics14040716

APA StyleKoubar, G., Haddad, F., Gadacha, A., Sadek, S., & Rahajandraibe, W. (2025). A Comprehensive Numerical Analysis of a 2.45 GHz Energy Harvesting Rectenna System and a Proposal for a Figure of Merit for Rectenna Systems. Electronics, 14(4), 716. https://doi.org/10.3390/electronics14040716