Study on Threshold Voltage Drift for SiC MOSFET Under Avalanche Stress

Abstract

1. Introduction

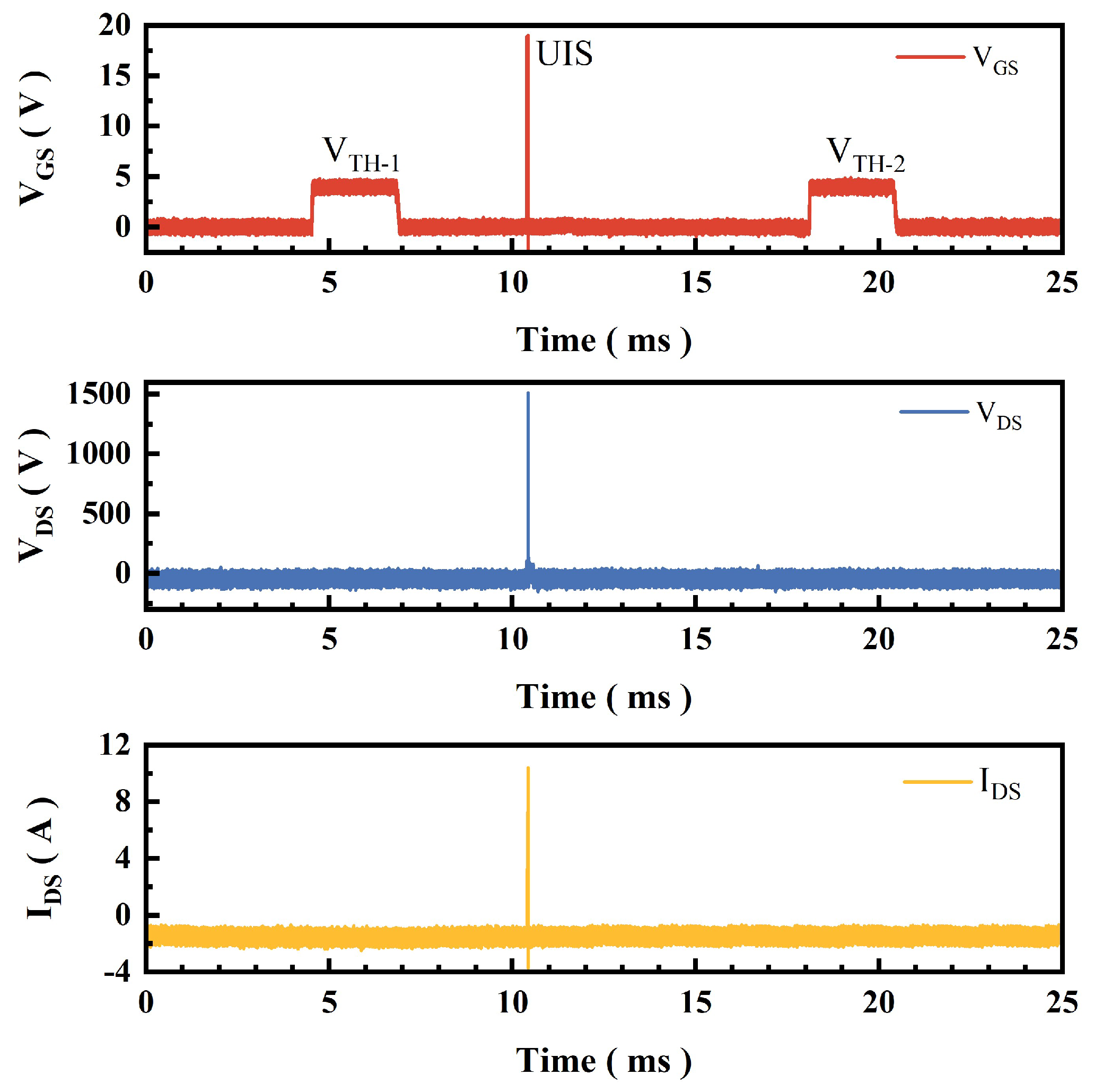

2. Low-Latency VTH Drift Test

3. Experimental Results and Analysis

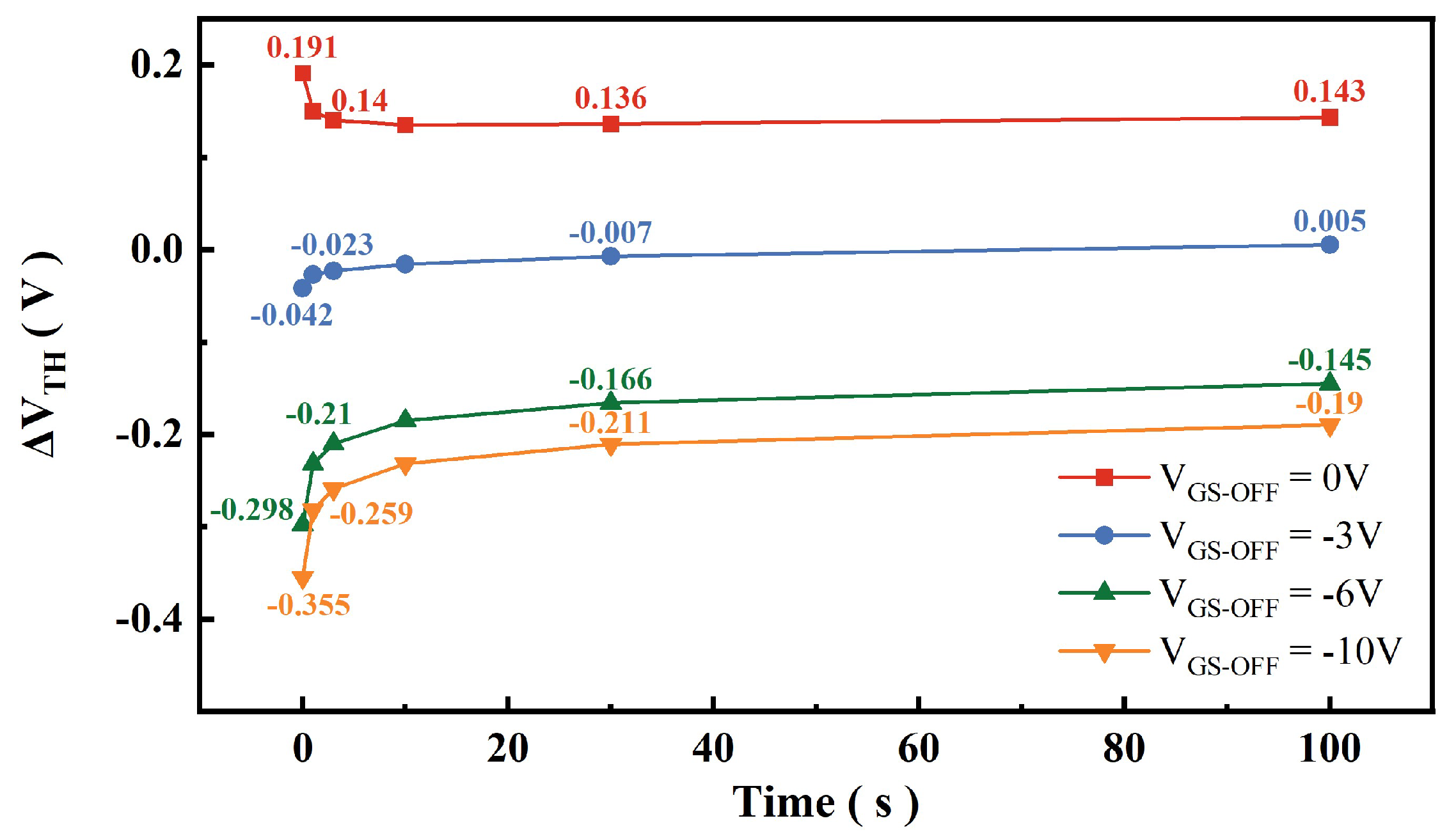

3.1. Single Avalanche Threshold Drift Test

3.2. Multiple Avalanche Threshold Drift Test

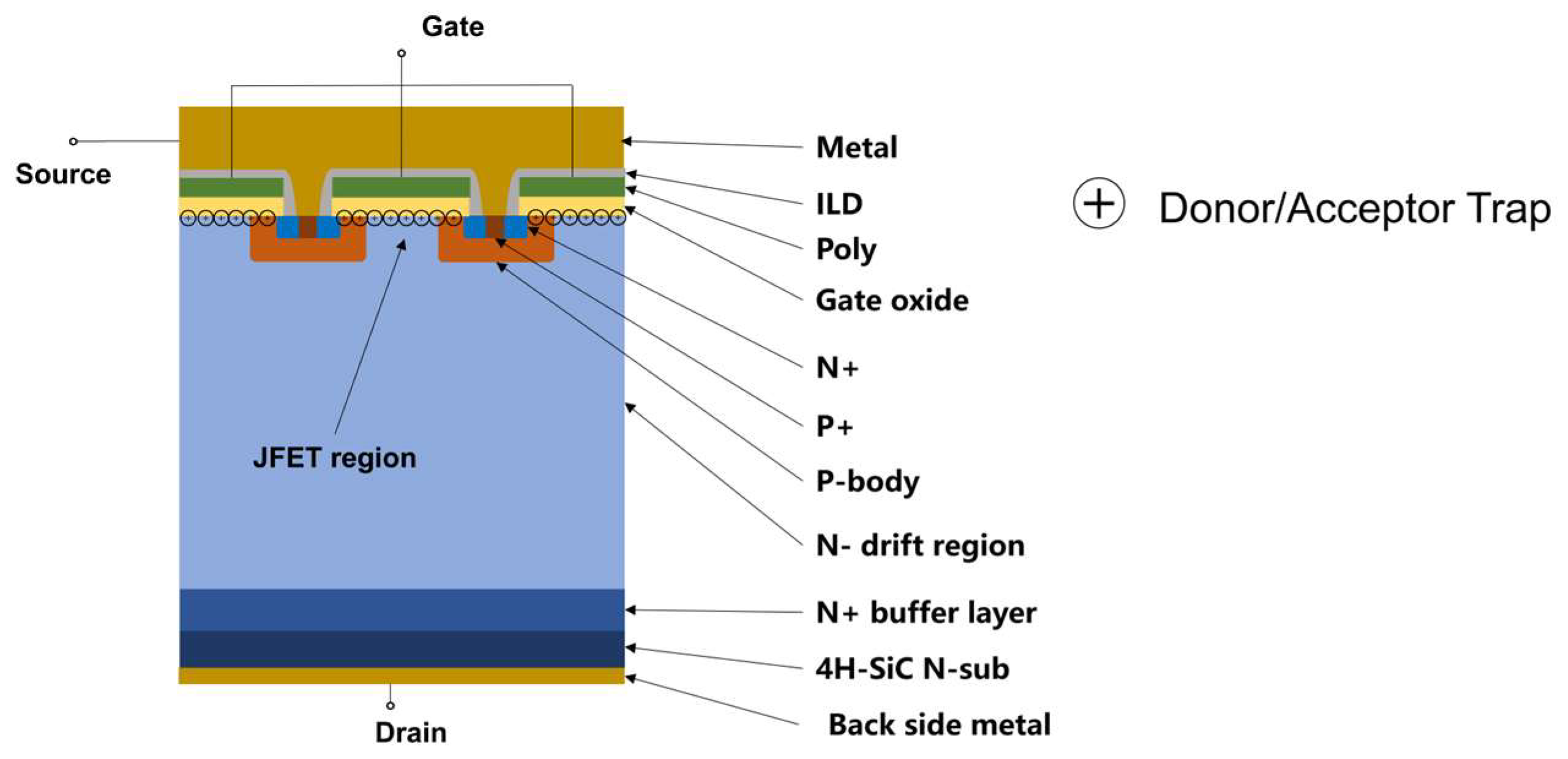

3.3. Mechanism Analysis

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tanimoto, Y.; Saito, A.; Matsuura, K.; Kikuchihara, H.; Jurgen Mattausch, H.; Miura-Mattausch, M.; Kawamoto, N. Power-Loss Prediction of High-Voltage SiC-mosfet Circuits with Compact Model Including Carrier-Trap Influences. IEEE Trans. Power Electron. 2016, 31, 4509–4516. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, M.; Jiang, H.; Wang, H.; Chen, K.J. Dynamic Degradation in SiC Trench MOSFET With a Floating P-Shield Revealed With Numerical Simulations. IEEE Trans. Electron. Devices 2017, 64, 2592–2598. [Google Scholar] [CrossRef]

- Ouaida, R.; Berthou, M.; Leon, J.; Perpina, X.; Oge, S.; Brosselard, P.; Joubert, C. Gate Oxide Degradation of SiC MOSFET in Switching Conditions. IEEE Electron. Device Lett. 2014, 35, 1284–1286. [Google Scholar] [CrossRef]

- Vobecký, J. The Current Status of Power Semiconductors. Facta Univ. Ser. Electron. Energ. 2015, 28, 193–203. [Google Scholar] [CrossRef]

- Shi, Y.; Xie, R.; Wang, L.; Shi, Y.; Li, H. Switching Characterization and Short-Circuit Protection of 1200 V SiC MOSFET T-Type Module in PV Inverter Application. IEEE Trans. Ind. Electron. 2017, 64, 9135–9143. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.; Liang, Z.; Costinett, D.; Blalock, B.J. Temperature-Dependent Short-Circuit Capability of Silicon Carbide Power MOSFETs. IEEE Trans. Power Electron. 2016, 31, 1555–1566. [Google Scholar] [CrossRef]

- Fayyaz, A.; Romano, G.; Castellazzi, A. Body Diode Reliability Investigation of SiC Power MOSFETs. Microelectron. Reliab. 2016, 64, 530–534. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B.; El, M. Basic Mechanisms of Threshold-Voltage Instability and Implications for Reliability Testing of SiC MOSFETs. IEEE Trans. Electron. Devices 2015, 62, 316–323. [Google Scholar] [CrossRef]

- Wei, J.; Liu, S.; Li, S.; Fang, J.; Li, T.; Sun, W. Comprehensive Investigations on Degradations of Dynamic Characteristics for SiC Power MOSFETs Under Repetitive Avalanche Shocks. IEEE Trans. Power Electron. 2019, 34, 2748–2757. [Google Scholar] [CrossRef]

- Fayyaz, A.; Yang, L.; Riccio, M.; Castellazzi, A.; Irace, A. Single Pulse Avalanche Robustness and Repetitive Stress Ageing of SiC Power MOSFETs. Microelectron. Reliab. 2014, 54, 2185–2190. [Google Scholar] [CrossRef]

- Castellazzi, A.; Fayyaz, A.; Yang, L. Characterization of High-Voltage SiC MOSFETs under UIS Avalanche Stress. In Proceedings of the 7th IET International Conference on Power Electronics, Machines and Drives (PEMD 2014), Manchester, UK, 8–10 April 2014; Institution of Engineering and Technology: Manchester, UK, 2014; p. 1.5.02. [Google Scholar]

- Liu, S.; Sun, W.; Qian, Q.; Gu, C.; Huang, Y.; Bai, S.; Chen, G.; Huang, R.; Tao, Y.; Liu, A. Investigations on Degradation and Optimization of 1.2kV 4H-SiC MOSFET under Repetitive Unclamped Inductive Switching Stress. In Proceedings of the 2015 IEEE 27th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hong Kong, China, 10–14 May 2015; IEEE: Hong Kong, China, 2015; pp. 205–208. [Google Scholar]

- Shi, L.; Qian, J.; Jin, M.; Bhattacharya, M.; Houshmand, S.; Yu, H.; Shimbori, A.; White, M.H.; Agarwal, A.K. Gate Oxide Reliability in Silicon Carbide Planar and Trench Metal-Oxide-Semiconductor Field-Effect Transistors Under Positive and Negative Electric Field Stress. Electronics 2024, 13, 4516. [Google Scholar] [CrossRef]

- Yen, C.-T.; Hung, C.-C.; Hung, H.-T.; Lee, C.-Y.; Lee, L.-S.; Huang, Y.-F.; Hsu, F.-J. Negative Bias Temperature Instability of SiC MOSFET Induced by Interface Trap Assisted Hole Trapping. Appl. Phys. Lett. 2016, 108, 012106. [Google Scholar] [CrossRef]

- Qian, J.; Shi, L.; Jin, M.; Bhattacharya, M.; Yu, H.; White, M.H.; Agarwal, A.K.; Shimbori, A.; Liu, T.; Zhu, S. Investigation of the Electron Trapping in Commercial Thick Silicon Dioxides Thermally Grown on 4H-SiC under the Constant Current Stress. In Proceedings of the 2024 IEEE International Reliability Physics Symposium (IRPS), Grapevine, TX, USA, 14–18 April 2024; IEEE: Grapevine, TX, USA, 2024; pp. 1–6. [Google Scholar]

- Qian, J.; Shi, L.; Jin, M.; Bhattacharya, M.; Shimbori, A.; Yu, H.; Houshmand, S.; White, M.H.; Agarwal, A.K. Modeling of Charge-to-Breakdown with an Electron Trapping Model for Analysis of Thermal Gate Oxide Failure Mechanism in SiC Power MOSFETs. Materials 2024, 17, 1455. [Google Scholar] [CrossRef] [PubMed]

- Zhang, H.; Kang, X.; Zheng, Y.; Wu, H.; Wei, K.; Liu, X.; Ye, T.; Jin, Z. Investigation on Dynamic Characteristics of AlGaN/GaN Lateral Schottky Barrier Diode. Micromachines 2021, 12, 1296. [Google Scholar] [CrossRef] [PubMed]

- Xu, Y.; Li, Z.; Yang, X.; Shi, L.; Zhang, P.; Cao, X.; Nie, J.; Wu, S.; Zhang, J.; Feng, Y.; et al. Migration of Carbon from Ga Sites to N Sites in GaN: A Combined PAS and Hybrid DFT Study. Jpn. J. Appl. Phys. 2019, 58, 090901. [Google Scholar] [CrossRef]

- Maresca, L.; Matacena, I.; Riccio, M.; Irace, A.; Breglio, G.; Daliento, S. Influence of the SiC/SiO2 SiC MOSFET Interface Traps Distribution on C–V. Measurements Evaluated by TCAD Simulations. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 2171–2179. [Google Scholar] [CrossRef]

- Majdi, S.; Gabrysch, M.; Suntornwipat, N.; Burmeister, F.; Jonsson, R.; Kovi, K.K.; Hallén, A. High-Temperature Deep-Level Transient Spectroscopy System for Defect Studies in Wide-Bandgap Semiconductors. Rev. Sci. Instrum. 2019, 90, 063903. [Google Scholar] [CrossRef] [PubMed]

- Buffolo, M.; Favero, D.; Marcuzzi, A.; De Santi, C.; Meneghesso, G.; Zanoni, E.; Meneghini, M. Review and Outlook on GaN and SiC Power Devices: Industrial State-of-the-Art, Applications, and Perspectives. IEEE Trans. Electron. Devices 2024, 71, 1344–1355. [Google Scholar] [CrossRef]

- Wei, Z.; Wei, J.; Fu, H.; Huang, L.; Tian, Y.; Cao, J.; Zhu, X.; Sun, J.; Liu, H.; Wang, Q.; et al. Suppression Effect of Split-Gate Structure on Repetitive Avalanche Stress Induced Degradation for SiC MOSFETs. IEEE Trans. Electron. Devices 2024, 71, 6596–6603. [Google Scholar] [CrossRef]

| VGS-OFF (V) | VTH-1 (V) | VTH-2 (V) | ΔVTH (V) |

|---|---|---|---|

| 0 | 2.773 | 2.883 | 0.110 |

| −3 | 2.734 | 2.658 | −0.075 |

| −6 | 2.762 | 2.542 | −0.220 |

| −10 | 2.795 | 2.569 | −0.226 |

| VGS-OFF (V) | VTH-1 (V) | VTH-2 (V) | ΔVTH (V) |

|---|---|---|---|

| 0 | 2.683 | 2.873 | 0.191 |

| −3 | 2.677 | 2.636 | −0.042 |

| −6 | 2.788 | 2.490 | −0.298 |

| −10 | 2.824 | 2.470 | −0.355 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, H.; Cai, L.; Fan, C.; Liu, H.; Yan, S.; Zhao, R.; Yuan, P. Study on Threshold Voltage Drift for SiC MOSFET Under Avalanche Stress. Electronics 2025, 14, 4511. https://doi.org/10.3390/electronics14224511

Zhang H, Cai L, Fan C, Liu H, Yan S, Zhao R, Yuan P. Study on Threshold Voltage Drift for SiC MOSFET Under Avalanche Stress. Electronics. 2025; 14(22):4511. https://doi.org/10.3390/electronics14224511

Chicago/Turabian StyleZhang, Haitao, Lin Cai, Chen Fan, Huipeng Liu, Su Yan, Rikang Zhao, and Pengpeng Yuan. 2025. "Study on Threshold Voltage Drift for SiC MOSFET Under Avalanche Stress" Electronics 14, no. 22: 4511. https://doi.org/10.3390/electronics14224511

APA StyleZhang, H., Cai, L., Fan, C., Liu, H., Yan, S., Zhao, R., & Yuan, P. (2025). Study on Threshold Voltage Drift for SiC MOSFET Under Avalanche Stress. Electronics, 14(22), 4511. https://doi.org/10.3390/electronics14224511