Investigation of Reliability Strengthening by Six-Sided Protective Structure in Fan-Out Wafer-Level Packaging

Abstract

1. Introduction

2. Materials and Methods

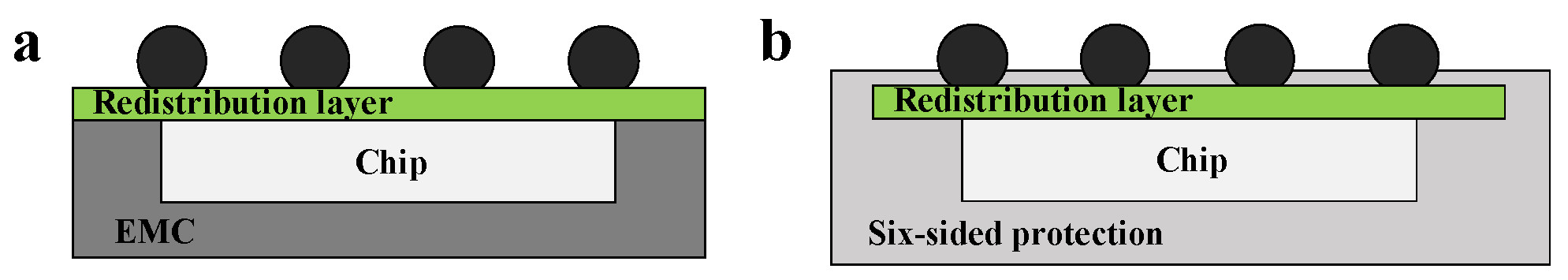

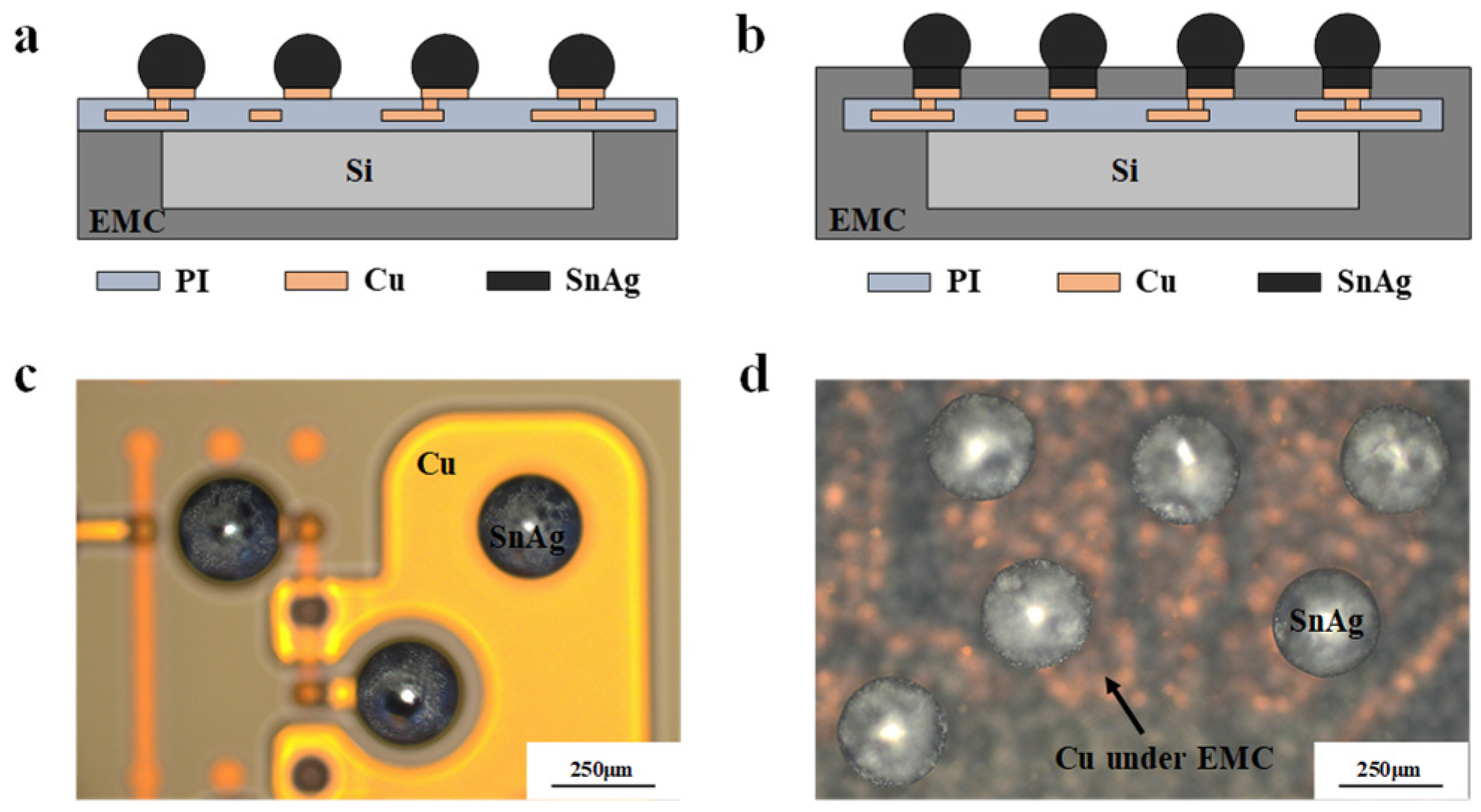

2.1. FOWLP Device

2.2. Shear Test

2.3. Reliability Test

2.4. Finite Element Simulation

3. Results and Discussion

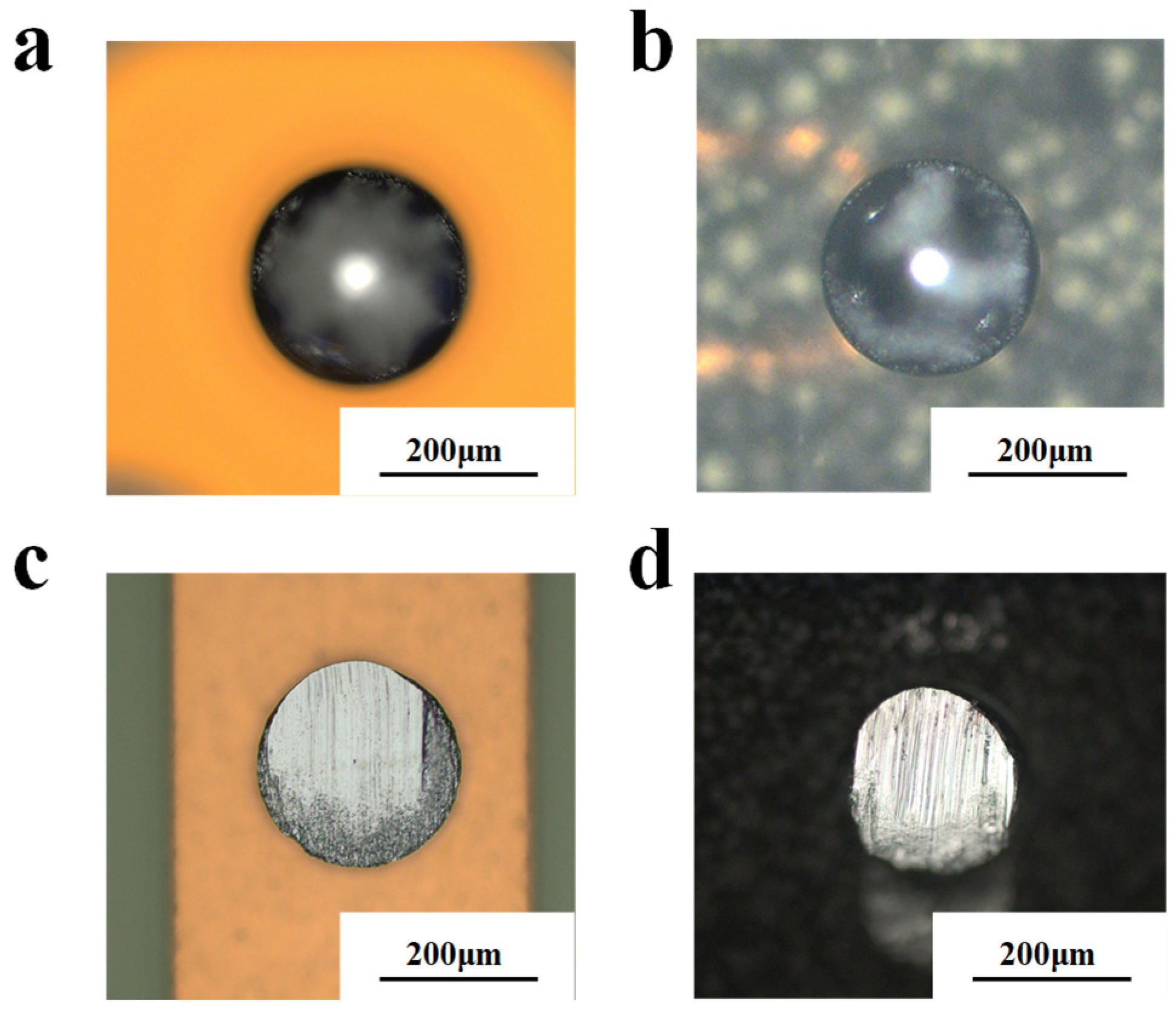

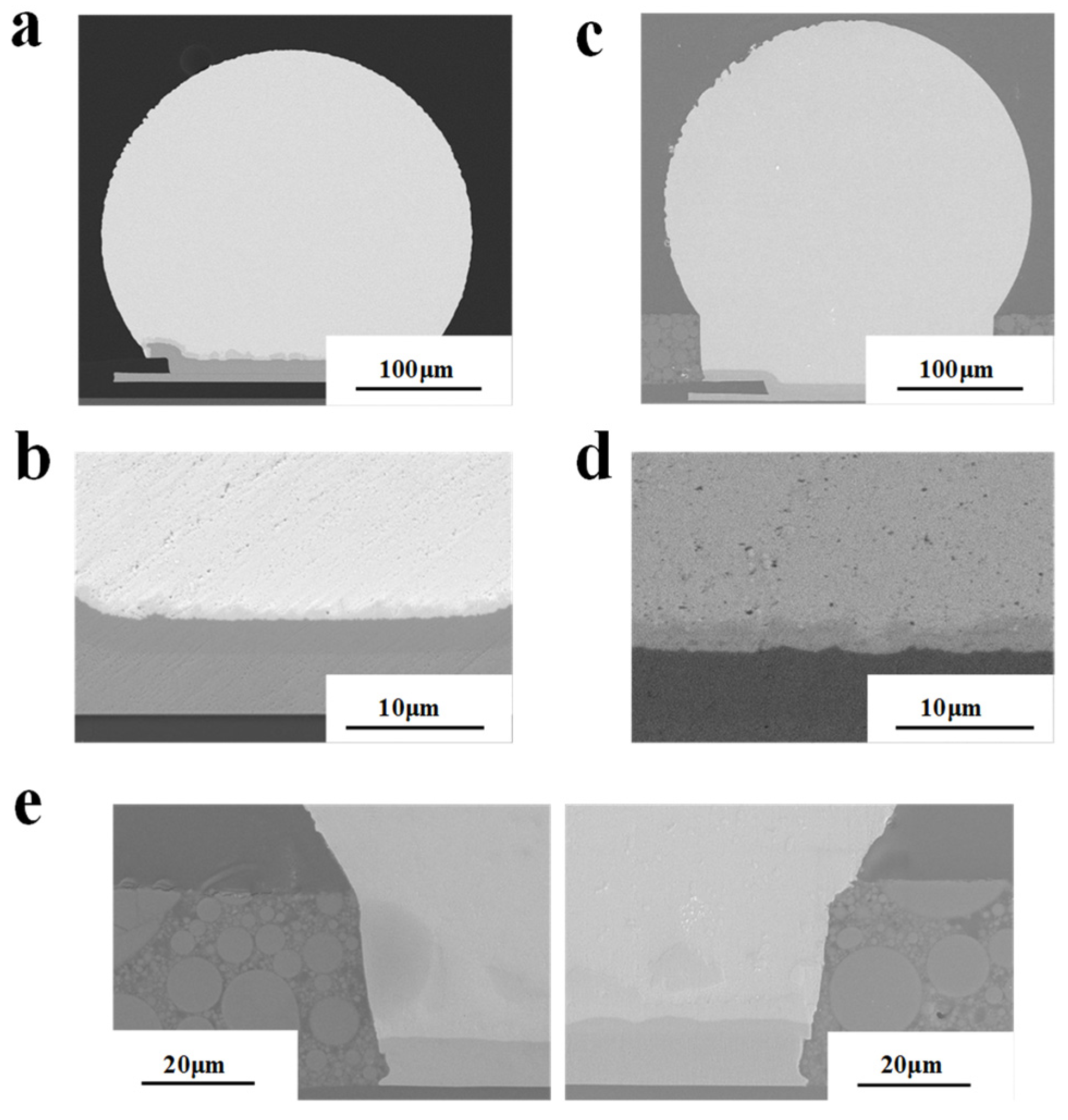

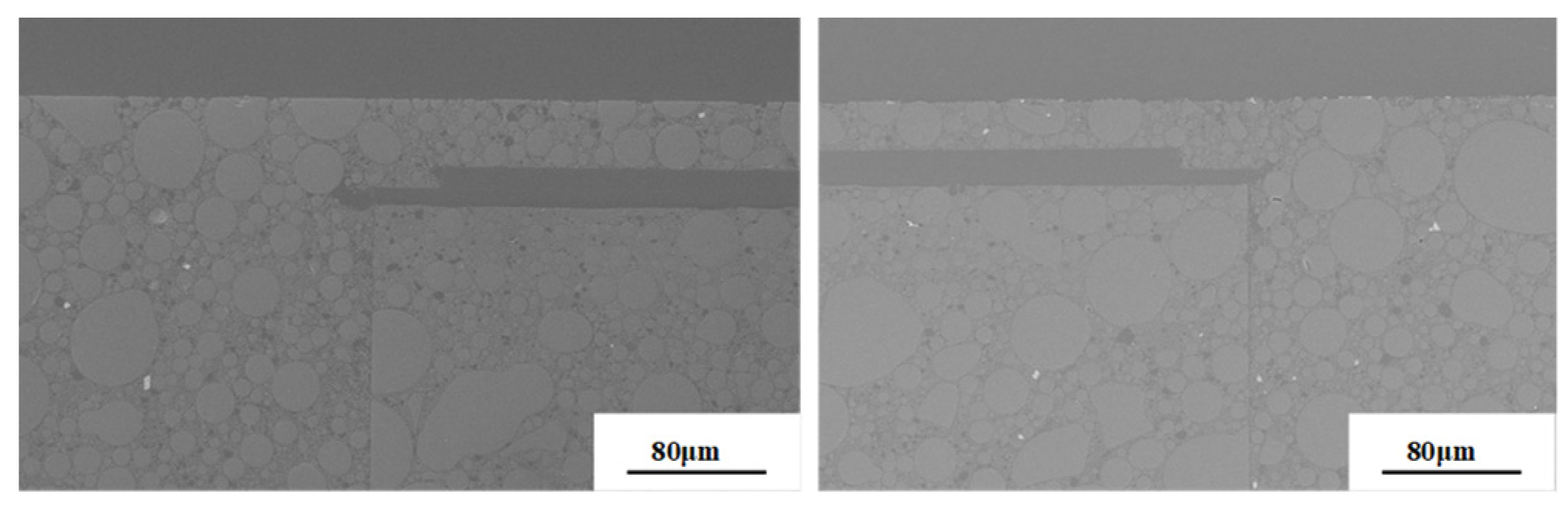

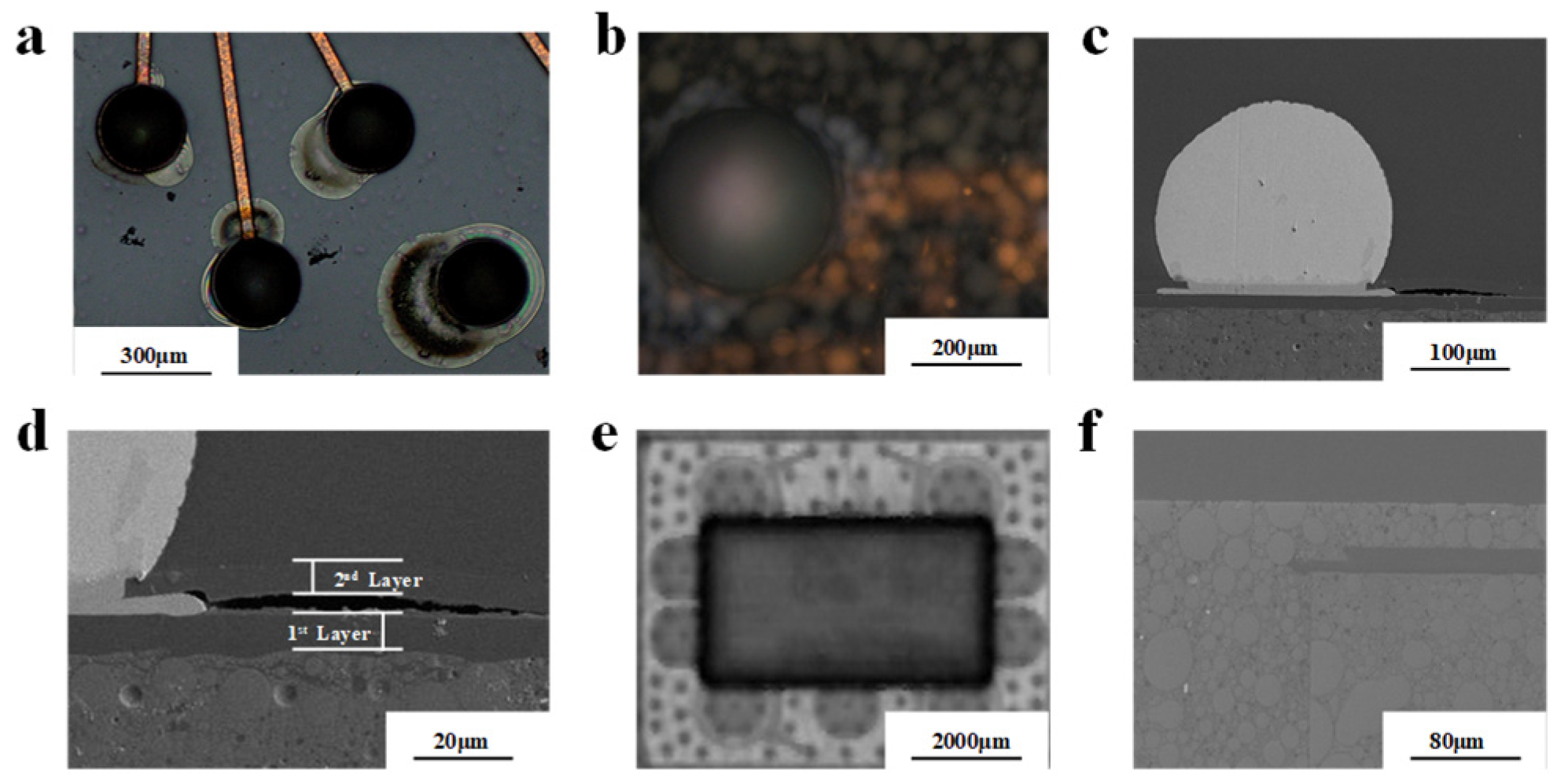

3.1. Packaging Structure Observations

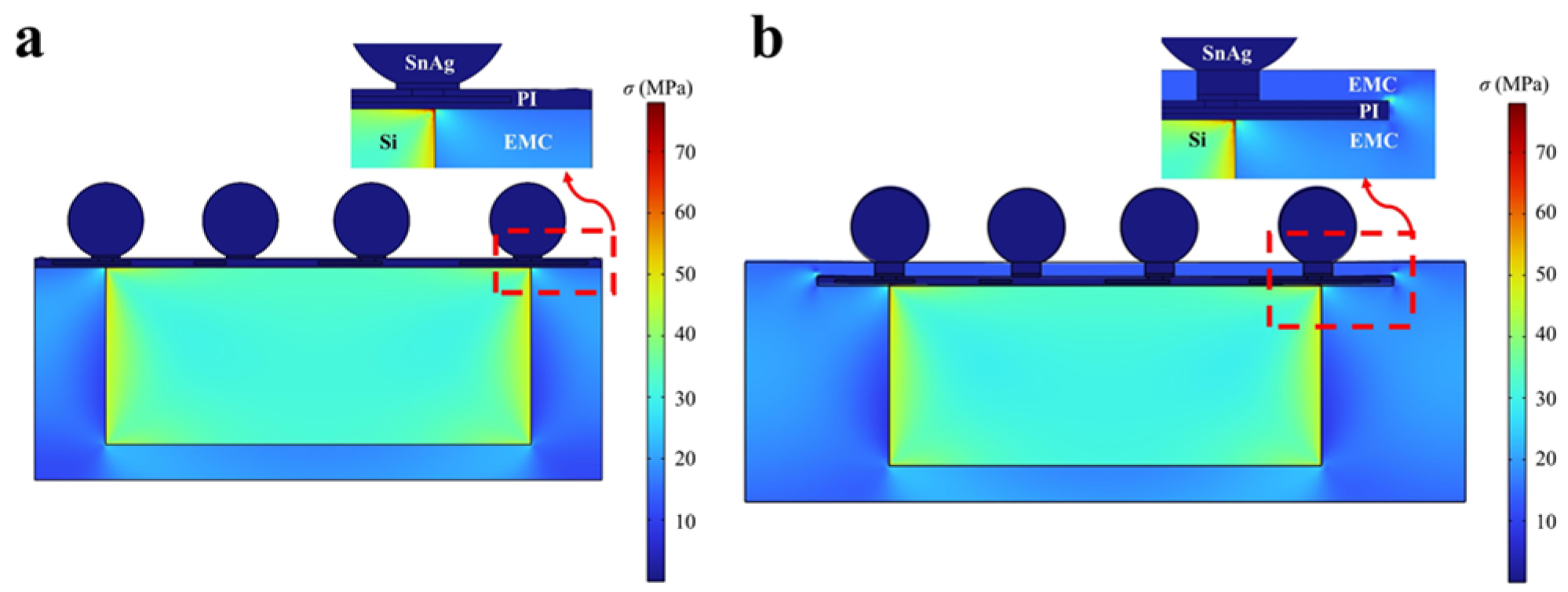

3.2. Structural Reliability Analysis

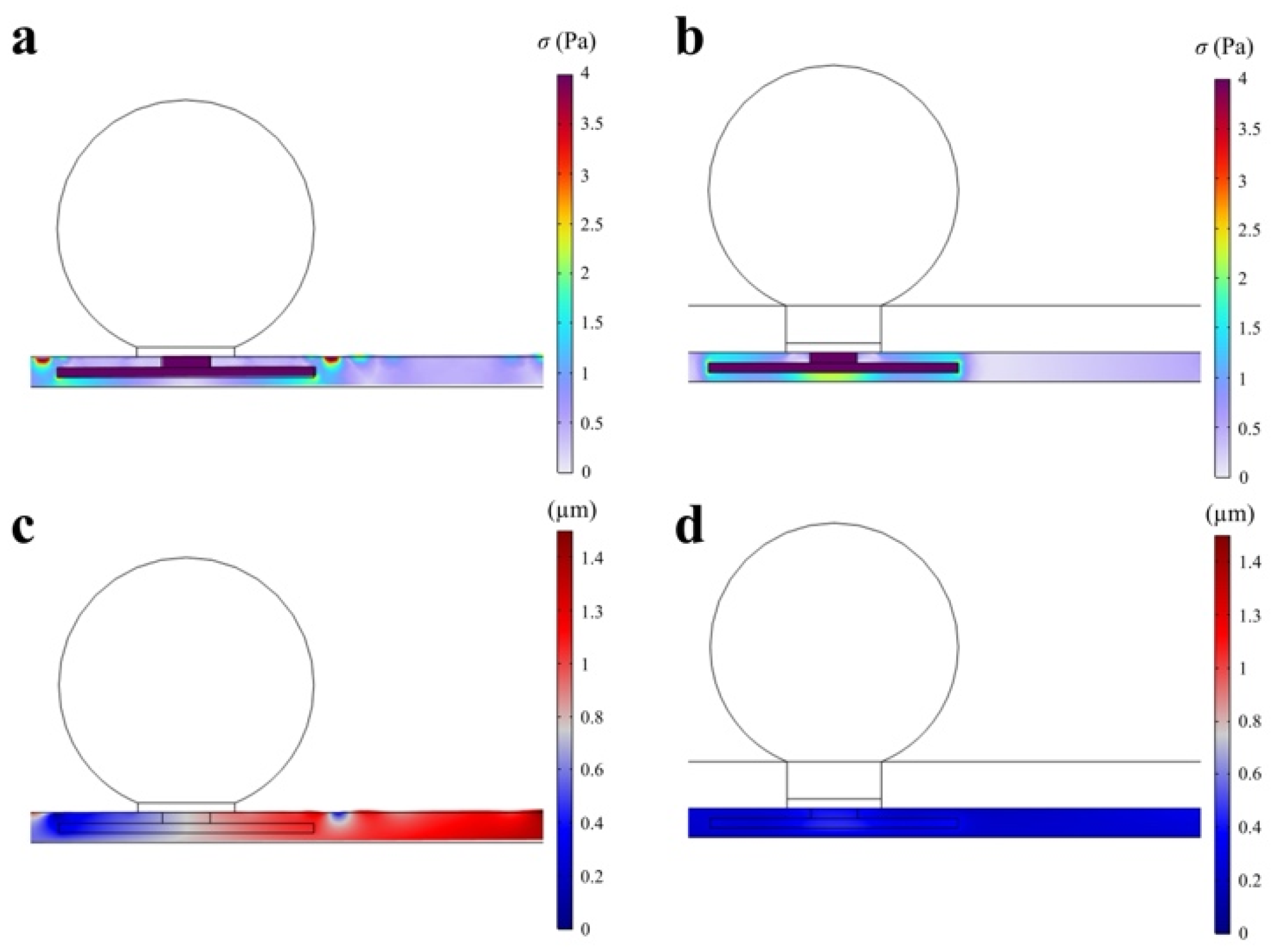

3.3. Solder Ball Performance

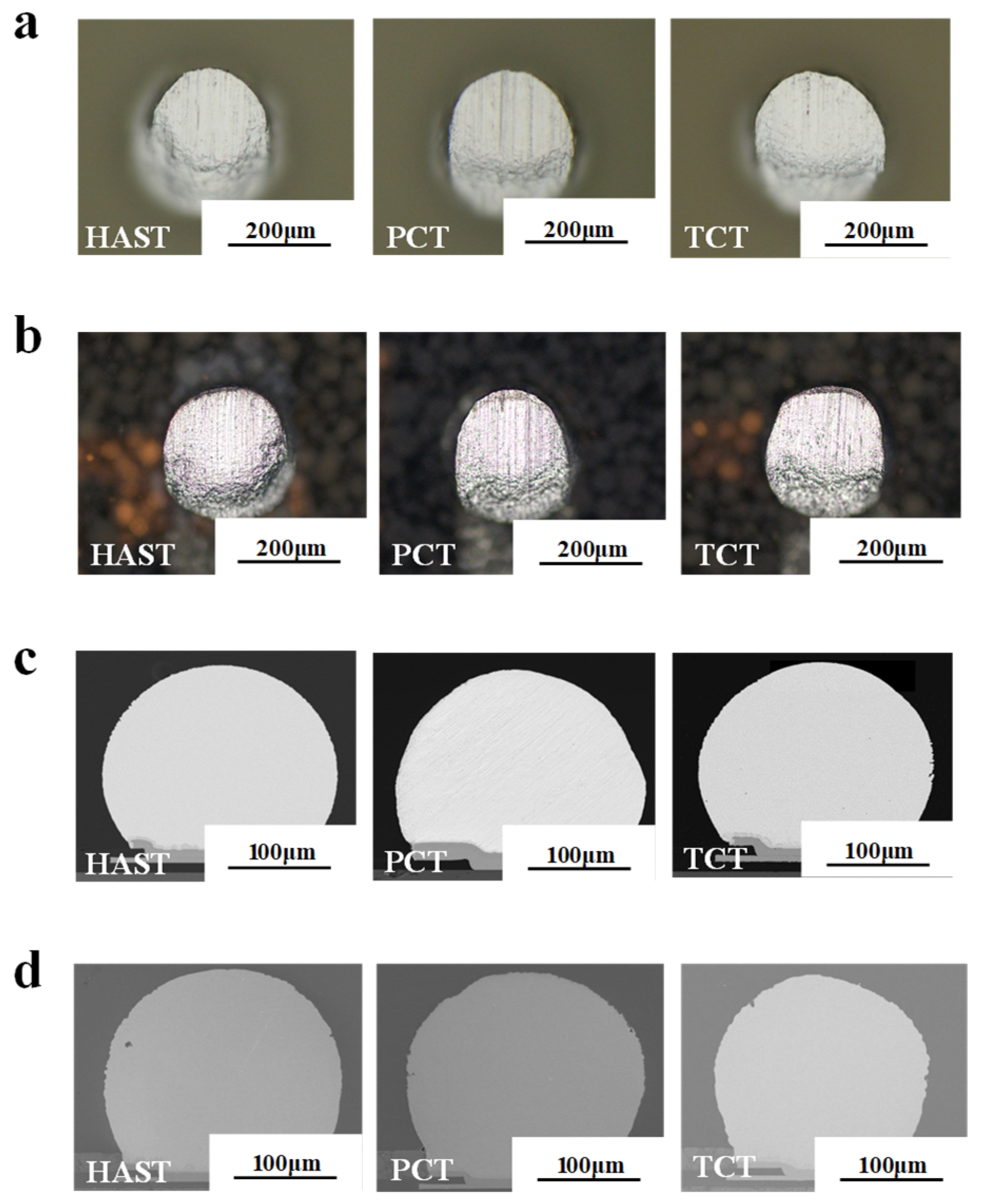

3.4. Microscopic Morphology

3.5. Reliability Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Qu, S.; Liu, Y. Wafer-Level Chip-Scale Packaging; Springer: New York, NY, USA, 2015; pp. 54–64. [Google Scholar] [CrossRef]

- Shi, L.; Chen, L.; Zhang, D.W.; Liu, E.; Liu, Q.; Chen, C.-I. Improvement of thermo-mechanical reliability of wafer-level chip scale packaging. J. Electron. Packag. 2018, 140, 011002. [Google Scholar] [CrossRef]

- Liu, P.; Wang, J.; Tong, L.; Tao, Y. Advances in the fabrication processes and applications of wafer level packaging. J. Electron. Packag. 2014, 136, 024002. [Google Scholar] [CrossRef]

- Arriola, E.R.; Ubando, A.T.; Gonzaga, J.A.; Lee, C.-C. Wafer-level chip-scale package lead-free solder fatigue: A critical review. Eng. Fail. Anal. 2023, 144, 106986. [Google Scholar] [CrossRef]

- Cao, L.; Lee, T.C.; Chen, R.; Chang, Y.-S.; Lu, H.; Chao, N.; Huang, Y.-L.; Wang, C.-C.; Huang, C.-Y.; Kuo, H.-C.; et al. Advanced fanout packaging technology for hybrid substrate integration. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–3 June 2022; pp. 1362–1370. [Google Scholar]

- Hsu, F.C.; Lin, J.; Chen, S.M.; Lin, P.Y.; Fang, J.; Wang, J.H.; Jeng, S.P. 3D heterogeneous integration with multiple stacking fan-out package. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 337–342. [Google Scholar]

- Lau, J.H. Recent advances and trends in fan-out wafer/panel-level packaging. J. Electron. Packag. 2019, 141, 040801. [Google Scholar] [CrossRef]

- Lau, J.H.; Li, M.; Li, Q.M.; Xu, I.; Chen, T.; Li, Z.; Tan, K.H.; Yong, Q.X.; Cheng, Z.; Wee, K.S.; et al. Design, materials, process, fabrication, and reliability of fan-out wafer-level packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2018, 8, 991–1002. [Google Scholar] [CrossRef]

- Braun, T.; Becker, K.-F.; Voges, S.; Thomas, T.; Kahle, R.; Bader, V.; Bauer, J.; Aschenbrenner, R.; Lang, K.-D. Challenges and opportunities for fan-out panel level packing (FOPLP). In Proceedings of the 2014 9th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, Taiwan, 22–24 October 2014; pp. 154–157. [Google Scholar]

- Chen, D.-L.; Hu, I.; Chen, K.Y.; Shih, M.-K.; Tarng, D.; Huang, D.; On, J. Material and structure design optimization for panel-level fan-out packaging. In Proceedings of the 2019 IEEE 69th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2019; pp. 1710–1715. [Google Scholar]

- Rongen, R.; Roucou, R.; Wel, P.V.; Voogt, F.; Swartjes, F.; Weide-Zaage, K. Reliability of wafer level chip scale packages. Microelectron. Reliab. 2014, 54, 1988–1994. [Google Scholar] [CrossRef]

- Chen, C.C.; Chen, K.H.; Wu, Y.S.; Tsao, P.H.; Leu, S.T. WLCSP solder ball interconnection enhancement for high temperature stress reliability. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 1212–1217. [Google Scholar]

- Lau, J.; Li, M.; Lei, Y.; Li, M.; Xu, I.; Chen, T.; Yong, Q.X.; Cheng, Z.; Kai, W.; Lo, P.; et al. Reliability of fan-out wafer-level heterogeneous integration. International Symposium on Microelectronics. Int. Microelectron. Assem. Packag. Soc. 2018, 2018, 224–232. [Google Scholar]

- Cardoso, A.; Martins, S.; Gouvea, A. Characterization of electromigration effects in rdl of wafer level fan-in and fan-out packaging using a novel analysis approach. In Proceedings of the 2018 7th Electronic System-Integration Technology Conference (ESTC), Dresden, Germany, 18–21 September 2018; pp. 1–7. [Google Scholar]

- Hou, F.; Lin, T.; Cao, L.; Liu, F.; Li, J.; Fan, X.; Zhang, G.Q. Experimental verification and optimization analysis of warpage for panel-level fan-out package. IEEE Trans. Compon. Packag. Manuf. Technol. 2017, 7, 1721–1728. [Google Scholar] [CrossRef]

- Yu, C.K.; Chiang, W.S.; Liu, N.W.; Lin, M.Z.; Fang, Y.H.; Lin, M.J.; Lin, B.; Huang, M. A unique failure mechanism induced by chip to board interaction on fan-out wafer level package. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 4A-6.1–4A-6.4. [Google Scholar]

- Lin, R.; Yip, L.; Lai, C.; Lin, B.-Y.; Peng, C.; Syu, C.; Chang, M. Reliability Challenges of Large Organic Substrate with High-Density Fan-out Package. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 277–282. [Google Scholar]

- Che, F.X. Study on board level solder joint reliability for extreme large fan-out WLP under temperature cycling. In Proceedings of the 2016 IEEE 18th Electronics Packaging Technology Conference (EPTC), Singapore, 30 November–3 December 2016; pp. 207–212. [Google Scholar]

- Lau, J.H.; Ko, C.-T.; Peng, C.-Y.; Tseng, T.-J.; Yang, K.-M.; Xia, T.; Lin, P.B.; Lin, E.; Chang, L.; Liu, H.N.; et al. Reliability of 6-side molded panel-level chip-scale packages (PLCSPs). In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; pp. 885–894. [Google Scholar]

- Smith, L.; Dimaano, J., Jr. Development approach & process optimization for sidewall WLCSP protection. In Proceedings of the 12th Annual International Wafer-Level Packaging Conference (IWLPC), San Jose, CA, USA, 12–14 October 2015; pp. 1–4. [Google Scholar]

- Ma, S.; Wang, T.; Xiao, Z.; Yu, D. Process development of five-and six-side molded WLCSP. In Proceedings of the 2018 China Semiconductor Technology International Conference (CSTIC), Shanghai, China, 11–12 March 2018; pp. 1–3. [Google Scholar]

- Lau, J.H.; Ko, C.-T.; Peng, C.-Y.; Tseng, T.-J.; Yang, K.-M.; Xia, T.; Lin, P.B.; Lin, E.; Chang, L.; Liu, H.N.; et al. Thermal cycling test and simulation of six-side molded panel-level chip-scale packages (PLCSPs). J. Microelectron. Electron. Packag. 2021, 18, 67–80. [Google Scholar] [CrossRef]

- Qin, F.; Zhao, S.; Dai, Y.; Yang, M.; Xiang, M.; Yu, D. Study of warpage evolution and control for six-side molded WLCSP in different packaging processes. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 730–738. [Google Scholar] [CrossRef]

- Yip, L.; Lin, R.; Lai, C.; Peng, C. Reliability challenges of high-density fan-out packaging for high-performance computing applications. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–3 June 2022; pp. 1454–1458. [Google Scholar]

- Lee, Y.-C.; Lai, W.-H.; Hu, I.; Shih, M.-K.; Kao, C.-L.; Tarng, D.; Hung, C.-P. Fan-out chip on substrate device interconnection reliability analysis. In Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 22–27. [Google Scholar]

- Fan, Y.; Tian, S.; Jiao, H.; Meng, D.; Wang, Z.; Meng, M. Interconnect Reliability Simulation Analysis of Fan-out Package redistribution Layer. In Proceedings of the 2023 8th International Conference on Integrated Circuits and Microsystems (ICICM), Nanjing, China, 20–23 October 2023; pp. 98–104. [Google Scholar]

- Zhang, L.; Sun, L.; Han, J.-G.; Guo, Y.-H. Reliability of lead-free solder joints in WLCSP device with finite element simulation and Taguchi method. Int. J. Nonlinear Sci. Numer. Simul. 2014, 15, 405–410. [Google Scholar] [CrossRef]

- Wang, P.H.; Huang, A.; Chiang, K.N. Design and reliability assessment of stacked fan-out packaging. In Proceedings of the 2018 Pan Pacific Microelectronics Symposium (Pan Pacific), Big Island, HI, USA, 5–8 February 2018; pp. 1–6. [Google Scholar]

- Shih, M.-K.; Lee, Y.-C.; Chen, R.; Tarng, D.; Hung, C.P. Parameters study of thermomechanical reliability of board-level fan-out package. In Proceedings of the 2017 International Conference on Electronics Packaging (ICEP), Yamagata, Japan, 19–22 April 2017; pp. 66–70. [Google Scholar]

- Zhang, S.; Duan, R.; Xu, S.; Xue, P.; Wang, C.; Chen, J.; Paik, K.-W.; He, P. Shear performance and accelerated reliability of solder interconnects for fan-out wafer-level package. J. Adv. Join. Process. 2022, 5, 100076. [Google Scholar] [CrossRef]

- Li, M.; Li, Q.; Lau, J.; Fan, N.; Kuah, E.; Kai, W.; Cheung, K.; Li, Z.; Tan, K.H.; Xu, I.; et al. Characterizations of fan-out wafer-level packaging. Int. Symp. Microelectronics. Int. Microelectron. Assem. Packag. Soc. 2017, 2017, 557–562. [Google Scholar] [CrossRef]

- Lau, J.H.; Lee, S.-W.R.; Chang, C. Solder joint reliability of wafer level chip scale packages (WLCSP): A time-temperature-dependent creep analysis. J. Electron. Packag. 2000, 122, 311–316. [Google Scholar] [CrossRef]

- Park, H.-P.; Seo, G.; Kim, S.; Ahn, K.-O.; Kim, Y.-H. Shear strength between Sn–3.0 Ag–0.5 Cu solders and Cu substrate after two solid-state aging processes for fan-out package process applications. J. Mater. Sci. Mater. Electron. 2019, 30, 10550–10559. [Google Scholar] [CrossRef]

- Zhu, J.; Ming, X.; Yao, X. Research on key process technology of RDL-first fan-out wafer level packaging. In Proceedings of the 2018 19th International Conference on Electronic Packaging Technology (ICEPT), Shanghai, China, 8–11 August 2018; pp. 309–313. [Google Scholar]

- Ke, C.Y.; Chen, L.P. The Simulation and Detection of Copper/Polyimide Delamination of Fan-Out Package Trace/Passivation Interface. In Proceedings of the 2021 International Conference on Electronics Packaging (ICEP), Tokyo, Japan, 12–14 May 2021; pp. 167–168. [Google Scholar]

| Materials | ρ kg/m3 | α 10−6/C | E MPa | k W/mk | Poisson’s Ratio | C J/(kg·K) |

|---|---|---|---|---|---|---|

| EMC | 2020 | 7.3 | 23,000 | 0.3 | 0.23 | 700 |

| Si | 2334 | 2.6 | 130,000 | 186(−40) 135(25) 96(140) | 0.28 | 700 |

| PI | 2000 | 50 | 3400 | 0.4 | 0.34 | 1165 |

| Cu | 9000 | 17 | 120,000 | 393 | 0.35 | 358 |

| SnAg | 7400 | 21.6 | 50,000 | 63.2 | 0.36 | 222.1 |

| Structure | Shear Force (mg/μm2) | |||

|---|---|---|---|---|

| Min. | Max. | Avg. | STDEV | |

| Normal structure | 5.4 | 6.4 | 5.7 | 0.27 |

| Six-sided protective structure | 5.5 | 6.4 | 5.9 | 0.27 |

| Structures | Reliability Tests | Shear Force (mg/μm2) | |||

|---|---|---|---|---|---|

| Min. | Max. | Avg. | STDEV | ||

| Normal structure | HAST | 4.0 | 4.4 | 4.2 | 0.14 |

| PCT | 4.0 | 4.5 | 4.3 | 0.15 | |

| TCT | 4.1 | 4.5 | 4.3 | 0.13 | |

| Six-sided protective structure | HAST | 4.1 | 4.6 | 4.4 | 0.14 |

| PCT | 4.0 | 4.5 | 4.2 | 0.15 | |

| TCT | 4.0 | 4.6 | 4.3 | 0.14 | |

| Structures | Reliability Tests | Number of Test Samples | |

|---|---|---|---|

| Total | Failed | ||

| Normal structure | HAST | 10 | 0 |

| PCT | 15 | 15 | |

| TCT | 15 | 0 | |

| Six-sided protective structure | HAST | 10 | 0 |

| PCT | 15 | 0 | |

| TCT | 15 | 0 | |

| Key Metrics | Normal Structure | Six-Sided Protective Structure | Improvement Value |

|---|---|---|---|

| Average thermal stress | 16.4 MPa | 15.0 MPa | −9.06% |

| Average temperature | 88.56 °C | 88.74 °C | −0.94% |

| HAST | Pass | Pass | - |

| PCT | Fail | Pass | 100% |

| TCT | Pass | Pass | - |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, C.; Tao, J.; Tang, W.; Dai, F.; Ji, Y.; Chen, W.; Wang, C. Investigation of Reliability Strengthening by Six-Sided Protective Structure in Fan-Out Wafer-Level Packaging. Electronics 2025, 14, 4429. https://doi.org/10.3390/electronics14224429

Yang C, Tao J, Tang W, Dai F, Ji Y, Chen W, Wang C. Investigation of Reliability Strengthening by Six-Sided Protective Structure in Fan-Out Wafer-Level Packaging. Electronics. 2025; 14(22):4429. https://doi.org/10.3390/electronics14224429

Chicago/Turabian StyleYang, Cheng, Junyu Tao, Wenxue Tang, Feihu Dai, Yong Ji, Weijin Chen, and Chengqian Wang. 2025. "Investigation of Reliability Strengthening by Six-Sided Protective Structure in Fan-Out Wafer-Level Packaging" Electronics 14, no. 22: 4429. https://doi.org/10.3390/electronics14224429

APA StyleYang, C., Tao, J., Tang, W., Dai, F., Ji, Y., Chen, W., & Wang, C. (2025). Investigation of Reliability Strengthening by Six-Sided Protective Structure in Fan-Out Wafer-Level Packaging. Electronics, 14(22), 4429. https://doi.org/10.3390/electronics14224429