Netlist-Aware Mixed-Cell-Height Legalization

Abstract

1. Introduction

2. Problem Statement

3. Proposed Algorithm

3.1. Introduction of the Legalization Algorithm

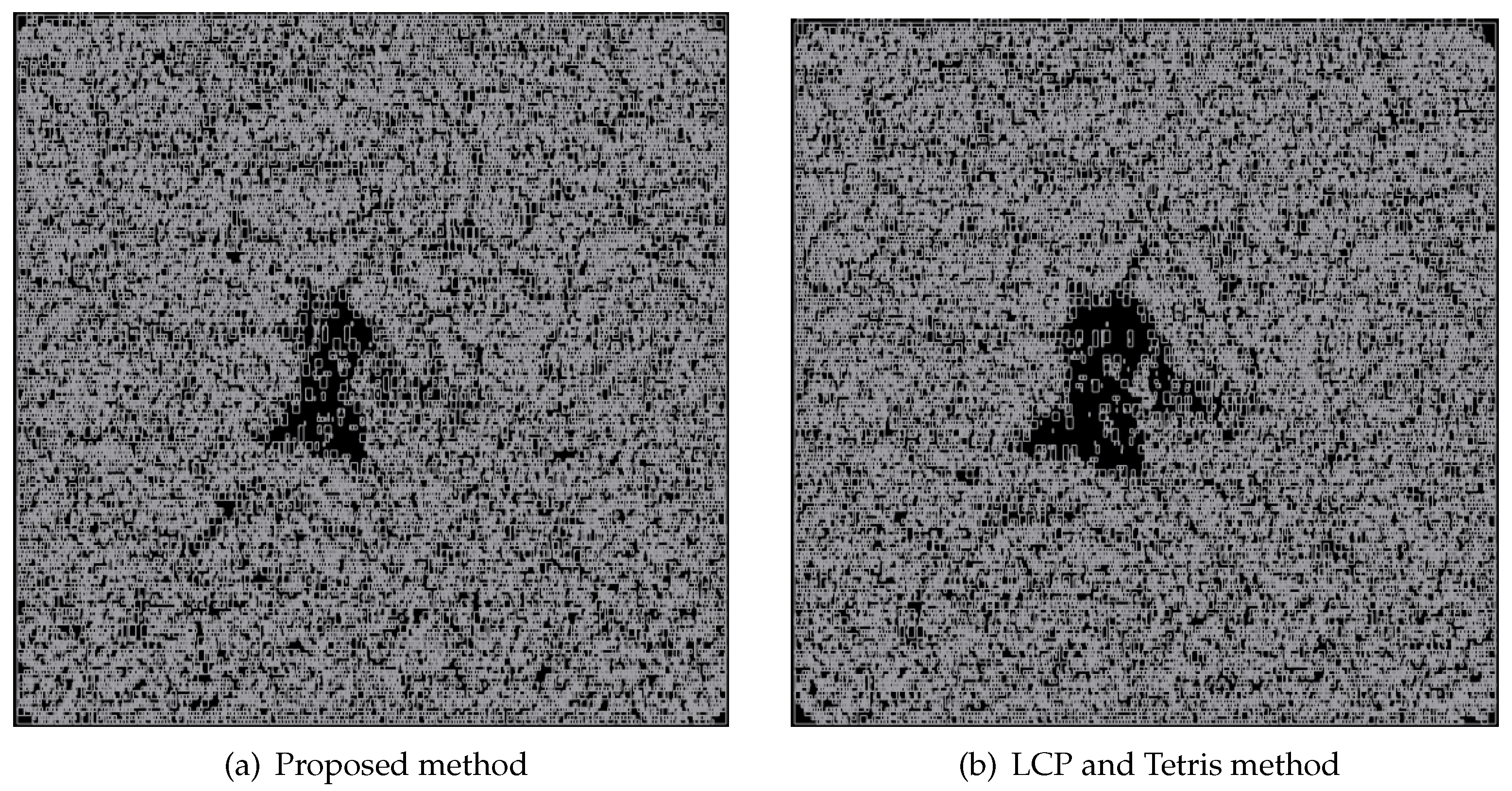

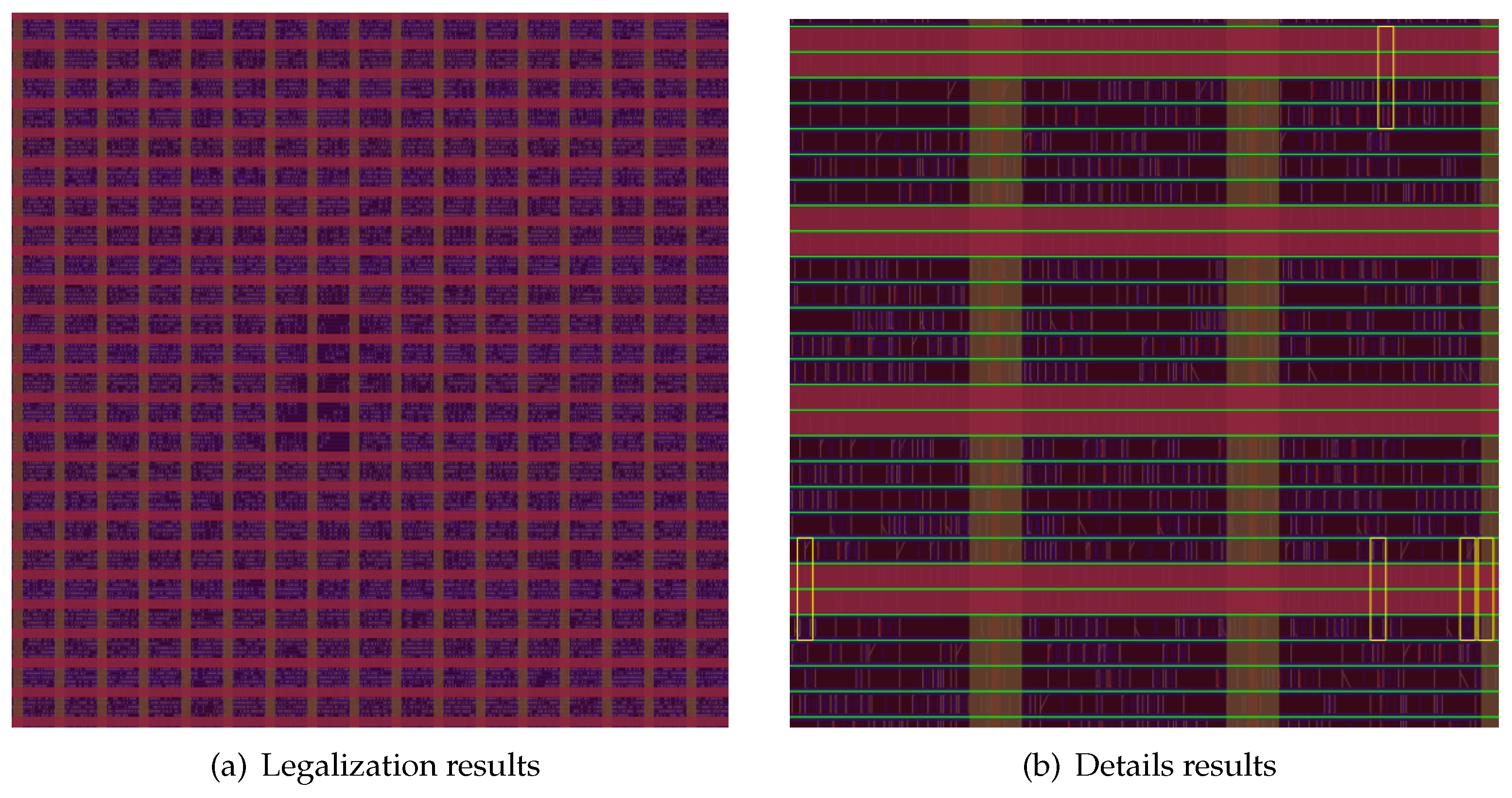

| Algorithm 1 Netlist-aware mixed-cell-height legalization |

Input: Global placement result

Output: Legalization result |

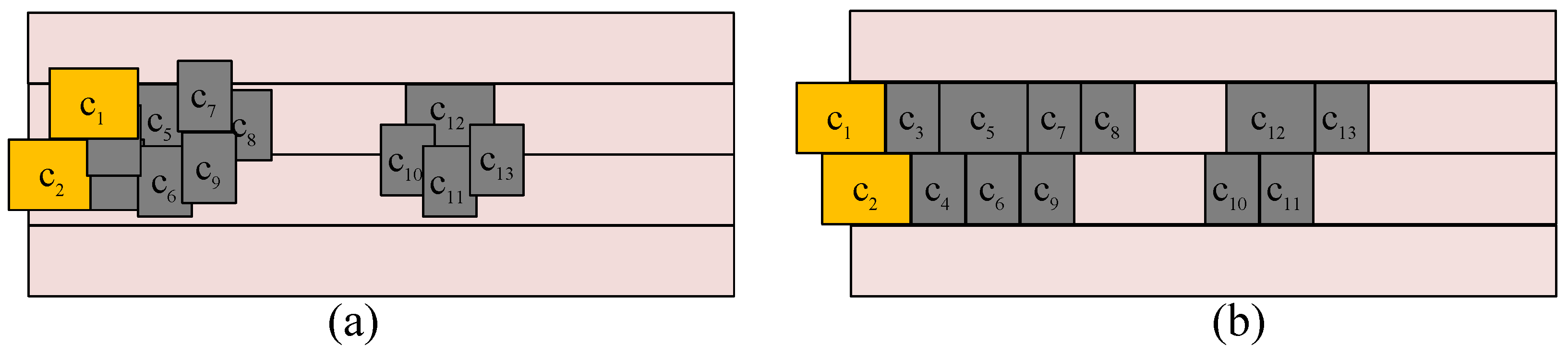

3.2. -Norm-Based Overlapped Cell Legalization

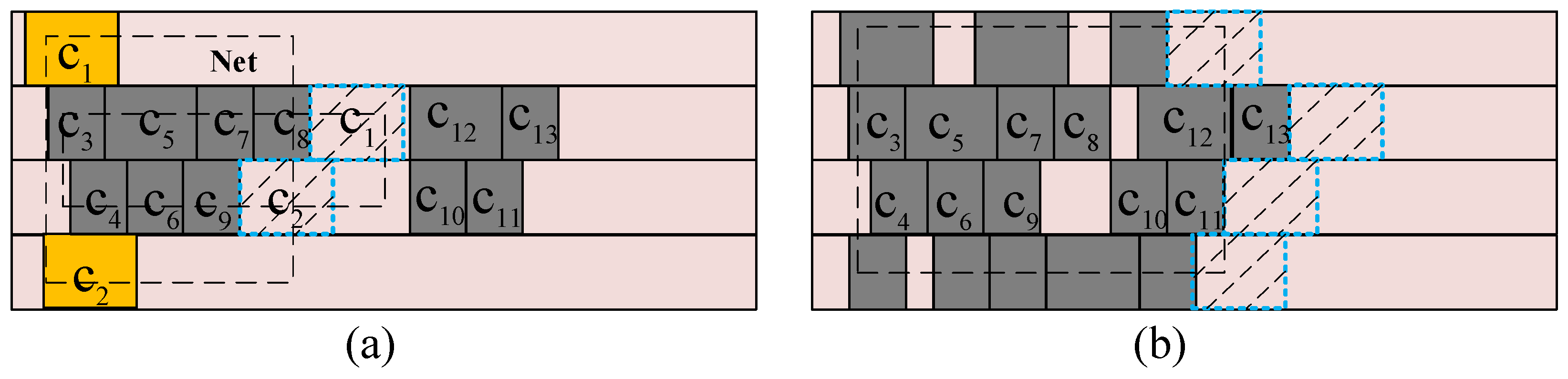

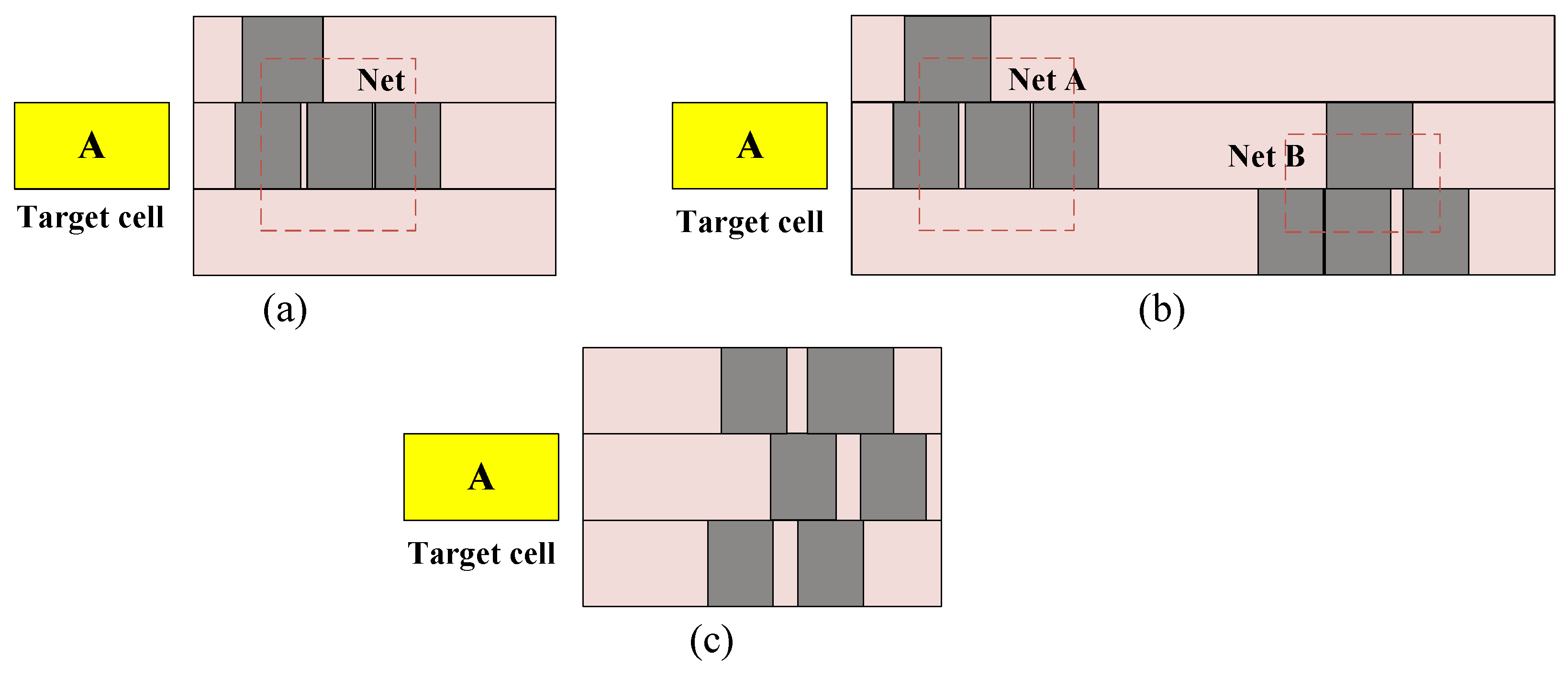

3.3. Netlist-Aware Available Region Filling

| Algorithm 2 Netlist-Aware Available Region Filling |

Input: q-th illegal cell

Output: Available site |

4. Netlist-Aware Available Region Filling

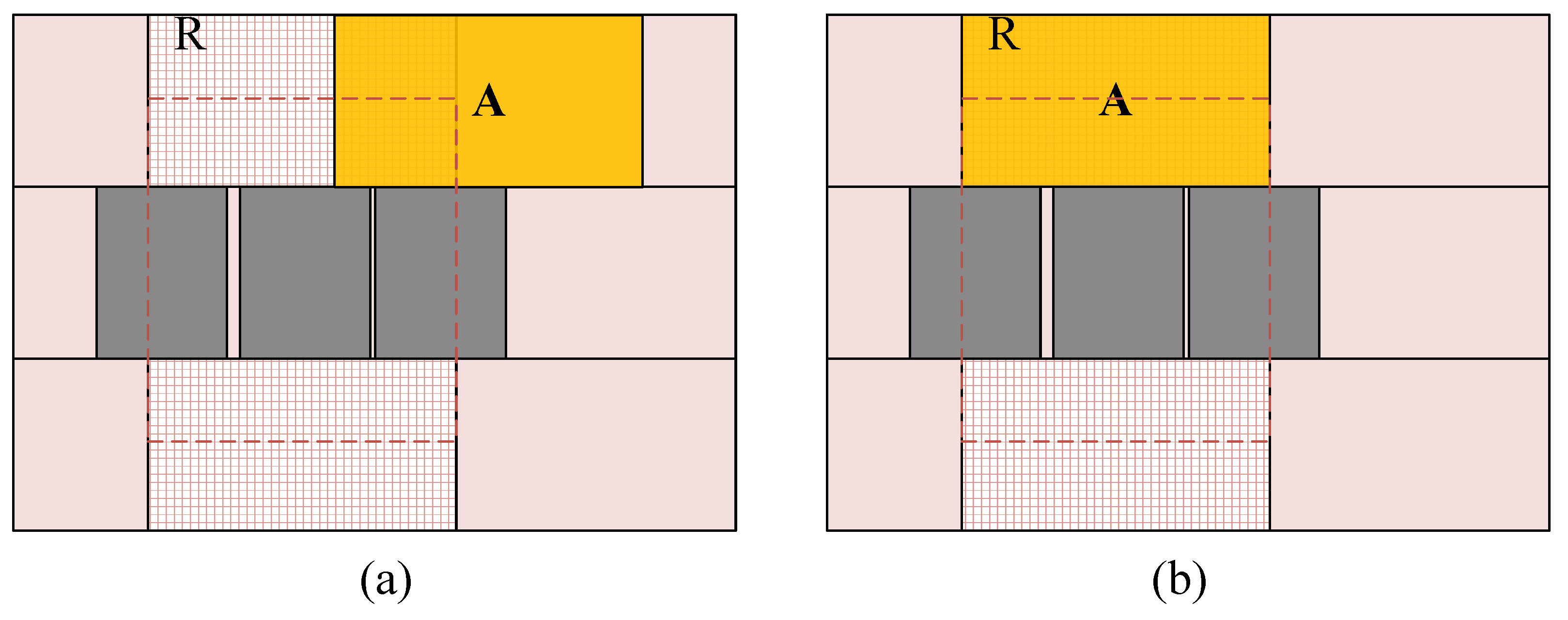

5. The Remarks of -Norm-Based Overlapped Cell Legalization

6. Experimental Results

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Qiu, Y.; Xing, Y.; Zheng, X.; Gao, P.; Cai, S.; Xiong, X. Progress of Placement Optimization for Accelerating VLSI Physical Design. Electronics 2023, 12, 337. [Google Scholar] [CrossRef]

- Li, L.; Cai, Y.; Zhou, Q. A survey on machine learning-based routing for VLSI physical design. Integration 2022, 86, 51–56. [Google Scholar] [CrossRef]

- Wu, J.; Ni, C.; Wang, H.; Chen, J. Graph Neural Networks for Efficient Clock Tree Synthesis Optimization in Complex SoC Designs. Appl. Comput. Eng. 2025, 150, 101–111. [Google Scholar] [CrossRef]

- Li, Z.; Chen, B.; Wang, W.; Lv, H.; Lv, Q.; Chen, J.; Wang, Y.; Li, J.; Zhang, C. A Method for Synthesizing Ultra-Large-Scale Clock Trees. Algorithms 2025, 18, 249. [Google Scholar] [CrossRef]

- Murali, S.L. Artificial Intelligence in VLSI Physical Design of Circuits to Optimize Power, Performance and Area (PPA). Int. Res. J. Eng. Technol. 2024, 11, 266–271. [Google Scholar]

- Abdollahi, M.; Yeganli, S.F.; Baharloo, M.; Baniasadi, A. Hardware Design and Verification with Large Language Models: A Scoping Review, Challenges, and Open Issues. Electronics 2025, 14, 120. [Google Scholar] [CrossRef]

- Liu, Y.; Zhou, H.; Wang, J.; Yang, F.; Zeng, X.; Shang, L. The Power of Graph Signal Processing for Chip Placement Acceleration. In Proceedings of the 43rd IEEE/ACM International Conference on Computer-Aided Design (ICCAD ’24), Newark, NJ, USA, 27–31 October 2024; ACM: New York, NY, USA, 2025. [Google Scholar]

- Jeong, J.; Kim, T. Placement legalization for heterogeneous cells of non-integer multiple-heights. Integration 2024, 97, 102177. [Google Scholar] [CrossRef]

- Chow, W.K.; Pui, C.W.; Young, E.F.Y. Legalization algorithm for multiple-row height standard cell design. In Proceedings of the 53rd Annual Design Automation Conference (DAC ’16), Austin, TX, USA, 5–9 June 2016. [Google Scholar]

- Wang, C.H.; Wu, Y.Y.; Chen, J.; Chang, Y.W.; Kuo, S.Y.; Zhu, W.; Fan, G. An effective legalization algorithm for mixed-cell-height standard cells. In Proceedings of the 22nd Asia and South Pacific Design Automation Conference, Chiba, Japan, 16–19 January 2017; ACM: New York, NY, USA, 2017; pp. 450–455. [Google Scholar]

- Spindler, P.; Schlichtmann, U.; Johannes, F.M. Abacus: Fast legalization of standard cell circuits with minimal movement. In Proceedings of the International Symposium on Physical Design, Portland, OR, USA, 13–16 April 2008; pp. 47–53. [Google Scholar]

- Hill, D. Method and System for High Speed Detailed Placement of Cells Within Integrated Circuit Designs. U.S. Patent US6370673B1, 9 April 2002. [Google Scholar]

- Chen, J.; Zhu, Z.; Zhu, W.; Yao-Wen, C. A Robust Modulus-Based Matrix Splitting Iteration Method for Mixed-Cell-Height Circuit Legalization. ACM Trans. Des. Autom. Electron. Syst. 2020, 26, 15. [Google Scholar] [CrossRef]

- Chen, J.; Lin, Z.; Xie, Y.; Zhu, W.; Chang, Y.W. Mixed-Cell-Height Placement With Complex Minimum-Implant-Area Constraints. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2022, 41, 4639–4652. [Google Scholar] [CrossRef]

- Wen, Y.; Zhu, B.; Lin, Z.; Chen, J. Effective Analytical Placement for Advanced Hybrid-Row-Height Circuit Designs. In Proceedings of the 29th Asia and South Pacific Design Automation Conference, Incheon, Republic of Korea, 22–25 January 2024; pp. 300–305. [Google Scholar]

- Zhu, Z.; Chen, J.; Zhu, W.; Chang, Y.W. Mixed-Cell-Height Legalization Considering Technology and Region Constraints. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2020, 39, 5128–5141. [Google Scholar] [CrossRef]

- Zhou, C.; Cao, Y.; Shi, Q.; Wang, L.; Wen, X. A Robust Newton Iteration Method for Mixed-Cell-Height Circuit Legalization Under Technology and Region Constraints. ACM Trans. Des. Autom. Electron. Syst. 2024, 29, 96. [Google Scholar] [CrossRef]

- Wu, C.H.; Mak, W.K.; Chu, C. Linear-time Mixed-Cell-Height Legalization for Minimizing Maximum Displacement. In Proceedings of the International Symposium on Physical Design, Virtual Event, 27–30 March 2022; pp. 211–218. [Google Scholar]

- Li, H.; Chow, W.K.; Chen, G.; Yu, B.; Young, E.F. Pin-Accessible Legalization for Mixed-Cell-Height Circuits. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2022, 41, 143–154. [Google Scholar] [CrossRef]

- Gu, H.; Gu, J.; Peng, K.; Zhu, Z.; Xu, N.; Geng, X.; Yang, J. LAMPlace: Legalization-Aided Reinforcement Learning-Based Macro Placement for Mixed-Size Designs With Preplaced Blocks. IEEE Trans. Circuits Syst. II Exp. Briefs 2024, 71, 3770–3774. [Google Scholar] [CrossRef]

- Hyun, D.; Lee, W.; Park, J.; Shin, Y. Integrated Power Distribution Network Synthesis for Mixed Macro Blocks and Standard Cells. IEEE Trans. Circuits Syst. II Exp. Briefs 2023, 70, 2211–2215. [Google Scholar] [CrossRef]

- Zhu, Z.; Huang, Z.; Yang, P.; Zhu, W.; Chen, J.; Zhou, H.; Dong, S. Mixed-cell-height legalization considering complex minimum width constraints and half-row fragmentation effect. Integration 2020, 71, 1–10. [Google Scholar] [CrossRef]

- Huang, T.P.; Fang, S.Y. Practical Mixed-Cell-Height Legalization Considering Vertical Cell Abutment Constraint. In Proceedings of the 2024 International Symposium on Physical Design (ISPD ’24), Taipei, Taiwan, 12–15 March 2024; ACM: New York, NY, USA, 2024; pp. 151–159. [Google Scholar]

- Goto, S. An efficient algorithm for the two-dimensional placement problem in electrical circuit layout. IEEE Trans. Circuits Syst. 1981, 28, 12–18. [Google Scholar] [CrossRef]

- Cauley, S.; Balakrishnan, V.; Hu, Y.C.; Koh, C.K. A parallel branch-and-cut approach for detailed placement. ACM Trans. Des. Autom. Electron. Syst. 2011, 16, 18. [Google Scholar] [CrossRef]

- Li, S.; Koh, C.K. Mixed integer programming models for detailed placement. In Proceedings of the ACM International Symposium on Physical Design, Austin, TX, USA, 16–19 March 2012; ACM: New York, NY, USA, 2012; pp. 87–94. [Google Scholar]

- Li, S.; Koh, C.k. MIP-based detailed placer for mixed-size circuits. In Proceedings of the International Symposium on Physical Design, Petaluma, CA, USA, 30 March–2 April 2014; ACM: New York, NY, USA, 2014; pp. 11–18. [Google Scholar]

- Zhao, Y.; Liao, P.; Yu, B. 3D-Flow: Flow-based Standard Cell Legalization for 3D ICs. In Proceedings of the 2025 62nd ACM/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 22–25 June 2025; pp. 1–7. [Google Scholar]

- Gurobi Optimization, LLC. Gurobi Optimizer Reference Manual; Gurobi Optimization, LLC: Beaverton, OR, USA, 2024. [Google Scholar]

- Kim, M.C.; Hu, J.; Li, J.; Viswanathan, N. ICCAD-2015 CAD contest in incremental timing-driven placement and benchmark suite. In Proceedings of the IEEE/ACM International Conference on Computer Aided Design, Austin, TX, USA, 2–6 November 2015; pp. 921–926. [Google Scholar]

- Mantik, S.; Posser, G.; Chow, W.K.; Ding, Y.; Liu, W.H. ISPD 2018 Initial Detailed Routing Contest and Benchmarks. In Proceedings of the International Symposium on Physical Design, Monterey, CA, USA, 25–28 March 2018; ACM: New York, NY, USA, 2018; pp. 140–143. [Google Scholar]

- Cheng, C.K.; Kahng, A.B.; Kang, I.; Wang, L. RePlAce: Advancing Solution Quality and Routability Validation in Global Placement. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2019, 38, 1717–1730. [Google Scholar] [CrossRef]

- Lu, J.; Zhuang, H.; Chen, P.; Chang, H.; Chang, C.C.; Wong, Y.C.; Sha, L.; Huang, D.; Luo, Y.; Teng, C.C.; et al. ePlace-MS: Electrostatics-Based Placement for Mixed-Size Circuits. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2015, 34, 685–698. [Google Scholar] [CrossRef]

| GP | ||||

|---|---|---|---|---|

| Benchmark | Density | HPWL (m) | #S. Cell | #M. Cell |

| fft_1 | 0.84 | 0.825 | 32,281 | 0 |

| fft_2 | 0.5 | 0.382 | 32,281 | 0 |

| perf_1 | 0.91 | 1.103 | 112,644 | 0 |

| mult_1 | 0.81 | 3.410 | 155,325 | 0 |

| ispd18_test1 | 0.86 | 0.101 | 8879 | 0 |

| fft_1_md | 0.84 | 0.825 | 30,362 | 1919 |

| fft_2_md | 0.5 | 0.382 | 30,362 | 1919 |

| perf_1_md | 0.91 | 1.103 | 104,159 | 8485 |

| mult_1_md | 0.81 | 3.410 | 152,632 | 2693 |

| %HPWL (Solving Problem (7)) | Max Disp (nm) | Total Disp (cm) | ||||

|---|---|---|---|---|---|---|

| Benchmark | LCP | Ours | Tetris-like | Ours | Tetris-like | Ours |

| fft_1 | 6.102 | 5.406 | 29,197 | 17,472 | 5.577 | 4.815 |

| fft_2 | 5.93 | 6.09 | 8249 | 8609 | 2.03 | 1.94 |

| perf_1 | 12.54 | 10.93 | 23,736 | 20,475 | 17.34 | 14.76 |

| mult_1 | 7.23 | 7.13 | 24,894 | 24,780 | 28.28 | 27.35 |

| ispd18_test1 | 51.260 | 37.572 | 346,809 | 203,892 | 16.24 | 10.92 |

| fft_1_md | 14.20 | 9.09 | 49,786 | 28,485 | 47.86 | 19.61 |

| fft_2_md | 5.778 | 5.947 | 7639 | 7550 | 2.12 | 2.01 |

| perf_1_md | 28.77 | 25.90 | 112,644 | 57,684 | 490.9 | 209.0 |

| mult_1_md | 13.782 | 10.785 | 76,346 | 45,282 | 108.6 | 61.18 |

| Average | 16.177 | 13.206 | 75,478 | 46,025 | 79.88 | 39.06 |

| %HPWL | LG HPWL (dm) | RT (s) | |||

|---|---|---|---|---|---|

| Benchmark | Tetris-like | Ours | Tetris-like | Ours | |

| fft_1 | 6.23 | 6.03 | 8.78 | 8.74 | 2.34 |

| fft_2 | 5.93 | 6.086 | 4.050 | 4.056 | 3.38 |

| perf_1 | 12.77 | 11.35 | 12.44 | 12.28 | 3.18 |

| mult_1 | 7.24 | 7.13 | 36.57 | 36.53 | 4.55 |

| ispd18_test1 | 48.68 | 33.76 | 1.63 | 1.47 | 3.3 |

| fft_1_md | 27.21 | 13.99 | 10.49 | 9.40 | 9.09 |

| fft_2_md | 5.78 | 5.94 | 4.04 | 4.04 | 2.44 |

| perf_1_md | 171.96 | 58.64 | 30.01 | 17.59 | 17.28 |

| mult_1_md | 15.59 | 12.18 | 39.42 | 38.25 | 81.67 |

| Average | 33.52 | 17.23 | 16.38 | 14.70 | 14.13 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Liang, T.; Chen, W.; Liao, B. Netlist-Aware Mixed-Cell-Height Legalization. Electronics 2025, 14, 4287. https://doi.org/10.3390/electronics14214287

Liang T, Chen W, Liao B. Netlist-Aware Mixed-Cell-Height Legalization. Electronics. 2025; 14(21):4287. https://doi.org/10.3390/electronics14214287

Chicago/Turabian StyleLiang, Taihua, Weijie Chen, and Bin Liao. 2025. "Netlist-Aware Mixed-Cell-Height Legalization" Electronics 14, no. 21: 4287. https://doi.org/10.3390/electronics14214287

APA StyleLiang, T., Chen, W., & Liao, B. (2025). Netlist-Aware Mixed-Cell-Height Legalization. Electronics, 14(21), 4287. https://doi.org/10.3390/electronics14214287