Output Filtering Capacitor Bank Monitoring for a DC–DC Buck Converter

Abstract

1. Introduction

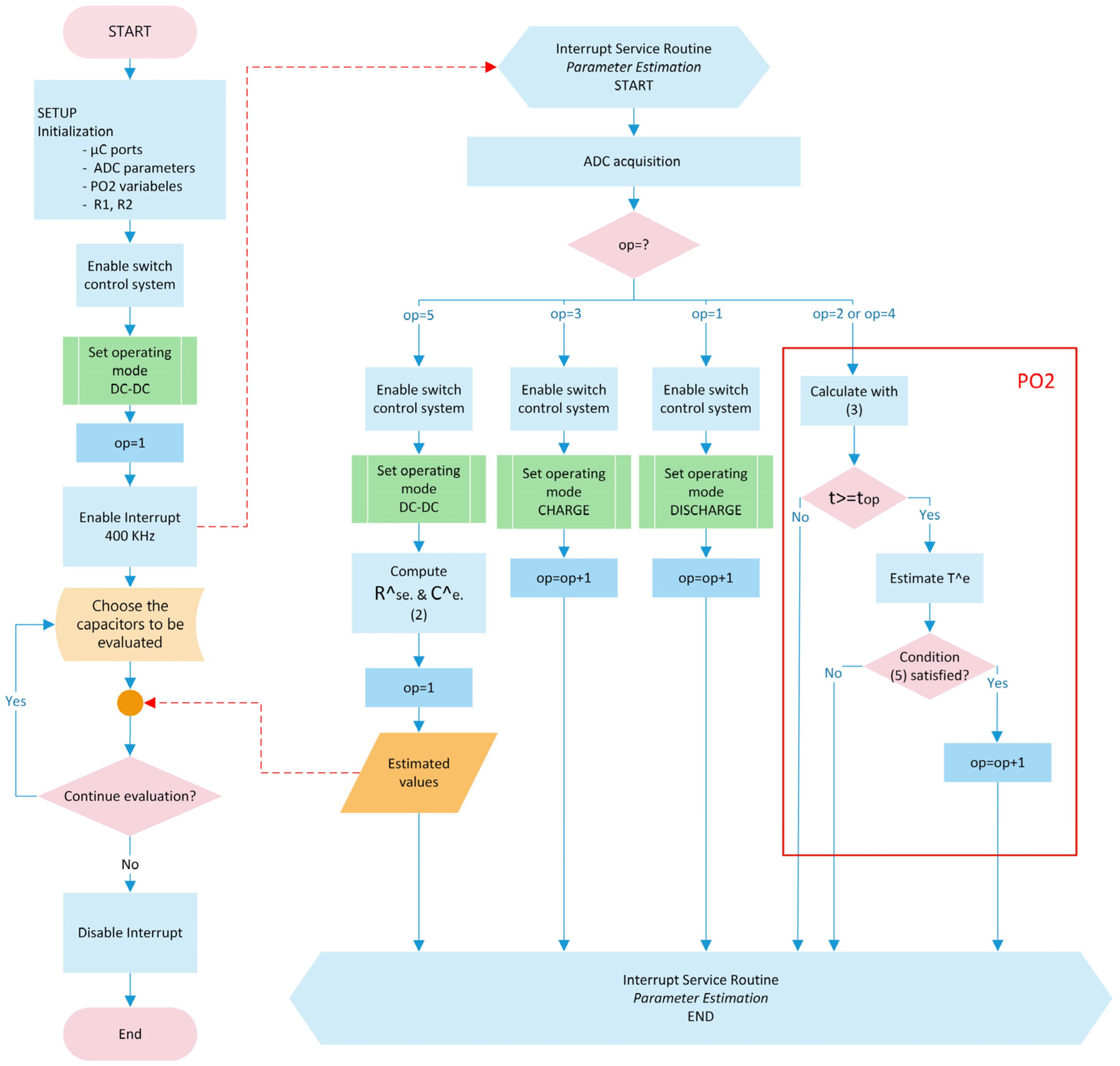

2. Materials and Methods

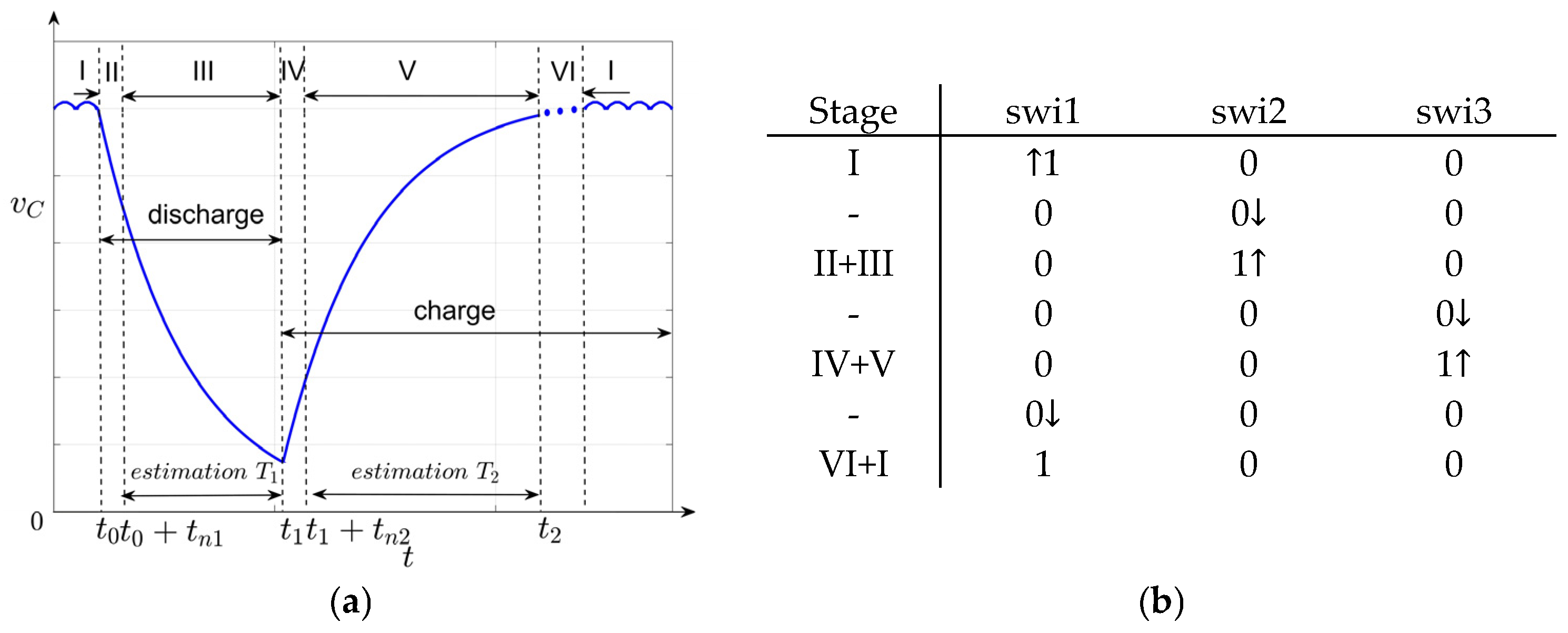

2.1. The Principle of Estimating the Values of the Equivalent Parameters of a Capacitor Modeled by a Series R–C Circuit

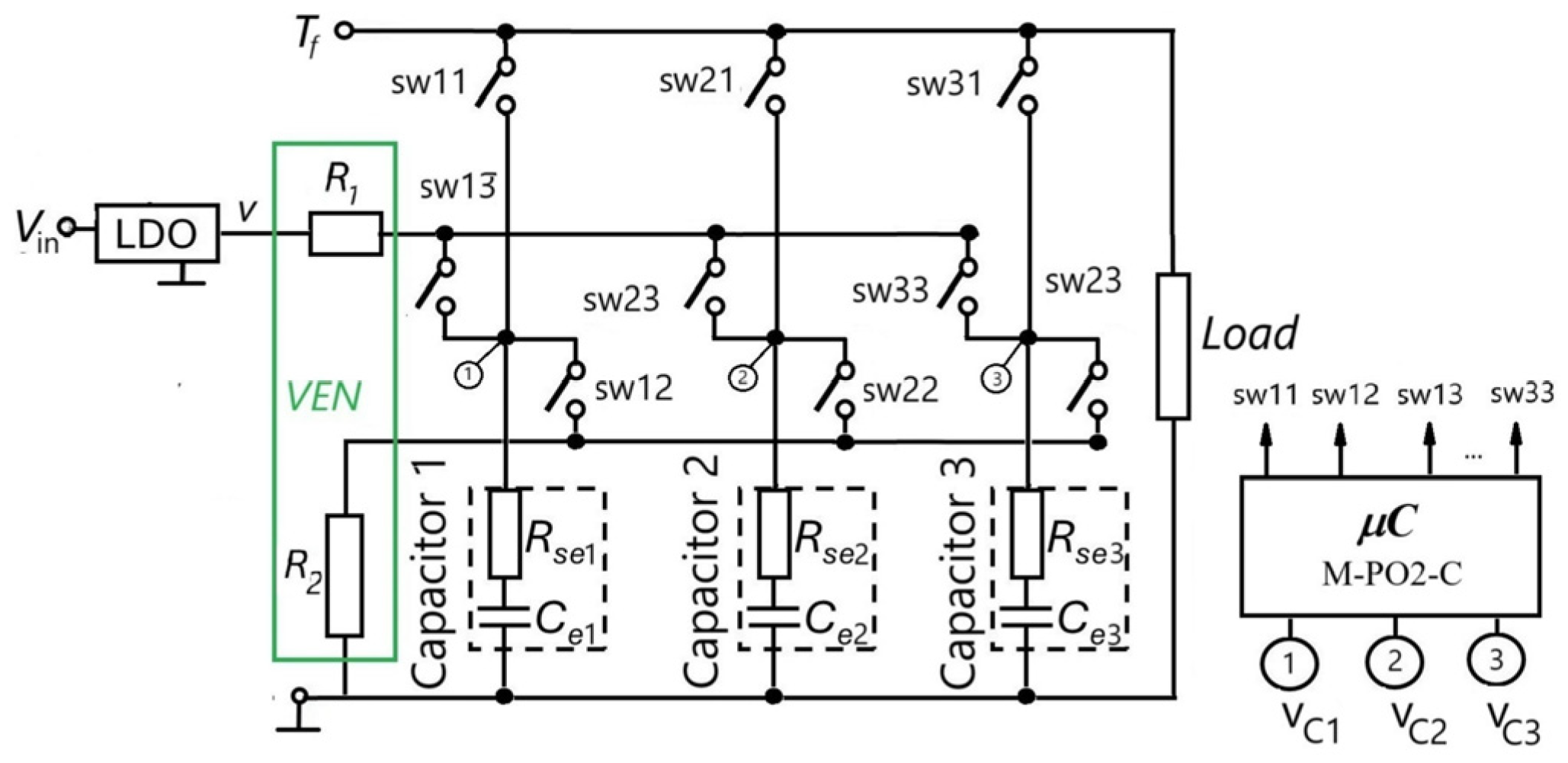

2.2. Basic Electrical Diagram for Estimating the Equivalent Parameters of the Capacitors That Make up the Output Filter of a DC–DC Buck Converter

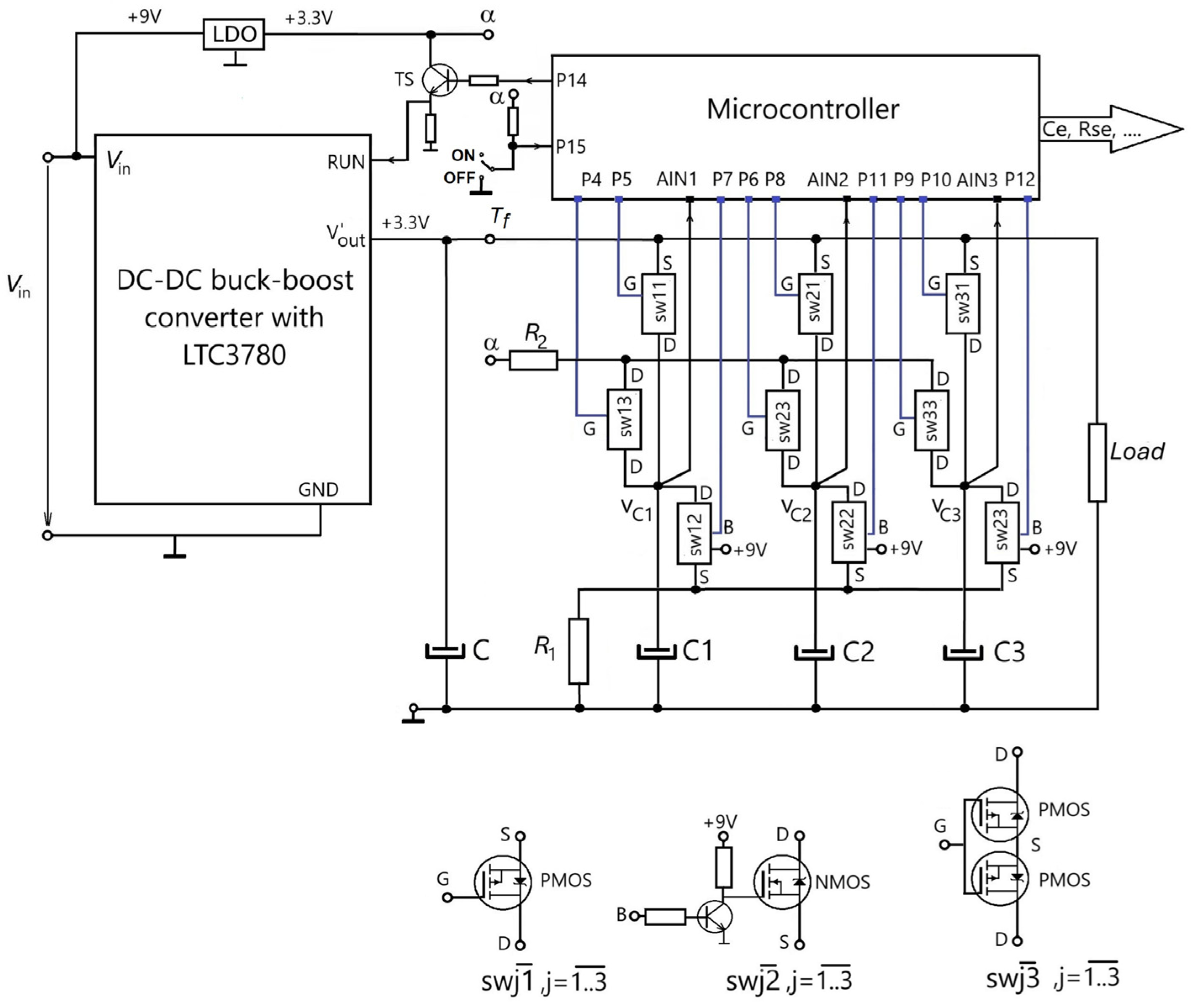

3. DC–DC Buck Converter Based on the Proposed Principle Diagram

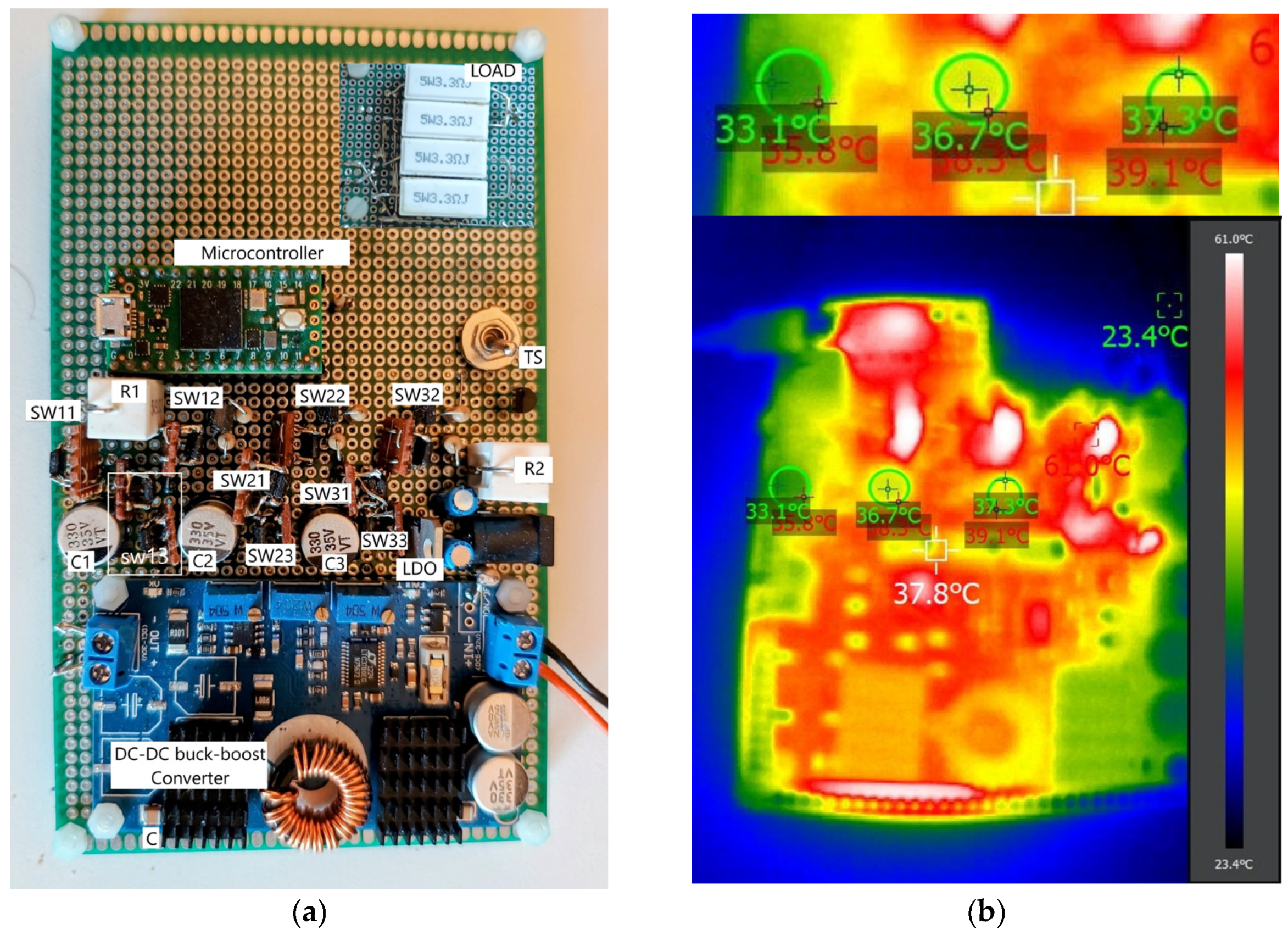

3.1. Implementation

3.2. Experimental Results

4. Discussion

- (i)

- The experiments performed with the DC–DC converter in Figure 5 confirm the applicability of the principle diagram in Figure 3. Moreover, the principle of estimating the parameters of the output filter capacitors can be applied for banks with more than three capacitors. In this case, scalability issues may arise, for example, regarding the number and compatibility of the microcontroller input/outputs needed for connecting the VEN.

- (ii)

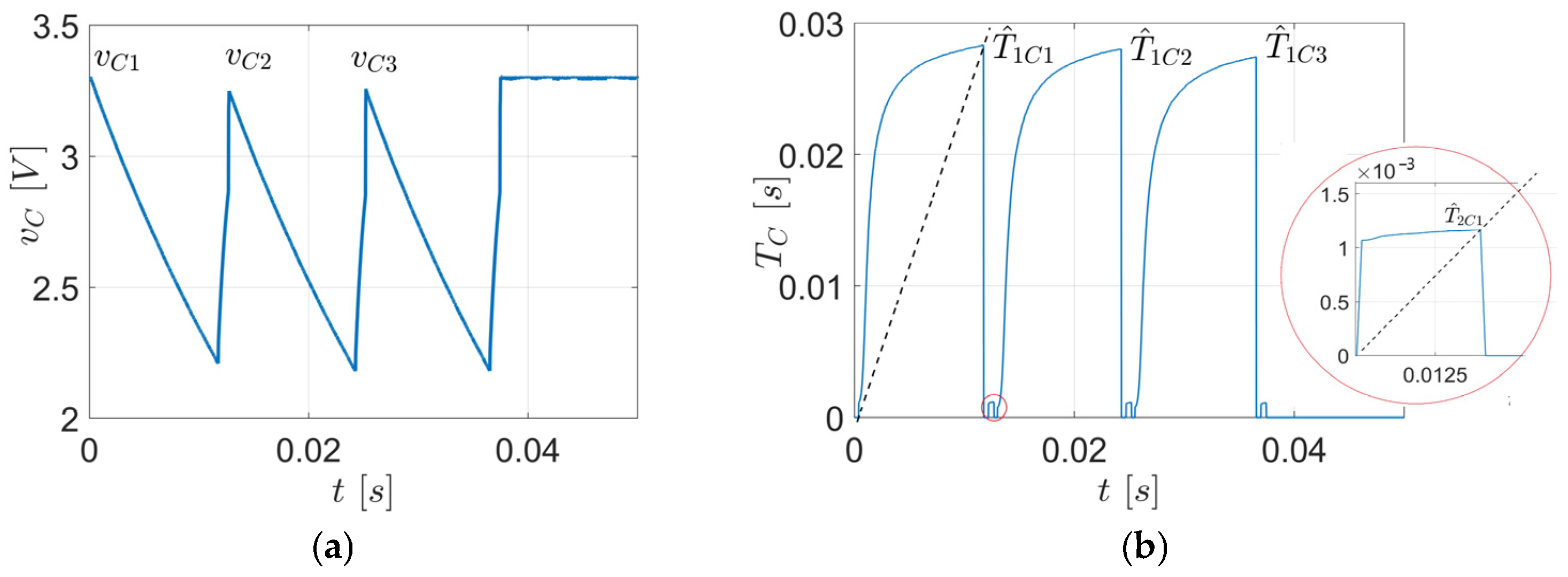

- The sum of the times in Table 3 indicates that a cycle of estimating the parameters of the three-capacitor bank is performed online and in real time, in less than .

- (iii)

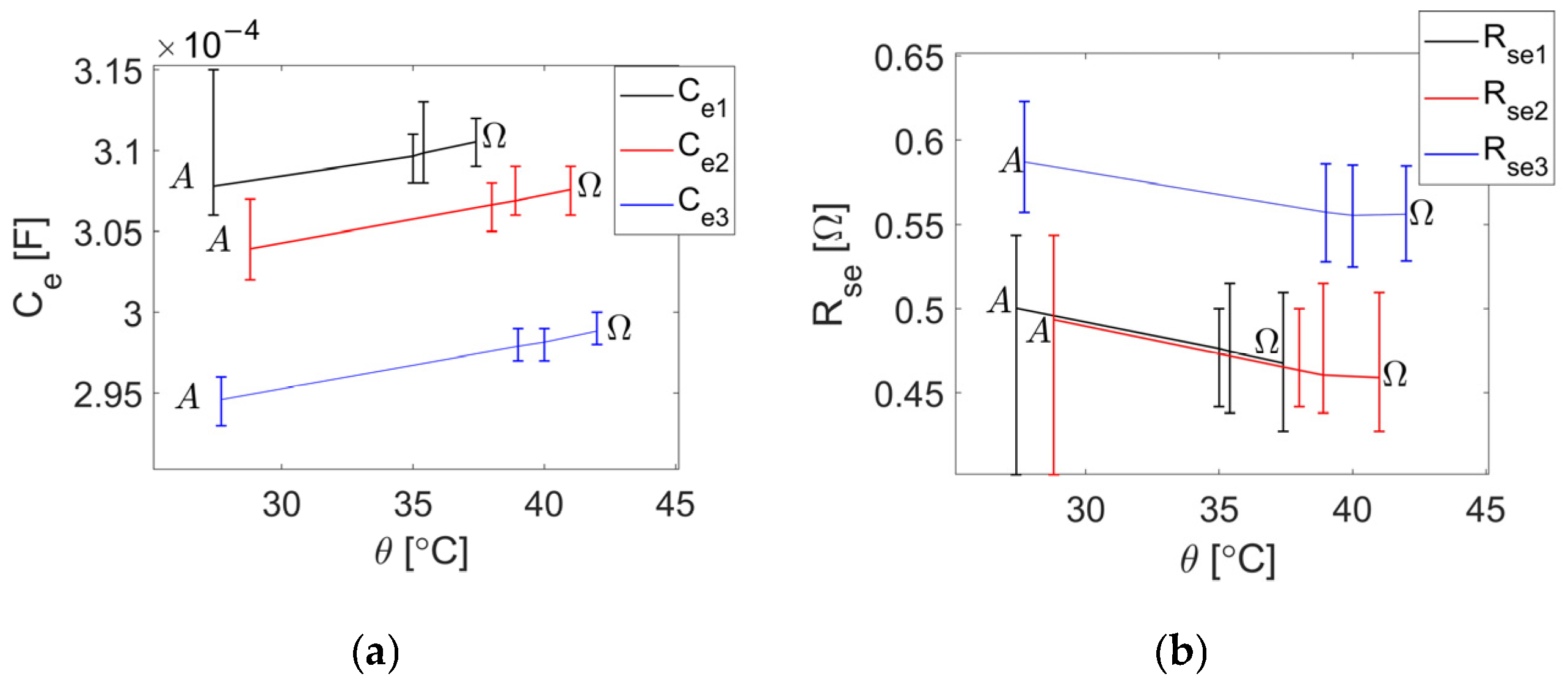

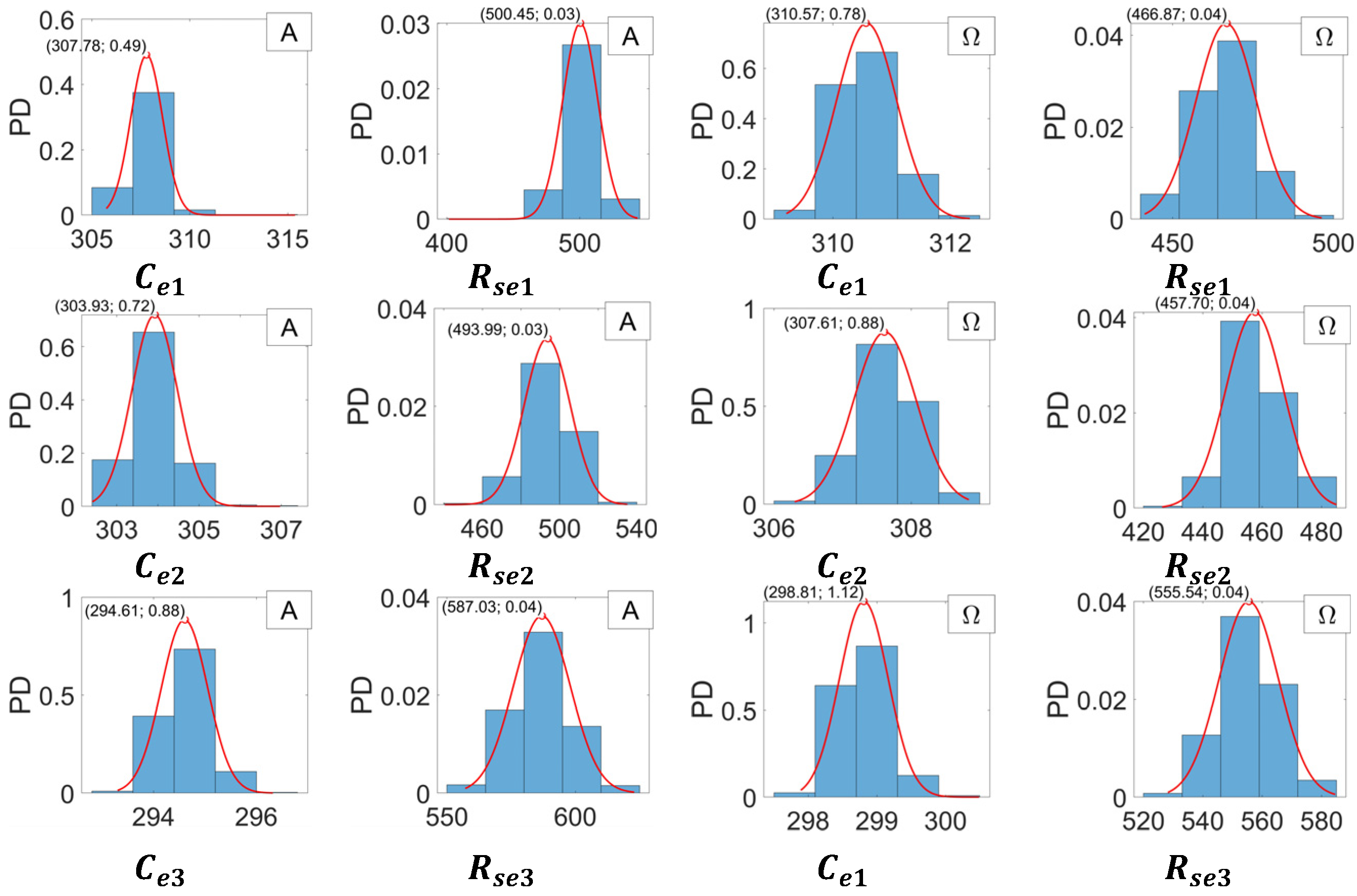

- Within each series of estimates, the temperatures of the three capacitors were different. During the experiments, they increased with effect on the average values of the equivalent parameters (Table 4) by increasing and decreasing .

- Considering that the stabilized equivalent mean values (line 1 of the series (Ω)) are correct, it is found that the values of , and of the series (A) are lower by approximately 1%, and the values of , and are higher by approx. 6–7% (last line of Table 4). Apart from , for any segment in Figure 10, the ranges of the estimated values intersect, although the mean values of / monotonically increase/decrease.

- The purpose of the configuration illustrated in Figure 3 is to estimate the capacitor parameters during the converter’s current operation. The triggering estimation depends on the management of diagnosis and prognosis. The above observations are crucial for defining these moments. The decision can only be made by the designer and/or converter user. They should also take into consideration the specific constructive elements, the environmental conditions, and the working regime of the converter.

- (iv)

- In the discharge/charge circuits of a capacitor, both the equivalent resistance of the capacitor and the conduction resistance of the switch transistor act as resistive elements. Therefore, the values in Table 4 correspond to the sum , where is the corrected value of ESR. The MOSFET transistors were chosen with a minimum control signal in the grid and conduction resistance as low as possible, i.e., . Their effect on the ESR values in the series of Table 4 is illustrated in Table 5. The values are reduced by 2.14% for C1, 2.18% for C2 and 1.8% for C3. The mean square deviation in percentage remains practically the same. If the bank capacitors had been of better quality, with a lower ESR, the weight in the estimation result using the presented method would have been higher.

- (v)

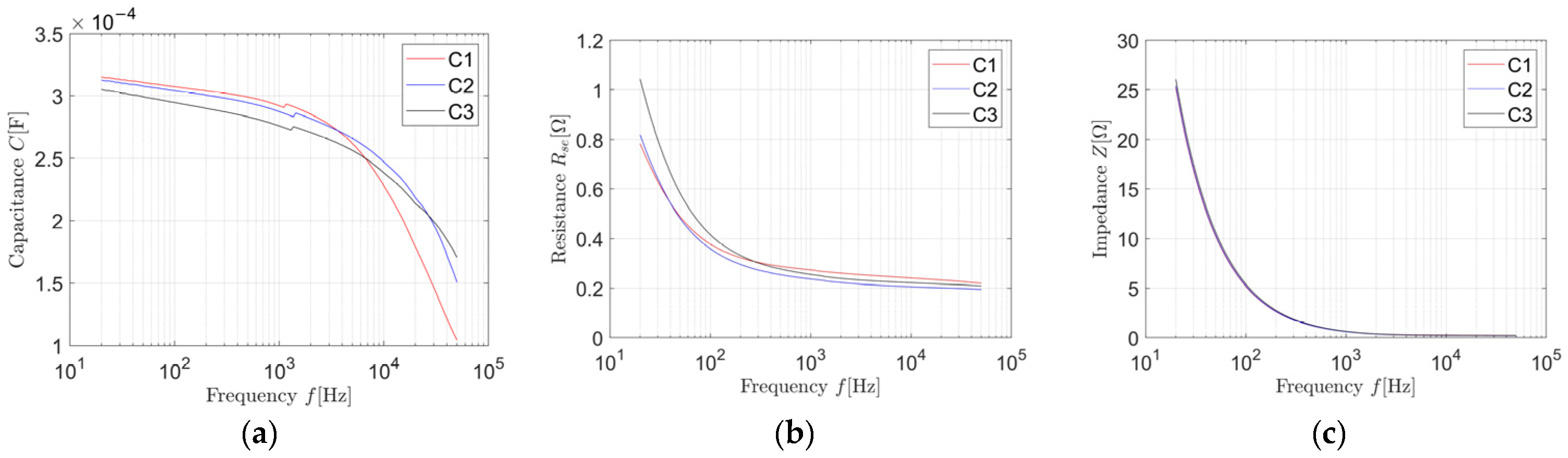

- A notable fact is the closeness of the frequencies associated with the average values of the equivalent parameters in Table 4 established on the frequency characteristics in Figure 7. They are given in Table 6 for the series of experiments (). The fact that the pairs of values (, ), correspond, according to Figure 7, to very close average frequencies (, , ), suggests that the presented estimation method associates an equivalent frequency to the equivalent values of the capacitor parameters. The attribute “equivalent” designates in this case both the association with the equivalent circuit and the association with the capacitor discharge/charge voltage signal spectrum.

- (vi)

- PO2 can be implemented on the same microcontroller interfaced with the converter integrated circuit, and the diagram in Figure 5 can be partially integrated into a single dedicated circuit [31]. The estimation cycle can be triggered whenever it is relevant during the operation of the converter, and the calculated parameters can be transmitted to the upper level of a maintenance application. It is also important to note that the number of monitored capacitors can be adapted as needed.

- (vii)

- The experiments were performed with a DC–DC buck-boost converter made with the LTC 3780 integrated circuit operating in buck mode at an output voltage of and with a resistive load aimed to validate the method for estimating the parameters of a filter capacitor bank. These values were chosen, on the one hand, from conditions of direct compatibility with the input voltage levels of the microcontroller, and on the other hand, so as not to charge the converter with a large load. To apply the proposed method for higher output voltage levels, both in buck and boost mode, it is necessary to complete the configuration with level shifter stages for adapting the converter voltages to the microcontroller.

- (viii)

- The estimation of capacitor parameters with the proposed model should be considered as an operation, part of the maintenance strategy chosen by the converter user. For this purpose, the microcontroller transmits to a higher level of maintenance structure the estimated values of C and ESR. The following aspects are useful for adopting a strategy:

- PO2 estimates the capacitance and ESR values by repeating cycles that may contain 1, 2, or 3 sequences.

- The estimations can be made continuously on preset time intervals, without interrupting the converter operation. They can highlight the following, in real time: (i) the aging effect when the capacitance decreases and the ESR increases, and (ii) the large variations in the time constants specific to the pre-breakdown regime when the insulation resistance decreases.

- Through additional operations, after each estimation cycle consisting of three sequences, an equivalent bank capacity can be calculated based on a bank model.

- The schematic allows, through additional control, performing maintenance operations at the capacitor level, not the capacitor bank. Thus, extracting and replacing a faulty capacitor can be discharged and disconnected without converter shutdown, as in the case of the estimation. This means a higher level of reliability at the system level by avoiding the system shutdown.

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| ESR | Equivalent Serial Resistance |

| LDO | Low Dropout Regulators |

| PO | Parameter Observer |

| PO2 | Parameter Observer on Two Edges |

| RUL | Remaining useful life |

| VEN | Variable Electrical Network |

Appendix A

| Paper/Year of Publication | Treated Issue | Complexity/Prototype/Simulation | Capacitors Monitoring | Observations |

|---|---|---|---|---|

| [17]/2014 | Methods for increasing the reliability of capacitors for DC-link applications in power electronic converters | Overview paper | - | - Capacitor banks are treated as a whole - A method for designing capacitor banks to optimize reliability, cost, and size |

| [18]/2016 | Description and classification of methods for monitoring the health of capacitors | Overview paper | - | Data and advanced algorithm-based methods category treats power electronic converters as a black box or semi-black box (can be used for capacitor banks) |

| [14]/2018 | Health monitoring of each capacitor of a bank using Physics of Failure models updated sequentially with Extended Kalman Filter algorithm | - Prototype with experimental results after 400 h of aging - DSP used for acquisition and data processing - No individual sensor for each capacitor needed | Estimates capacity and ESR for each capacitor of a bank based on models and electrical inputs measured with sensors for the entire bank | - |

| [19]/2019 | DC-link capacitors in three-phase pulsewidth modulation ac–dc–ac power converters | A VEN unit is used for each capacitor in the bank. | C and ESR of dc-link capacitors are estimated through VEN units during the discharging process. | A series capacitor bank consisting of several capacitors is employed to sustain the intermediate circuit voltage. |

| [12]/2020 | Health monitoring techniques for capacitors used in power electronics converters | - Overview paper - The monitoring methods mentioned vary in their level of complexity | - Methods for monitoring the parameters of individual capacitors; - Monitoring the equivalent parameters of the capacitor bank as a whole | Considerations about mixed banks containing multiple types of capacitors. |

| [20]/2022 | Design of a Rogowski coil for online monitoring of a single-capacitor in the dc bank. | Complex as Rogowski coils sensor are integrated in PCB and offer small signals. | - Monitoring each capacitor in DC-link bank - Practical performance assessment of the circuit | ESR at high-frequency region as a new aging indicator. |

| [21]/2022 | Quasi off-line monitoring of the time constant for discharging circuit during converter shutdown | - Prototype | Monitoring for DC-link bank capacitors | Optimizing the sampling frequency to reduce noises |

| [22]/2023 | Monitor ESR and C of each capacitor in a dc-link capacitor bank with PCB integrated Rogowski coils as sensors. | Complex as Rogowski coils and other sensors are integrated in the PCB circuit. | - Monitoring individual capacitor in the bank; - After temperature standardization provides monitoring and prediction for each capacitor | - Theoretical analysis, simulation and laboratory experimental setup using a single-phase inverter. |

| [23]/2023 | Monitor capacitor condition in a dc-link of power converters, following active methodology by signal injecting to estimate the ESR and C of a dc-link capacitor. | Complex as it implies signal injection | Monitoring of capacitor DC-link bank as a whole | - Capacitor parameter estimation method comparison from execution time point of view; - Theoretical analysis and microgrid laboratory experimental setup |

| [24]/2025 | High-gain adaptive observer for estimating floating voltages and monitoring capacitors aging in multicell converters | Simulation for 3-cell converter | - Simultaneous estimation of states and parameters in a p-cell converter, - Does not apply to each capacitor of a bank | - Good balance between estimation accuracy and computational feasibility - Needs a high-performance current sensor and sufficiently powerful computing software for commercial implementation |

References

- Bacha, S.; Munteanu, I.; Bratcu, A.I. Power Electronic Converters Modeling and Control; Springer: London, UK, 2014. [Google Scholar] [CrossRef]

- Chen, Y.; Zhang, B. Equivalent-Small-Parameter Analysis of DC/DC Switched-Mode Converter; CPSS Power Electronics Series; Springer: Singapore, 2019. [Google Scholar] [CrossRef]

- Bhargava, C.; Sharma, P.K.; Senthilkumar, M.; Padmanaban, S.; Ramachandaramurthy, V.K.; Leonowicz, Z.; Blaabjerg, F.; Mitolo, M. Review of Health Prognostics and Condition Monitoring of Electronic Components. IEEE Access 2020, 8, 75163–75183. [Google Scholar] [CrossRef]

- Amaral, A.M.R.; Cardoso, A.J.M. Estimating Aluminum Electrolytic Capacitors Condition Using a Low Frequency Transformer Together with a DC Power Supply. In IEEE International Symposium on Industrial Electronics; Institute of Electrical and Electronics Engineers: New York, NY, USA, 2010; pp. 815–820. [Google Scholar] [CrossRef]

- Leong, C.; Wong, C.; Lan, C. An Online ESR Estimation Method for Output Capacitor of DC-DC Boost Converter Without Current Sensor. IEEE Trans. Power Electron. 2024, 40, 2196–2209. [Google Scholar] [CrossRef]

- Buiatti, G.M.; Amaral, A.M.R.; Cardoso, A.J.M. An Online Technique for Estimating the Parameters of Passive Components in Non-Isolated DC/DC Converters. In Proceedings of the IEEE International Symposium on Industrial Electronics, Vigo, Spain, 4–7 June 2007; pp. 606–610. [Google Scholar] [CrossRef]

- Cen, Z. Capacitance Online Estimation Based on Adaptive Model Observer. MATEC Web Conf. 2016, 77, 02006. [Google Scholar] [CrossRef]

- TDK. B32672L Film Capacitors Metallized Polypropylene Film Capacitors (MKP); TDK: Tokyo, Japan, 2019. [Google Scholar]

- Li, H.; Huang, X.; Li, Z.; Li, H.; Wang, W.; Wang, B.; Zhang, Q.; Lin, F. Modeling of ESR in Metallized Film Capacitors and Its Implication on Pulse Handling Capability. Microelectron. Reliab. 2015, 55, 1046–1053. [Google Scholar] [CrossRef]

- Zhao, Z.; Davari, P.; Lu, W.; Wang, H.; Blaabjerg, F. An Overview of Condition Monitoring Techniques for Capacitors in DC-Link Applications. IEEE Trans. Power Electron. 2021, 36, 3692–3716. [Google Scholar] [CrossRef]

- Amaral, A.M.R.; Laadjal, K.; Cardoso, A.J.M. Assessment of Aluminum Electrolytic Capacitors Health Status Through Signal-Based Techniques. In Proceedings of the 2024 IEEE 21st International Power Electronics and Motion Control Conference, PEMC, Pilsen, Czech Republic, 30 September–3 October 2024; Institute of Electrical and Electronics Engineers Inc.: New York, NY, USA, 2024. [Google Scholar] [CrossRef]

- Dang, H.L.; Kwak, S. Review of Health Monitoring Techniques for Capacitors Used in Power Electronics Converters. Sensors 2020, 20, 3740. [Google Scholar] [CrossRef] [PubMed]

- Sundararajan, P.; Sathik, M.H.M.; Sasongko, F.; Tan, C.S.; Pou, J.; Blaabjerg, F.; Gupta, A.K. Condition Monitoring of DC-Link Capacitors Using Goertzel Algorithm for Failure Precursor Parameter and Temperature Estimation. IEEE Trans. Power Electron. 2020, 35, 6386–6396. [Google Scholar] [CrossRef]

- Gupta, Y.; Ahmad, M.W.; Narale, S.; Anand, S. Health Estimation of Individual Capacitors in a Bank with Reduced Sensor Requirements. IEEE Trans. Ind. Electron. 2019, 66, 7250–7259. [Google Scholar] [CrossRef]

- Chen, M.; Wang, H.; Wang, H.; Blaabjerg, F.; Wang, X.; Pan, D. Reliability Assessment of Hybrid Capacitor Bank Using Electrolytic- and Film-Capacitors in Three-Level Neutral-Point-Clamped Inverters. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 17–21 March 2019; pp. 2826–2832. [Google Scholar] [CrossRef]

- Narale, S.B.; Kumar, P.N.; Ahmad, M.W.; Verma, A.; Anand, S. Reliability Comparison of Dc Link Capacitor Bank for Different Configurations. In Proceedings of the IEEE International Conference on Industrial Technology, Melbourne, Australia, 13–15 February 2019; pp. 1023–1027. [Google Scholar] [CrossRef]

- Wang, H.; Blaabjerg, F. Reliability of Capacitors for DC-Link Applications in Power Electronic Converters—An Overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar] [CrossRef]

- Soliman, H.; Wang, H.; Blaabjerg, F. A Review of the Condition Monitoring of Capacitors in Power Electronic Converters. IEEE Trans. Ind. Appl. 2016, 52, 4976–4989. [Google Scholar] [CrossRef]

- Wu, Y.; Du, X. A VEN Condition Monitoring Method of DC-Link Capacitors for Power Converters. IEEE Trans. Ind. Electron. 2019, 66, 1296–1306. [Google Scholar] [CrossRef]

- Liu, Y.; Bai, J.; Huang, M.; Zha, X. An Online Monitoring Method for Single Aluminum Electrolytic Capacitor in the DC Bank of Single-Phase Inverter Based on the Rogowski Coil. IEEE Trans. Power Electron. 2022, 37, 12647–12658. [Google Scholar] [CrossRef]

- Baumann, T.F.; Papastergiou, K.; Garcia, R.M.; Peftitsis, D. A Quasi-Offline Condition Monitoring Method of DC-Link Capacitor Banks in Accelerator Power Converters. In Proceedings of the 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hanover, Germany, 5–9 September 2022; pp. 1–12. [Google Scholar]

- Zhu, M.; Liu, Y.; Huang, M.; Li, Z.; Zha, X. A Digital Twin System of Capacitive DC Bank Using Rogowski Coil to Monitor Individual Capacitors. IEEE Trans. Power Electron. 2023, 38, 9251–9260. [Google Scholar] [CrossRef]

- Ribeiro, R.L.A.; Sangwongwanich, A.; Alves, D.K.; Blaabjerg, F.; de Oliveira Alves Rocha, T.A. Wavelet-Based Estimation Method for Online Condition Monitoring of Dc-Link Capacitors of Distributed Energy Resources. Int. J. Electr. Power Energy Syst. 2023, 151, 109141. [Google Scholar] [CrossRef]

- Nait Slimani, B.; Ghanes, M.; Djennoune, S. High-Gain Adaptive Observer for Floating Voltages Estimation and Capacitor Aging Monitoring in Multicell Converters. Eng. Sci. Technol. Int. J. 2025, 65, 102036. [Google Scholar] [CrossRef]

- Cen, Z.; Stewart, P. Condition Parameter Estimation for Photovoltaic Buck Converters Based on Adaptive Model Observers. IEEE Trans. Reliab. 2017, 66, 148–160. [Google Scholar] [CrossRef]

- Meng, J.; Chen, E.X.; Ge, S.J. Online E-Cap Condition Monitoring Method Based on State Observer. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition, PEAC, Shenzhen, China, 4–7 November 2018. [Google Scholar] [CrossRef]

- Gara, H.; Ben Saad, K. Fault Detection for Linear Switched Systems Based on a Bank of Luenberger Observers. In Proceedings of the 2018 International Conference on Advanced Systems and Electric Technologies, IC_ASET, Hammamet, Tunisia, 22–25 March 2018; Institute of Electrical and Electronics Engineers Inc.: New York, NY, USA, 2018; pp. 92–97. [Google Scholar] [CrossRef]

- Bărbulescu, C.; Căiman, D.V.; Nanu, S.; Dragomir, T.L. Implementation of Parameter Observer for Capacitors. Sensors 2023, 23, 948. [Google Scholar] [CrossRef] [PubMed]

- Căiman, D.V.; Bărbulescu, C.; Nanu, S.; Dragomir, T.L. DC-DC Buck Converters with Quasi-Online Estimation of Filter Capacitor Equivalent Parameters. Appl. Sci. 2024, 14, 10756. [Google Scholar] [CrossRef]

- LTC3780 Datasheet and Product Info|Analog Devices. Available online: https://www.analog.com/en/products/ltc3780.html (accessed on 21 July 2025).

- PJRC. Teensy 4.0. Available online: https://www.pjrc.com/store/teensy40.html (accessed on 4 August 2025).

| Id | Figure 7a, [29] | Figure 7b, [29] | Figure 7c, [29] | Figure 7d, [29] | Figure 3 |

|---|---|---|---|---|---|

| 1. | 1 | 1 | 1 | 2 | 3 |

| 2. | 1 | 1 | 2 | 2 or 4 | 2 |

| 3. | |||||

| 4. | PO2 | PO2 | PO | PO | PO2 |

| 5. | quasi-online /quasi-online | quasi-online /quasi-online | quasi-online /online | 1quasi-online+1online /online | 1quasi-online+2online /online (*) |

| 6. | - | - | - | successive | successive |

| 7. | or | (**) |

| Id. | Meaning |

|---|---|

| 1. | Number of capacitors in the output filter. |

| 2. | Number of resistors in the VEN. |

| 3. | The process to which the capacitor is subjected during the estimation. |

| 4. | Type of parameter observer. |

| 5. | Participation of the monitored capacitors in the filtering operation during the estimation/continuity of the load connection to the converter during the estimation. |

| 6. | How to include the capacitors in the bank in the measurement process. |

| 7. | Number of discharges (↘)/charges (↗) supported by the evaluated capacitor during the estimation of the parameters. |

| C1 | C2 | C3 |

|---|---|---|

| , = [3.266088 V, 2.209389 V] | , = [3.216883 V, 2.18035 V] | , = [3.216076 V, 2.181156 V] |

| = 0.00048 s, = [2.628035 V, 2.865994 V] | = 0.00046 s, = [2.606256 V, 2.845828 V] | = 0.000461 s, = [2.619162 V, 2.861154 V] |

| [F] | [Ω] | [F] | [Ω] | [F] | [Ω] | |

|---|---|---|---|---|---|---|

| (A)- | ||||||

| 1. (*) | 0.000308 | 0.500353 | 0.000304 | 0.493573 | 0.000295 | 0.586933 |

| 2. | [0.000306, 0.000315] | [0.401475, 0.543484] | [0.000302, 0.000307] | [0.440476, 0.535087] | [0.000293, 0.000296] | [0.55714, 0.622899] |

| 3. | 8.13 × 10−7/ 0.247% | 0.01287/ 2.572% | 5.54 × 10−7/ 0.169% | 0.011034/ 2.235% | 4.51 × 10−7/ 0.124% | 0.010091/ 1.719% |

| 4. | 301/75.25% | 292/73% | 275/68.75% | 276/69% | 275/75.25% | 278/73% |

| (Ω)- | ||||||

| 1. (**) | 0.000311 | 0.467614 | 0.000308 | 0.458981 | 0.000299 | 0.556098 |

| 2. | [0.000309, 0.000312] | [0.42724, 0.509411] | [0.000306, 0.000309] | [0.4263, 0.513102] | [0.000298, 0.0003] | [0.528205, 0.584585] |

| 3. | 5.18 × 10−7/ 0.162% | 0.00989/ 2.114% | 4.64 × 10−7/ 0.148% | 0.010116/ 2.204% | 3.67 × 10−7/ 0.120% | 0.009489/ 1.706% |

| 4. | 281/70.25% | 283/70.75% | 270/67.5% | 278/69.5% | 284/70.25% | 277/70.75% |

| Deviations of (*) from (**) | ||||||

| −0.9646% | +7% | −1.2987% | +7.5366% | −1.3377% | +5.5448% | |

| [Ω] | [Ω] | [Ω] | [Ω] | [Ω] | [Ω] |

|---|---|---|---|---|---|

| 0.467614 | 0.457614 | 0.458981 | 0.448981 | 0.556098 | 0.546098 |

| [F] | [Ω] | [F] | [Ω] | [F] | [Ω] |

|---|---|---|---|---|---|

| 0.00031054 * | 0.457614 | 0.0003075 * | 0.448981 | 0.0002988374 * | 0.546098 |

| 53.88 Hz | 58.27 Hz | 55.3 Hz | 58.27 Hz | 52.49 Hz | 56.77 Hz |

|  |  | |||

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Căiman, D.-V.; Bărbulescu, C.; Nanu, S.; Dragomir, T.-L. Output Filtering Capacitor Bank Monitoring for a DC–DC Buck Converter. Electronics 2025, 14, 3614. https://doi.org/10.3390/electronics14183614

Căiman D-V, Bărbulescu C, Nanu S, Dragomir T-L. Output Filtering Capacitor Bank Monitoring for a DC–DC Buck Converter. Electronics. 2025; 14(18):3614. https://doi.org/10.3390/electronics14183614

Chicago/Turabian StyleCăiman, Dadiana-Valeria, Corneliu Bărbulescu, Sorin Nanu, and Toma-Leonida Dragomir. 2025. "Output Filtering Capacitor Bank Monitoring for a DC–DC Buck Converter" Electronics 14, no. 18: 3614. https://doi.org/10.3390/electronics14183614

APA StyleCăiman, D.-V., Bărbulescu, C., Nanu, S., & Dragomir, T.-L. (2025). Output Filtering Capacitor Bank Monitoring for a DC–DC Buck Converter. Electronics, 14(18), 3614. https://doi.org/10.3390/electronics14183614