An E-Band High-Precision Active Phase Shifter Based on Inductive Compensation and Series Peaking Enhancement Techniques

Abstract

1. Introduction

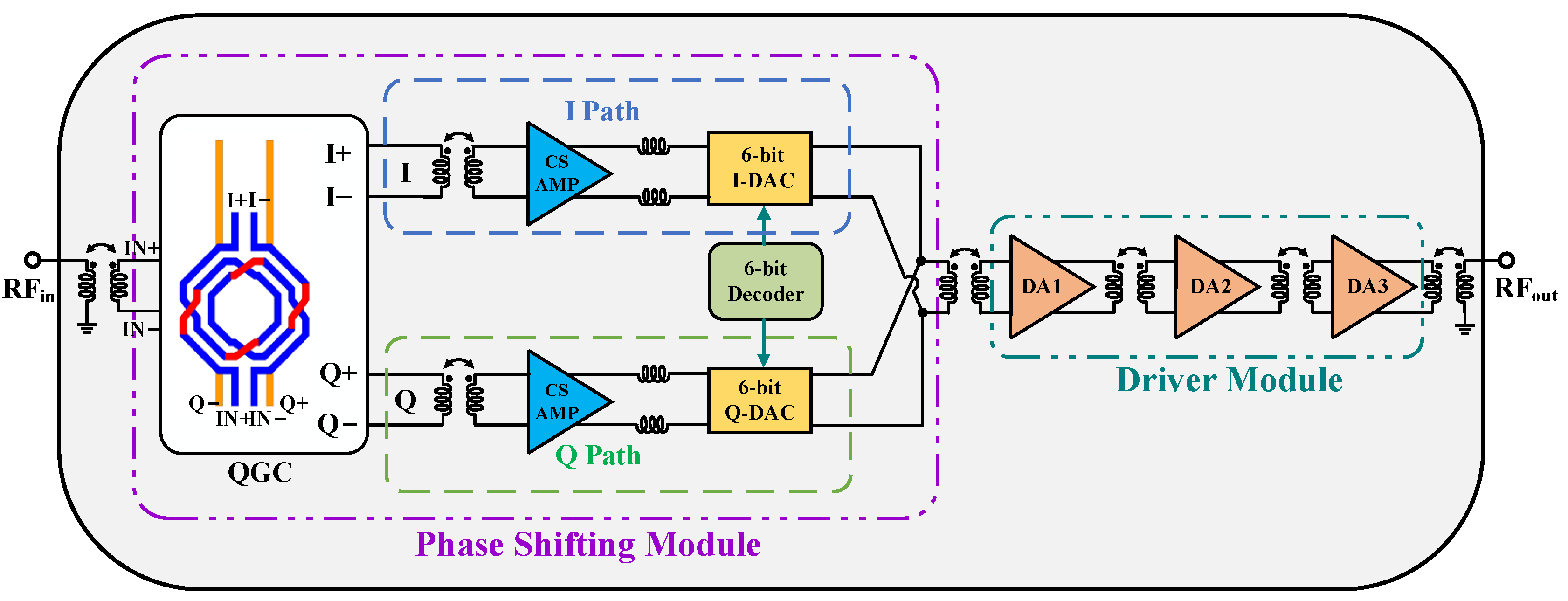

2. Circuit Design of the Proposed PS

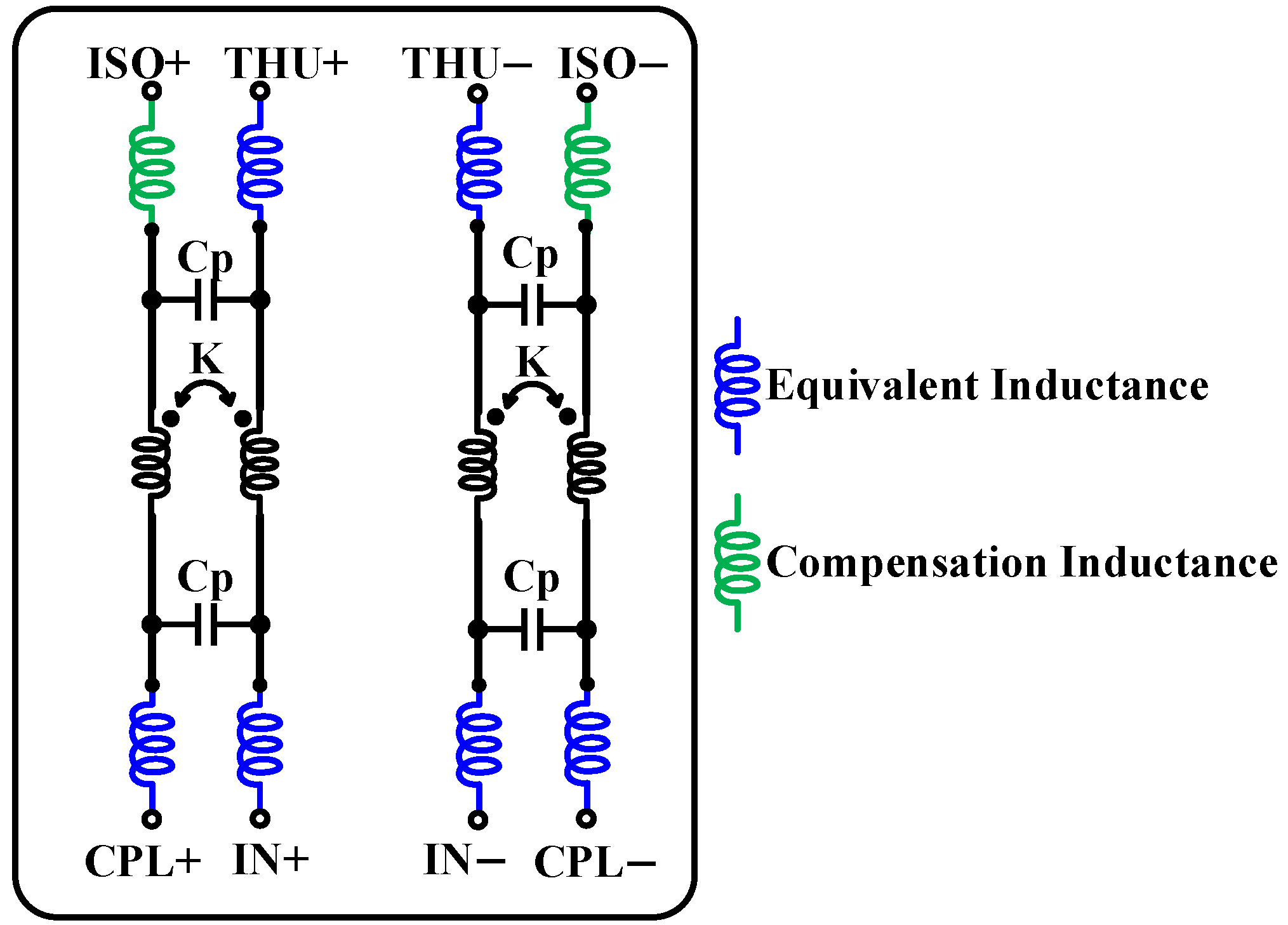

2.1. Compact Impedance-Compensated and Capacitor-Free QGC

- ,

- ,

- ,

- ,

- , .

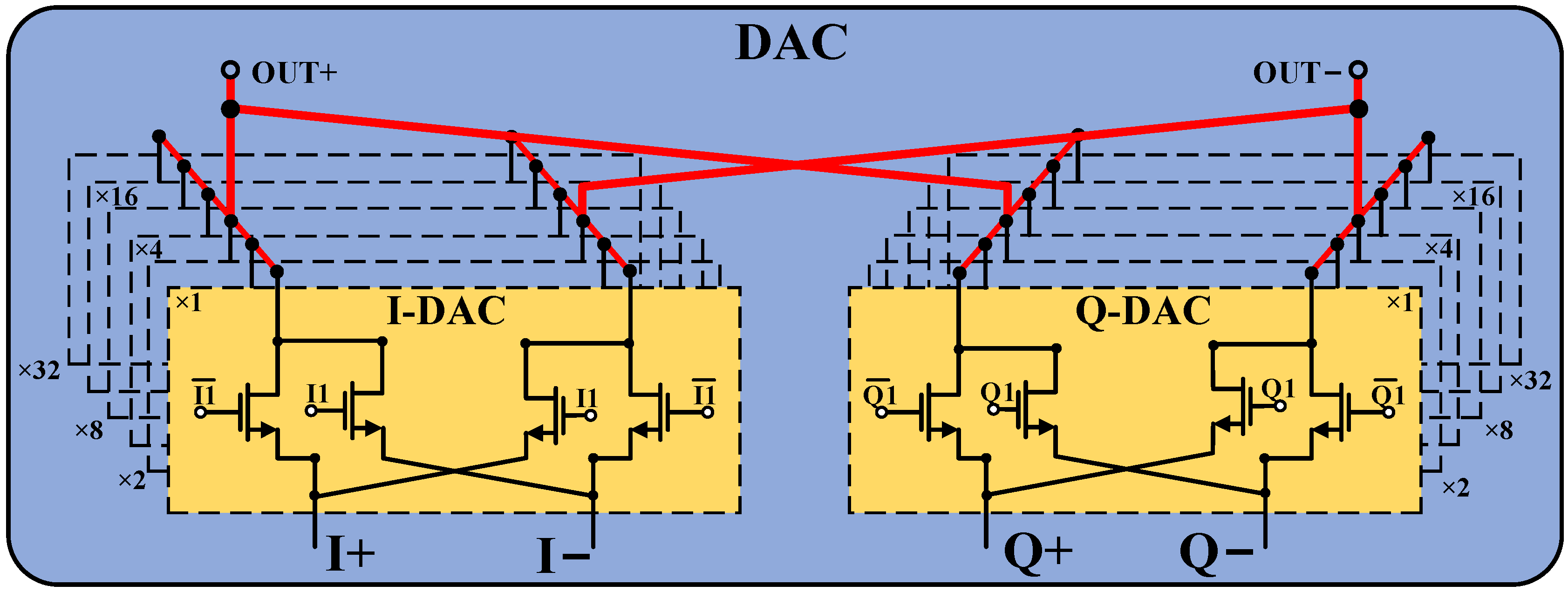

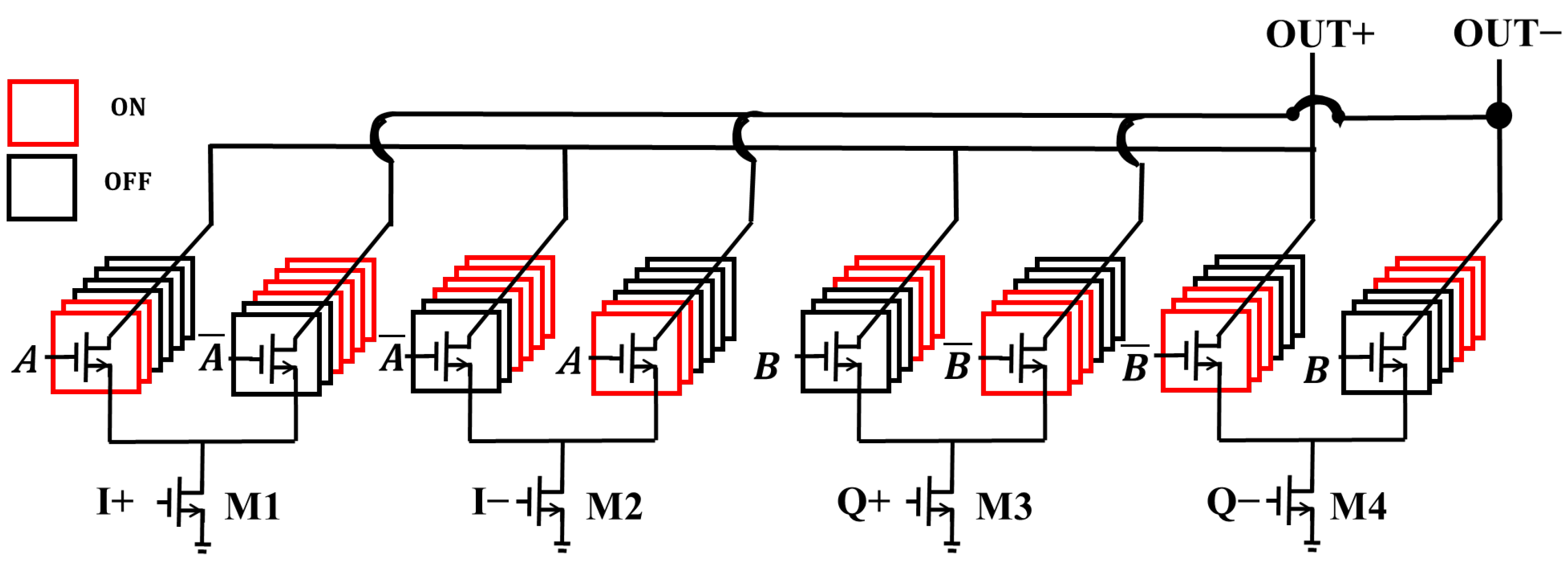

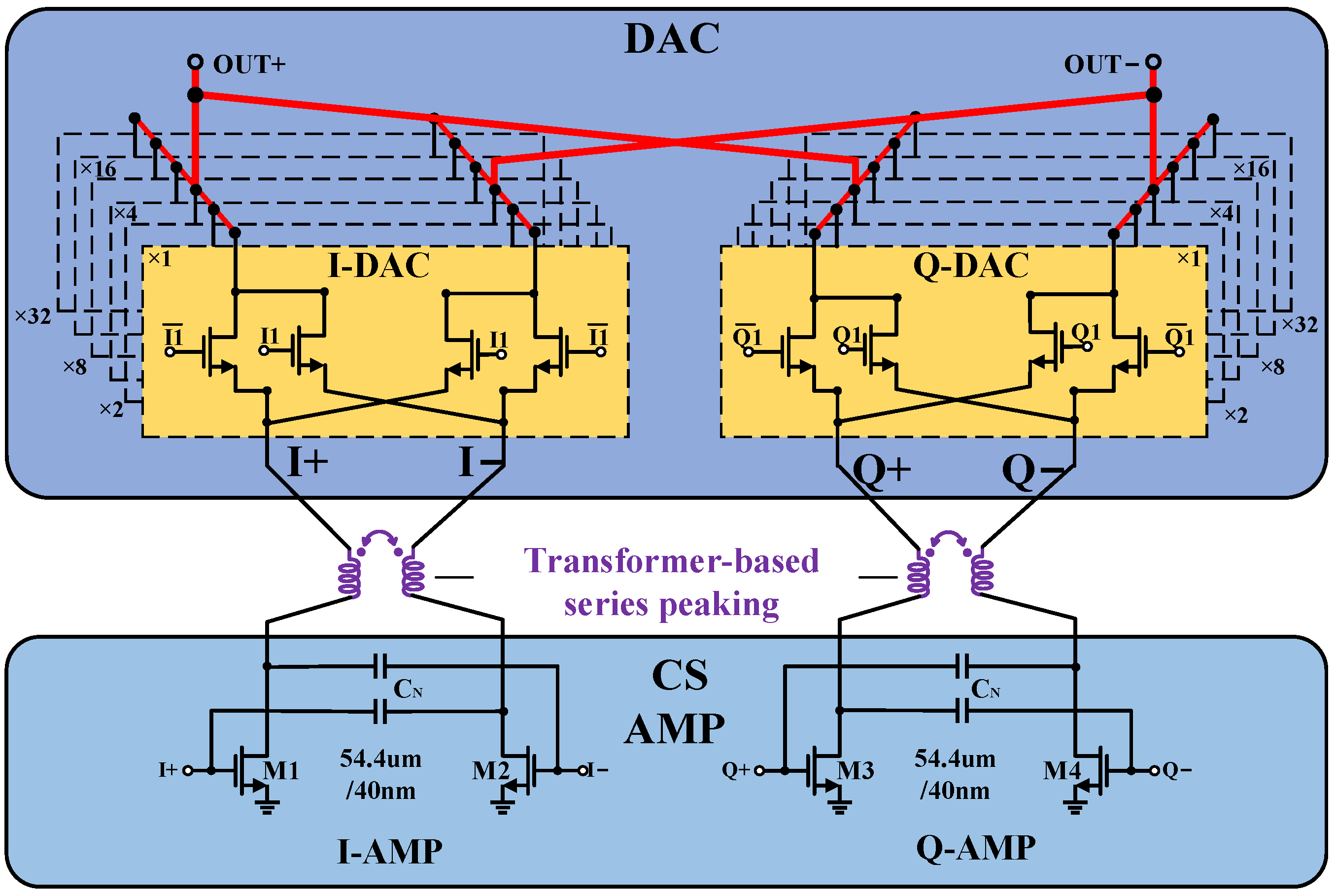

2.2. Complementary Switch-Type I/Q Path DAC Design

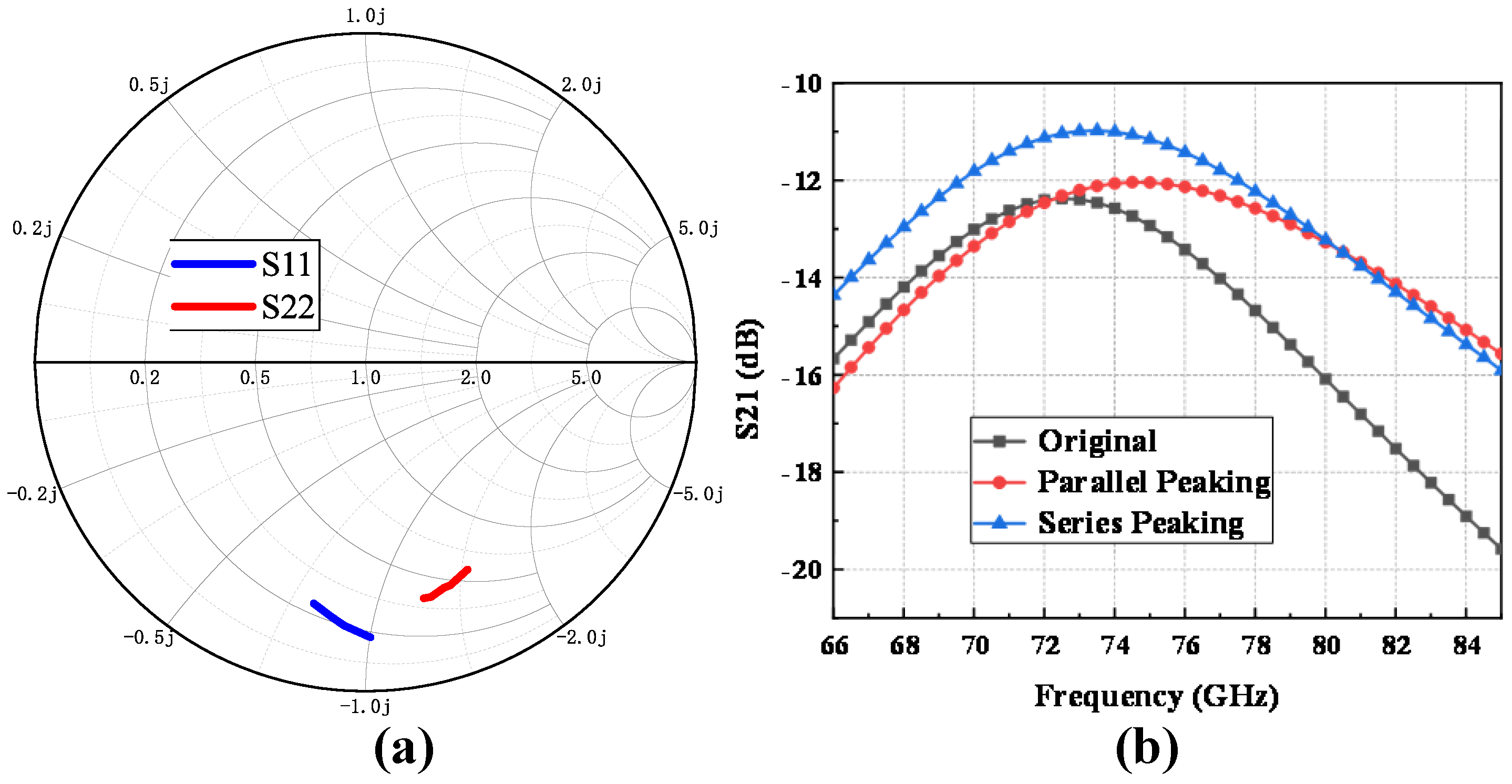

2.3. Series Peaking Enhancement Technique

- (1)

- Bandwidth Optimization: By adding series inductance, the 3 dB bandwidth of the PS increases from 7.6 GHz to 10 GHz, a 31.5% increase. This improvement alleviates the frequency deviation effects during testing, reducing the risk of the measured frequency deviating from the target frequency band, thereby enhancing the stability of the results.

- (2)

- Gain Enhancement: The introduction of series inductance significantly improves the peak gain of the PS (an increase of 1.3 dB), thus optimizing the transmitter link gain. This improvement reduces the design complexity of the subsequent power amplifier and enhances the overall link efficiency.

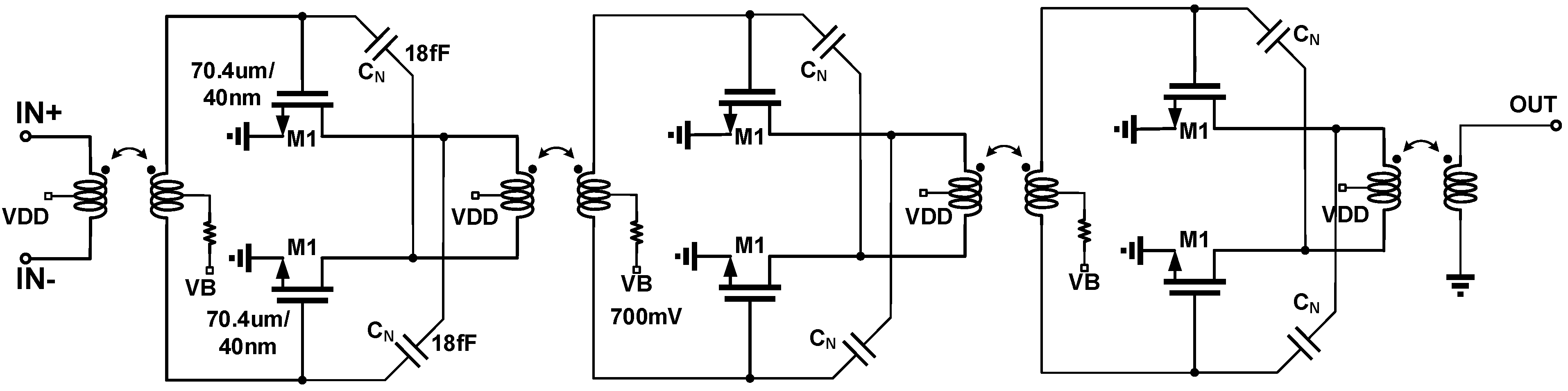

2.4. Driver Module Design

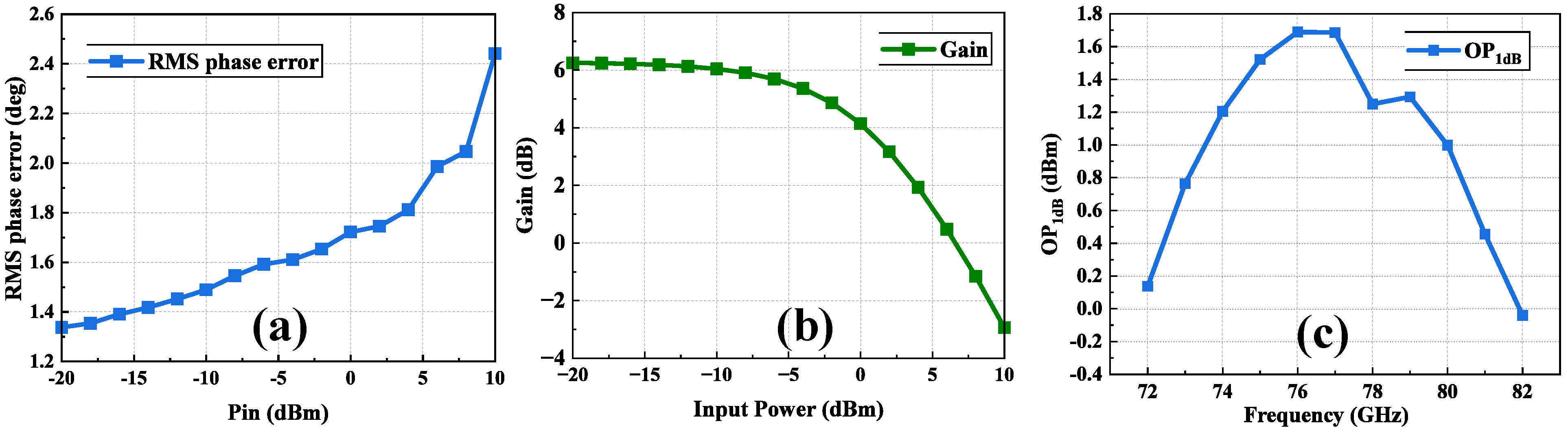

2.5. Large-Signal Simulation Results

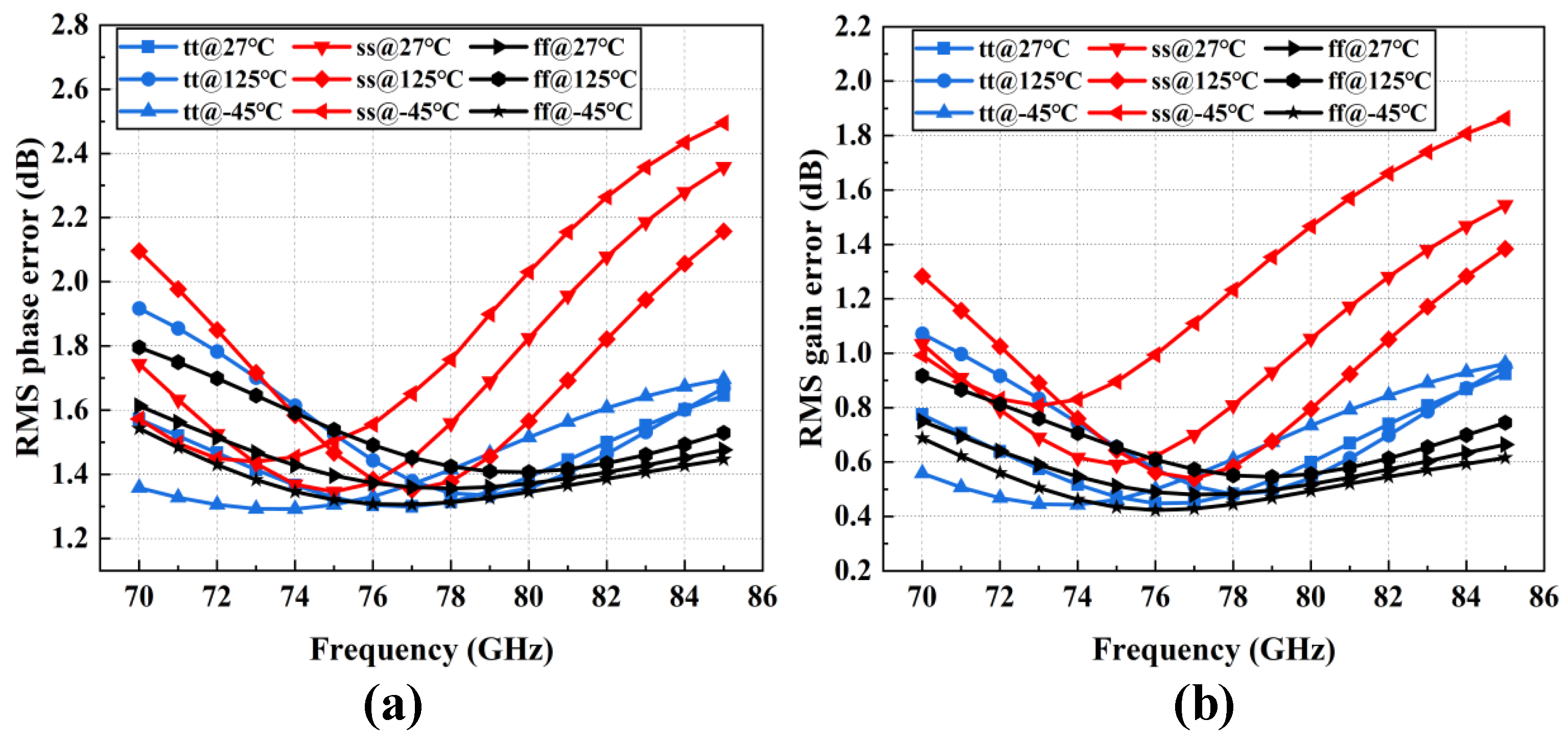

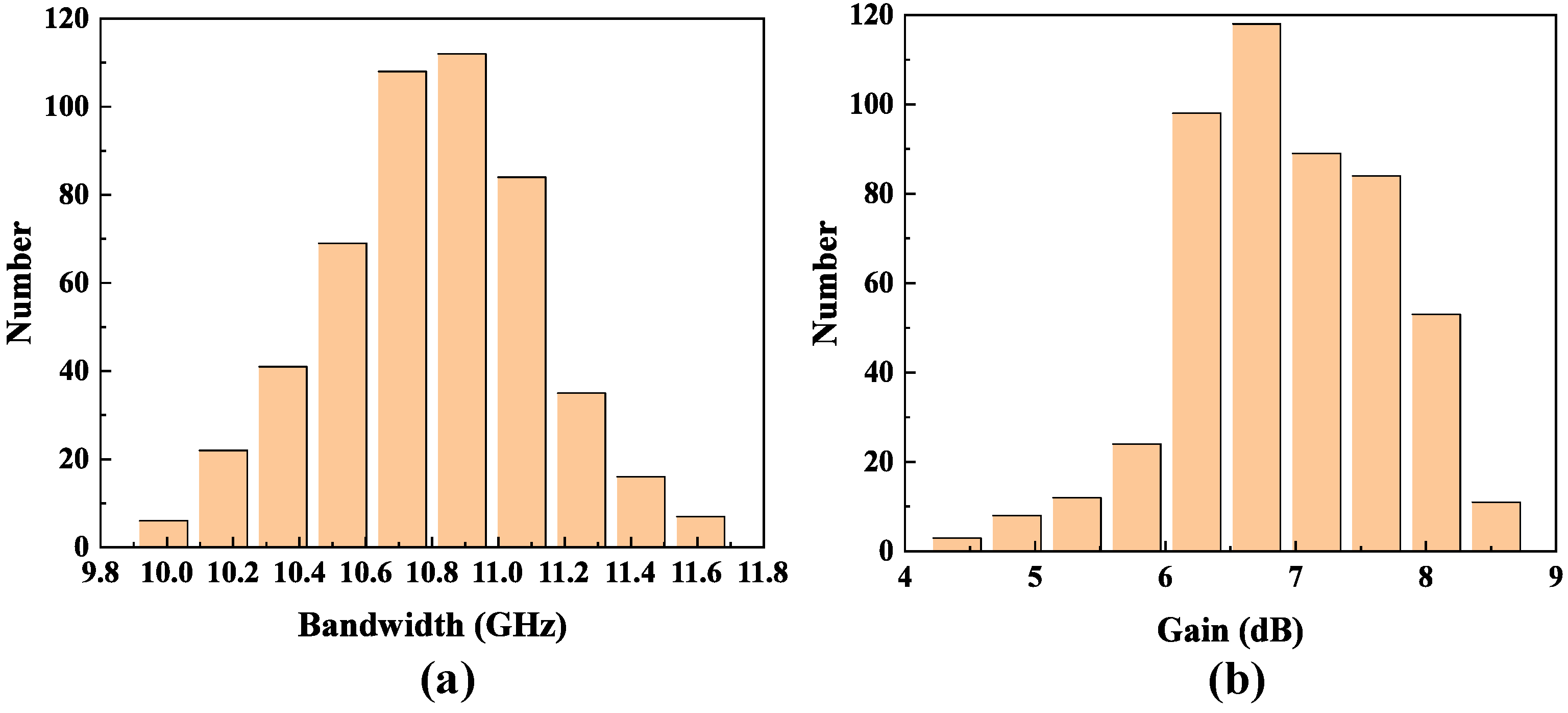

2.6. Process/Temperature Variation and Monte Carlo Analysis

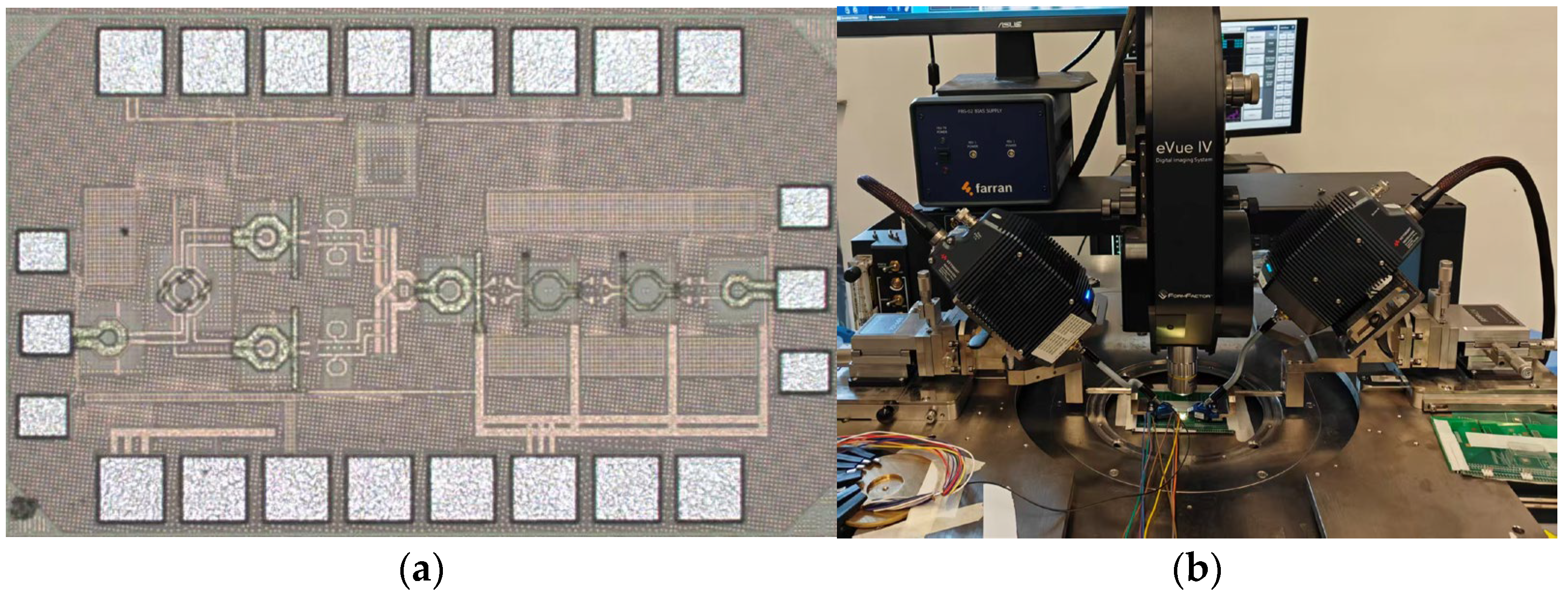

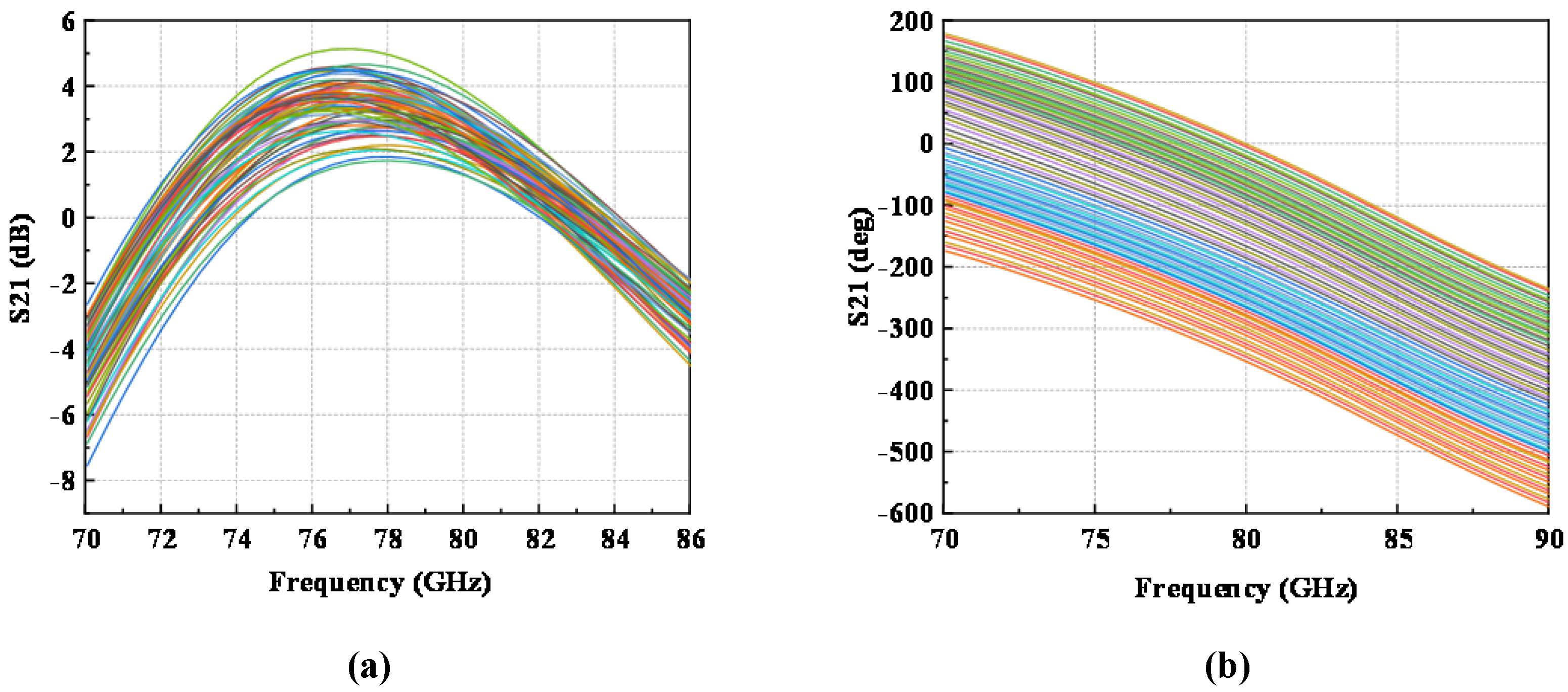

3. Measurement Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Sowlati, T.; Sarkar, S.; Perumana, B.; Chan, W.L.; Afshar, B.; Boers, M.; Shin, D.; Mercer, T.; Chen, W.H.; Toda, A.P.; et al. A 60GHz 144-element phased-array transceiver with 51dBm maximum EIRP and ±60° beam steering for backhaul application. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 66–68. [Google Scholar] [CrossRef]

- Kibaroglu, K.; Sayginer, M.; Rebeiz, G.M. A Low-Cost Scalable 32-Element 28-GHz Phased Array Transceiver for 5G Communication Links Based on a 2 × 2 Beamformer Flip-Chip Unit Cell. IEEE J. Solid-State Circuits 2018, 53, 1260–1274. [Google Scholar] [CrossRef]

- Sadhu, B.; Tousi, Y.; Hallin, J.; Sahl, S.; Reynolds, S.K.; Renström, Ö.; Sjögren, K.; Haapalahti, O.; Mazor, N.; Bokinge, B.; et al. A 28-GHz 32-Element TRX Phased-Array IC with Concurrent Dual-Polarized Operation and Orthogonal Phase and Gain Control for 5G Communications. IEEE J. Solid-State Circuits 2017, 52, 3373–3391. [Google Scholar] [CrossRef]

- Zhu, W.; Lv, W.; Liao, B.; Zhu, Y.; Dai, Y.; Li, P.; Zhang, L.; Wang, Y. A 21 to 30-GHz Merged Digital-Controlled High Resolution Phase Shifter-Programmable Gain Amplifier with Orthogonal Phase and Gain Control for 5-G Phase Array Application. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 67–70. [Google Scholar] [CrossRef]

- Trinh, K.T.; Lin, C.-H.; Kao, H.-L.; Chiu, H.-C.; Karmakar, N.C. 18–20 GHz Compact Passive 4-Bit GaAs MMIC Phase Shifter with Low Insertion Loss. In Proceedings of the 2019 IEEE Asia-Pacific Microwave Conference (APMC), Singapore, 10–13 December 2019; pp. 968–970. [Google Scholar] [CrossRef]

- Chen, C.-Y.; Wang, Y.-S.; Lin, Y.-H.; Hsiao, Y.-H.; Wu, Y.-C.; Wang, H. A 36–40 GHz full 360° ultra-low phase error passive phase shifter with a novel phase compensation technique. In Proceedings of the 2017 47th European Microwave Conference (EuMC), Nuremberg, Germany, 10–12 October 2017; pp. 1245–1248. [Google Scholar] [CrossRef]

- Tian, Y.; Gu, J.; Xu, H.; Liu, W.; Duan, Z.; Gao, H.; Yan, N. A 26-32GHz 6-bit Bidirectional Passive Phase Shifter with 14dBm IP1dB and 2.6° RMS Phase Error for Phased Array System in 40nm CMOS. In Proceedings of the 2023 IEEE/MTT-S International Microwave Symposium—IMS 2023, San Diego, CA, USA, 11–16 June 2023; pp. 195–198. [Google Scholar] [CrossRef]

- Li, X.; Liu, B.; Fu, H.; Ma, K. A 30–36 GHz Passive Hybrid Phase Shifter with a Transformer-Based High-Resolution Reflect-Type Phase Shifting Technique. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2419–2423. [Google Scholar] [CrossRef]

- Duan, Z.; Wang, Y.; Lv, W.; Dai, Y.; Lin, F. A 6-bit CMOS Active Phase Shifter for Ku-Band Phased Arrays. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 615–617. [Google Scholar] [CrossRef]

- Cetindogan, B.; Ozeren, E.; Ustundag, B.; Kaynak, M.; Gurbuz, Y. A 6 Bit Vector-Sum Phase Shifter with a Decoder Based Control Circuit for X-Band Phased-Arrays. IEEE Microw. Wirel. Compon. Lett. 2016, 26, 64–66. [Google Scholar] [CrossRef]

- Wu, T.; Zhao, C.; Liu, H.; Wu, Y.; Yu, Y.; Kang, K. A 51.5–64.5 GHz Active Phase Shifter Using Linear Phase Control Technique with 1.4° Phase resolution in 65-nm CMOS. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 59–62. [Google Scholar] [CrossRef]

- Zhang, X.; Deng, B.; Sun, L.; Pan, D.; Cheng, L. A W-Band 0.18-dB RMS Gain and 0.97° Phase Error Active Phase Shifter in 28-nm CMOS. IEEE Microw. Wirel. Technol. Lett. 2024, 34, 923–926. [Google Scholar] [CrossRef]

- Huang, D.; Zhang, L.; Li, D.; Zhang, L.; Wang, Y.; Yu, Z. A 60-GHz 360° 5-Bit Phase Shifter with Constant IL Compensation Followed by a Normal Amplifier with ±1 dB Gain Variation and 0.6-dBm OP −1dB. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1437–1441. [Google Scholar] [CrossRef]

- Xia, J.; Farouk, M.; Boumaiza, S. Digitally-Assisted 27-33 GHz Reflection-Type Phase Shifter with Enhanced Accuracy and Low IL-Variation. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 63–66. [Google Scholar] [CrossRef]

- Huang, D.; Zhang, L.; Zhu, H.; Chen, B.; Tang, Y.; Wang, Y. A 94GHz 2×2 Phased-Array FMCW Imaging Radar Transceiver with 11dBm Output Power and 10.5dB NF in 65nm CMOS. In Proceedings of the 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2–4 June 2019; pp. 47–50. [Google Scholar] [CrossRef]

- Zhou, J.; Qian, H.J.; Luo, X. A 9-Bit Vector-Sum Digital Phase Shifter Using High Resolution VGAs and Compensated Quadrature Signal Generator. In Proceedings of the 2019 IEEE MTT-S International Microwave Conference on Hardware and Systems for 5G and Beyond (IMC-5G), Atlanta, GA, USA, 15–16 August 2019; pp. 1–3. [Google Scholar] [CrossRef]

- Huang, S.; Wang, Y.; Feng, G. A Compact 53–62 GHz Phase Shifter with Series Peaking Technique in 40-nm CMOS Technology. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 4407–4411. [Google Scholar] [CrossRef]

- So, C.; Sung, E.-T.; Hong, S. A 60-GHz Variable Gain Phase Shifter Based on Body Floated RF-DAC Structure. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 4749–4753. [Google Scholar] [CrossRef]

- Que, X.; Jiang, L.; Huang, S.; Wang, Y. A CMOS E-Band Reconfigurable Series Doherty Power Amplifier for 6-/12-dB Back-Off Efficiency Enhancement. IEEE Microw. Wirel. Technol. Letters 2025, 35, 1202–1205. [Google Scholar] [CrossRef]

- Pepe, D.; Zito, D. Two mm-Wave Vector Modulator Active Phase Shifters with Novel IQ Generator in 28 nm FDSOI CMOS. IEEE J. Solid-State Circuits 2017, 52, 344–356. [Google Scholar] [CrossRef]

- Jang, J.; Kim, B.; Kim, C.-Y.; Hong, S. 79-GHz Digital Attenuator-Based Variable-Gain Vector-Sum Phase Shifter with High Linearity. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 693–695. [Google Scholar] [CrossRef]

- Park, G.H.; Byeon, C.W.; Park, C.S. A 60-GHz Low-Power Active Phase Shifter with Impedance-Invariant Vector Modulation in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2020, 68, 5395–5407. [Google Scholar] [CrossRef]

- Sung, E.-T.; Wang, S.; Hong, S. A 60-GHz Polar Vector Modulator with Lookup Table-Based Calibration. IEEE Microw. Wirel. Compon. Lett. 2021, 31, 572–574. [Google Scholar] [CrossRef]

- Quan, X.; Yi, X.; Boon, C.C.; Yang, K.; Li, C.; Liu, B.; Liang, Z.; Zhuang, Y. A 52–57 GHz 6-Bit Phase Shifter with Hybrid of Passive and Active Structures. IEEE Microw. Wirel. Compon. Lett. 2018, 28, 236–238. [Google Scholar] [CrossRef]

| Refs | CMOS Process | Frequency (GHz) | Resolution (bits) | RMS Phase Error (deg) | RMS Gain Error (dB) | Peak Gain (dB) | DC Power (mW) | Core Area (mm2) | FoM (dB) |

|---|---|---|---|---|---|---|---|---|---|

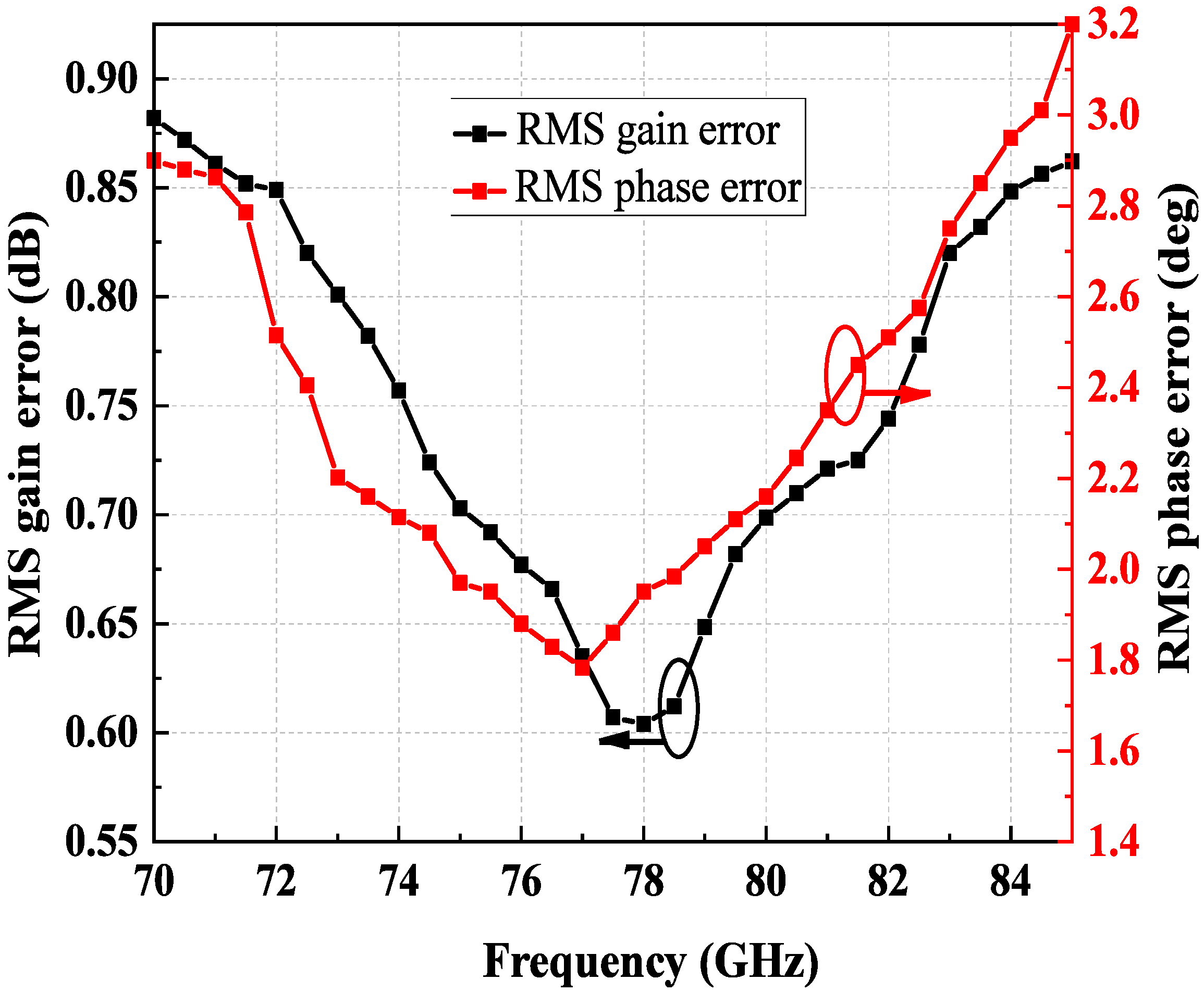

| This work | 40 nm | 72.3–82.3 | 6 | 1.78–2.55 | 0.6–0.75 | 5.1 | 57.2 | 0.26 | 86.4 |

| [20] | 28 nm | 78.8–92.8 | 4 | 9.4–11.9 | 1.68–2 | 2.3 | 21.6 | 0.12 | 66.8 |

| JSSC’17 | |||||||||

| [21] | 65 nm | 79 * | 5 | 6.74 | 1.89 | −11.4 | 24.7 | 0.14 | 35.5 * |

| MWCL’18 | |||||||||

| [22] | 65 nm | 51–66.3 | 5 | 7 | 0.72 | −1.8 | 5 | 0.3 | 67.6 |

| TMTT’20 | |||||||||

| [23] | 28 nm | 55–64 | 5 | 3.3 | 0.47 | −3.02 | 15.4 | 0.41 | 64.4 |

| MWCL’21 | |||||||||

| [24] | 40 nm | 52–57 | 6 | 2.8–3.76 | 2.07–2.23 | −9 | 14.3 | 0.15 | 56.5 |

| MWCL’18 | |||||||||

| [13] | 65 nm | 57–66 | 5 | 4–8 | 0.18–0.25 | −16 | 0 | 0.44 | 62.8 |

| TCAS II’17 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, L.; Cai, B.; Huang, S.; Que, X.; Wang, Y. An E-Band High-Precision Active Phase Shifter Based on Inductive Compensation and Series Peaking Enhancement Techniques. Electronics 2025, 14, 3545. https://doi.org/10.3390/electronics14173545

Jiang L, Cai B, Huang S, Que X, Wang Y. An E-Band High-Precision Active Phase Shifter Based on Inductive Compensation and Series Peaking Enhancement Techniques. Electronics. 2025; 14(17):3545. https://doi.org/10.3390/electronics14173545

Chicago/Turabian StyleJiang, Lingtao, Bing Cai, Shangyao Huang, Xianfeng Que, and Yanjie Wang. 2025. "An E-Band High-Precision Active Phase Shifter Based on Inductive Compensation and Series Peaking Enhancement Techniques" Electronics 14, no. 17: 3545. https://doi.org/10.3390/electronics14173545

APA StyleJiang, L., Cai, B., Huang, S., Que, X., & Wang, Y. (2025). An E-Band High-Precision Active Phase Shifter Based on Inductive Compensation and Series Peaking Enhancement Techniques. Electronics, 14(17), 3545. https://doi.org/10.3390/electronics14173545