Suppression of Cohesive Cracking Mode Based on Anisotropic Porosity in Sintered Silver Die Attach Encapsulated by Epoxy Molding Compounds

Abstract

1. Introduction

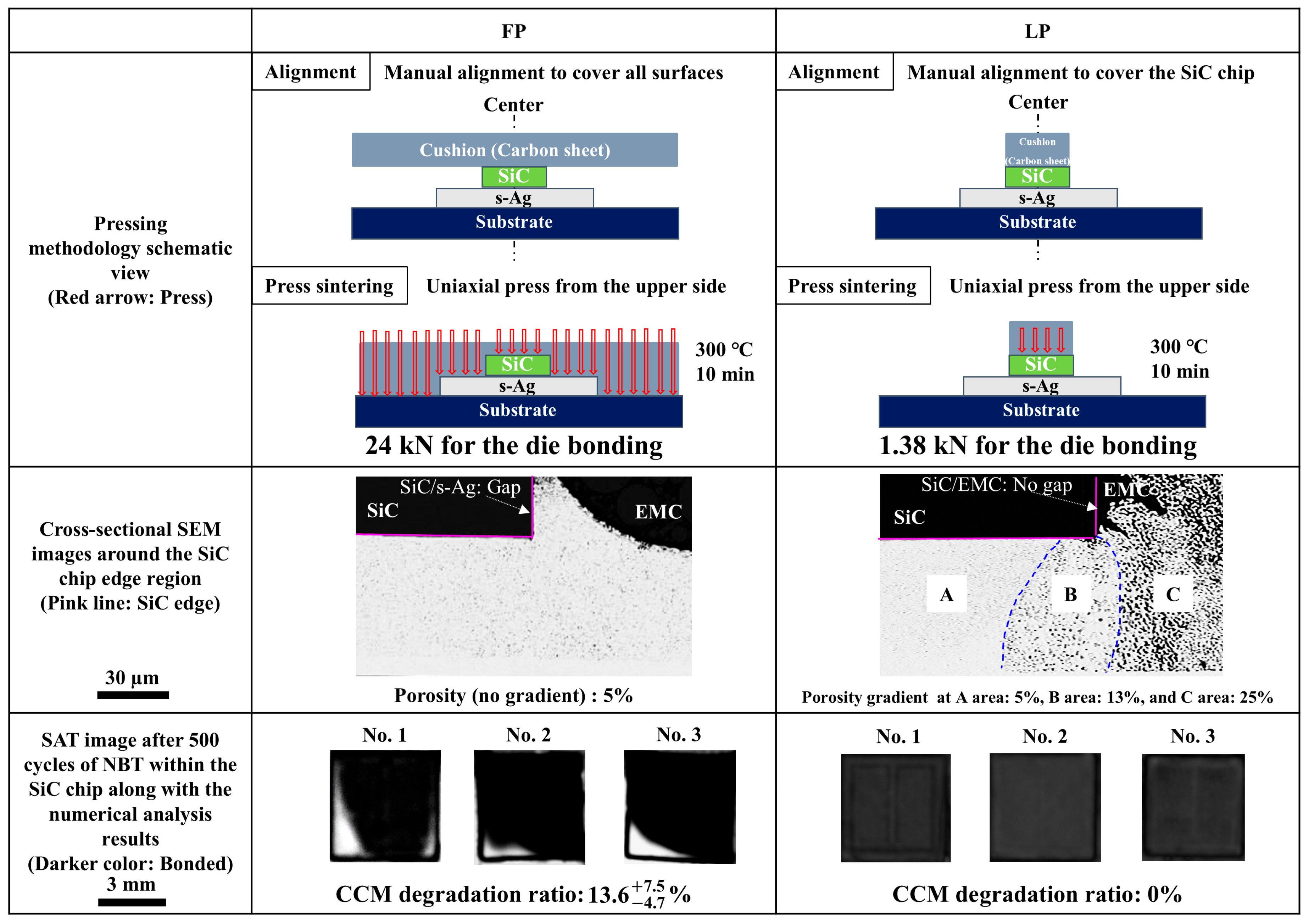

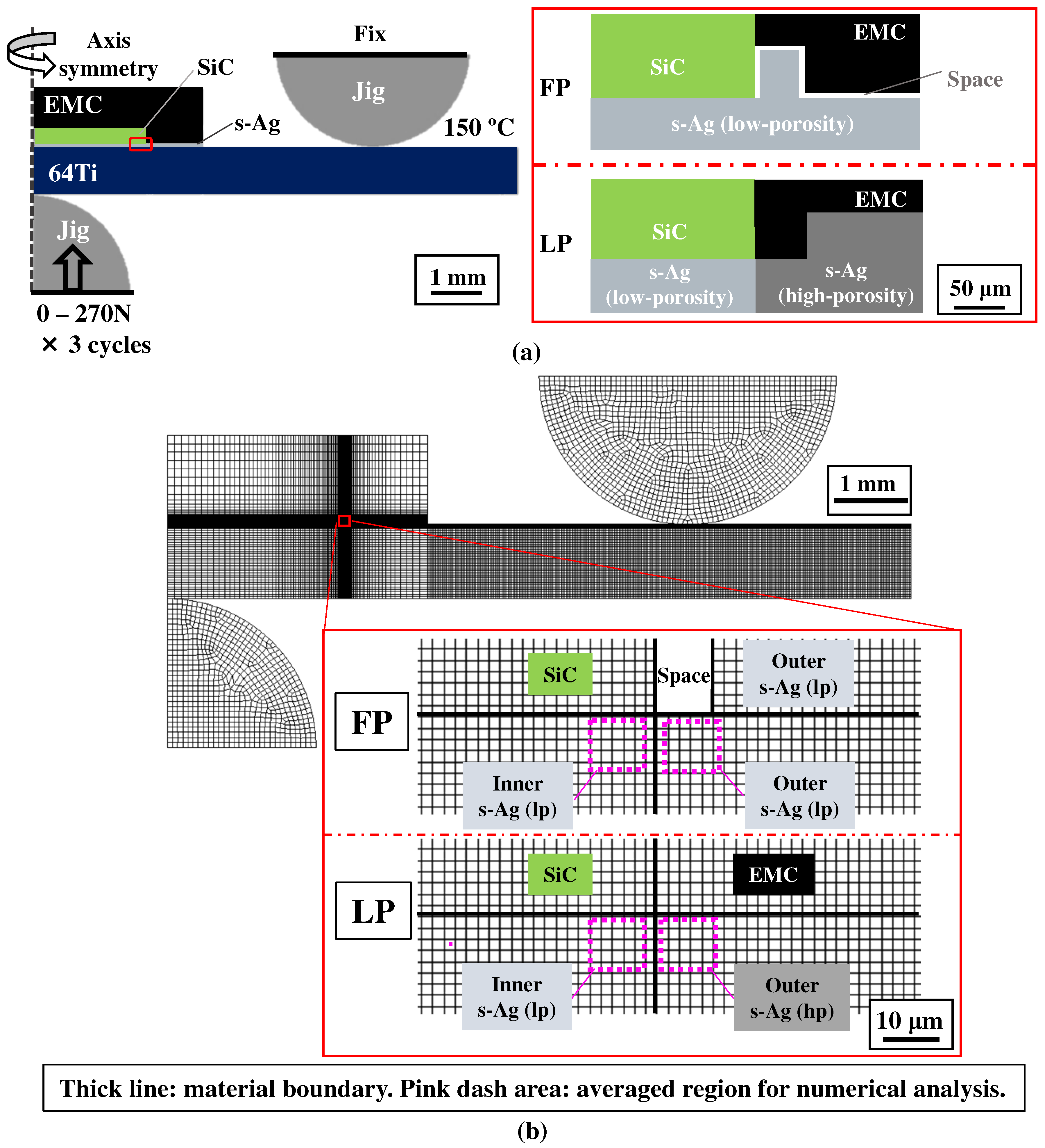

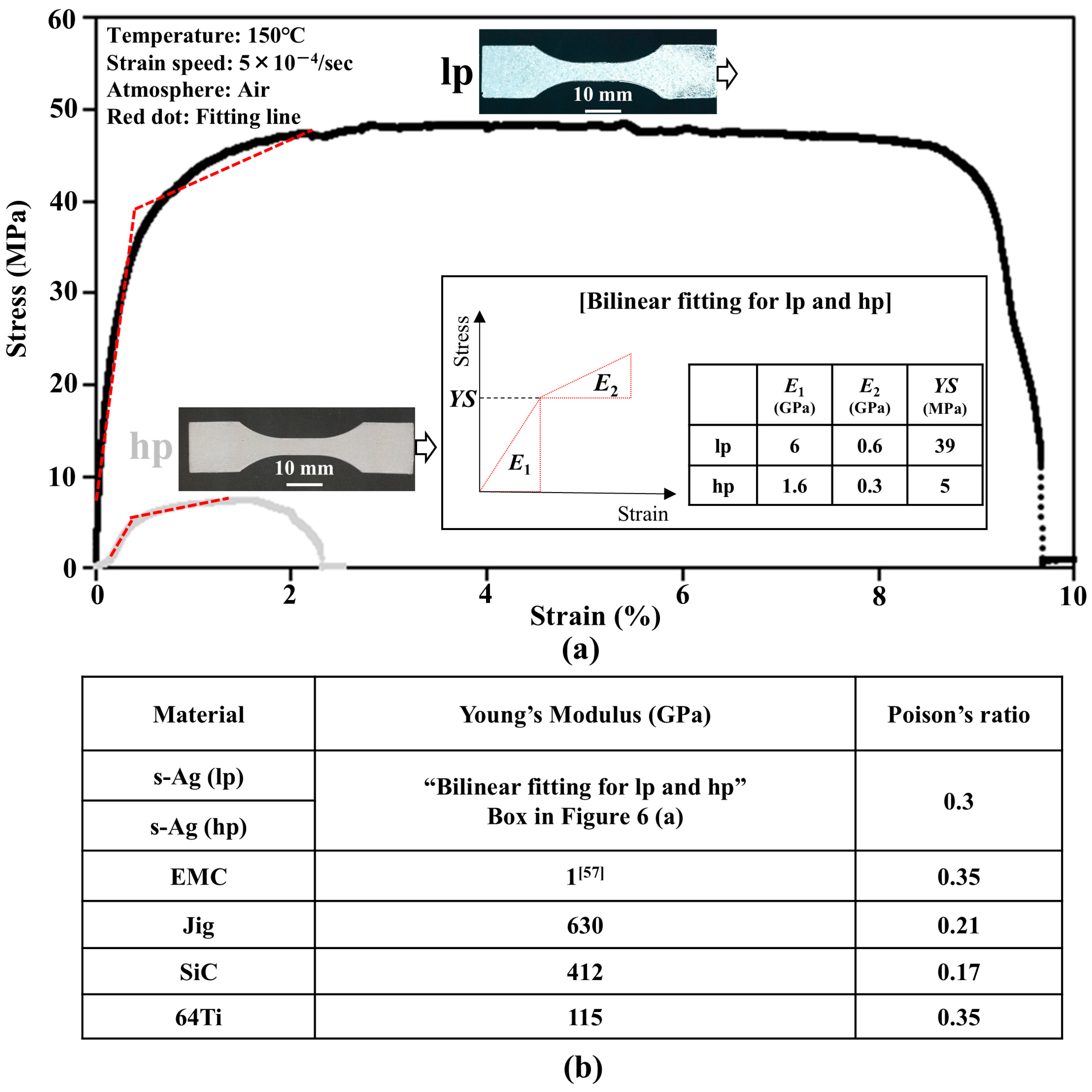

2. Materials and Methods

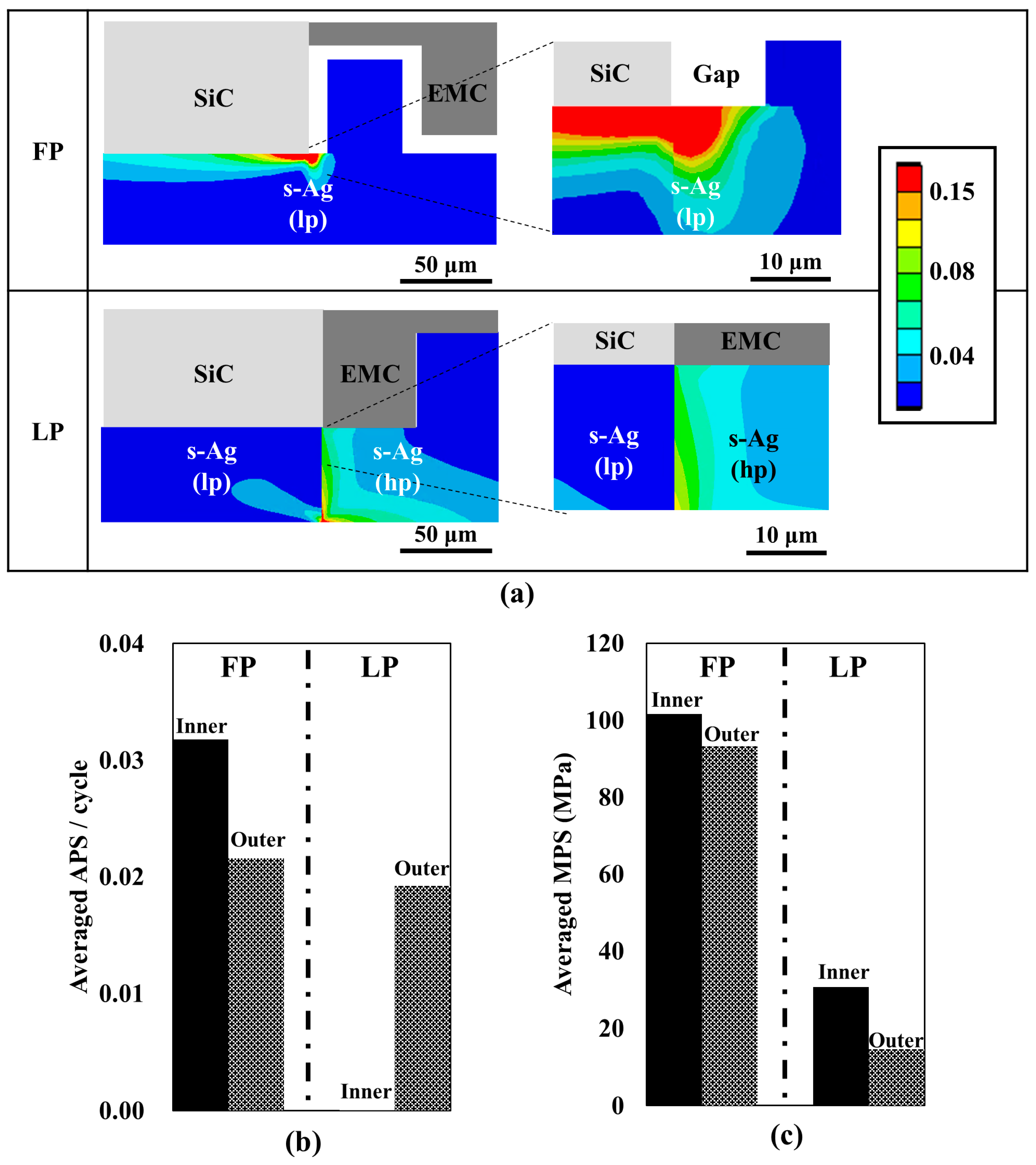

3. Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| CCM | Cohesive cracking mode |

| IDM | Interface delamination mode |

| s-Ag | Sintered silver |

| hp | High-porosity |

| lp | Low-porosity |

| FP | Full press |

| LP | Local press |

| DAAs | Die-attached assemblies |

| WBG | Wide band gap |

| SiC | Silicon carbide |

| NBT | Nine-point bending test |

| TST | Thermal shock test |

| APS | Accumulated plastic strain |

| PKG | Packaging |

| EMC | Epoxy molding compounds |

| CTE | Coefficients of thermal expansion |

| Rth | Thermal resistance of the PKG |

| rth | Rth increase ratio |

| SAT | Scanning acoustic tomography |

| 2D | Two dimensional |

| FEA | Finite element analysis |

| BSE | Backscattering elecron |

| SEM | Scanning electron microscopy |

| S–S | Stress–strain |

| YS | Yield stress |

| MPS | Maximum principal stress |

References

- Sprenger, M.; Forndran, F.; Ottinger, B.; Braum, T.; Franke, J. Reliability assesment and thermal characterization of automotive power module package based on novel thick copper-ceramic substrate and hard epoxy encapsulation. In Proceedings of the 12th International Conference on Integrated Power Electronics Systems (CIPS), Berlin, Germany, 15–17 March 2022. [Google Scholar]

- Emon, A.I.; Hassan, M.U.; Mirza, A.B.; Narayanasamy, B.; Luo, F. A Figure of Merit for SiC MOSFET Power Modules to Achieve High Power-Density Energy Conversion. IEEE Trans. Electron. Devices 2023, 70, 3718–3725. [Google Scholar] [CrossRef]

- Hudgins, J.L.; Simin, G.S.; Santi, E.; Khan, M.A. An assessment of wide bandgap semiconductors for power devices. IEEE Trans. Power Electron. 2003, 18, 907–914. [Google Scholar] [CrossRef]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors. IEEE Trans. Ind. Electron. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Peng, P.; Hu, A.; Gerlich, A.P.; Zou, G.; Liu, L.; Zhou, Y.N. Joining of Silver Nanomaterials at Low Temperatures: Processes, Properties, and Applications. ACS Appl. Mater. Interfaces 2015, 7, 12597–12618. [Google Scholar] [CrossRef] [PubMed]

- Siow, K.S. Are Sintered Silver Joints Ready for Use as Interconnect Material in Microelectronic Packaging? J. Electron. Mater. 2014, 43, 947–961. [Google Scholar] [CrossRef]

- Chen, C.-J.; Chen, C.-M.; Horng, R.-H.; Wuu, D.-S.; Hong, J.-S. Thermal Management and Interfacial Properties in High-Power GaN-Based Light-Emitting Diodes Employing Diamond-Added Sn-3 wt.%Ag-0.5 wt.%Cu Solder as a Die-Attach Material. J. Electron. Mater. 2010, 39, 2618–2626. [Google Scholar] [CrossRef]

- Youssef, T.; Rmili, W.; Woirgard, E.; Azzopardi, S.; Vivet, N.; Martineau, D.; Meuret, R.; Le Quilliec, G.; Richard, C. Power modules die attach: A comprehensive evolution of the nanosilver sintering physical properties versus its porosity. Microelectron. Reliab. 2015, 55, 1997–2002. [Google Scholar] [CrossRef]

- Ordonez-Miranda, J.; Hermens, M.; Nikitin, I.; Kouznetsova, V.G.; van der Sluis, O.; Ras, M.A.; Reparaz, J.S.; Wagner, M.R.; Sledzinska, M.; Gomis-Bresco, J.; et al. Measurement and modeling of the effective thermal conductivity of sintered silver pastes. Int. J. Therm. Sci. 2016, 108, 185–194. [Google Scholar] [CrossRef]

- Lv, W.; Liu, J.; Lei, X.; Zhu, F. Porosity Dependence of Thermal and Electrical Properties in Nano-Silver Paste. IEEE Trans. Electron. Devices 2023, 70, 702–707. [Google Scholar] [CrossRef]

- ECPE Guideline AQG 324: Qualification of Power Modules for Use in Power Electronics Converter Units in Motor Vehicles; ECPE European Center for Power Electronics e.V.: Nuremberg, Germany, 2019.

- Wilde, J.; Staiger, W.; Thoben, M.; Schuch, B.; Kilian, H. Integration of Liquid Cooling, Thermal and Thermomechanical Design for the Lifetime Prediction of Electrical Power Modules. In Proceedings of the International Congress and Exposition, Detroit, MI, USA, 23–26 February 1998. [Google Scholar]

- Wakamoto, K.; Otsuka, T.; Nakahara, K.; Namazu, T. Degradation Mechanism of Pressure-Assisted Sintered Silver by Thermal Shock Test. Energies 2021, 14, 5532. [Google Scholar] [CrossRef]

- Wakamoto, K.; Kumakiri, Y.; Otsuka, T.; Nakahara, K.; Namazu, T. Comparison of sintered silver die attach failure between thermal shock test and mechanical cycling test. Jpn. J. Appl. Phys. 2022, 61, SD1029. [Google Scholar] [CrossRef]

- Herboth, T.; Guenther, M.; Fix, A.; Wilde, J. Failure Mechanisms of Sintered Silver Interconnections for Power Electronic Applications. In Proceedings of the 63rd Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 28–31 May 2013. [Google Scholar]

- Henaff, F.L.; Azzopardi, S.; Woirgard, E.; Youssef, T.; Bontemps, S.; Joguet, J. Lifetime Evaluation of Nanoscale Silver Sintered Power Modules for Automotive Application Based on Experiments and Finite-Element Modeling. IEEE Trans. Device Mat. Rel. 2015, 15, 326–334. [Google Scholar] [CrossRef]

- Sugiura, K.; Iwashige, T.; Tsuruta, K.; Chen, C.; Nagao, S.; Funaki, T. Reliability Evaluation of SiC Power Module with Sintered Ag Die Attach and Stress-Relaxation Structure. IEEE Trans. Compon. Packag. Manuf. Technol. 2019, 9, 609–615. [Google Scholar] [CrossRef]

- Wakamoto, K.; Fuji, K.; Otsuka, T.; Nakahara, K.; Namazu, T. Nine Point Bending Test Technique for Understanding of Sintered Silver Die Bonding Failure Mechanism. Exp. Tech. 2024, 48, 399–408. [Google Scholar] [CrossRef]

- Zhang, Z.; Chen, C.; Suetake, A.; Hsieh, M.-C.; Suganuma, K. Reliability of Ag Sinter-Joining Die Attach Under Harsh Thermal Cycling and Power Cycling Tests. J. Electron. Mater. 2021, 50, 6597–6606. [Google Scholar] [CrossRef]

- Qin, F.; Hu, Y.; Dai, Y.; An, T.; Chen, P.; Gong, Y.; Yu, H. Crack Effect on the Equivalent Thermal Conductivity of Porously Sintered Silcer. J. Electron. Mater. 2020, 49, 5994–6008. [Google Scholar] [CrossRef]

- Gorecki, P.; Gorecki, K.; Kisiel, R.; Brzozowski, E.; Bar, J.; Guziewicz, M. Investigations of an Influence of the Assembling Method of the Die to the Case on Thermal Parameters of IGBTs. IEEE Trans. Compon. Packag. Manuf. Technol. 2021, 11, 1988–1996. [Google Scholar] [CrossRef]

- Dai, J.; Li, J.; Agyakwa, P.; Corfield, M.; Johnson, C.M. Comparative Thermal and Structural Characterization of Sintered Nano-Silver and High-Lead Solder Die Attachments During Power Cycling. IEEE Trans. Device Mater. Reliab. 2018, 18, 256–265. [Google Scholar] [CrossRef]

- Liu, S.; Vuorinen, V.; Liu, X.; Fredrikson, O.; Brand, S.; Tiwary, N. Fatigue Crack Networks in Die-Attach Layers of IGBT Modules Under a Power Cycling Test. IEEE Trans. Power Electron. 2024, 39, 16695–16707. [Google Scholar] [CrossRef]

- Huang, Y.; Luo, Y.; Xiao, F.; Liu, B. Failure Mechanism of Die-Attach Solder Joints in IGBT Modules Under Pulse High-Current Power Cycling. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 99–107. [Google Scholar] [CrossRef]

- Wunderle, B.; Becker, K.F.; Sinning, R.; Wittler, O.; Schacht, R.; Walter, H.; Schneider-Ramelow, M.; Halser, K.; Simper, N.; Michel, B.; et al. Thermo-mechanical reliability during technology development of power chip-on-board assemblies with encapsulation. Microsyst. Technol. 2009, 15, 1467–1478. [Google Scholar] [CrossRef]

- Heilmann, J.; Nikitin, I.; Zschenderlein, U.; May, D.; Pressel, K.; Wunderle, B. Reliability experiments of sintered silver based interconnections by accelerated isothermal bending tests. Microelectron. Reliab. 2017, 74, 136–146. [Google Scholar] [CrossRef]

- Forndran, F.; Heilmann, J.; Metzler, M.; Leicht, M.; Wunderle, B. Determination of Rate- and Temperature Dependent Inelastic Material Data for Sintered Silver Die Attach and Simulative Implementation. In Proceedings of the 23rd International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), St. Julian, Malta, 25–27 April 2022. [Google Scholar]

- Heilmann, J.; Wunderle, B.; Zschenderlein, U.; Wille, C.; Pressel, K. Physics of failure based lifetime modelling for sintered silver die attach in power electronics: Accelerated stress testing by isothermal bending and thermal shock in comparison. Microelectron. Reliab. 2023, 145, 114973. [Google Scholar] [CrossRef]

- Wakamoto, K.; Mochizuki, Y.; Otsuka, T.; Nakahara, K.; Namazu, T. Temperature Dependence on Tensile Mechanical Properties of Sintered Silver Film. Materials 2020, 13, 4061. [Google Scholar] [CrossRef] [PubMed]

- Wakamoto, K.; Yasugi, D.; Otsuka, T.; Nakahara, K.; Namazu, T. Fracture Mechanism of Sintered Silver Film Revealed by In Situ SEM Uniaxial Tensile Loading. IEEE Trans. Compon. Packag. Manuf. Technol. 2024, 14, 240–250. [Google Scholar] [CrossRef]

- Wakamoto, K.; Otsuka, T.; Nakahara, K.; Mugilgeethan, V.; Matsumoto, R.; Namazu, T. Degradation Mechanism of Silver Sintering Die Attach Based on Thermal and Mechanical Reliability Testing. IEEE Trans. Compon. Packag. Manuf. Technol. 2023, 13, 197–210. [Google Scholar] [CrossRef]

- Herboth, T.; Fruh, C.; Gunther, M.; Wilde, J. Assessment of Thermo-Mechanical Stresses in Low Temperature Joining Technology. In Proceedings of the 13th International Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EurosimE), Cascais, Portugal, 16–18 April 2012. [Google Scholar]

- Gadaud, P.; Caccuri, V.; Bertheau, D.; Carr, J.; Milhet, X. Ageing sintered silver: Relationship between tensile behavior, mechanical properties and the nanoporous structure evolution. Mater. Sci. Eng. A 2016, 669, 379–386. [Google Scholar] [CrossRef]

- Nikitin, I.; Pressel, K. Mechanical Properties of Porous Silver Materials Depending on Sintering Parameters, In Proceedings of the 20th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC), Greenwich, UK, 24–26 September 2014.

- Ng, W.C.W.; Seatman, K.; Kumagai, K.; Takamura, K.; Nishimura, T.; Letz, S.; Schletz, A. The correlation between sintered silver joint reliability and pressure assisted sintering parameters. In Proceeding of the 19th Electronics Packaging Technology Conference (EPTC), Shingapore, 6–9 December 2017. [Google Scholar]

- Zabihzadeh, S.; Van Petegem, S.; Holler, M.; Diaz, A.; Duarte, L.I.; Van Swygenhoven, H. Deformation behavior of nanoporous polycrystalline silver. Part I: Microstructure and mechanical properties. Acta Mater. 2017, 131, 467–474. [Google Scholar] [CrossRef]

- Fan, J.; Xu, D.; Zhang, H.; Qian, C.; Fan, X.; Zhang, G. Experimental Investigation on the Sintering Kinetics of Nanosilver Particles Used in High-Power Electronic Packaging. IEEE Trans. Compon. Packag. Manuf. Technol. 2020, 10, 1101–1109. [Google Scholar] [CrossRef]

- Xu, Y.; Qiu, X.; Li, W.; Wang, S.; Ma, N.; Ueshima, M.; Chen, C.; Suganuma, K. Development of high thermal conductivity of Ag/diamond composite sintering paste and its thermal shock reliability evaluation in SiC power modules. J. Mater. Res. Technol. 2023, 26, 1079–1093. [Google Scholar] [CrossRef]

- Zhang, H.; Nagao, S.; Suganuma, K. Addition of SiC Particles to Ag Die-Attach Paste to Improve High-Temperature Stability; Grain Growth Kinetics of Sintered Porous Ag. J. Electron. Mater. 2015, 44, 3896–3903. [Google Scholar] [CrossRef]

- Heuck, N.; Langer, A.; Stranz, A.; Palm, G.; Sittig, R.; Bakin, A.; Waag, A. Analysis and Modeling of Thermomechanically Improved Silver-Sintered Die-Attach Layers Modified by Additives. IEEE Trans. Compon. Packag. Manuf. Technol. 2011, 1, 1846–1855. [Google Scholar] [CrossRef]

- Wakamoto, K.; Kumakiri, Y.; Namazu, T. Mechanical property changes in sintered silver films by including copper oxide nanoparticles. Microelectron. Reliab. 2024, 153, 115322. [Google Scholar] [CrossRef]

- Lv, W.; Liu, J.; Mou, Y.; Ding, Y.; Chen, M.; Zhu, F. Fabrication and sintering behavior of nano Cu-Ag composite paste for high-power device. IEEE Trans. Electron. Devices 2023, 70, 3202–3207. [Google Scholar] [CrossRef]

- Rajaguru, P.; Lu, H.; Bailey, C. Sintered silver finite element modelling and reliability based design optimisation in power electronic module. Microelectron. Reliab. 2015, 55, 919–930. [Google Scholar] [CrossRef][Green Version]

- Forndran, F.; Heilmann, J.; Metzler, M.; Leicht, M.; Wunderle, B. A Parametric Simulative Study for Lifetime Prediction of Sintered Silver Die Attach Under Different Accelerated Testing Conditions. In Proceedings of the 22nd International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), St. Julian, Malta, 19–21 April 2021. [Google Scholar]

- Weidler, J.; Newman, R.; Zhai, C.J. Optimizing assembly factors to minimize interlayer die stress in a PBGA package. In proceeding of the 52nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 28–31 May 2002. [Google Scholar]

- Manikam, V.R.; Paing, S.; Ang, A. Effects of soft solder materials and die attach process parameters on large power semiconductor dies joint reliability. In Proceedings of the 15th Electronics Packaging Technology Conference (EPTC), Singapore, 11–13 December 2013. [Google Scholar]

- Schaal, M.; Klingler, M.; Metais, B.; Gruninger, R.; Hoffmann, S.; Wunderle, B. Reliability Assessment of Ag Sintered Joints Using a SiC Semiconductor and Determination of Failure Mechanism in the Field of Power Electronics. In Proceedings of the 21st International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Microelectronics and Microsystems (EuroSimE), Cracow, Poland, 5–8 July 2020. [Google Scholar]

- Zhao, Z.; Zou, G.; Zhang, H.; Ren, H.; Liu, L.; Zhou, Y.N. The mechanism of pore segregation in the sintered nano Ag for high temperature power electronics applications. Materaial Lett. 2018, 228, 168–171. [Google Scholar] [CrossRef]

- Zhang, B.; Zhang, S.; Lu, X.; Han, L.; Mei, Y.-H. Reliability Improvement of Low-Temperature Sintered Nano-Silver as Die Attachment by Porosity Optimization. IEEE Trans. Compon. Packag. Manuf. Technol. 2023, 13, 1209–1216. [Google Scholar] [CrossRef]

- Weerasing, H.C.; Sirimanne, P.M.; Simon, G.P.; Cheng, Y.-B. Cold isostatic pressing technique for producing highly efficient flexible dye-sensitised solar cells on plastic substrates. Prog. Photovolt Res. Appl. 2012, 20, 321–332. [Google Scholar] [CrossRef]

- Oh, C.; Nagao, S.; Suganuma, K. Silver stress migration bonding driven by themomechanical stress with various substrates. J. Mater. Sci. Mater. Electron. 2015, 26, 2525–2530. [Google Scholar] [CrossRef]

- Liu, Y.; Zhang, H.; Wang, L.; Fan, X.; Zhang, G. Effect of Sintering Pressure on the Porosity and the Shear Strength of the Pressure-Assisted Silver Sintering Bonding. IEEE Trans. Device Mater. Reliab. 2018, 18, 240–246. [Google Scholar] [CrossRef]

- Bajwa, A.A.; Zeiser, R.; Wilde, J. Process optimization and characterization of a noverl micro-scaled silver sintering paste as a die-attach material for high temperature high power semiconductor devices. In Proceedings of the 36th Electronic Components and Technology Conference (ISSE), Alba lulia, Romania, 8–12 May 2013. [Google Scholar]

- Wakamoto, K.; Mochizuki, Y.; Otsuka, T.; Nakahara, K.; Namazu, T. Tensile mechanical properties of sintered porous silver films and their dependence on porosity. Jpn. J. Appl. Phys. 2019, 58, SDDL08. [Google Scholar] [CrossRef]

- Wang, M.; Mei, Y.; Li, X.; Burgos, R.; Boroyevich, D.; Lu, G.-Q. How to determine surface roughness of copper substrate for robust pressureless sintered silver in air. Mater. Lett. 2018, 228, 327–330. [Google Scholar] [CrossRef]

- Chen, C.; Gao, Y.; Liu, Z.-Q.; Suginima, K. 3D pyramid-shape Ag plating assisted interface connection growth of sinter micron-sized Ag paste. Scr. Mater. 2020, 179, 36–39. [Google Scholar] [CrossRef]

- Ukita, M.; Wakamoto, K.; Nakahara, K. Increased high-temperature stifness of an epoxy-based molding compound through high-temperature storage. Microelectron. Reliab. 2025, 166, 115605. [Google Scholar] [CrossRef]

- Rakesh, P.; Pal, B. Finite element analysis of Ti6Al4V porous structure for low-stiff hip implant application. Int. J. Simul. Multidisci. Des. Optim. 2021, 12, 12. [Google Scholar] [CrossRef]

- Onaka, S.; Kato, M.; Soeta, S.; Mori, T. A New Approach for Diffusional Growth of Grain-Boundary Voids. Trans. Jpn. Inst. Met. 1988, 29, 284–291. [Google Scholar] [CrossRef][Green Version]

- Onaka, S.; Kato, M. Unified Analysis for Various Diffusion-controlled Deformation and Fracture Processes. ISIJ Int. 1991, 31, 331–341. [Google Scholar] [CrossRef][Green Version]

- Han, Y.C.; Kim, E.; Kim, W.; Im, H.-G.; Bae, B.-S.; Choi, K.C. A flexible moisture barrier comprised of a SiO2-embedded organic-inorganic hybrid nanocomposite and Al2O3 for thin-film encapsulation of OLEDs. Org. Electron. 2013, 14, 1435–1440. [Google Scholar] [CrossRef]

- Kwon, J.H.; Jeong, E.G.; Jeon, Y.; Kim, D.-G.; Lee, S.; Choi, K.C. Design of Highly Water Resistant, Impermeable, and Flexible Thin-Film Encapsulation Based on Inorganic/Organic Hybrid Layers. ACS Appl. Mater. Interfaces 2019, 11, 3251–3261. [Google Scholar] [CrossRef] [PubMed]

| Step | Tester or Material | Specification or condition |

|---|---|---|

| 1 | Nano silver paste (commercial product) | - 18 nm in diameter |

| 1 | Carbon sheet (TOYO TANSO, VVF30, Osaka, Japan) | - FP: 20 mm square, LP: 4.8 mm square, thickness: 1.6 mm |

| 1 | Uniaxial press machine (SHINTOKOGIO, Ltd., CYPM-200, Aichi, Japan) | - 60 MPa pressure for 10 min at 300 °C |

| 2 | EMC (commercial product) | - Silica filler 88 wt% (20 nm–40 μm in diameter) - Biphenyl type epoxy resin |

| 2 | Compression molding machine (TOWA, CPM-1080, Kyoto, Japan) | - 13.8 MPa pressure - Cure: 2 min at 165 °C |

| 2 | Thermal chamber (ESPEC, ST-120, Osaka, Japan) | - Air atmosphere - Post-mold cure: 5 h at 175 °C |

| 3 | Laser marker (KEYENCE, MD-U1000C, Osaka, Japan) | - Ultraviolet laser (λ = 355 nm) of Gaussian beam profile |

| 4 | Universal test system (Instron Japan, 68TM-5, Kanagawa, Japan) | - In air atmosphere at 150 °C - Force control (0 and 270 N under triangle waveform) - 500 cycles |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wakamoto, K.; Ukita, M.; Saito, A.; Nakahara, K. Suppression of Cohesive Cracking Mode Based on Anisotropic Porosity in Sintered Silver Die Attach Encapsulated by Epoxy Molding Compounds. Electronics 2025, 14, 3227. https://doi.org/10.3390/electronics14163227

Wakamoto K, Ukita M, Saito A, Nakahara K. Suppression of Cohesive Cracking Mode Based on Anisotropic Porosity in Sintered Silver Die Attach Encapsulated by Epoxy Molding Compounds. Electronics. 2025; 14(16):3227. https://doi.org/10.3390/electronics14163227

Chicago/Turabian StyleWakamoto, Keisuke, Masaya Ukita, Ayumi Saito, and Ken Nakahara. 2025. "Suppression of Cohesive Cracking Mode Based on Anisotropic Porosity in Sintered Silver Die Attach Encapsulated by Epoxy Molding Compounds" Electronics 14, no. 16: 3227. https://doi.org/10.3390/electronics14163227

APA StyleWakamoto, K., Ukita, M., Saito, A., & Nakahara, K. (2025). Suppression of Cohesive Cracking Mode Based on Anisotropic Porosity in Sintered Silver Die Attach Encapsulated by Epoxy Molding Compounds. Electronics, 14(16), 3227. https://doi.org/10.3390/electronics14163227