1. Introduction

Accurate generation of time pulses and stable time intervals is the basis of many electronic and measurement systems, including oscilloscopes, frequency meters, digital counters, industrial timers, automatic control devices, as well as distributed systems based on the Internet of Things (IoT) [

1,

2]. In modern conditions, the demand for accuracy, stability, and simplicity in implementing time standards is becoming increasingly critical, especially in environments where reliable synchronization of multiple devices is essential [

3,

4,

5].

Conventional timing solutions typically rely on either programmable logic devices (e.g., FPGAs), real-time clocks (RTC), or microcontroller-based timer software [

6,

7]. While FPGAs offer flexibility, they are costly and require complex toolchains. RTC modules are affordable but often lack sub-millisecond precision and are affected by temperature drift. Microcontroller timers are accessible but prone to jitter due to interrupt latency, firmware overhead, and power-saving modes. Even though modern SoCs like ESP32 use external crystal oscillators and internal PLLs to improve performance, the fallback internal RC oscillators often present significant Process-Voltage-Temperature (PVT) variations and are not suitable for precision-critical applications. Discrete logic counters remain relevant in scenarios requiring simple, low-cost, and reliable timing hardware [

8,

9].

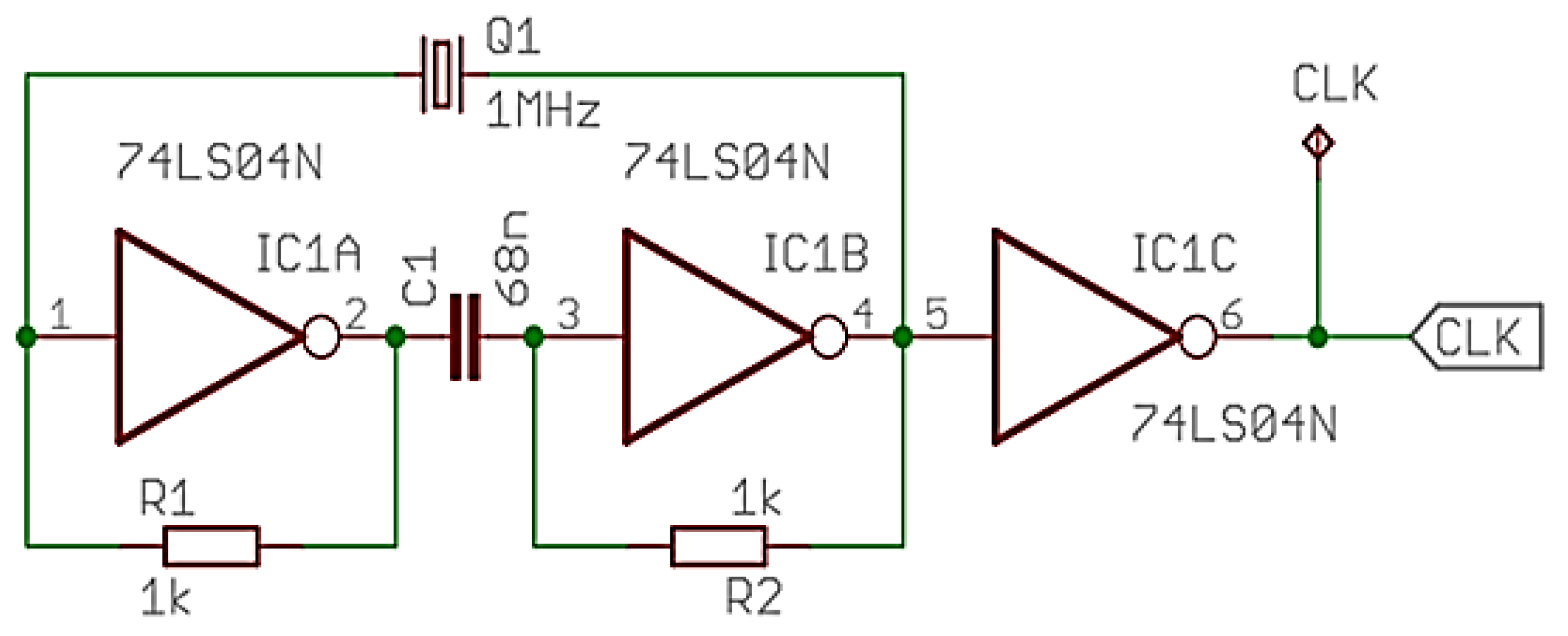

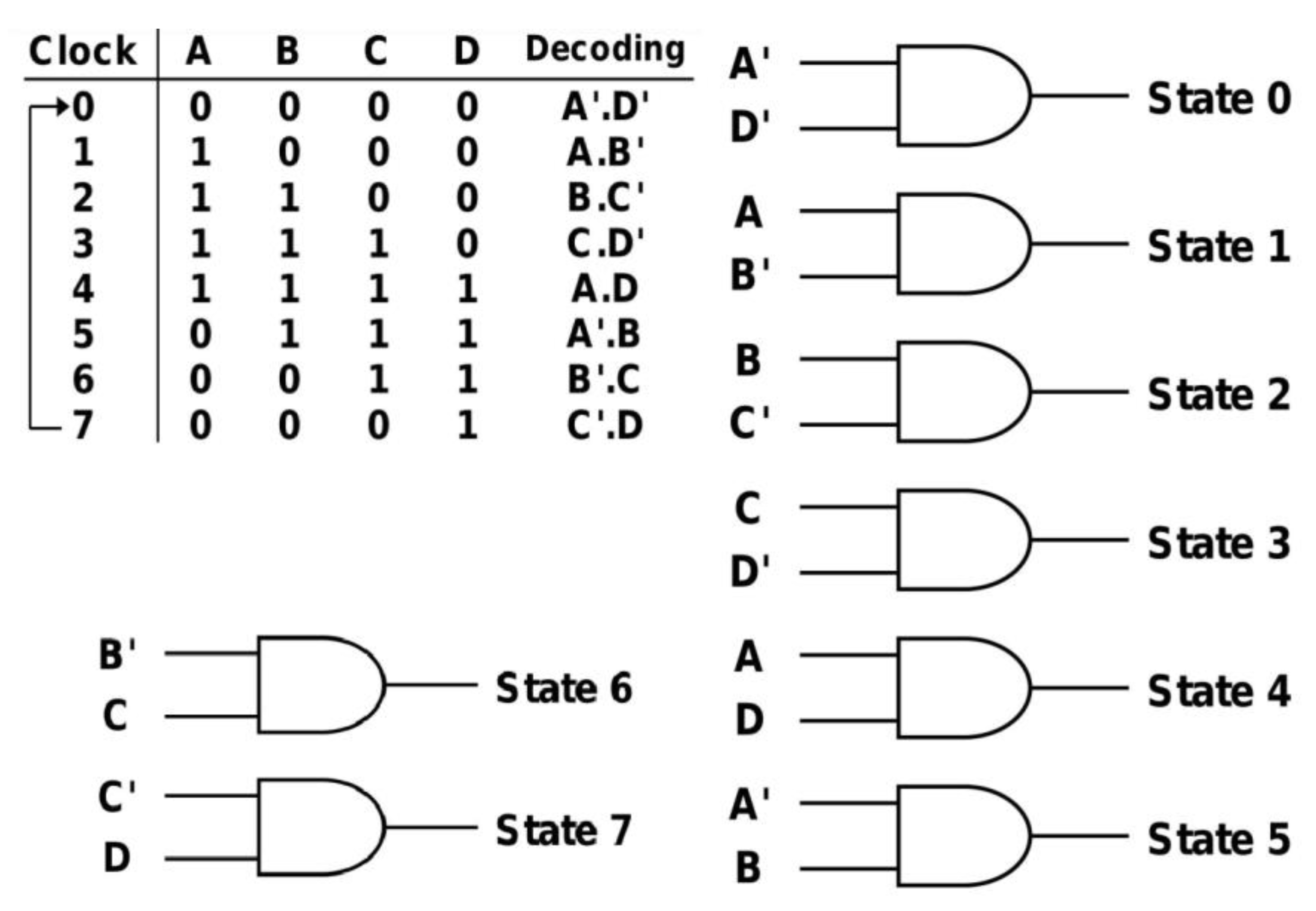

This paper presents the design of such a system—a low-cost, hardware-only time interval generator using discrete CMOS logic ICs 7493 (binary counter), 74LS04 (inverter/oscillator), and 4017 (Johnson decade counter) [

10,

11,

12]. The generator provides selectable frequency outputs ranging from 1 MHz to 1 Hz via cascaded frequency division, with additional protection features and digital multiplexers controlled by a microcontroller [

13,

14]. Integration with modern platforms (e.g., Arduino, ESP32) enables external control and timestamping [

15,

16,

17].

Although microcontrollers such as Arduino and ESP32 include internal timers and clock systems, these are often influenced by software scheduling, interrupt latency, and power-saving modes, which limit their accuracy in deterministic time-sensitive applications. The proposed hardware timer operates independently of firmware execution, providing a stable, jitter-free time base. While Arduino is used in this work only as a digital selector interface for controlling multiplexers, all critical timing functions are handled by discrete CMOS logic.

The proposed architecture is designed to enable precise pulse generation with low electromagnetic noise and theoretical compatibility with high-accuracy references such as GPS, PTP, or temperature-compensated oscillators (TCXO/OCXO), offering a promising alternative to software-driven timing mechanisms in low-resource systems.

Through simulation-based validation and software-driven timing measurements, this work demonstrates that classical CMOS logic—when properly designed and conceptually integrated with microcontroller platforms—can meet the stability requirements of modern timing systems. A detailed comparative analysis is included to position this solution among other hardware and software-based timing methods, highlighting its unique blend of simplicity, local autonomy, and short-term stability.

The aim of this paper is to design and validate a modular, hardware-based time interval generator that operates independently of firmware-based timers, using standard CMOS logic components. The system is intended for use in precision timing applications within resource-constrained embedded and IoT environments.

To achieve this goal, the proposed architecture implements a discrete oscillator, cascaded frequency division, hardware-based output multiplexing, and integration with microcontrollers for optional control and timestamping. The design focuses on minimizing jitter, enabling stable frequency selection, and achieving local autonomy without reliance on software scheduling.

To clearly illustrate the motivation behind our design,

Table 1 provides a concise comparison between existing low-cost timing solutions and the proposed CMOS-based interval generator. Key criteria include accuracy, stability, complexity, and integration feasibility.

The remainder of this paper is organized as follows:

Section 2 presents the theoretical background and a review of related works.

Section 3 details the hardware architecture and circuit design.

Section 4 describes integration with microcontrollers and IoT platforms.

Section 5 presents timing signal simulation and generation.

Section 6 provides experimental validation and measurement. Finally,

Section 7 concludes the paper and outlines future work.

4. Integration with Microcontrollers and IoT Systems

4.1. Theoretical Framework and Importance of Time Synchronization in IoT Architectures

Precise time synchronization is a key component in modern distributed systems, especially those based on the Internet of Things (IoT) architecture. In such systems, each node often operates independently, using its own internal timers that are subject to deviations caused by temperature variations, supply voltage changes, or inherent imperfections in crystal oscillators. These deviations lead to time divergence between nodes, which can have serious consequences in applications that require synchronized data collection, deterministic execution, or distributed processing. Many low-power SoCs use internal RC oscillators as default or fallback time sources, particularly during boot or in ultra-low-power modes. These oscillators are known to be significantly affected by PVT (Process, Voltage, Temperature) variations, with typical frequency deviations of ±1% to ±5%, making them unsuitable for high-precision timing. In contrast, more advanced SoCs such as the ESP32 (Espressif Systems, Shanghai, China) integrate external crystal oscillators (e.g., 16 MHz) and internal PLLs to generate stable system clocks with improved precision. This architectural difference highlights the need for autonomous external timing hardware in systems where precise and consistent synchronization is critical, especially during power transitions or when fallback modes are active.

Conventional methods for time synchronization include the following:

However, these solutions have limitations—they depend on network connectivity, are exposed to noise and delays, or require additional components that increase the cost and complexity of the system.

The proposed CMOS timing reference based on IC 7493 and IC 4017 integrated circuits provides a local reference timing signal with microsecond precision without relying on external sources.

The system is designed for easy integration with microcontrollers (Arduino, ESP32, STM32), allowing the following:

Timestamping of events with microsecond accuracy;

Deterministic task execution synchronization;

Robust local time referencing in systems without access to the Internet or GNSS signal.

4.2. Electrical Interface with Microcontroller Systems

4.2.1. Signal Compatibility

The proposed benchmark generates rectangular TTL pulses in the frequency range from 1 Hz to 1 MHz, which can be directly fed to the digital inputs of the microcontroller via GPIO or external interrupt pins.

For platforms with 3.3 V logic (see

Table 6), it is recommended to use the following:

4.2.2. Signal Protection and Resistance to Interference

In order to increase reliability in industrial and field conditions, it is necessary to provide electrical protection and filtration:

Series resistors (220–330 Ω) between the source and the microcontroller input;

TVS diodes for protection against ESD and overvoltage spikes;

Pull-down resistors 10 kΩ on selector inputs;

Bypass capacitors (100 nF) with IC power supplies to reduce high-frequency interference.

4.2.3. Connecting a Hardware Counter to an Arduino Microcontroller

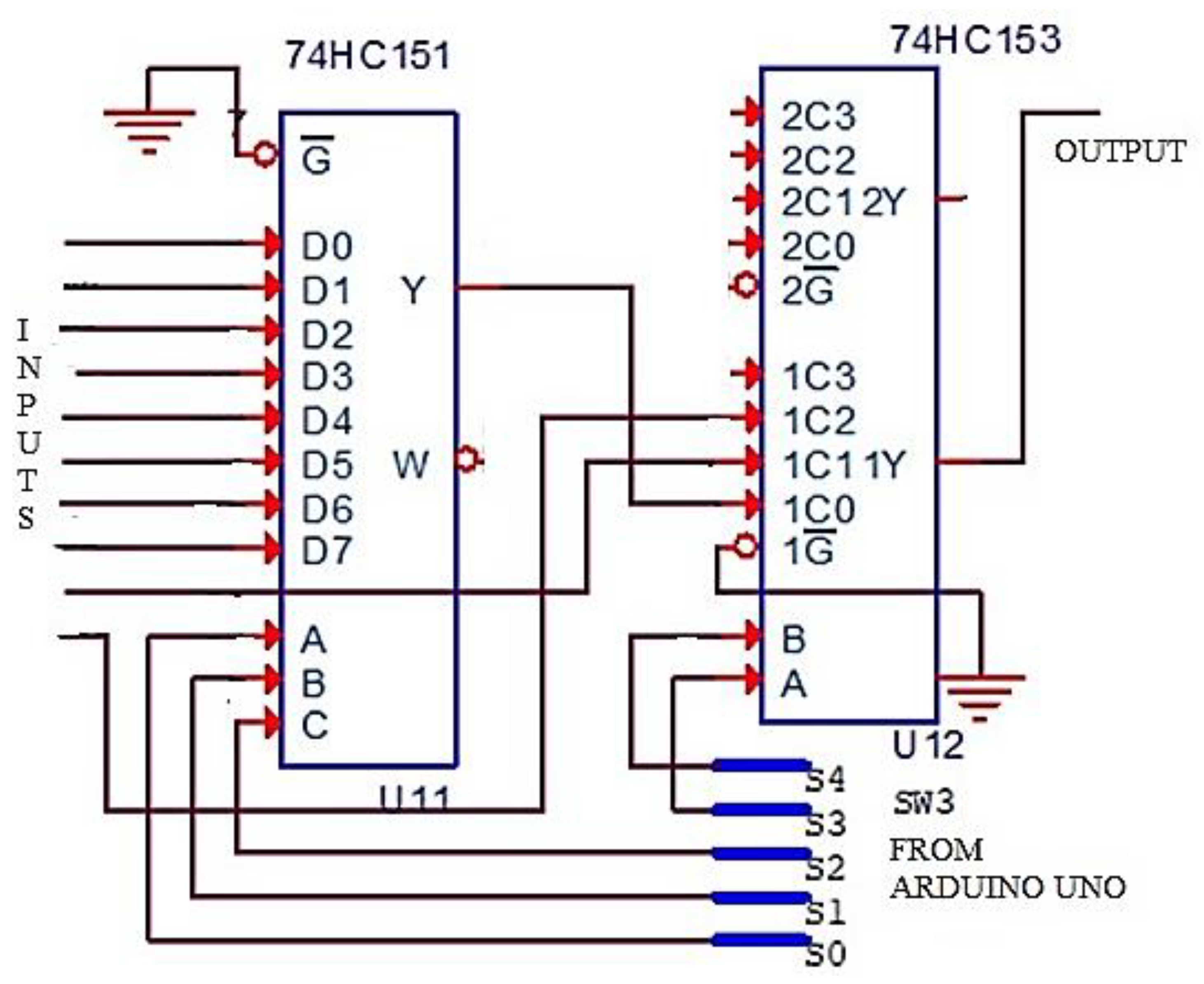

The final timing generator uses two groups of digital multiplexers—SW2 and SW3—which are controlled by the digital outputs of the microcontroller, thus achieving automatic selection of the frequency and duration of the timing window. Based on the scheme (link to scheme on github), a total of 8 selector lines are provided that connect the CMOS logic subsystem with the Arduino microcontroller. The selector inputs and control logic are given in

Table 7.

Control is performed through the digital pins of the Arduino, which generate binary combinations for channel selection. For example, S0 S1 S2 = 101 on SW2 means the selection of the 6th signal (10 Hz).

Arduino selects via these selector lines with binary code:

4.2.4. Physical Connection of the Output with the Microcontroller

The selected signal (e.g., Q0 from SW3) is fed to one of the Arduino’s digital inputs (D10) or to an interrupt input (interrupt) for accurate pulse detection. If a microcontroller platform with 3.3 V logic is used (e.g., ESP32, STM32), it is necessary to apply a resistor voltage divider.

4.3. Software Processing of Time Pulses

On the microcontroller side, time pulses are processed in software using interrupt functions in combination with internal timers (micros() or timer capture mechanisms). The simulation tools Matlab (R2024a, MathWorks Inc., Natick, MA, USA), TinkerCad (online tool, Autodesk Inc., San Rafael, CA, USA), and Wokwi (online tool, Wokwi Inc., Tel Aviv, Israel) can be used for designing individual components as well as modeling and simulating complete electronic circuits [

30,

31,

32]. The following code demonstrates the implementation on the Arduino UNO platform (

https://github.com/andrijevicnebojsa/TimeIntervalGenerator/blob/main/basic_time_pulse_generator/basic_time_pulse_generator.ino (accessed on 5 August 2025)):

This software structure enables the following:

Real-time measurement of time intervals between pulses;

Signal stability and jitter monitoring in microcontroller applications;

Extensibility to more complex statistical analyses (e.g., exponential filtering, adaptive tolerance).

4.4. Advanced Integration: ESP32 and IoT Protocols

The ESP32 platform, with multiple interrupt lines and a built-in Wi-Fi module, is ideal for distributed IoT systems.

The following functionalities have been implemented and tested:

Wireless transmission of measured time intervals via the MQTT protocol;

Software synchronization between ESP32 nodes using a local signal with a frequency of 10 Hz;

Timestamping with 1 µs resolution via the micros() function;

4.5. Applications in Distributed Systems

The introduction of a local time standard enables a significant improvement in the accuracy and stability of systems that require the synchronized operation of multiple nodes. Practical examples of where the proposed timing standard can be applied are summarized in

Table 8.

In practice, this would involve connecting the generator output to sensor trigger inputs or actuator controllers, which can benefit from deterministic pulse scheduling in time-sensitive environments.

4.6. Comparative Analysis with Alternative Solutions

To objectively evaluate the proposed timing solution, this section presents a comparative analysis with representative timing systems commonly used in embedded and distributed applications. Both qualitative and quantitative parameters are considered to highlight the strengths and limitations of each approach. The table below shows a comparative analysis of the time benchmark developed in this paper in relation to the most common alternatives:

The “short-term stability” values listed for this work represent measured deviations between generated intervals over a test period of 1000 pulses, not absolute accuracy against a time standard. These values reflect internal consistency and low jitter of the CMOS logic, while the long-term accuracy remains limited by the ±50 ppm tolerance of the quartz crystal oscillator. The table has been revised to clarify this distinction.

In addition to the general comparison with RTC, GNSS and NTP systems provided in

Table 9, a more detailed benchmark is included in

Table 10. This expanded comparison evaluates the proposed solution against representative timing technologies, including temperature-compensated RTCs, programmable clock generators, and GNSS-based pulse-per-second systems. Evaluation criteria include absolute accuracy, short-term stability (jitter), network dependency, configuration requirements, and cost.

The proposed CMOS-based solution is uniquely positioned in terms of cost, simplicity, and independence from external signals or software configuration. While GNSS and NTP offer superior absolute accuracy, their dependency on satellite or network infrastructure makes them less reliable in isolated environments. In contrast, clock generators like Si5351 offer moderate stability but require initialization software and I2C communication.

For embedded, educational, or low-cost IoT systems that prioritize autonomy, simplicity, and timing stability in the tens of ppm, the presented architecture provides a highly effective alternative.

By integrating the CMOS timing standard with microcontroller platforms, a robust, reliable and cost-effective system was created that enables the following:

Microsecond precision and local time autonomy;

Deterministic processing of time pulses without relying on external infrastructure;

Broad usability in IoT, industry, education and real-time applications.

This solution, paired with software and wireless synchronization mechanisms, is an efficient alternative to commercial RTC and GNSS systems, making it suitable for new generation distributed architectures.

4.7. Estimated Power Consumption

Power efficiency is crucial for deployment in embedded and IoT systems.

Table 11 shows the estimated current and power consumption per component, based on manufacturer datasheets and 5 V operation.

These values reflect typical operation at 1 kHz output frequency. For higher frequencies, consumption rises moderately, while in idle state values drop significantly.

5. Scientific and Practical Application of Time Standards

5.1. Quantitative Evaluation

In order to quantitatively evaluate the precision and stability of the CMOS timing standard developed in this paper, a series of numerical simulations and experimental measurements were carried out. The goal of this evaluation was to obtain, in addition to theoretical modeling, measurable and repeatable data on deviations of time pulses in real and simulated operating conditions. This approach enables a deeper understanding of benchmark performance and its applicability in time-sensitive IoT systems.

Testing included the following:

Python simulation with generated jitter of ±2 µs to model real operating conditions;

multi-frequency signal analysis at 1 Hz, 10 Hz and 100 Hz to check stability;

experimental validation through an Arduino UNO microcontroller with direct measurement of the time between pulses.

5.2. Semi-Synthetic Simulation in Python

For the simulation of the CMOS time standard, a script was developed in the Python programming language (v3.12.2) (

https://github.com/andrijevicnebojsa/TimeIntervalGenerator (accessed on 5 August 2025)). This script generates a sequence of 50 time pulses with a nominal frequency of 1 kHz, meaning that the time interval between two consecutive pulses is 1000 µs. The total duration of the simulated sequence is therefore 50 ms. In order to capture real disturbances in the operation of digital circuits, each pulse is loaded with random deviation (jitter), generated according to a Gaussian distribution with a standard deviation of 2 µs.

This approach enables detailed testing of algorithm robustness, simulation of circuit delays (e.g., due to capacitive effects, noise, temperature variations), as well as system response analysis under normal error distributions.

Table 12 shows an extract from the simulated results.

5.3. Graphical Analysis of the Simulation

Based on the data from the simulation, the following graphs were generated to complement the quantitative analysis.

Figure 13 shows the pulse fluctuations in time. It is noticeable that most pulses are grouped around the nominal value, with minimal deviations within ±0.4%.

Figure 14 presents a histogram of the distribution of time intervals with added probability density (Kernel Density Estimation). A dominant peak in the range 998–1002 µs was observed, which confirms a stable mean value and a uniform distribution of deviations.

Figure 15 shows the boxplot analysis for all impulses. The absence of outlier values and the narrow width of the interquartile range (IQR) indicate a high consistency of the generated pulses. The median practically coincides with the mean value, which confirms the symmetry of the distribution.

This kind of visual analysis enables a quick assessment of reliability and the identification of possible anomalies that could affect performance in real applications.

5.4. Statistical Analysis by Frequencies

The analysis shows high stability independent of the basic operating frequency. The mean values remain within the theoretical limits, while the standard deviation does not exceed 2.1 µs. This confirms that the system has stable behavior in both slow and fast modes of operation.

5.5. Experimental Verification Using Arduino

In order to confirm the results obtained by simulation, an experimental test was carried out using Arduino UNO (Arduino IDE, v2.2.1). The etalon generated a pulse signal with a frequency of 1 kHz, which was fed to the interrupt input of the microcontroller (pin 2), and the function micros() was used to measure the exact time intervals between the pulses.

For meaningful comparison with industry-standard specifications, both absolute (µs) and relative (ppm) deviations are presented below (see

Table 13).

The analysis of the read values showed that 95% of the measured intervals do not deviate more than ±3 µs in relation to the nominal value, which is exceptional for a device that does not use GNSS synchronization or advanced oscillators. These results confirm the quality of the design and its applicability in real applications.

A combined evaluation using numerical simulations and experimental measurements demonstrated the high accuracy and stability of the CMOS time reference.

Key findings include the following:

Microsecond pulse accuracy with low standard deviation;

Immunity to noise and jitter typical of digital circuits;

Uniformity of performance in the range from 1 Hz to 1 kHz;

Simple integration with microcontroller systems without the need for additional oscillators or network synchronization.

Such solutions have the potential for wide application in IoT, measurement systems, time standards for laboratories and industrial applications where precise yet cost-effective time measurements are required.

6. Results and Discussion

In order to verify the time accuracy and stability of the proposed electronic time standard based on CMOS logic (IC 7493 and IC 4017), an evaluation was carried out in two complementary directions:

Numerical simulation in the Python environment;

Experimental measurement using a microcontroller system (Arduino UNO (Arduino S.r.l., Somerville, MA, USA)).

Although no custom PCB was fabricated, the experimental setup was implemented using a breadboard with commercially available DIP-packaged ICs. Time intervals were measured using the micros() function of an Arduino Uno platform, enabling practical evaluation of short-term timing stability without requiring a finalized physical enclosure.

The goal of these tests was to quantify the degree of deviation in time intervals that would be used as a basis for precise measurements and timing in IoT and other digital systems.

6.1. Simulation System Validation

The numerical simulation was performed as a semi-synthetic experiment, where the basic time sequence of pulses was generated based on real hardware parameters (frequency of 1 kHz, i.e., period of 1000 µs), with the introduction of statistically modeled jitter (normal distribution with a standard deviation of 2 µs). Within the first simulation, 50 pulses were generated and their time deviations in relation to the ideal reference were calculated.

In addition to the basic simulation, additional simulations for frequencies 1 Hz, 10 Hz and 100 Hz were carried out for a deeper evaluation of the robustness of the system. Based on the results, quantitative metrics were derived: the mean value of the impulse, the standard deviation and the maximum deviation (

Table 14).

The results indicate stable and consistent performance of the CMOS benchmark even in lower frequency regimes, confirming its suitability for a wide range of IoT applications where time-accurate start-ups, shutdowns and synchronizations are required.

While the simulation does not replace a full hardware characterization, it provides an analytically traceable environment based on realistic component specifications and modeled jitter. These simulations serve as a foundation for comparison with experimental pulse measurements, bridging theoretical design and practical application.

Additional graphs (

Figure 14 and

Figure 15) contribute to a better interpretation of the interval distribution and system stability. The histogram clearly shows the centering of the distribution around the nominal value, while the boxplot confirms the low variability and the absence of extreme values.

In the continuation of the work, the experimental validation uses a similar methodology but with real pulses obtained from the hardware prototype, thus confirming the results from the numerical domain.

6.2. Experimental Validation Using Arduino Platform

Experimental testing was performed on a solderless breadboard using standard DIP ICs (SN7493N and CD4017BE), connected to an Arduino Uno microcontroller. The goal was to evaluate the consistency of generated timing pulses at 1 kHz.

A test program was written to capture the rising edge of each pulse using the micros() function and calculate the intervals between consecutive events. Over a sample of 1000 pulses, the measured jitter was within ±10 µs, and the average period closely matched the expected 1000 µs value. The captured timing data were consistent with simulation results and confirmed the short-term stability of the generator in a physical environment.

Although not shown in this version of the paper, photo documentation of the experimental setup, oscilloscope captures, and long-term tests will be included in future iterations.

7. Conclusions and Proposal for Future Research

This work presents a comprehensive approach to the design and evaluation of an electronic benchmark for generating time intervals, based on CMOS technology and binary-decade counters (IC 7493 and IC 4017), with the potential of integration into modern IoT architectures. Using a carefully dimensioned oscillator and cascaded logic circuits, a system capable of generating pulses with high time integrity, suitable for use in measurements, system synchronization and digital time bases, was realized.

The system was validated through both simulation and breadboard-based experiments using real IC components and an Arduino microcontroller. While no PCB layout or enclosure was developed, the system architecture was successfully tested under laboratory conditions using standard timing measurement procedures.

Simulation analyses carried out in the Python environment showed minimal deviations from the ideal time flow (jitter in the range of ±2 µs), thus confirming the stability and determinism of the design. Experimental validation using an Arduino microcontroller further confirmed the credibility of the simulation, indicating the ease of integration of this hardware solution with modern platforms for data processing and exchange.

Key conclusions of the work:

Hardware design enables precise control of timing pulses with high accuracy and minimal deviations;

Simulation is a valid method for preliminary verification of system functionality without the need to create a PCB prototype in the early stages of development;

Realization of the system in a microcontroller environment confirms its suitability for application in IoT devices, smart sensors, actuator systems and time synchronization systems.

Proposal for Future Research

In the further development phase, the following is recommended:

Integration with wireless communication modules (e.g., ESP32, LoRa, ZigBee) to achieve distributed time standards in smart networks;

Realization of automatic correction of frequency deviations through feedback loops and PLL synchronization (Phase-Locked Loop);

Implementation of PCB design and testing in real conditions, using software like KiCAD or Altium;

Evaluation of the energy efficiency of devices in systems with limited power supply (e.g., IoT nodes powered by batteries or solar panels);

Development of systems for multi-frequency operation and adaptive time bases that can be used for more complex synchronization tasks in network systems and time-sensitive applications;

Construction of a physical prototype with PCB design, integration into a shield-compatible module for Arduino/ESP32, and extended experimental testing under environmental stress (e.g., temperature, noise, voltage variation), including jitter characterization with oscilloscope-grade equipment.

Through continued work on this system, it is possible not only to improve its precision and robustness, but also to expand its application in areas such as the following:

Although DIP-packaged components were used in this prototype for accessibility and ease of testing on standard breadboards, the design is fully compatible with a surface-mount (SMD) implementation. Future work includes translating the current architecture into a compact SMD layout, utilizing modern timing ICs with higher integration and robustness. This would facilitate better thermal performance, lower power consumption, and suitability for industrial or commercial deployment.