1. Introduction

Electric vehicles are becoming more widely used due to their low emissions. Electric vehicle systems comprise an on-board charger that converts grid voltage into a voltage suitable for charging electric vehicle batteries [

1]. Presently, these on-board chargers are required to provide charging functionality and operate in the reverse operation mode. In the reverse operation mode, the battery can simultaneously release energy to AC loads or to the grid that supplies power to other electric vehicles. Electric vehicle batteries can function as distributed power sources to smoothen fluctuations in energy demand from the grid.

Figure 1 displays a schematic of a typical electric vehicle system comprising a filter cascaded with an AC-DC converter and a DC-DC converter. The AC-DC converter requires a high power factor and often uses power factor correction. The DC-DC converter provides the isolation required to ensure safety during vehicle charging. Among DC-DC converters, the CLLC converter is becoming increasingly popular because it can achieve maximum efficiency and soft switching across the full load range [

2].

CLLC converters can operate under soft switching conditions for primary switches and secondary rectifiers. In addition, the voltage stresses of the power switches are confined to the input and output voltage without any clamping circuits. The operation of CLLC converters differs between the forward and reverse power conversion modes because of the asymmetric turn ratios and the structure of resonant networks with the transformer. Several studies have explored the design and control of CLLC converters, especially focusing on bidirectional and resonant converters. For instance, recent research has highlighted advanced control methods to enhance the dynamic response and improve the converter’s performance under varying load conditions [

3]. However, limited studies have provided a comprehensive approach that ensures high efficiency during bidirectional operation while addressing practical challenges such as component size, thermal management, and complexity control. Some researchers have proposed adaptive control methods, such as model predictive control and artificial intelligence-based techniques, to optimize the response time of resonant converters under varying load and voltage conditions [

4]. These approaches focus on rapid settling times while maintaining efficiency and ensuring reliable operation across a wide range of operating scenarios. Bidirectional converters operate at a diverse range of voltages and relatively high efficiency. As their name suggests, they are capable of transferring power in both directions [

5]. Bidirectional converters have risen in prominence as a topic of research in power electronics because of their extensive range of applications, including wind farms, electric vehicles, aircraft, uninterruptible power supply, solar farms, X-ray, and military applications [

5]. Recent studies have also explored combining conventional control strategies, such as phase-shift modulation, with state-plane trajectory control to improve the dynamic response, particularly under transient conditions [

6]. These hybrid solutions offer a balance between simplicity and improved transient performance, providing a viable pathway for optimizing converters in modern applications.

Resonant converters operate on the principle of circuit resonance [

7]. Resonance occurs in a circuit when the inductive reactance is equal to the capacitive reactance. At resonance, both the inductor, which stores magnetic energy, and the capacitor, which stores electrical energy, charge and discharge energy continuously. Resonant converters contain resonant LC networks whose voltage and current waveforms vary sinusoidally during one or more subintervals of each switching period. Resonant converters induce soft switching with LC elements. Resonant converters can be classified into three types: series, parallel, and series–parallel hybrid [

8]. CLLC converters belong to the series–parallel hybrid type of resonant converters. Recent works have also explored novel resonant converter topologies to further optimize efficiency and voltage regulation [

9].

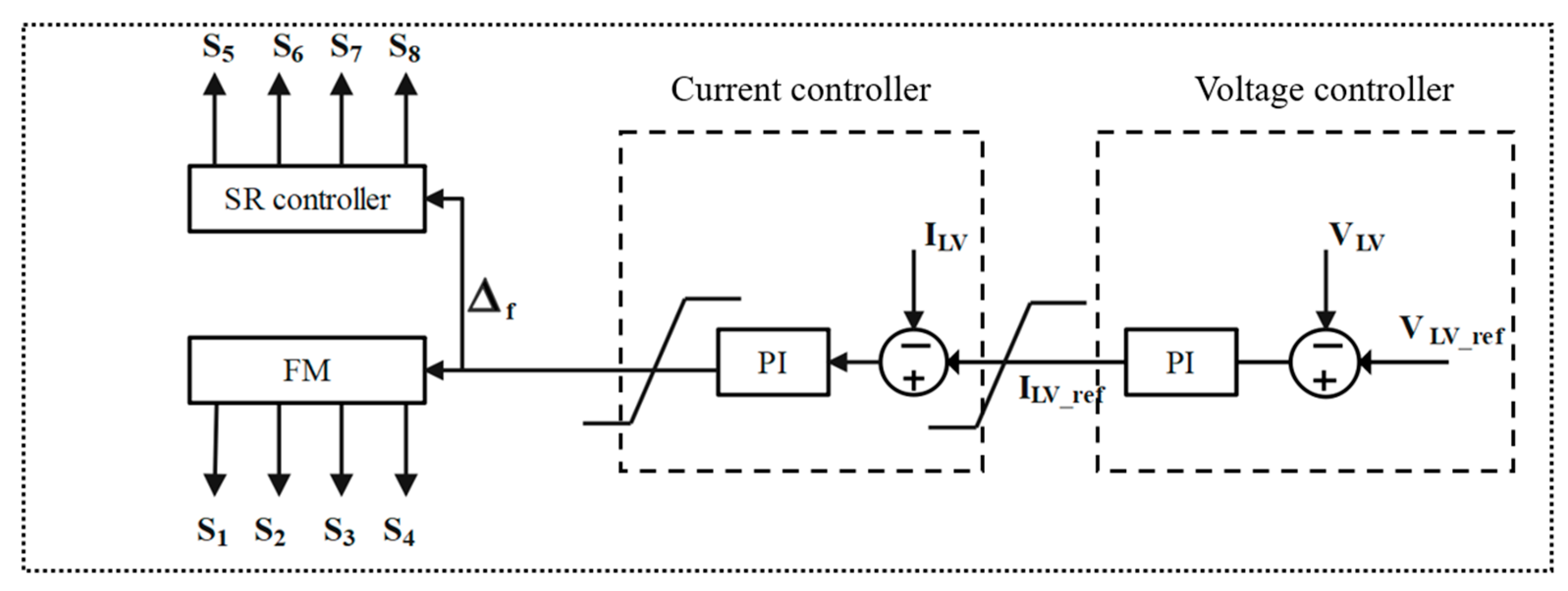

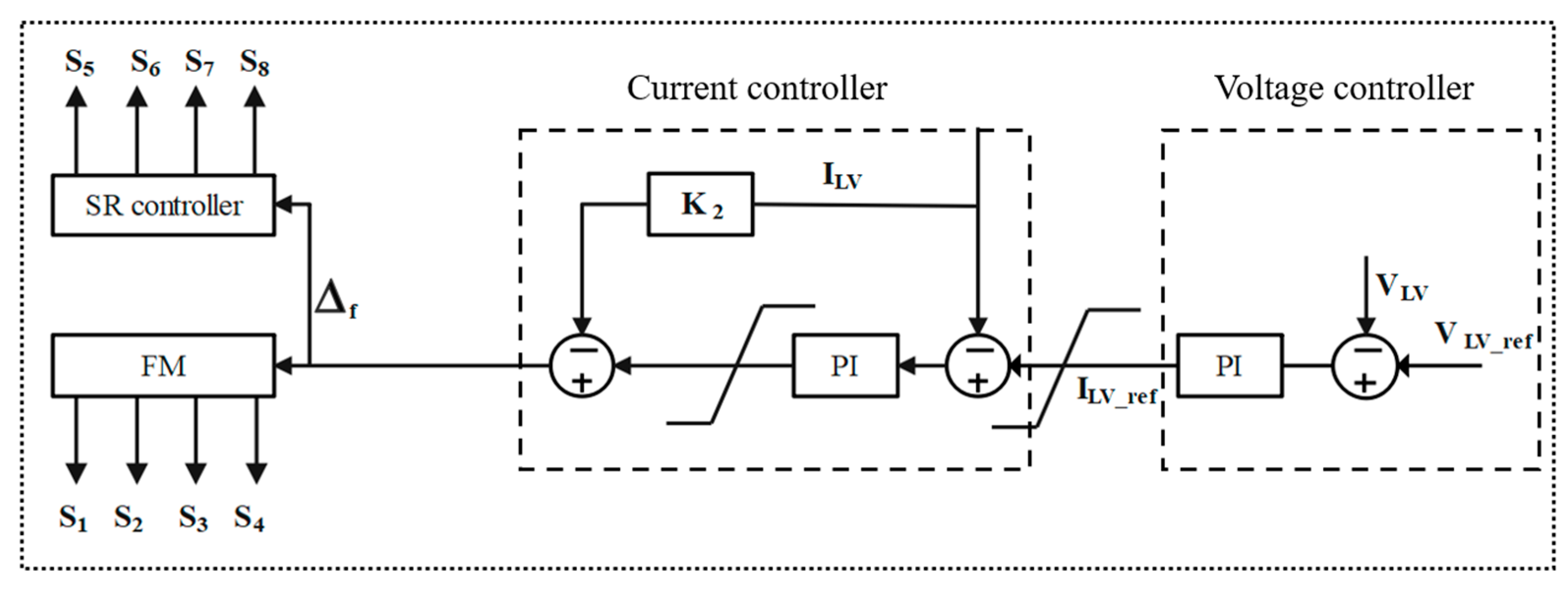

Five methods are commonly used for controlling CLLC converters: frequency modulation (FM) control, phase-shift modulation (PSM) control, self-sustained oscillation control, self-sustained PSM control, and optimum control [

10]. Each of these methods has some benefits and some drawbacks. FM control, which is often employed to preserve zero-voltage switching (ZVS), requires wide frequency variation [

11]. The converter is considerably derated because of the operating frequency, which is far more than the resonant frequency. Furthermore, tuning of the magnetic components and gate driver circuitry becomes challenging because of the notable frequency fluctuation. Overall, the huge size of power circuit components and reduced efficiency are the drawbacks of FM control in resonant converters. Conversely, PSM control enables fixed-frequency control methods, such as ZVS capability and the constant frequency functioning of the converter. However, under conditions of a light load and a broad input voltage range, all switches fail to maintain ZVS [

12]. A hybrid controller, often referred to as a mixed controller, was proposed to address the shortcomings of both the FM and PSM control methods [

5]. At low power levels, the hybrid controller locks the frequency at a maximum predetermined value and utilizes the PSM controller to prevent operations at frequencies well above the resonant frequency. At medium-to-high power levels, the hybrid controller leverages the traditional FM controller to operate within a limited range of fluctuating frequencies. However, the hybrid control method is complicated by the presence of two controllers. A previous study demonstrated the real-world applicability of this hybrid control strategy by adopting a fixed-frequency PSM method for CLLC converters [

10]. This method is preferred when the converter maintains a constant output voltage at a fixed switching frequency. Nevertheless, its major drawback is the inability to effectively control converters operating over a wide output voltage range. To address this limitation, the FM method operates in conjunction with the PSM method to regulate the output voltage under conditions of low output voltage and a light load [

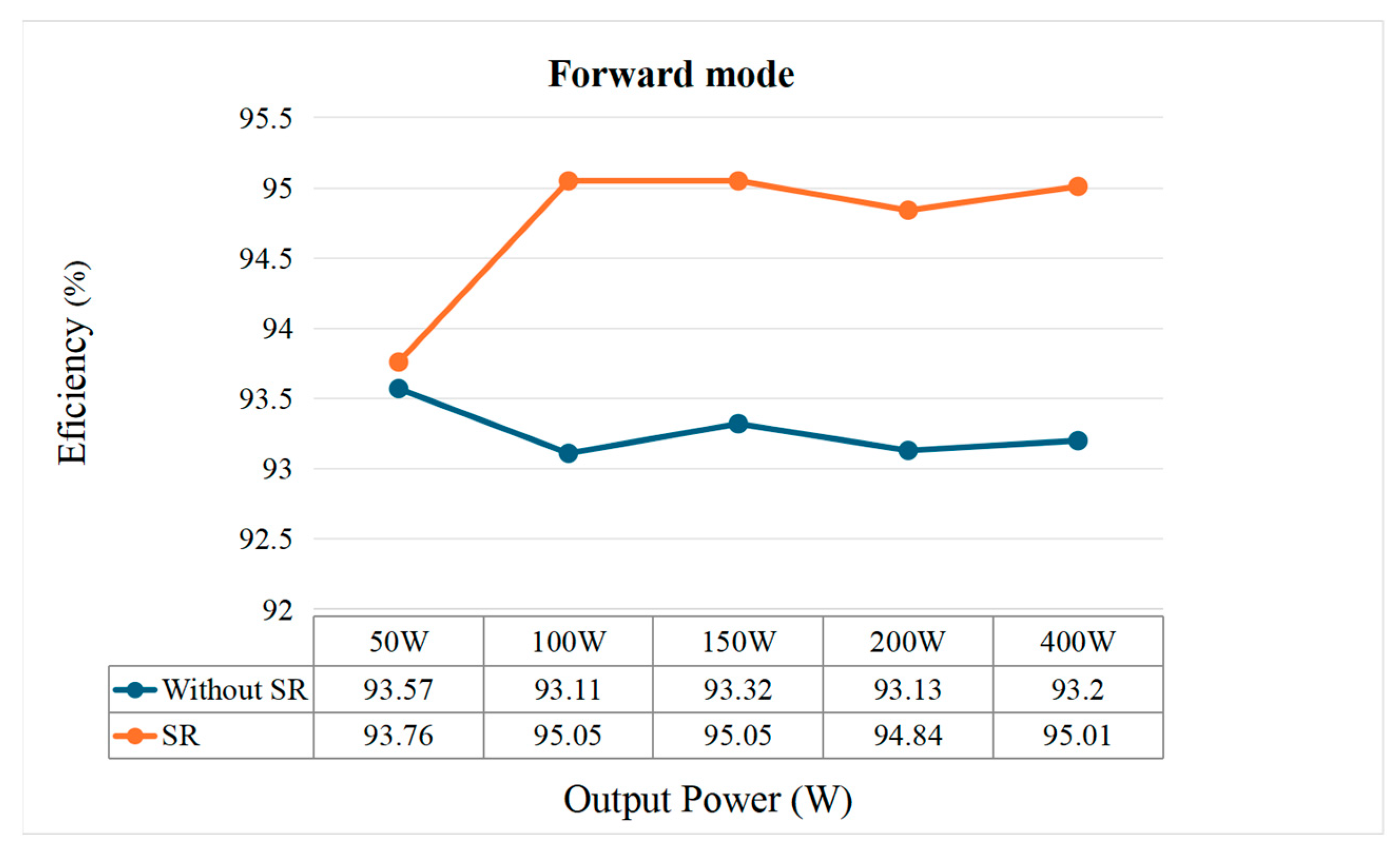

11]. In the present study, the proposed method associates the specific output voltage with the switching frequency, thereby improving control flexibility. Additionally, the FM method can be combined with a synchronous rectifier (SR) for a low-voltage energy storage system [

12]. The advantage of the proposed method is that it employs an SR for mitigating conduction losses in the switches and for increasing efficiency in the forward and reverse modes. Furthermore, state-plane trajectory control can be used as a variable frequency controller in resonant converters. It provides extremely rapid transient responses and inherent protection against the overcurrent. However, it resembles the all-state feedback control approach in that it requires the measurement of every converter state. Optimum control is regarded as a particular instance of state-plane trajectory control wherein the controller follows a certain path while maintaining the resonant tank energy within predetermined bounds [

13]. Load resonant converters are a type of variable frequency controller that perform better than FM controllers because they operate at a lower frequency. Recent investigations have also introduced machine learning algorithms to enhance real-time performance and adapt to varying load conditions, which represents another promising avenue of innovation [

14].

In response to the recent literature on adaptive and AI-based control strategies for bidirectional resonant converters [

3,

4,

6,

9,

11,

13,

14], the proposed gain-compensated PI loop has been comparatively analyzed in terms of speed, robustness, and implementation complexity.

Table 1 summarizes the comparison among various control techniques. While the proposed method may not achieve the ultra-fast response of AI or MPC-based techniques, it offers an optimal trade-off between control performance and system simplicity, making it particularly suitable for real-time embedded applications with constrained resources.

Recent developments in digital control for resonant converters, particularly in electric vehicle (EV) systems, have introduced machine learning techniques, model predictive control (MPC), and advanced nonlinear controllers to enhance system response, robustness, and adaptability [

3,

15,

16]. These approaches aim to address challenges in rapid load fluctuations, such as those experienced during regenerative braking or sudden acceleration in EVs. Compared to traditional CLLC converters, other resonant topologies such as LLC, LCC, and Dual-Active-Bridge (DAB) converters have also been explored for high-efficiency, high-power density applications [

15,

17]. While the CLLC provides inherent bidirectional capability and ZVS/ZCS operation, other topologies may offer improved control simplicity or integration with battery management systems (BMS). Modern EV architectures increasingly demand compatibility with vehicle-to-grid (V2G) interfaces, smart charging protocols, and CAN-based communication. Integrating resonant converters with such systems requires controllers to support fast communication, predictive adaptation, and fault-tolerant operation [

18]. Although PI controllers are widely used for their simplicity and implementation ease on microcontrollers, alternative strategies such as sliding mode control, deadbeat control, and adaptive feedback linearization are gaining attention due to their robustness against parameter variation and nonlinearity [

3,

19].

In particular, CLLC converters are increasingly employed in electric vehicle systems for high-efficiency power transfer. In such applications, the load variation in the CLLC converter occurs during braking or acceleration of the electric vehicle system. In fact, the CLLC converter must adapt and regulate the output voltage to a nearly stable value while the load varies. Most authors have used the first harmonic approximation (FHA) to analyze the characteristics of voltage gain and design of the control system, but the FHA cannot describe the dynamic response of the system [

13].

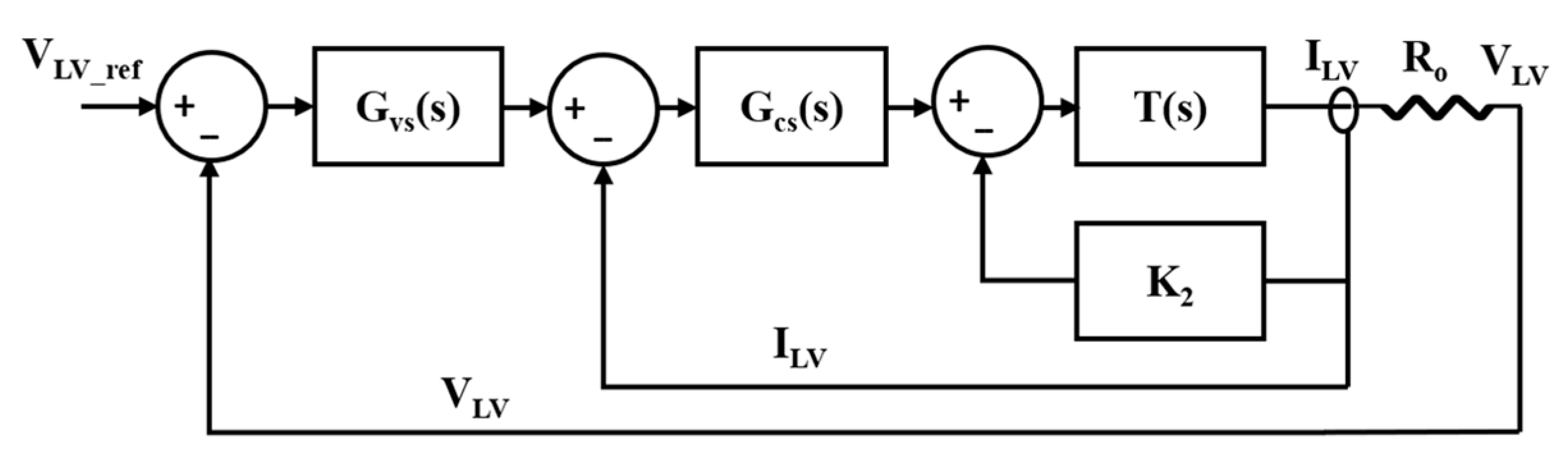

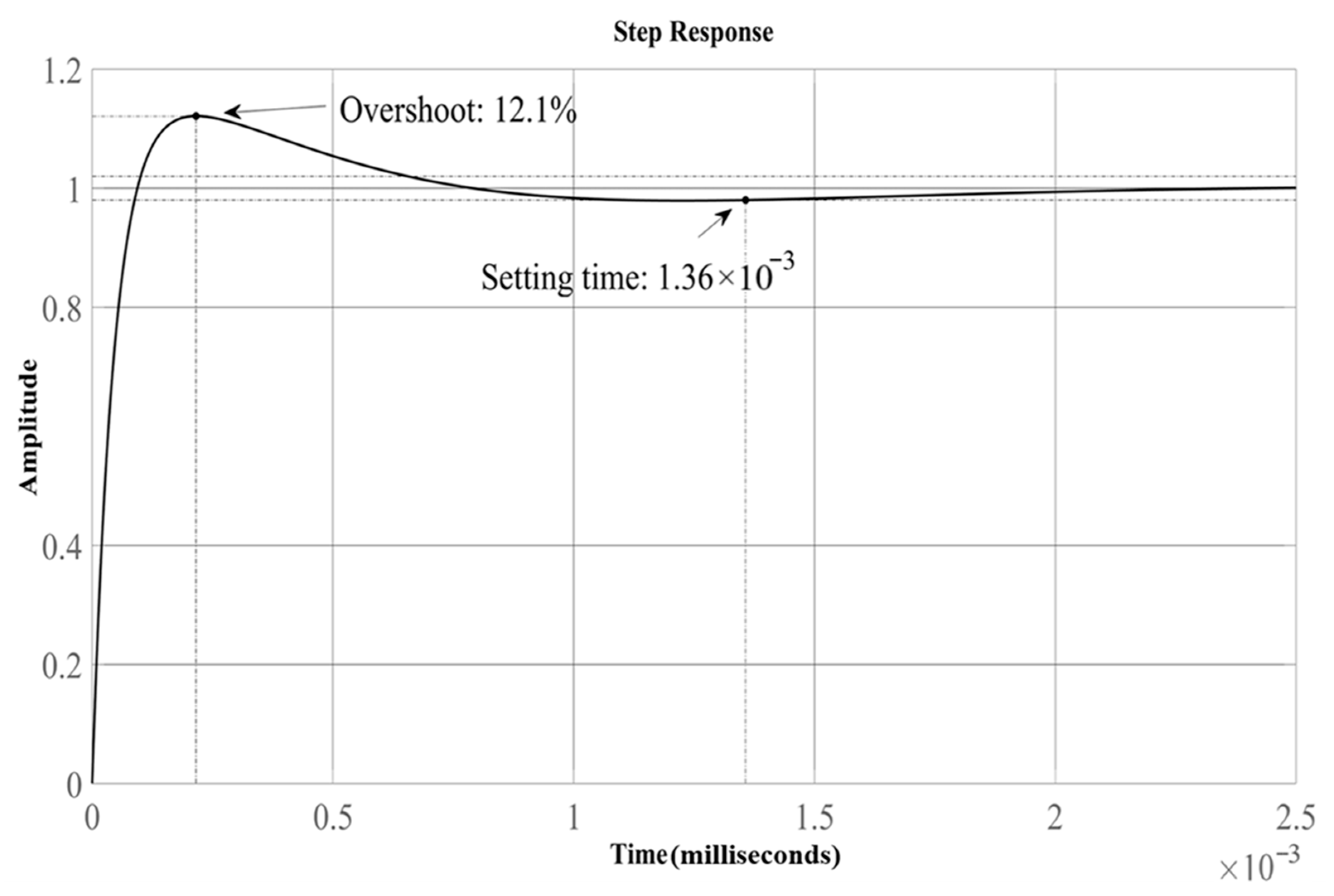

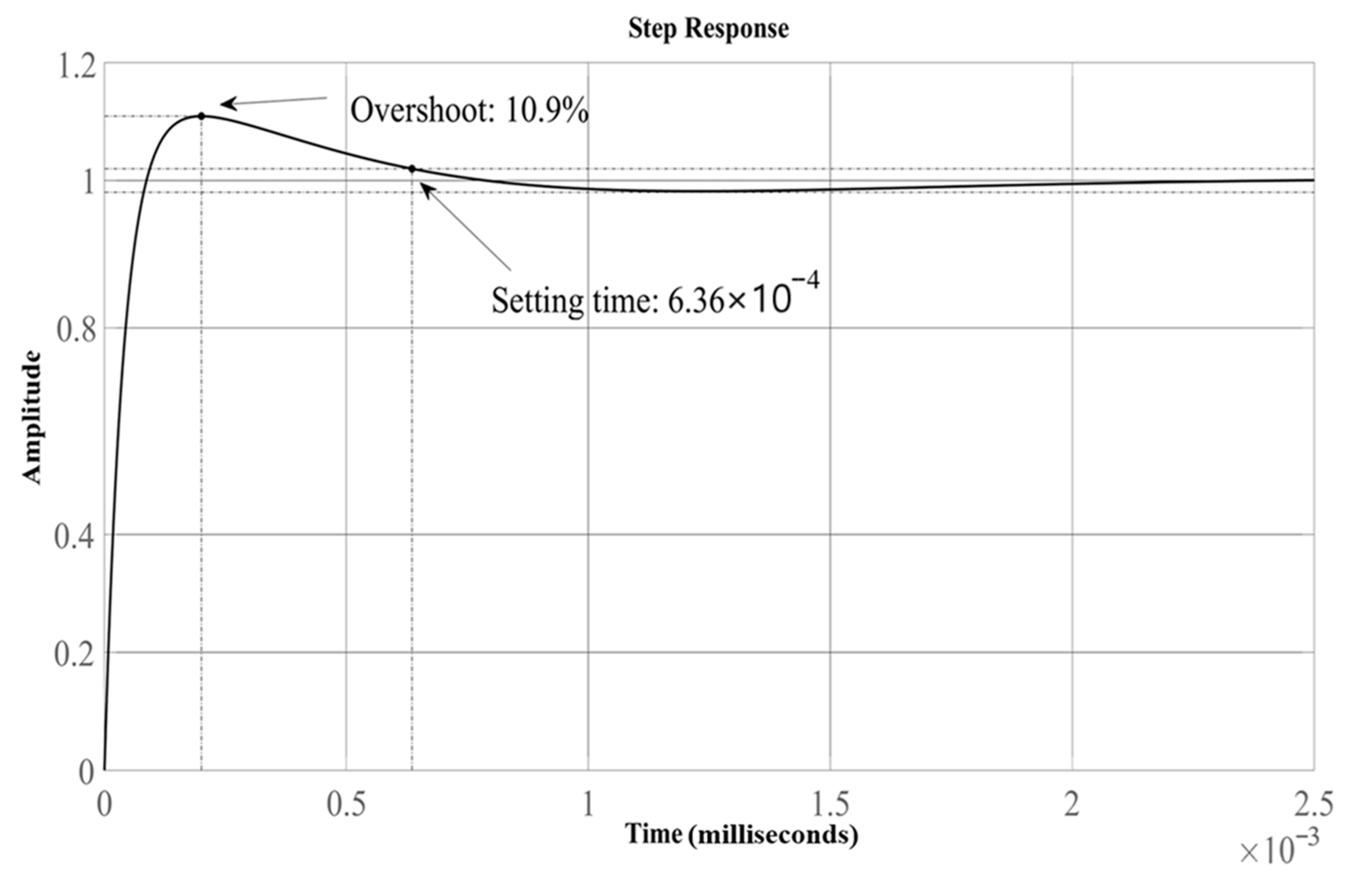

In modern electric vehicles, a fast dynamic response in power converters is crucial to ensure stable and reliable operation during events such as rapid acceleration, regenerative braking, and transitions between charging and discharging modes. A sluggish control response can result in voltage instability, increased stress on components, and inefficient energy transfer. While several studies have investigated bidirectional CLLC converters, many of them have not achieved the fast dynamic response required for electric vehicle (EV) applications under rapidly changing load conditions [

3,

5]. Moreover, existing digital control strategies are often constrained by implementation complexity or hardware limitations [

12]. To address these gaps, this study proposes a gain-compensated control algorithm designed to improve the settling time of the CLLC converter while maintaining practical simplicity for real-time implementation. The proposed gain-compensated control algorithm improves the converter’s transient response, allowing it to adapt more quickly to sudden load changes while maintaining a high efficiency. This makes the method particularly well-suited for on-board EV chargers and bidirectional energy interfaces, where both performance and reliability are critical. By addressing a key control challenge, this work contributes to the development of more robust and responsive power systems for future EV applications.

2. Operating Principles

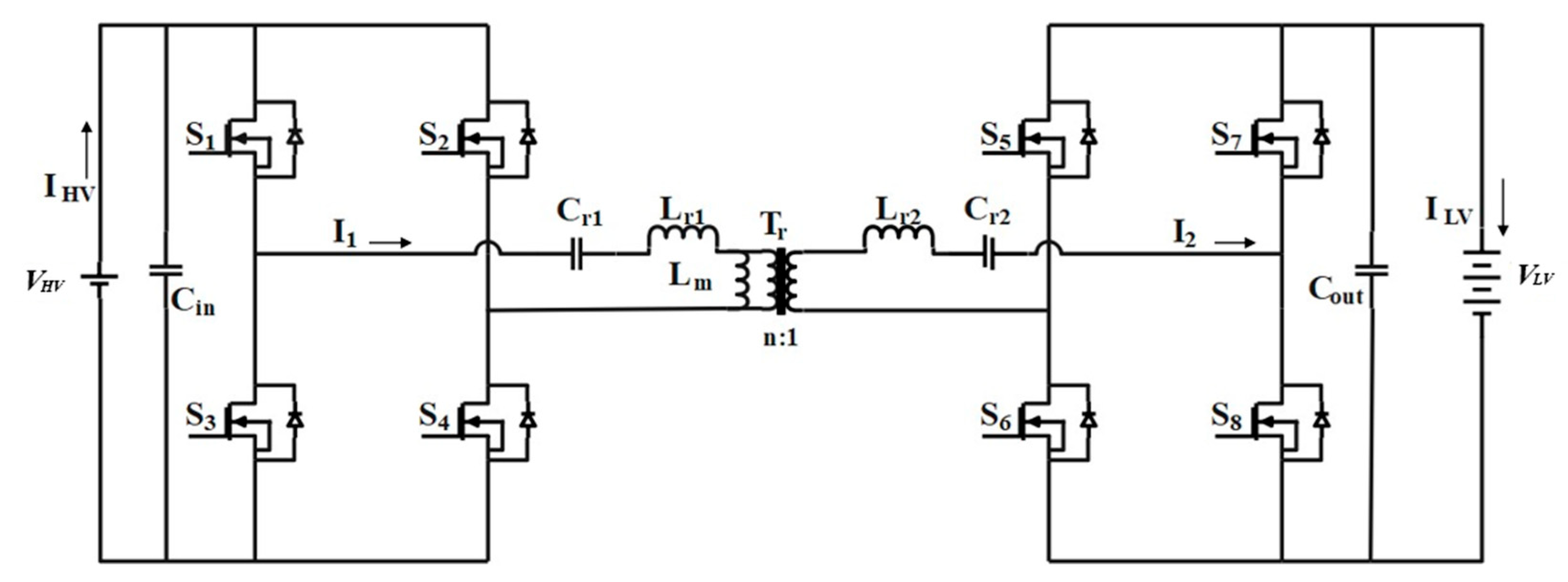

Figure 2 illustrates the configuration of the CLLC converter. In

Figure 2,

and

denote the voltage and current at the high voltage side, respectively;

denotes the primary current;

denote the primary switches;

denote the secondary switches;

and

denote the resonant capacitors;

and

denote the resonant inductors;

denotes the magnetizing inductor;

denotes the secondary current;

and

denote the input and output capacitors, respectively; and

denotes the voltage at the low voltage side.

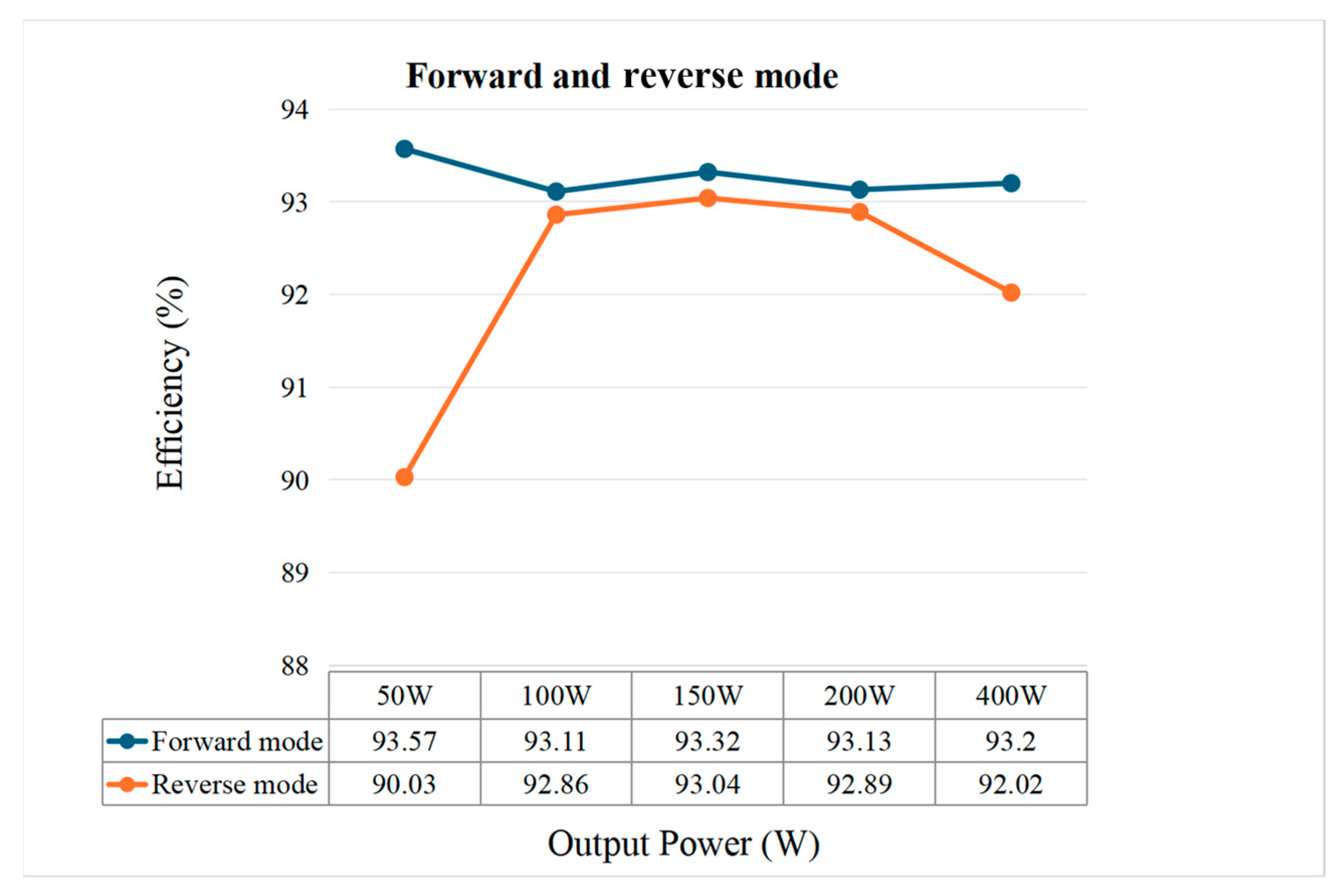

The converter can operate in the forward or reverse operating mode. In the forward mode, power is converted from the primary to the secondary side, and the output voltage is lower than the input voltage with the purpose of charging the battery. In the reverse mode, power is converted from the secondary to the primary side, and the output voltage is greater than the input voltage with the purpose of releasing energy from the battery.

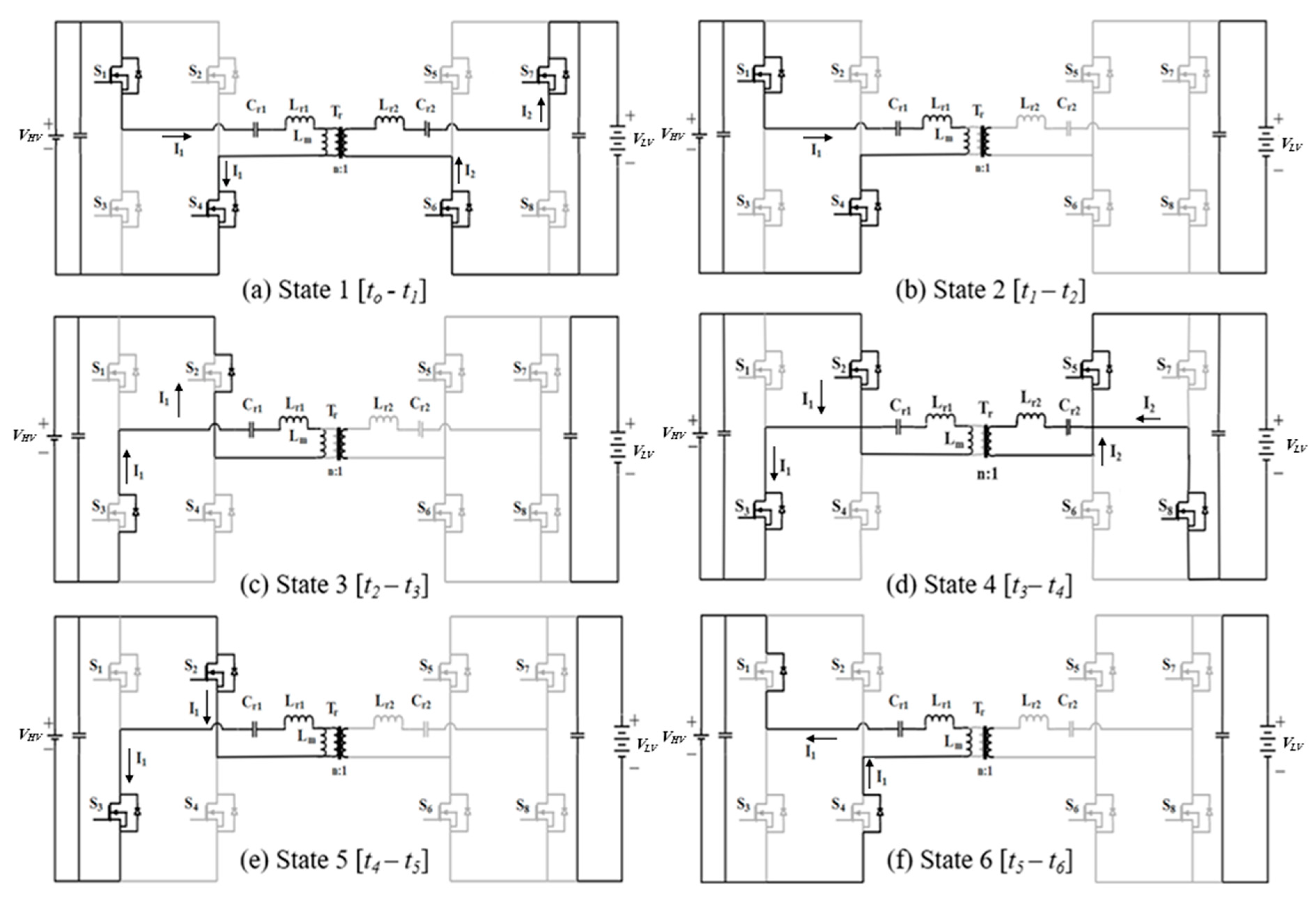

Figure 3 depicts the operating states of the proposed CLLC converter. The converter operates in six states during a switching cycle. States 1, 2, and 3 are operated repeatedly with various pairs of switches and rectifiers to achieve States 4, 5, and 6. States 1 and 4 are modes of resonance and power transfer, States 2 and 5 are modes of non-resonance, and States 3 and 6 represent the dead-time duration. The switches on the primary side function in the forward mode when energy is converted from the primary to the secondary side, whereas the switches on the secondary side are turned off and function as rectifiers. In the figure, the red and blue arrows indicate the current flow on both sides of the converter (I

1 and I

2, respectively), clearly showing how energy is transferred through the transformer (T

r). The voltage boosting process occurs as the secondary-side current is reflected to the primary side according to the transformer turns ratio, demonstrating the step-up conversion capability of the CLLC topology.

State 1 []: and are turned on, and power is converted to the secondary rectifying stage through the transformer . The input voltage source forces the primary currents to flow in the positive direction through and . The output voltage on the secondary side is induced on the magnetizing inductor , leading to the linear buildup of the magnetizing current . Therefore, does not participate in the resonance of the primary side.

State 2 [–]: The resonance is broken, and power is no longer converted to the secondary side when drops to . The primary current is equal to the magnetizing current during this mode, and the magnetizing energy is built up until the switches and are turned off. During this period, participates in the resonant operation because the output stage is separated from the primary side. The resonant tank is configured such that is in series with and . In State 2, follows with a large magnetizing inductance, so its resonance can be ignored.

State 3 []: In this state, the pair of switches and are used to create a dead-time duration. Under the ZVS state, the antiparallel diodes of and conduct the current.

State 4 []: The converter begins to convert power from the primary side to the secondary side when and are turned on. Similarly to State 1, changes direction throughout this mode.

State 5 []: Similarly to State 2, resonance is broken in State 5, and power is no longer being converted. becomes zero in the absence of power conversion through .

State 6 []: No power is delivered to the secondary rectifying stage during this dead-time state. The antiparallel diodes of and conduct the primary current, enabling the operation of a switch in the ZVS state.

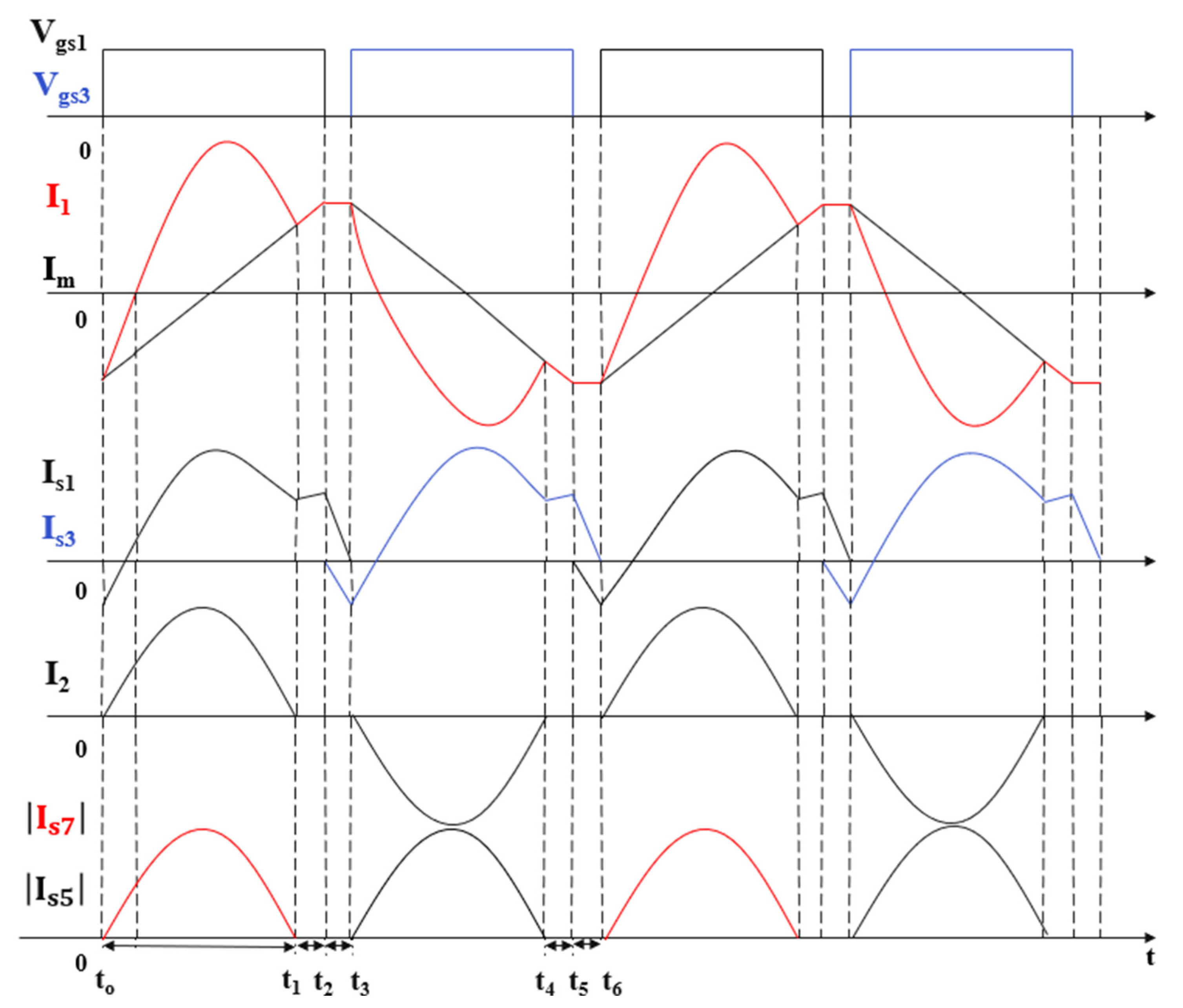

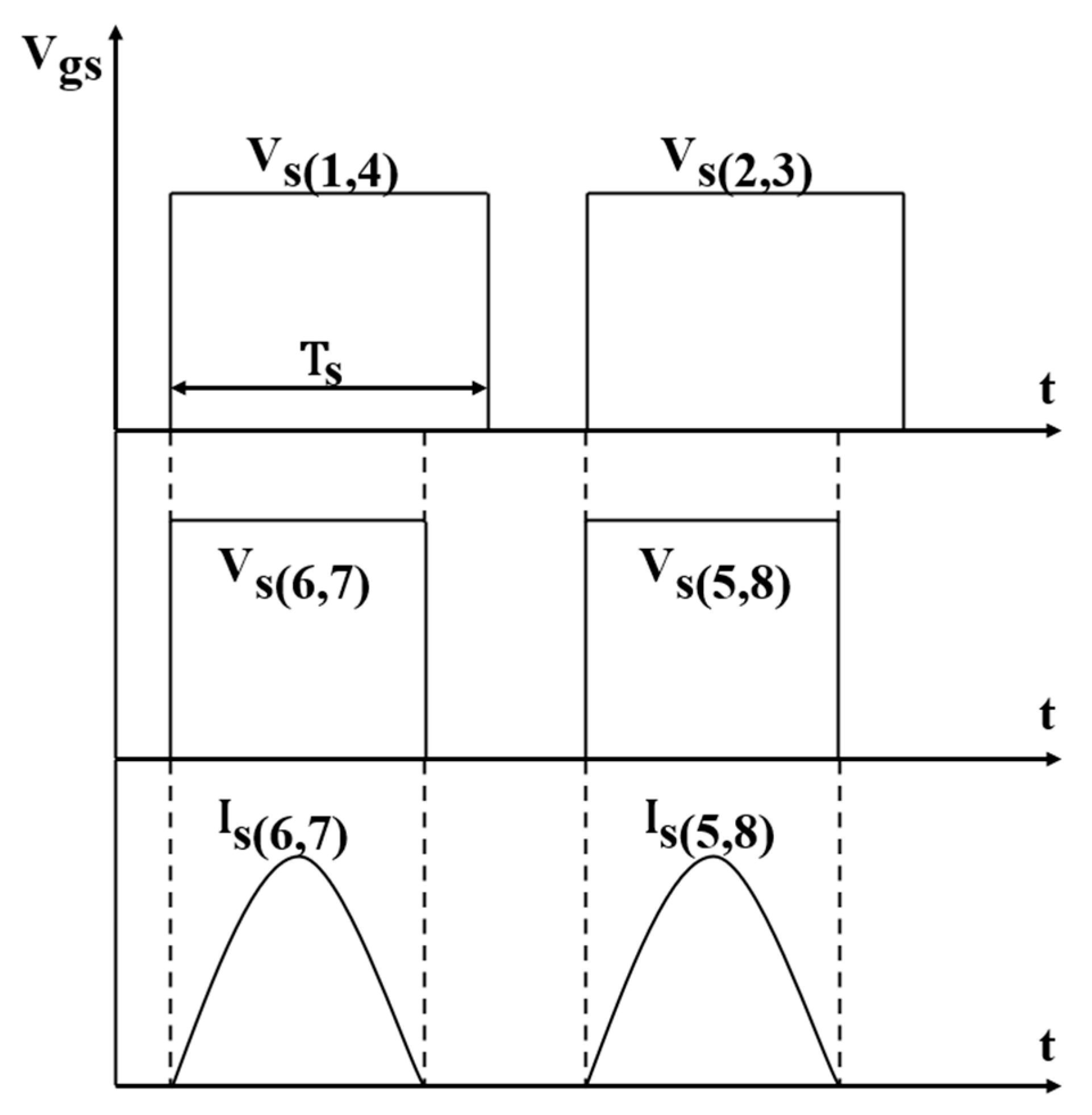

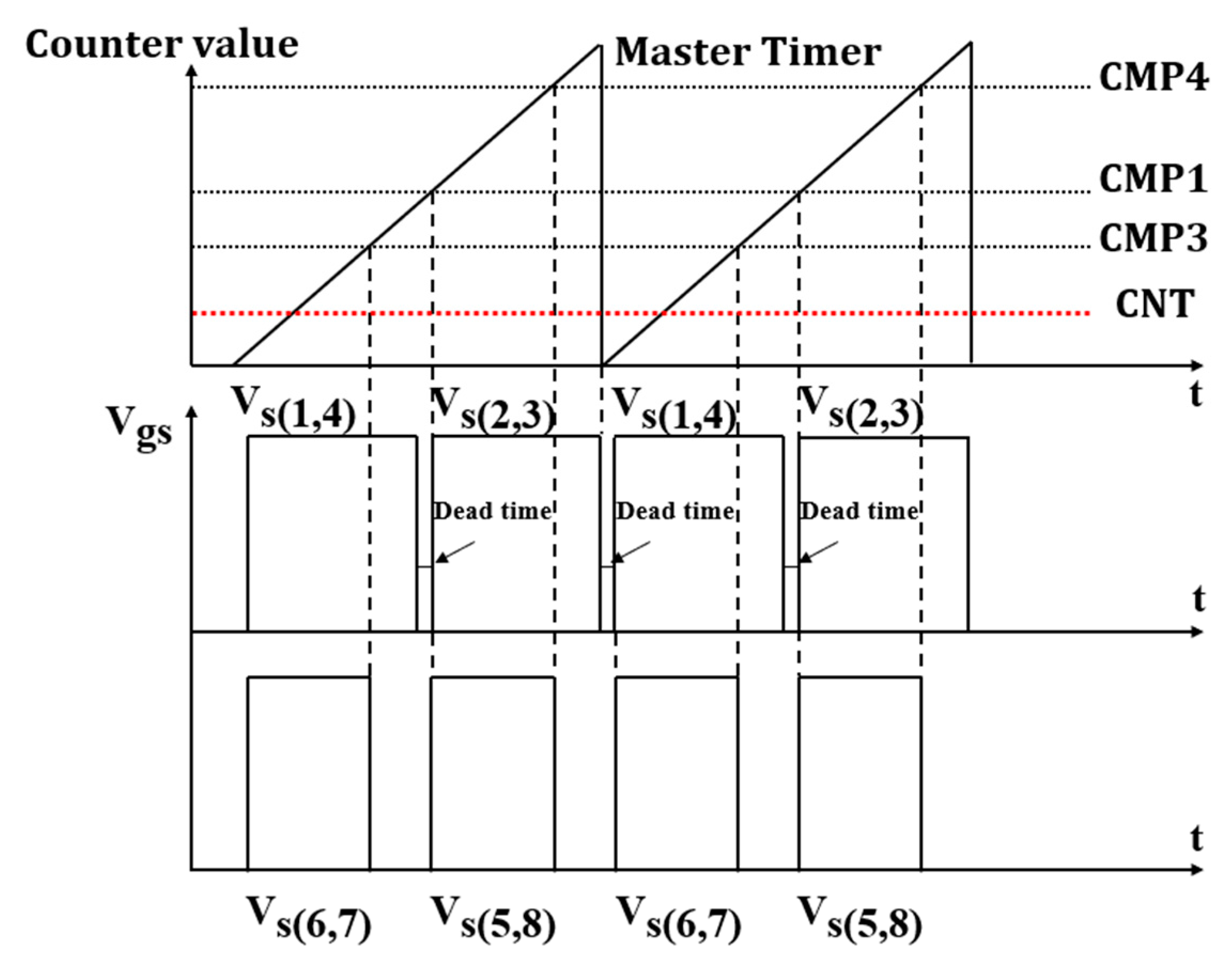

Figure 4 illustrates the theoretical waveforms for each mode during a single switching cycle. Because the configuration of the primary and secondary sides is symmetric, the waveforms of the forward and reverse modes are identical. This symmetric configuration ensures that the power conversion efficiency and the switch control method are maintained constantly regardless of the power flow direction.

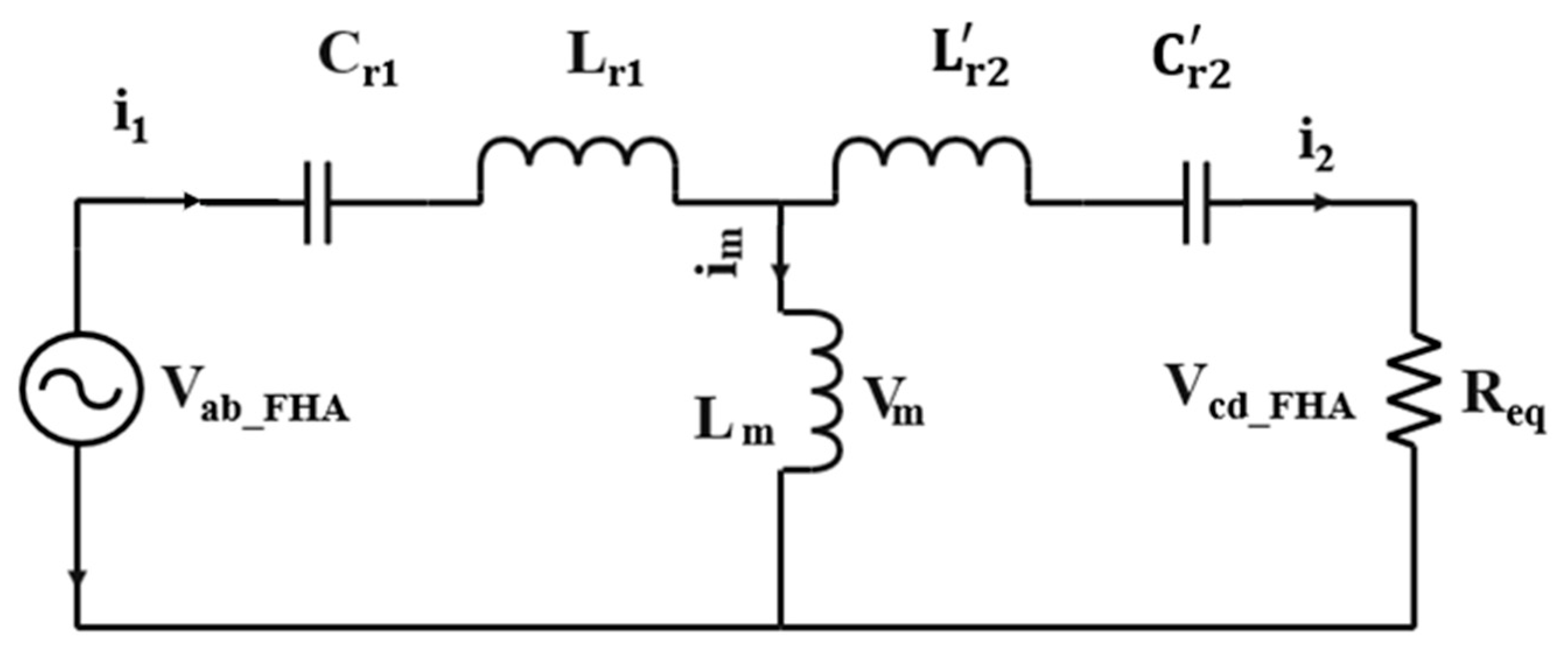

The FHA method greatly simplifies the design process. The voltage gain equation, which relates the output voltage to the input voltage as a function of switching frequency, plays an important role in the design of resonant converters. This equation has a clear physical interpretation, making it amenable for use in the design of new converters. Through the FHA method, the circuit depicted in

Figure 2 can be approximated to the equivalent circuit depicted in

Figure 5. The electrical circuit of the proposed converter can be simplified to obtain the gain of the resonant network with respect to the switching frequency.

The square wave can be mathematically expressed using a Fourier series as follows:

The fundamental component of

can be extracted from Equation (1) using the FHA method as follows:

where

is the time parameter;

is the switching frequency; and

is a square waveform that varies from

to

. The root-mean-square value of

is

which can be calculated as follows:

Accordingly, the output voltage of the resonant network,

, can be expressed as follows:

where

is the phase shift associated with the input voltage;

is a square waveform that varies from

to

. The root-mean-square value of

is

, which can be calculated as follows:

The fundamental component of the rectifier current,

, can also be expressed in the same form as Equations (2) and (4) as follows:

where

is the root-mean-square value of

. Therefore, the average output current,

, can be derived from Equation (6) as follows:

Given that

and

are in phase, the resistive load of the resonant network,

, is equal to the ratio of the instantaneous voltage to the current with the load resistance, as shown in Equation (8).

The mathematical expression for equivalent resistance on the primary side is given in Equation (9):

where

is the original load resistance in the forward mode. All the equivalent resonant parameters associated with the primary side can be derived as shown in Equation (10).

From Equation (1),

and

can be derived in the Laplace domain as follows:

The following relations can be derived by applying Kirchhoff’s voltage law to the configuration presented in

Figure 5.

The expression for the equivalent output current

in the Laplace domain is presented in Equation (14). The equivalent output current in the Laplace domain can be expressed in terms of the switching frequency using Equation (13).

The expression for the equivalent output voltage before the diode bridge in the frequency domain can be derived by combining Equations (9) and (14), as follows:

The general transfer function

can be determined from Equations (11) and (15) as follows:

The gain function of the CLLC converter can be derived from Equation (16) as follows:

The mathematical expressions for the quality factor, inductance ratio, resonant frequency, and normalized frequency are given in Equations (18)–(22), respectively.

In this section, the relationship between , , and is analyzed, and the voltage gain characteristic of the system is explained. In the next section, the mathematical expressions for calculating the value of each component, such as , , , , and , will be discussed.