Research on Improving the Avalanche Current Limit of Parallel SiC MOSFETs

Abstract

1. Introduction

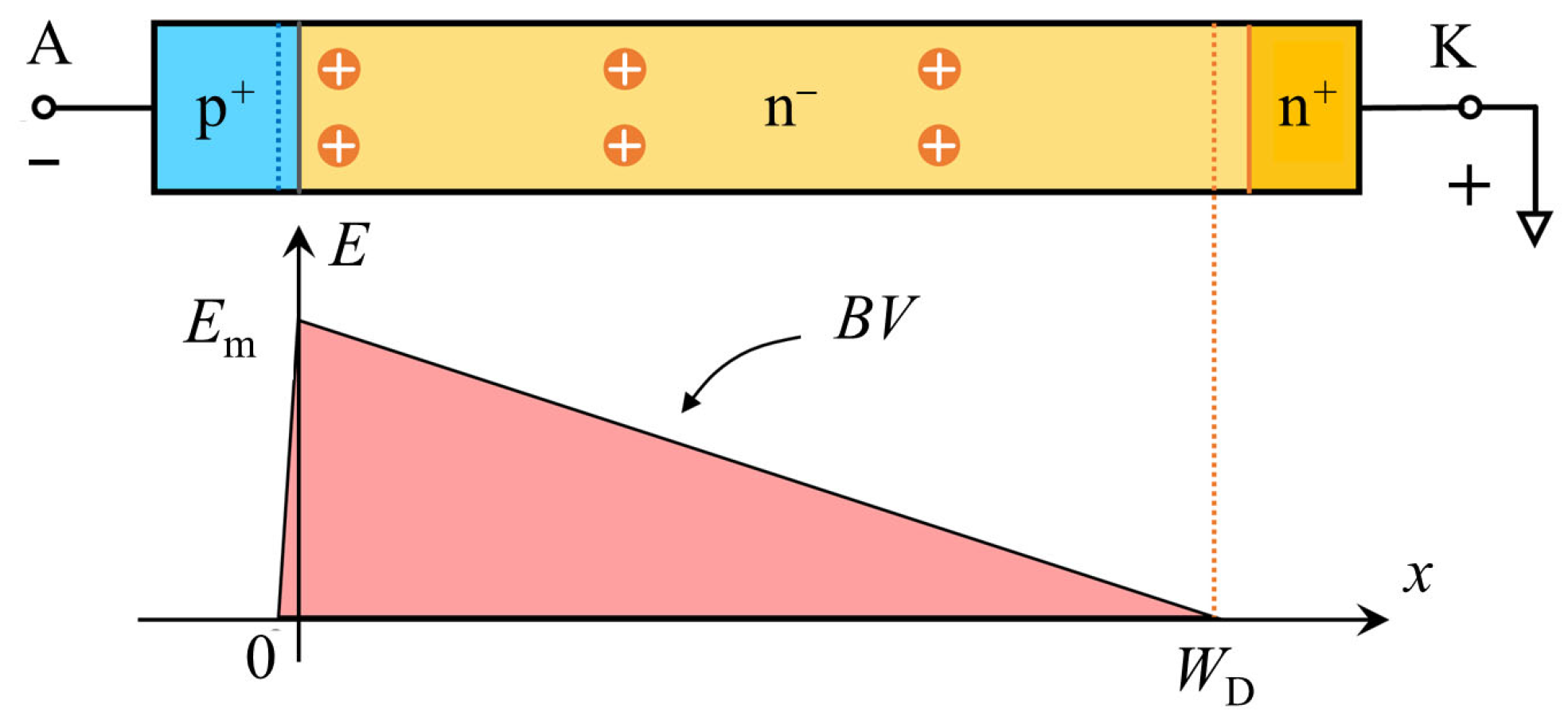

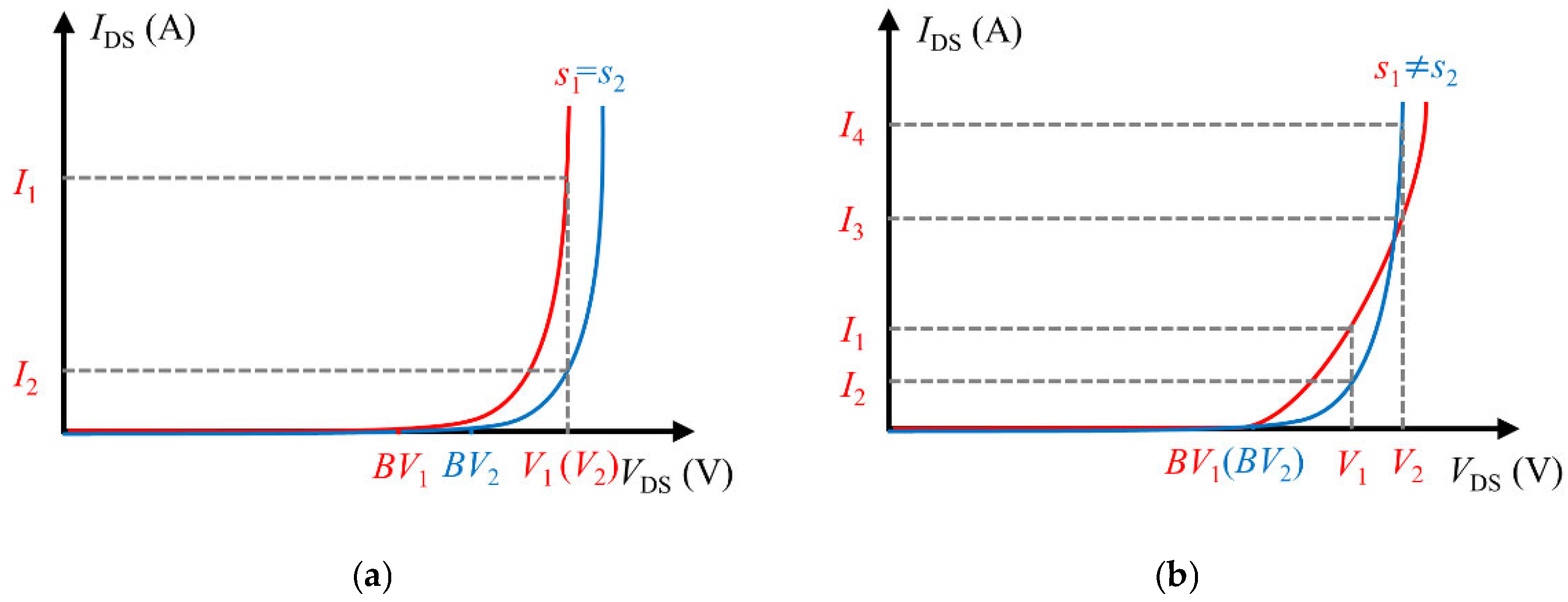

2. Principle of Avalanche Breakdown of Power Devices

3. Avalanche Test of Power Devices

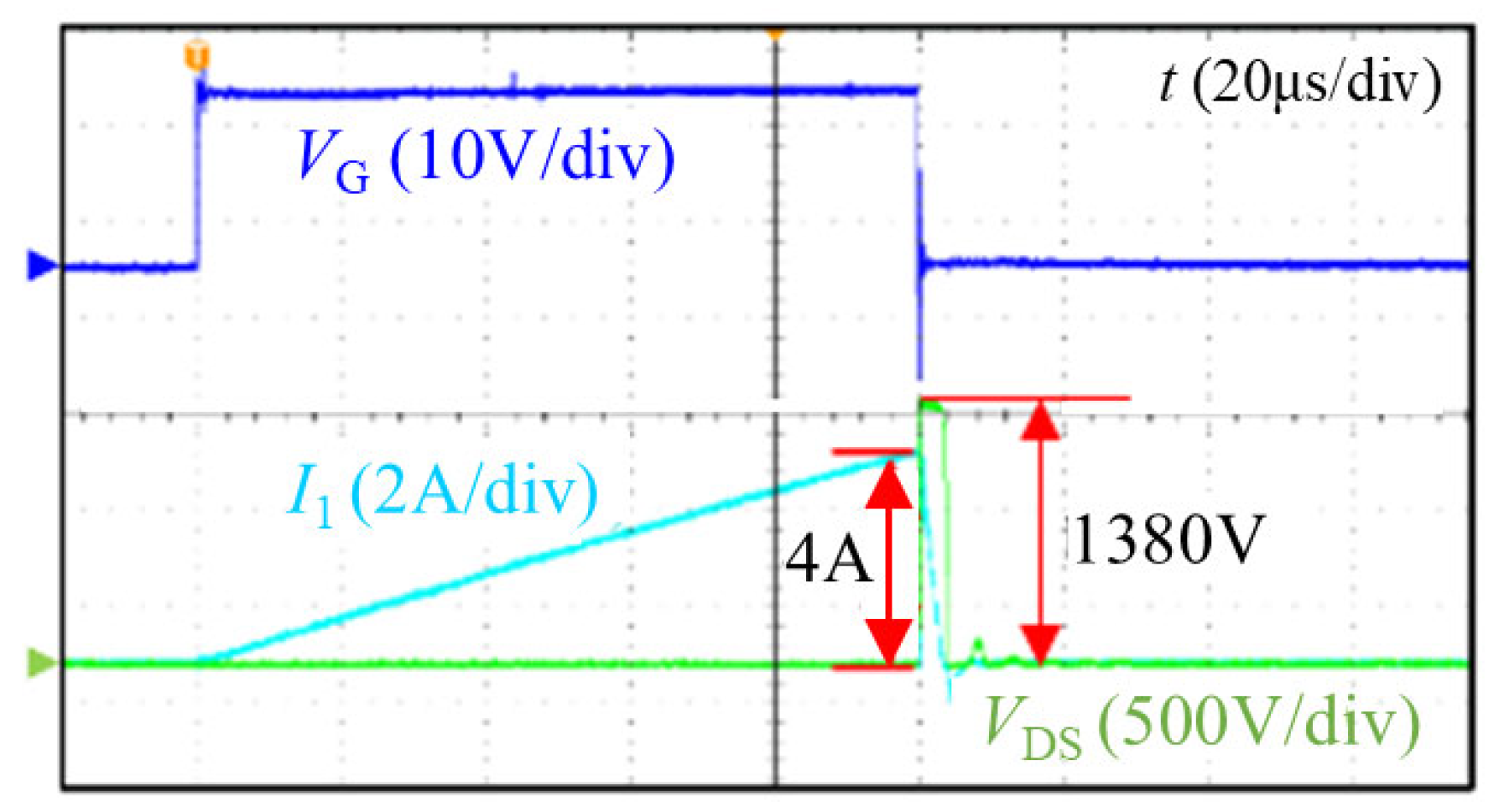

3.1. Principle of UIS Avalanche Test

3.2. Design of UIS Avalanche Test Plan

4. Proposal and Verification of Methods for Improving Parallel Avalanche Capability

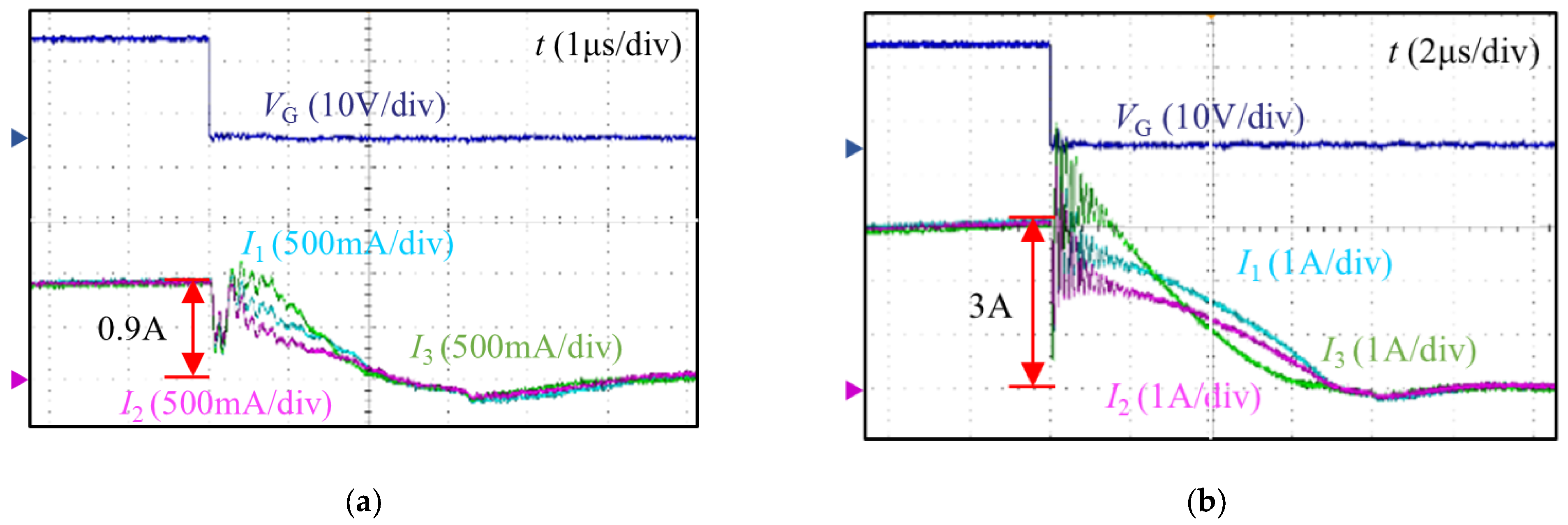

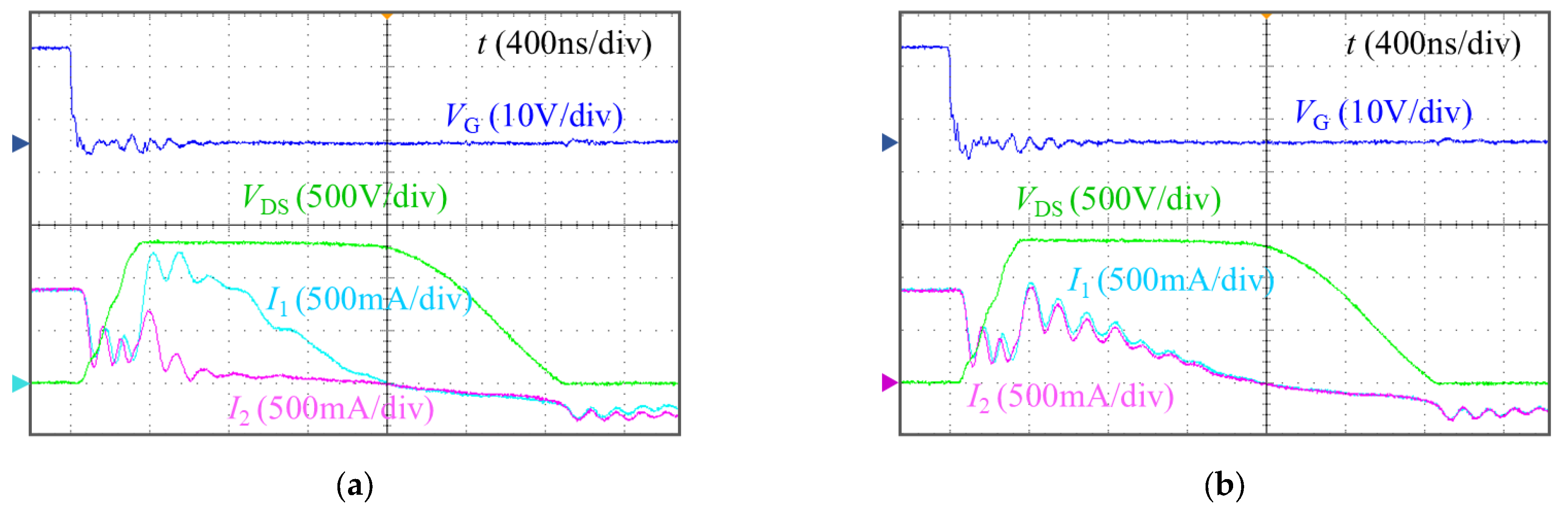

- (a)

- Firstly, an Agilent B1505A is used to test the static parameters of a large number of SCT3120AL. The electrical characteristic curves, such as the forward I-V curve when VG = 18 V and Ttest = 25 °C, and the reverse I-V curve when VG = −4 V and Ttest = 25 °C, and the threshold voltage are tested after the drain electrode and the gate electrode are shorted; the drain-source voltage is the threshold voltage when the drain-source is 10 mA.

- (b)

- In addition, the blocking characteristic curve is tested for all devices, and the drain-source voltage at ID = 1 mA is selected as the low-current BV.

- (c)

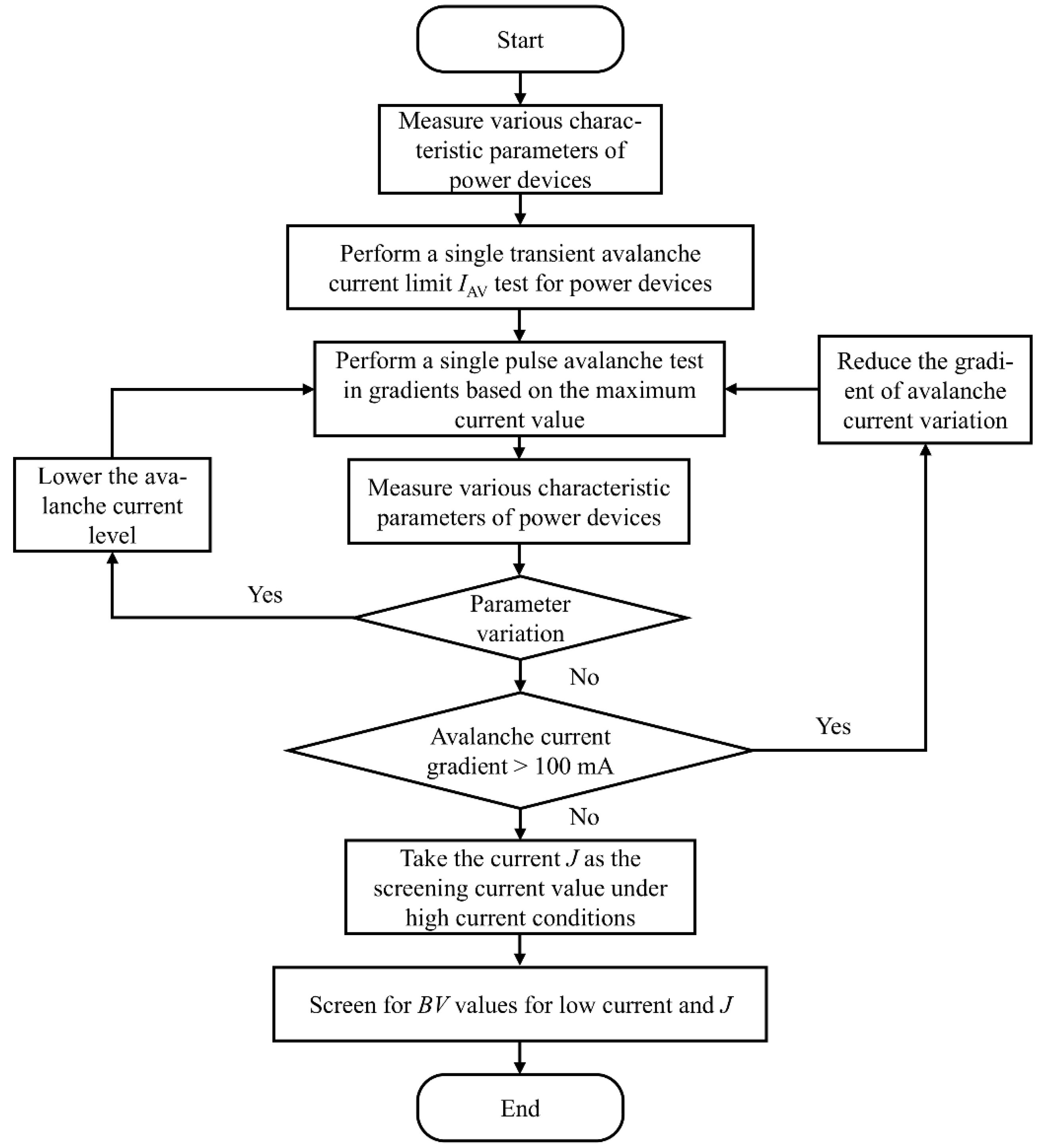

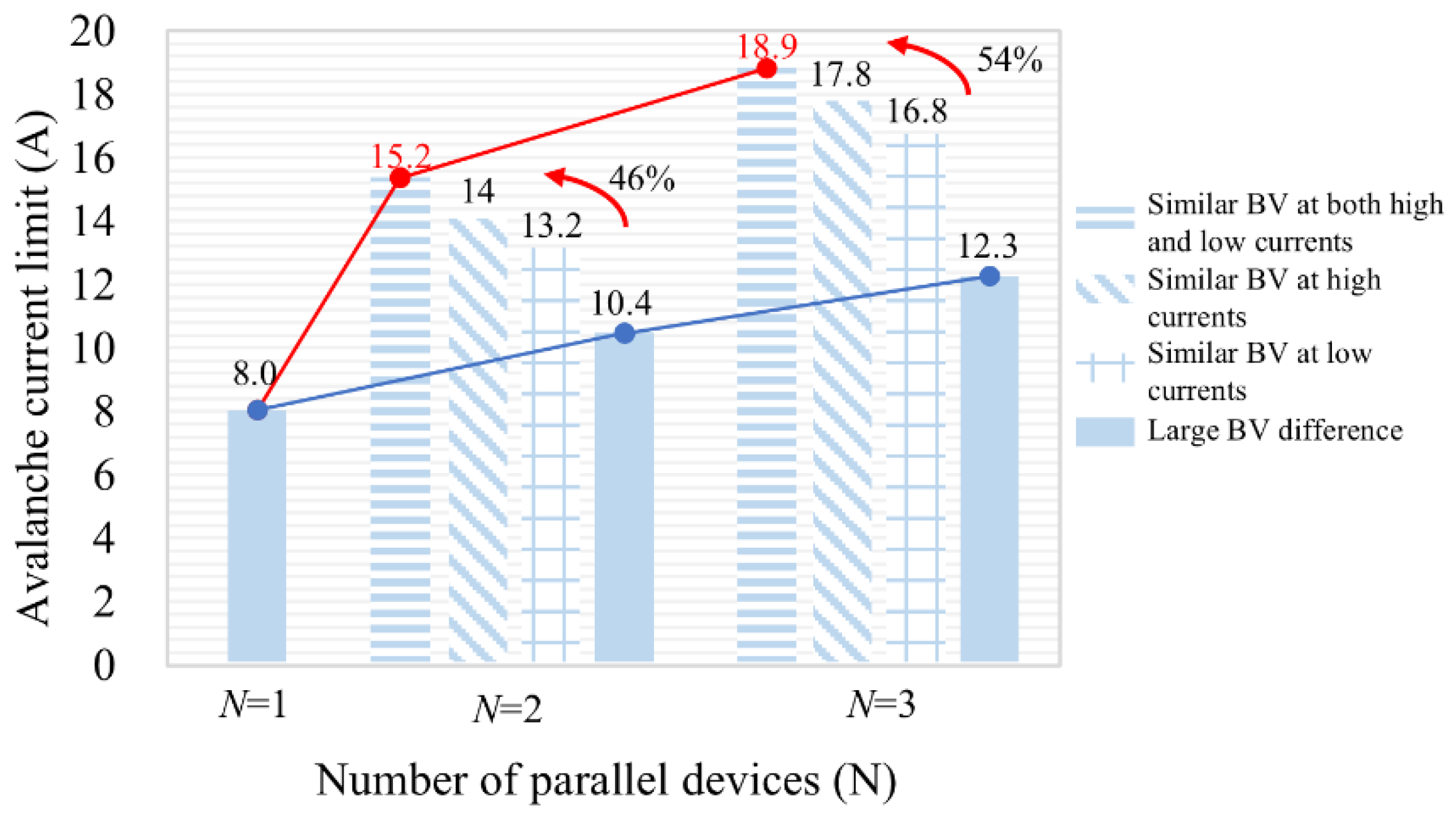

- Parts of SiC MOSFETs are selected for single avalanche current limit testing to determine the current limit IAV of the device. The charging duration is maintained at 100 μs, and the charging voltage is continuously increased for the UIS test until the device fails. After multiple tests, the IAV of the selected DUT is around 8 A.

- (d)

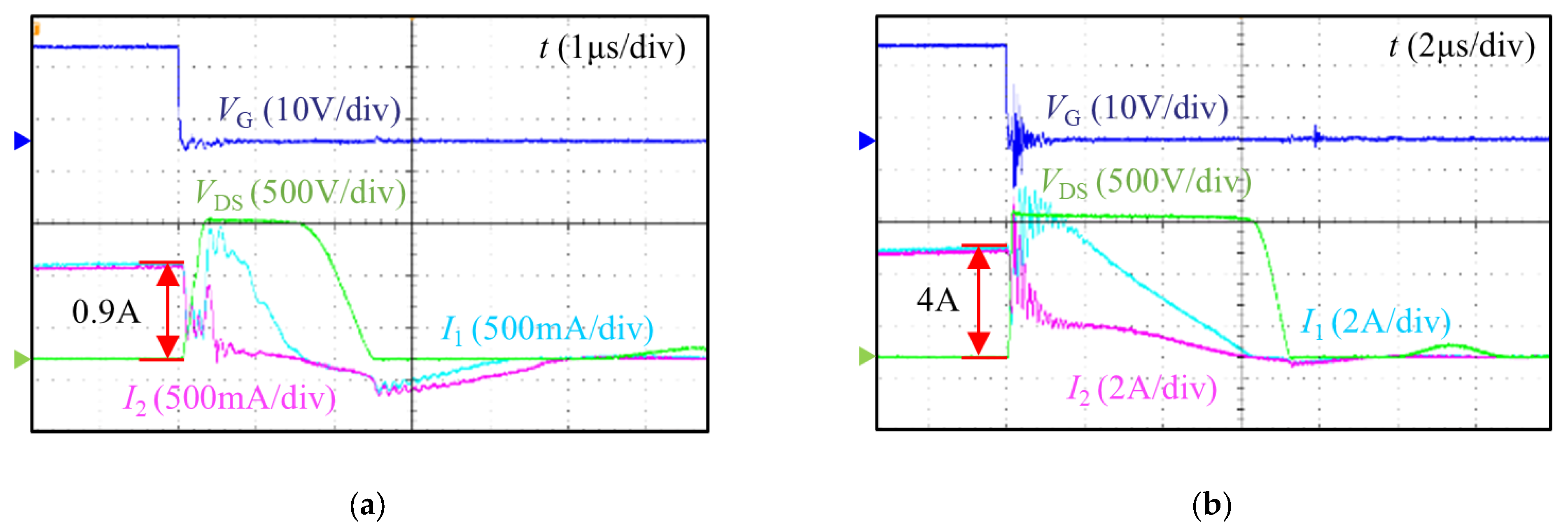

- Some SiC MOSFETs are selected to perform avalanche at different avalanche current levels, with three devices used for comparison at each current level. Taking the selected DUT as an example, after three tests are performed at avalanche current levels of 7 A, 6.5 A, and 500 mA, respectively, the static electrical parameters are tested and recorded.

- (e)

- For devices that have not undergone numerical changes, the current range is narrowed, and the maximum value is continuously approached. Screening is stopped when the avalanche current gradient is less than 100 mA.

- (f)

- The final result is that the devices will experience an avalanche at 900 mA without significantly changes; therefore, devices with similar BVs measured at 1 mA and 900 mA are selected for parallel avalanche.

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Long, Y.; Chen, Y.; Wang, P.; Hou, B.; He, H. A novel insight into the mechanism of bipolar degradation in 4H-SiC MOSFET. IEEE Electron Device Lett. 2025, 46, 464–467. [Google Scholar] [CrossRef]

- Kim, M.; Forbes, J.J.; Hirsch, E.A. Evaluation of long-term reliability and overcurrent capabilities of 15-kV SiC MOSFETs and 20-kV SiC IGBTs during narrow current pulsed conditions. IEEE Trans. Plasma Sci. 2020, 48, 3962–3967. [Google Scholar] [CrossRef]

- Deng, X.; Huang, W.; Li, X.; Chen, C.; Wen, Y.; Ding, J.; Chen, W.; Sun, Y.; Zhang, B. Investigation of failure mechanisms of 1200 V rated trench SiC MOSFETs under repetitive avalanche stress. IEEE Trans. Power Electron. 2022, 37, 10562–10571. [Google Scholar] [CrossRef]

- Luo, H.C.; Wu, H.; Zhang, J.P.; Zheng, B.F.; Lang, L.; Zhang, G.Q.; Chen, X.P. Study on Characteristics and UIS of Hexagonal Planar SiC VDMOSFETs With Varied JFET Width. IEEE Trans. Device Mater. Reliab. 2024, 24, 323–328. [Google Scholar] [CrossRef]

- Mao, H.; Qiu, G.; Jiang, X.; Jiang, H.; Zhong, X.; Tang, L.; Zhang, Y.; Ran, L.; Wu, Y. Investigation on the degradations of parallel-connected 4H-SiC MOSFETs under repetitive UIS stresses. IEEE Trans. Electron Devices 2022, 69, 650–657. [Google Scholar] [CrossRef]

- Mao, H.; Ran, L.; Chen, H.; Zhou, X.; Jiang, H. Avalanche capability degradation of the parallel-connected SiC MOSFETs. Microelectron. Reliab. 2023, 142, 114926. [Google Scholar] [CrossRef]

- He, Y.; Zhang, J.; Shao, S. Dynamic current balancing for paralleled SiC MOSFETs with circuit mismatches considering circulating current in drive circuit. CPSS Trans. Power Electron. Appl. 2024, 9, 219–229. [Google Scholar] [CrossRef]

- Smith, J.; Doe, A.B.; Lee, C. Toward understanding the positive shift of reverse turn-on voltage in the third quadrant operation in planar SiC power MOSFETs after avalanche breakdown. IEEE Trans. Electron Devices 2023, 70, 1234–1245. [Google Scholar]

- Abuogo, J.; Schwabe, C.; Lutz, J.; Basler, T. Comparison of a Power Cycling Test using Repetitive Unclamped Inductive Switching for Heat Generation with the DC Power Cycling Test. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023; pp. 1–8. [Google Scholar]

- Mortazavinatanzi, S.; Rezania, A.; Rosendahl, L. High-Throughput Manufacturing of Flexible Thermoelectric Generators for Low- to Medium-Temperature Applications Based on Nano-Silver Bonding. IEEE Trans. Electron Devices 2022, 69, 5760–5765. [Google Scholar] [CrossRef]

- Shao, W.; Ran, L.; Zeng, Z.; Li, X.; Philip, M. Design and evaluation of SiC multichip power module with low and symmetrical inductance. J. Eng. 2019, 2019, 3573–3577. [Google Scholar]

- Zhu, C.; Zhao, L.; Yang, Z.; Gu, X. Degradation and breakdown behaviors of SGTs under repetitive unclamped inductive switching avalanche stress. Chin. Phys. B 2022, 31, 097303. [Google Scholar] [CrossRef]

- Ren, N.; Hu, H.; Lyu, X.; Wu, J.; Xu, H.; Li, R.; Zuo, Z.; Wang, K.; Sheng, K. Investigation on single pulse avalanche failure of SiC MOSFET and Si IGBT. Solid-State Electron. 2019, 152, 33–40. [Google Scholar] [CrossRef]

- Zhao, X.; Li, T.; Liang, X.; Wu, Y.; Li, C.; Zheng, Z. Investigation on SiC MOSFET’s avalanche and short-circuit failure mechanism. In Proceedings of the 2022 IEEE 5th International Electrical and Energy Conference (CIEEC), Nanjing, China, 27–29 May 2022; pp. 3916–3921. [Google Scholar]

- Kim, D.; Jang, S.Y.; Morgan, A.J.; Sung, W. Influence of P+ Body on Performance and Ruggedness of 1.2 kV 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2024, 71, 7659–7665. [Google Scholar] [CrossRef]

- Liu, S.; Gu, C.; Wei, J.; Qian, Q.; Sun, W.; Huang, A.Q. Repetitive Unclamped-Inductive-Switching-Induced Electrical Parameters Degradations and Simulation Optimizations for 4H-SiC MOSFETs. IEEE Trans. Electron Devices 2016, 63, 4331–4338. [Google Scholar] [CrossRef]

- Yue, G.; Ren, N.; Sheng, K. Investigation of the Single-Pulse Avalanche Capability of Commercial 1.2 kV SiC MOSFETs with Different Structures. In Proceedings of the 2024 IEEE 11th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Dayton, OH, USA, 4–6 September 2024; pp. 1–4. [Google Scholar]

- Lu, J.; Song, W.; Liu, T.; Tang, J.; Zhao, W.; Li, D.; Li, B. Analysis of single event response and hardening methods in 1.2 kV SiC power MOSFET with multicell and termination structure. IEEE Trans. Electron Devices 2023, 70, 6459–6464. [Google Scholar] [CrossRef]

- Wu, H.; Luo, H.; Zhang, J.; Zheng, B.; Lang, L.; Wang, Z.; Zhang, G.; Chen, X. Investigation of unclamped inductive switch characteristics in 4H-SiC MOSFETs with different cell topologies. IEEE Trans. Electron Devices 2023, 70, 1181–1187. [Google Scholar] [CrossRef]

- Rikimaru, K.; Sakakura, S.; Shiraishi, T.; Yasutake, T.; Kishimoto, H.; Nishiguchi, T.; Kato, H. Avalanche Capability Improvement by Ion Implantation-induced Defects Control for Trench Power MOSFET. In Proceedings of the 2024 International Symposium on Semiconductor Manufacturing (ISSM), Tokyo, Japan, 9–10 December 2024; pp. 1–4. [Google Scholar]

- Miyamoto, K.; Ishi, D.; Hirose, T.; Kishimoto, H.; Sato, K.; Kachi, T.; Katou, H. Improvement of P-base contact resistance in power MOSFETs and its impact on avalanche capability. In Proceedings of the 2024 International Symposium on Semiconductor Manufacturing (ISSM), Tokyo, Japan, 9–10 December 2024; pp. 1–4. [Google Scholar]

- Mao, H.; Jiang, H.; Qiu, G.; Zhang, Y.; Zhong, X.; Feng, H.; Ran, L. Single-Pulse Avalanche Failure Characterization of Single and Paralleled SiC MOSFETs. In Proceedings of the 2021 IEEE Workshop on Wide Bandgap Power Devices and Applications in Asia (WiPDA Asia), Wuhan, China, 25–27 August 2021; pp. 467–471. [Google Scholar]

- Kumar, A.; Kokkonda, R.K.; Bhattacharya, S.; Veliadis, V. Single Shot Avalanche Characterization of Series and Parallel Connection of SiC Power MOSFETs. In Proceedings of the 2019 IEEE 7th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Raleigh, NC, USA, 29–31 October 2019; pp. 438–443. [Google Scholar]

- Hu, J.; Alatise, O.; Ortiz-Gonzalez, J.A.; Alexakis, P.; Ran, L.; Mawby, P. Finite element modelling and experimental characterisation of paralleled SiC MOSFET failure under avalanche mode conduction. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–9. [Google Scholar]

- Takamori, T.; Wada, K.; Saito, W.; Nishizawa, S.-I. Paralleled SiC MOSFETs DC Circuit Breaker with SiC MPS Diode as Avalanche Voltage Clamping. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 225–229. [Google Scholar]

- Herrmann, C.; He, M.; Alaluss, M.; Basler, T.; Lutz, J. Avalanche Robustness of SiC MOSFETs in Parallel Connections. In Proceedings of the PCIM Europe 2023; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 9–11 May 2023; pp. 1–10. [Google Scholar]

- Fayyaz, A.; Asllani, B.; Castellazzi, A.; Riccio, M.; Irace, A. Avalanche ruggedness of parallel SiC power MOSFETs. Microelectron. Reliab. 2018, 88, 666–670. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices; John Wiley & Sons: Hoboken, NJ, USA, 2006. [Google Scholar]

| No. | Object | No. | Object |

|---|---|---|---|

| 1 | Main power supply | 6 | Agilent N1265A |

| 2 | Main circuit | 7 | Agilent B1505A |

| 3 | Auxiliary power | 8 | Tektronix TCP0030A |

| 4 | Control panel | 9 | Tektronix THDP0100 |

| 5 | Inductance | 10 | FLIR E5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mao, H.; Wu, B.; Lan, X.; Xia, Y.; Chen, J.; Tang, L. Research on Improving the Avalanche Current Limit of Parallel SiC MOSFETs. Electronics 2025, 14, 2502. https://doi.org/10.3390/electronics14132502

Mao H, Wu B, Lan X, Xia Y, Chen J, Tang L. Research on Improving the Avalanche Current Limit of Parallel SiC MOSFETs. Electronics. 2025; 14(13):2502. https://doi.org/10.3390/electronics14132502

Chicago/Turabian StyleMao, Hua, Binbing Wu, Xinsheng Lan, Yalong Xia, Junjie Chen, and Lei Tang. 2025. "Research on Improving the Avalanche Current Limit of Parallel SiC MOSFETs" Electronics 14, no. 13: 2502. https://doi.org/10.3390/electronics14132502

APA StyleMao, H., Wu, B., Lan, X., Xia, Y., Chen, J., & Tang, L. (2025). Research on Improving the Avalanche Current Limit of Parallel SiC MOSFETs. Electronics, 14(13), 2502. https://doi.org/10.3390/electronics14132502