Bulk-Driven CMOS Differential Stages for Ultra-Low-Voltage Ultra-Low-Power Operational Transconductance Amplifiers: A Comparative Analysis

Abstract

1. Introduction

- (a)

- Lower transconductance, i.e., the bulk transconductance is lower than the gate counterpart. This translates to lower gain, lower gain-bandwidth product (GBW) and higher noise for a given standby current.

- (b)

- Access to bulk terminals. Both bulks of p- and n-MOS devices need to be accessible for full BD exploitation. This is not possible in early single-well technology.

- (c)

- Poor matching and large silicon area. Related to point (b), devices laid out in different wells can have poor matching characteristics and require non-minimum area.

- (d)

- Maintaining a safe bulk-source biasing voltage. This is to avoid the turn on of the bulk-source p-n junction.

- (e)

- Poor concomitant BD and subthreshold operation MOS transistor modeling [34]. Performance predictions through simulations may not be accurate under these circumstances.

2. Definitions and Background

2.1. Definitions

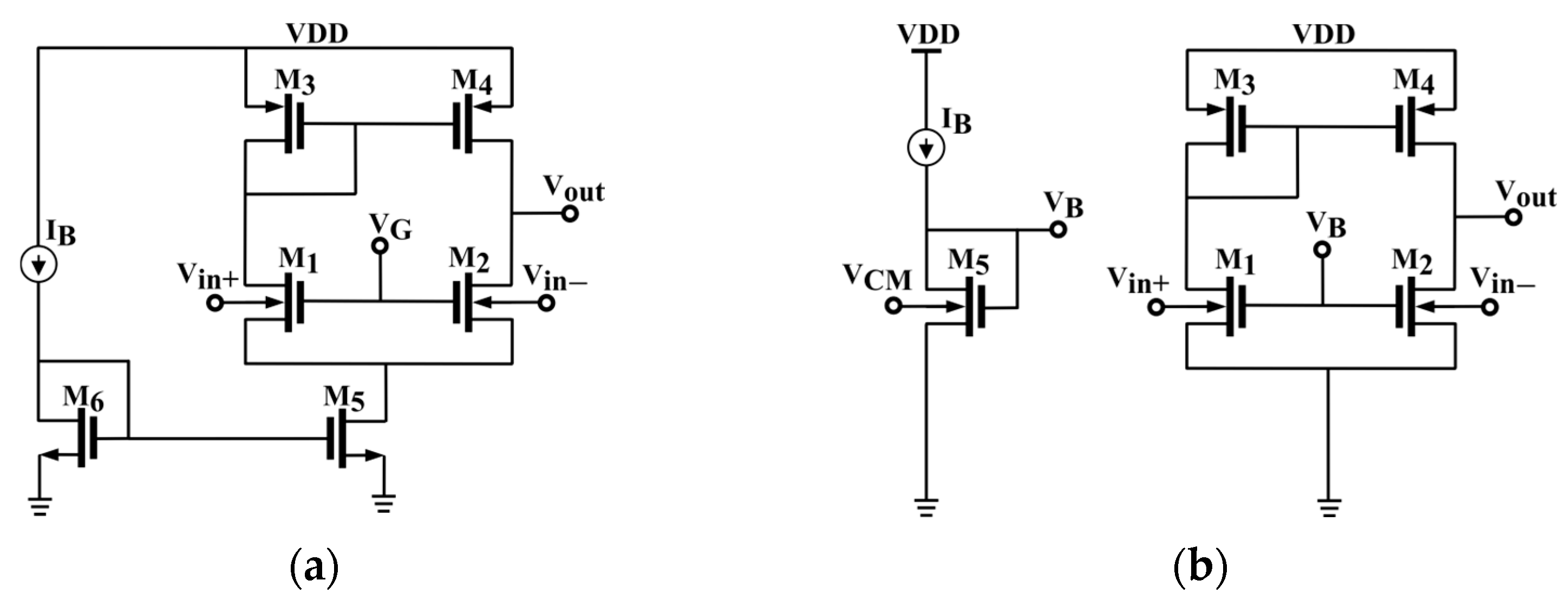

2.2. Basic BD Differential Stage Topologies

3. High Performance BD Input Stages

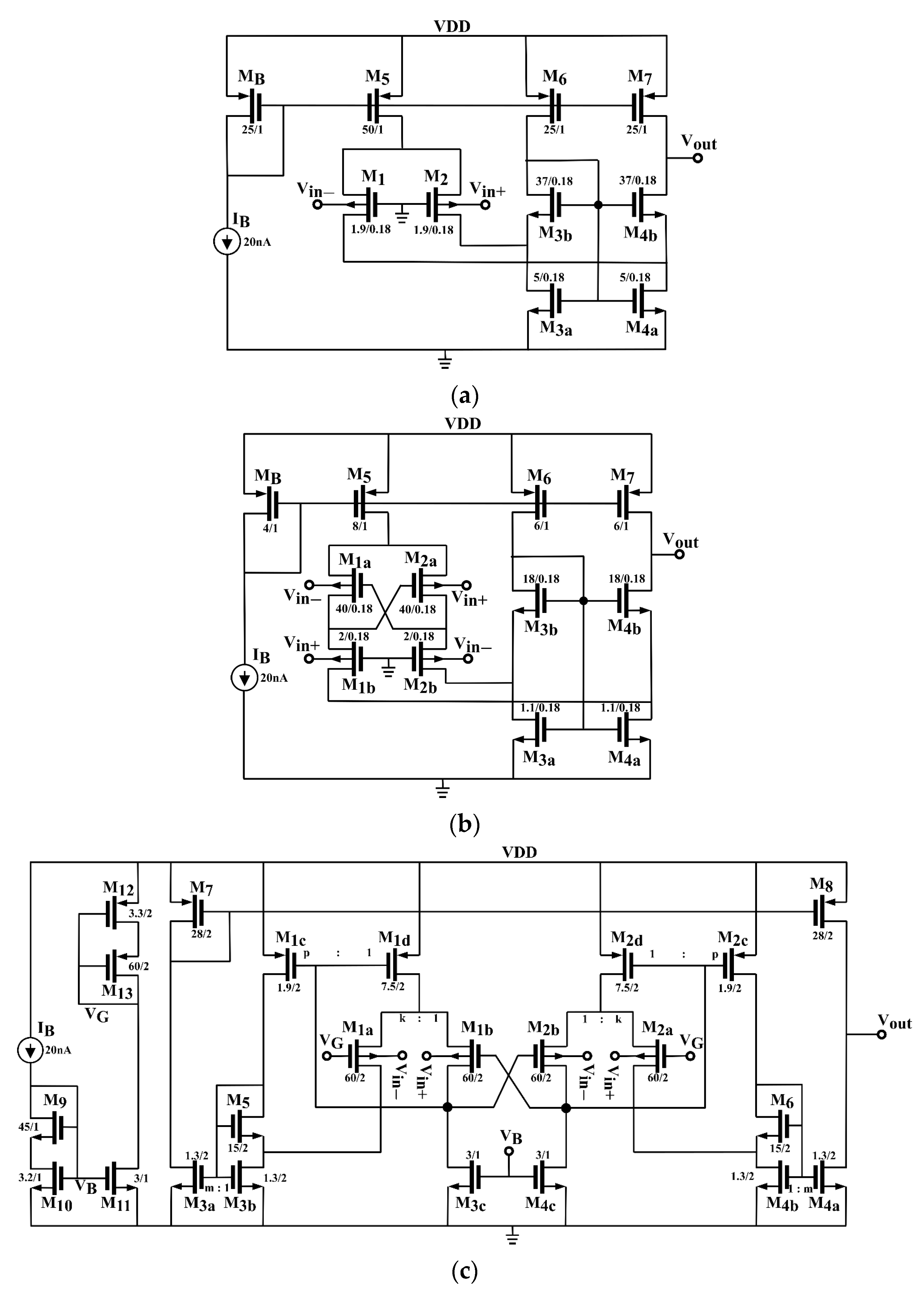

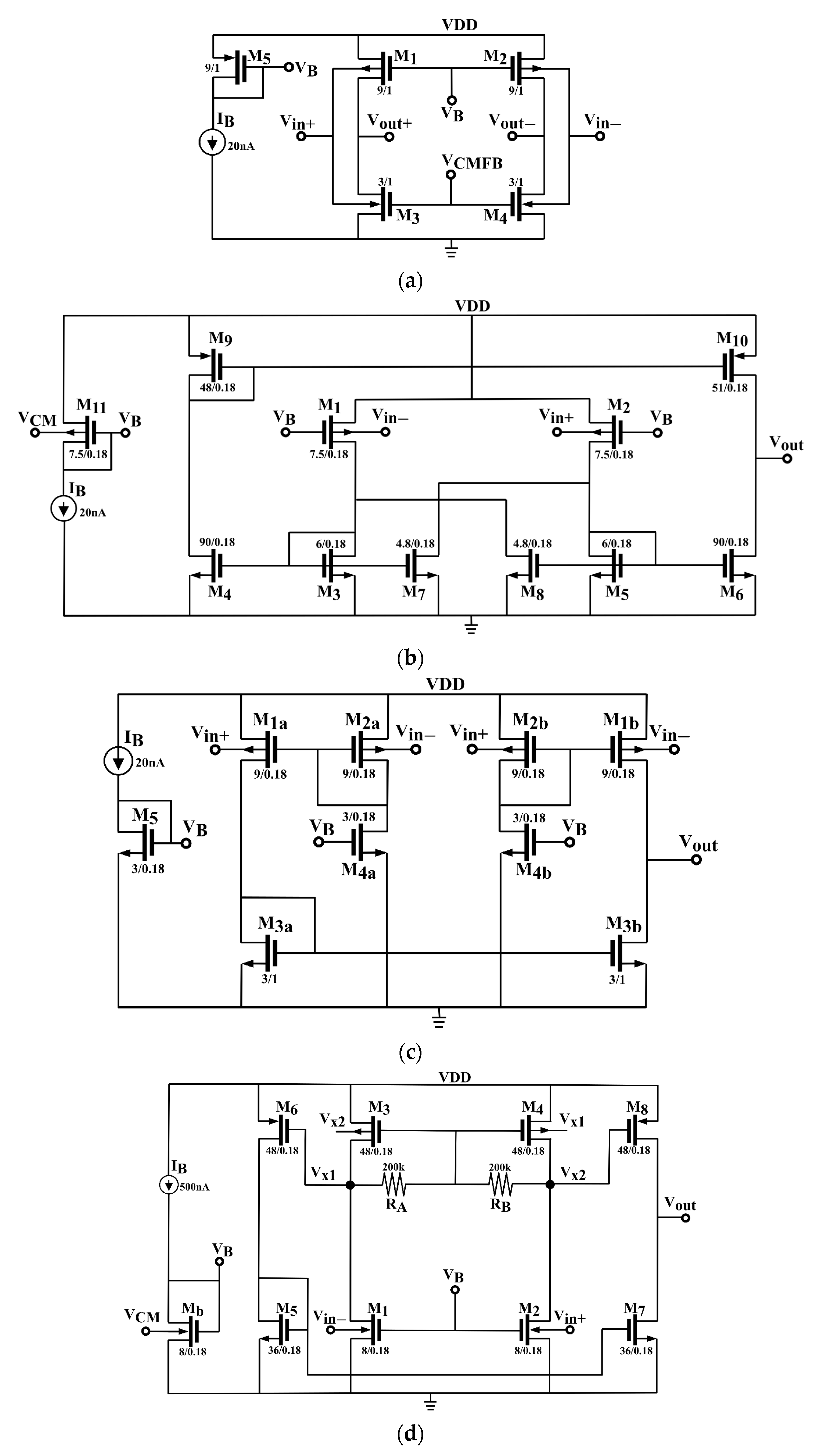

3.1. Tailed Differential Stages

3.2. Tail-Less Class-A Differential Stages

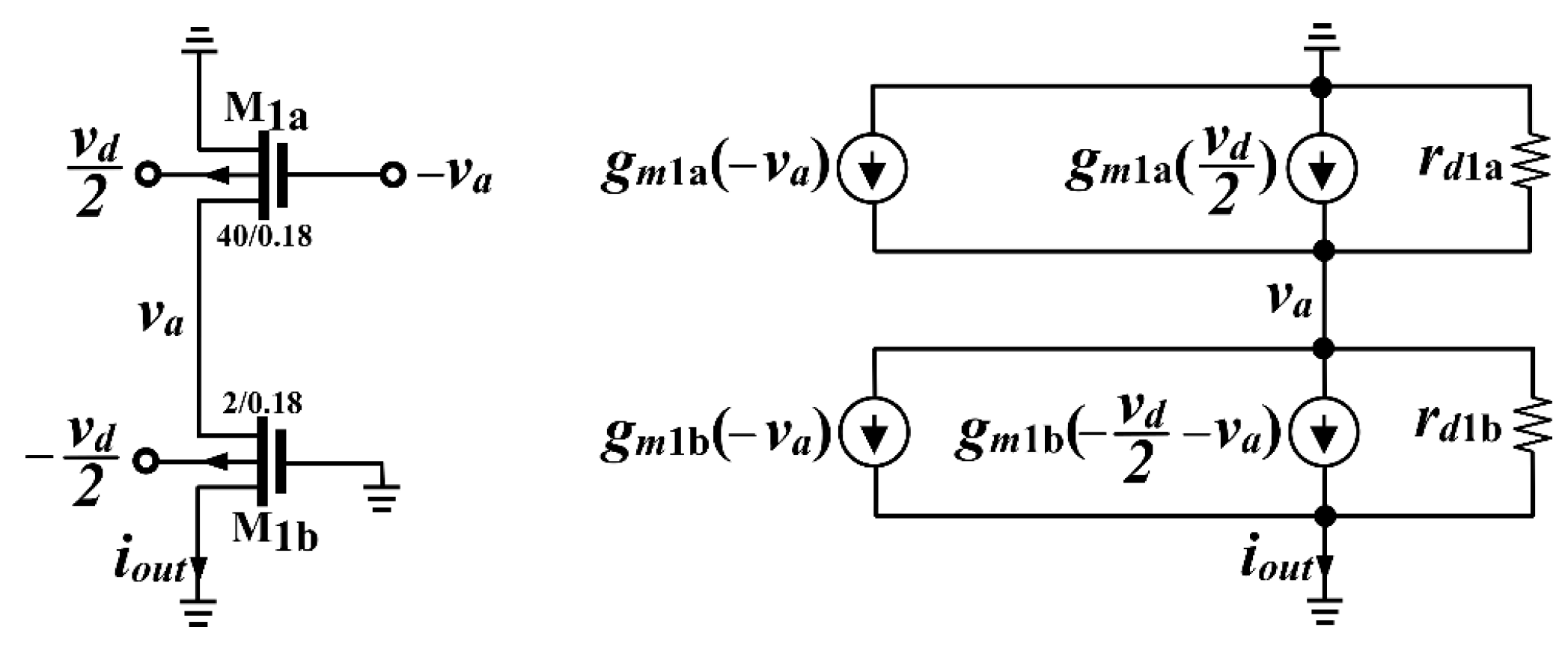

3.3. Tail-Less Class-AB Differential Stages

4. Comparison and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Huijsing, J.H.; Linebarger, D. Low-voltage operational amplifier with rail-to-rail input and output ranges. IEEE J. Solid-State Circuits 1985, 20, 1144–1150. [Google Scholar] [CrossRef]

- Zhang, F.; Holleman, J.; Otis, B.P. Design of Ultra-Low Power Biopotential Amplifiers for Biosignal Acquisition Applications. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 344–355. [Google Scholar] [CrossRef]

- Sharma, P.; Ali, M.S.A.; Misra, S. Ultra-Low Power CMOS Circuit Design for Wireless Sensor Networks. IEEE Sens. J. 2019, 19, 5117–5125. [Google Scholar]

- Jha, A.B.R.; Kumar, S.; Gupta, A. Ultra-Low Power CMOS Circuits for Medical Implantable Devices. IEEE Trans. Biomed. Eng. 2020, 67, 2285–2293. [Google Scholar]

- Reddy, M.V.M.; Srinivasan, M.L.; Reddy, L. Ultra-Low Power CMOS Energy Harvesting Systems for Remote Sensing. IEEE Trans. Ind. Electron. 2019, 66, 1989–1997. [Google Scholar]

- Lee, H.; Choi, S.; Kim, J. Low-Power CMOS Circuits for Battery-Powered Consumer Electronics. IEEE J. Solid-State Circuits 2020, 55, 3112–3123. [Google Scholar]

- Shih, C.P.; Huang, S.C.; Tseng, Y.C. Low-Power Design Techniques for Standby and Sleep Modes in CMOS Circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 332–343. [Google Scholar]

- Vittoz, E.; Fellrath, J. CMOS Analog Integrated Circuits Based on Weak Inversion Operations. IEEE J. Solid-State Circuits 1977, 12, 224–231. [Google Scholar] [CrossRef]

- Beloso-Legarra, J.; Grasso, A.D.; Lopez-Martin, A.J.; Palumbo, G.; Pennisi, S. Two-Stage OTA With All Subthreshold MOSFETs and Optimum GBW to DC-Current Ratio. IEEE Trans. Circuits Syst. II Express Br. 2022, 69, 3154–3158. [Google Scholar] [CrossRef]

- Grasso, A.D.; Marano, D.; Palumbo, G.; Pennisi, S. Design Methodology of Subthreshold Three-Stage CMOS OTAs Suitable for Ultra-Low-Power Low-Area and High Driving Capability. IEEE Trans. Circuits Syst. Regul. Pap. 2015, 62, 1453–1462. [Google Scholar] [CrossRef]

- Nauta, B. A CMOS Transconductance-C Filter Technique for Very High Frequencies. IEEE J. Solid-State Circuits 1992, 27, 142–153. [Google Scholar] [CrossRef]

- Figueiredo, M.; Santos-Tavares, R.; Santin, E.; Ferreira, J.; Evans, G.; Goes, J. A Two-Stage Fully Differential Inverter-Based Self-Biased CMOS Amplifier With High Efficiency. IEEE Trans. Circuits Syst. Regul. Pap. 2011, 58, 1591–1603. [Google Scholar] [CrossRef]

- Rodovalho, L.H.; Aiello, O.; Rodrigues, C.R. Ultra-Low-Voltage Inverter-Based Operational Transconductance Amplifiers with Voltage Gain Enhancement by Improved Composite Transistors. Electronics 2020, 9, 1410. [Google Scholar] [CrossRef]

- Centurelli, F.; Giustolisi, G.; Pennisi, S.; Scotti, G. A Biasing Approach to Design Ultra-Low-Power Standard-Cell-Based Analog Building Blocks for Nanometer SoCs. IEEE Access 2022, 10, 25892–25900. [Google Scholar] [CrossRef]

- Crovetti, P.S. A Digital-Based Analog Differential Circuit. IEEE Trans. Circuits Syst. Regul. Pap. 2013, 60, 3107–3116. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Fully Digital Rail-to-Rail OTA With Sub-1000-Μm2 Area, 250-mV Minimum Supply, and nW Power at 150-pF Load in 180 Nm. IEEE Solid-State Circuits Lett. 2020, 3, 474–477. [Google Scholar] [CrossRef]

- Toledo, P.; Crovetti, P.; Aiello, O.; Alioto, M. Design of Digital OTAs With Operation Down to 0.3 V and nW Power for Direct Harvesting. IEEE Trans. Circuits Syst. Regul. Pap. 2021, 68, 3693–3706. [Google Scholar] [CrossRef]

- Privitera, M.; Crovetti, P.S.; Grasso, A.D. A Novel Digital OTA Topology with 66-dB DC Gain and 12.3-kHz Bandwidth. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 3988–3992. [Google Scholar] [CrossRef]

- Ho, R.; Lau, C.; Hills, G.; Shulaker, M.M. Carbon Nanotube CMOS Analog Circuitry. IEEE Trans. Nanotechnol. 2019, 18, 845–848. [Google Scholar] [CrossRef]

- Khaleqi, M.; Jooq, Q.; Behbahani, F.; Moaiyeri, M.H. An ultra-efficient recycling folded cascode OTA based on GAA-CNTFET technology for MEMS/NEMS capacitive readout applications. AEU Int. J. Electron. Commun. 2021, 136, 153773. [Google Scholar] [CrossRef]

- Blalock, B.J.; Allen, P.E. A low-voltage bulk-driven MOSFET current mirror for CMOS technology. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS 1995), Seattle, WA, USA, 30 April–3 May 1995; Volume 3, pp. 1972–1975. [Google Scholar]

- Guzinski, A.; Bialko, M.; Matheau, J. Body driven differential amplifier for application in continuous-time active-C filter. In Proceedings of the European Conference on Circuit Theory and Design (ECCTD 1987), Paris, France, 1–4 September 1987; pp. 315–319. [Google Scholar]

- Jiang, Y.; Raut, R. A low-voltage low-power voltage-to-current transconductor using bulk-driven CMOS transistors. In Proceedings of the 5th International Conference on VLSI and CAD, Seoul, Republic of Korea, 13–15 October 1997; pp. 451–453. [Google Scholar]

- Blalock, B.J.; Allen, P.E.; Rincon-Mora, G.A. Designing 1-V opamps using standard digital CMOS technology. IEEE Trans. Circuits Syst. II 1998, 45, 769–780. [Google Scholar]

- Grasso, A.D.; Pennisi, S.; Venezia, C. A Survey of Ultra-Low-Power Amplifiers for Internet of Things Nodes. Electronics 2023, 12, 4361. [Google Scholar] [CrossRef]

- Narendra, S.; Antoniadis, D.; De, V. Impact of using adaptive body bias to compensate die-to-die Vt variation on within-die Vt variation. In Proceedings of the International Symposium on Low Power Electronics and Design, San Diego, CA, USA, 16–17 August 1999; pp. 229–232. [Google Scholar]

- Keshavarzi, A.; Ma, S.; Narendra, S.; Bloechel, B.; Mistry, K.; Ghani, T.; Borkar, S.; De, V. Effectiveness of reverse body bias for leakage control in scaled dual VT CMOS ICS. In Proceedings of the International Symposium on Low Power Electronics and Design, Huntington Beach, CA, USA, 6 August 2001; pp. 207–212. [Google Scholar]

- Tschanz, J.W.; Kao, J.T.; Narendra, S.G.; Nair, R.; Antoniadis, D.A.; Chandrakasan, A.P.; De, V. Adaptive body bias for reducing impacts of die-to-die and within-die parameter variations on microprocessor frequency and leakage. IEEE J. Solid-State Circuits 2002, 37, 1396–1402. [Google Scholar] [CrossRef]

- Neau, C.; Roy, K. Optimal body bias selection for leakage improvement and process compensation over different technology generations. In Proceedings of the ISLPED ‘03: 2003 International Symposium on Low Power Electronics and Design; Seoul, Korea, 25 August 2003, pp. 116–121.

- Roy, K.; Mukhopadhyay, S.; Mahmoodi-Meimand, H. Leakage current mechanisms and leakage reduction techniques in deep submicrometer CMOS circuits. Proc. IEEE 2003, 91, 305–327. [Google Scholar] [CrossRef]

- Nomura, M.; Ikenaga, Y.; Takeda, K.; Nakazawa, Y.; Aimoto, Y.; Hagihara, Y. Delay and power monitoring schemes for minimizing power consumption by means of supply and threshold voltage control in active and standby modes. IEEE J. Solid-State Circuits 2006, 41, 805–814. [Google Scholar] [CrossRef]

- Kim, K.K.; Kim, Y.B. A novel adaptive design methodology for minimum leakage power considering PVT variations on nanoscale VLSI systems. IEEE Trans. VLSI Syst. 2009, 17, 517–528. [Google Scholar] [CrossRef]

- Jeon, H.J.; Kim, Y.B.; Choi, M. Standby leakage power reduction technique for nanoscale CMOS VLSI systems. IEEE Trans. Instrum. Meas. 2010, 59, 1127–1133. [Google Scholar] [CrossRef]

- Carrillo, J.M.; Duque-Carrillo, J.F.; Torelli, G. Design considerations on CMOS bulk-driven differential input stages. In Proceedings of the 2012 International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD), Seville, Spain, 19–21 September 2012; pp. 85–88. [Google Scholar]

- Monsurró, P.; Pennisi, S.; Scotti, G.; Trifiletti, A. Exploiting the Body of MOS Devices for High Performance Analog Design. IEEE Circuits Syst. Mag. 2011, 11, 8–23. [Google Scholar] [CrossRef]

- Hollis, T.M.; Comer, D.J.; Comer, D.T. Optimization of MOS Amplifier Performance through Channel Length and Inversion Level Selection. IEEE Trans. Circuits Syst. II Express Briefs 2005, 52, 545–549. [Google Scholar] [CrossRef]

- Valero Bernal, M.R.; Celma, S.; Medrano, N.; Calvo, B. An Ultralow-Power Low-Voltage Class-AB Fully Differential OpAmp for Long-Life Autonomous Portable Equipment. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 643–647. [Google Scholar] [CrossRef]

- Chatterjee, S.; Tsividis, Y.; Kinget, P. 0.5-V Analog Circuit Techniques and Their Application in OTA and Filter Design. IEEE J. Solid-State Circuits 2005, 40, 2373–2387. [Google Scholar] [CrossRef]

- Magnelli, L.; Amoroso, F.A.; Crupi, F.; Cappuccino, G.; Iannaccone, G. Design of a 75-nW, 0.5-V Subthreshold Complementary Metal–Oxide–Semiconductor Operational Amplifier. Int. J. Circuit Theory Appl. 2014, 42, 967–977. [Google Scholar] [CrossRef]

- Qin, Z.; Tanaka, A.; Takaya, N.; Yoshizawa, H. 0.5-V 70-nW Rail-to-Rail Operational Amplifier Using a Cross-Coupled Output Stage. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 1009–1013. [Google Scholar] [CrossRef]

- Monsurrò, P.; Pennisi, S.; Scotti, G.; Trifiletti, A. 0.9-V CMOS Cascode Amplifier with Body-driven Gain Boosting. Int. J. Circ. Theor. Appl. 2009, 37, 193–202. [Google Scholar] [CrossRef]

- Mohieldin, A.N.; Sanchez-Sinencio, E.; Silva-Martinez, J. A fully balanced pseudo-differential OTA with common-mode feedforward and inherent common-mode feedback detector. IEEE J. Solid-State Circuits 2003, 38, 663–668. [Google Scholar] [CrossRef]

- Mohieldin, A.N.; Sanchez-Sinencio, E.; Silva-Martinez, J. Nonlinear effects in pseudo differential OTAs with CMFB. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 2003, 50, 762–770. [Google Scholar] [CrossRef]

- Bahmani, F.; Sanchez-Sinencio, E. A highly linear pseudo-differential transconductance [CMOS OTA]. In Proceedings of the 30th European Solid-State Circuits Conference, Leuven, Belgium, 23 September 2004; pp. 111–114. [Google Scholar] [CrossRef]

- Aamir, S.A.; Wikner, J.J. A 1.2-V pseudo-differential OTA with common-mode feedforward in 65-NM CMOS. In Proceedings of the 2010 17th IEEE International Conference on Electronics, Circuits and Systems, Athens, Greece, 12–15 December 2010; pp. 29–32. [Google Scholar]

- Tao, C.; Lei, L.; Chen, Z.; Huang, Y.; Hong, Z. A 29.5 dBm OOB IIP3 TIA Based on a Two-Stage Pseudo-Differential OTA With R-C Compensation and Cascode Negative Resistance. IEEE Access 2023, 11, 24343–24352. [Google Scholar] [CrossRef]

- Ferreira, L.H.C.; Pimenta, T.C.; Moreno, R.L. An Ultra-Low-Voltage Ultra-Low-Power CMOS Miller OTA With Rail-to-Rail Input/Output Swing. IEEE Trans. Circuits Syst. II Express Br. 2007, 54, 843–847. [Google Scholar] [CrossRef]

- Carrillo, J.M.; Torelli, G.; Duque-Carrillo, J.F. Transconductance enhancement in bulk-driven input stages and its applications. Analog Integr Circ Sig Process 2011, 68, 207–217. [Google Scholar] [CrossRef]

- Ferreira, L.H.C.; Sonkusale, S.R. A 60-dB Gain OTA Operating at 0.25-V Power Supply in 130-nm Digital CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1609–1617. [Google Scholar] [CrossRef]

- Akbari, M.; Hussein, S.M.; Hashim, Y.; Tang, K.T. An Enhanced Input Differential Pair for Low-Voltage Bulk-Driven Amplifiers. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2021, 29, 1601–1611. [Google Scholar] [CrossRef]

- Carvajal, R.G.; Ramírez-Angulo, J.; Torralba, A.; Galán, J.A.G. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Sala, R.D.; Centurelli, F.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A 0.3V Rail-to-Rail Three-Stage OTA With High DC Gain and Improved Robustness to PVT Variations. IEEE Access 2023, 11, 19635–19644. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Pennisi, S. 0.4-V, 81.3-nA bulk-driven single-stage CMOS OTA with enhanced transconductance. Electronics 2022, 11, 2704. [Google Scholar] [CrossRef]

- Kulej, T.; Khateb, F. A Compact 0.3-V Class AB Bulk-Driven OTA. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2020, 28, 224–232. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.D.; Pennisi, S.; Susinni, G. A 0.3-V 8.5-μA Bulk-Driven OTA. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2023, 31, 1444–1448. [Google Scholar] [CrossRef]

- Akbari, M.; Hussein, S.M.; Hashim, Y.; Tang, K.T. 0.4-V Tail-Less Quasi-Two-Stage OTA Using a Novel Self-Biasing Transconductance Cell. IEEE Trans. Circuits Syst. I Regul. Pap. 2022, 69, 2805–2818. [Google Scholar] [CrossRef]

- Centurelli, F.; Sala, R.D.; Monsurro, P.; Tommasino, P.; Trifiletti, A. An ultra-low-voltage class-AB OTA exploiting local CMFB and body-to-gate interface. AEU-Int. J. Electron. Commun. 2022, 145, 154081. [Google Scholar] [CrossRef]

- Centurelli, F.; Sala, R.D.; Monsurrò, P.; Scotti, G.; Trifiletti, A. A 0.3 V rail-to-rail ultra-low-power OTA with improved bandwidth and slew rate. J. Low Power Electron. Appl. 2021, 11, 19. [Google Scholar] [CrossRef]

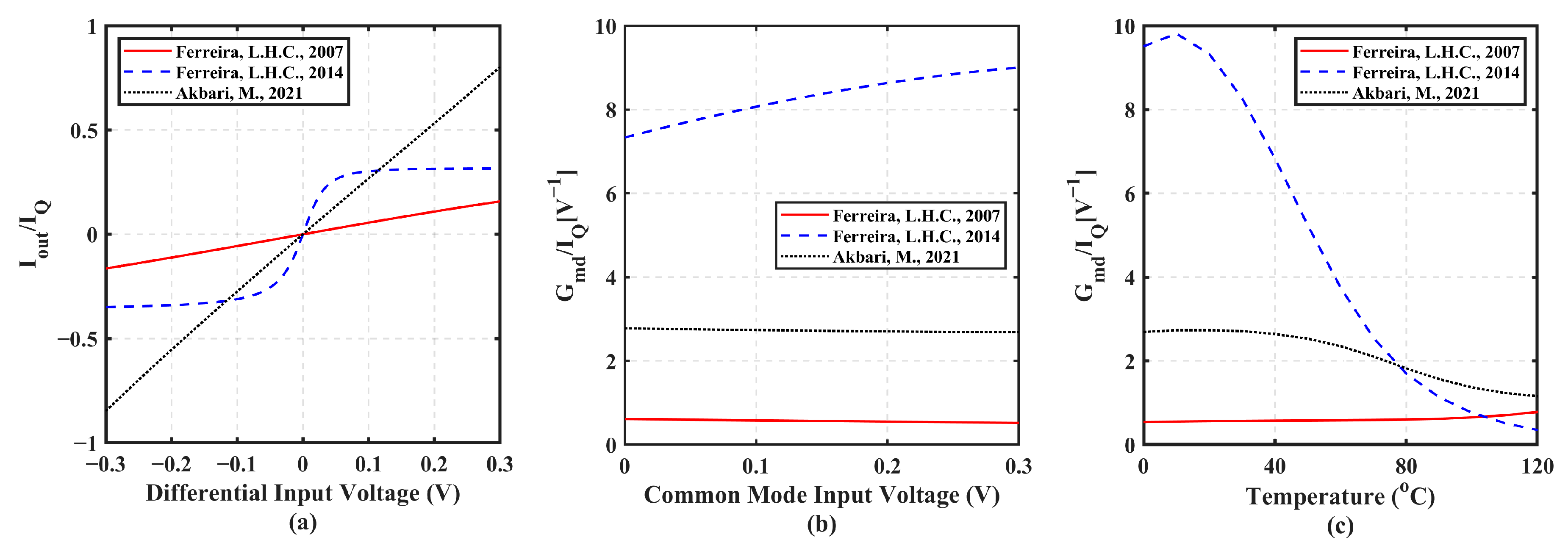

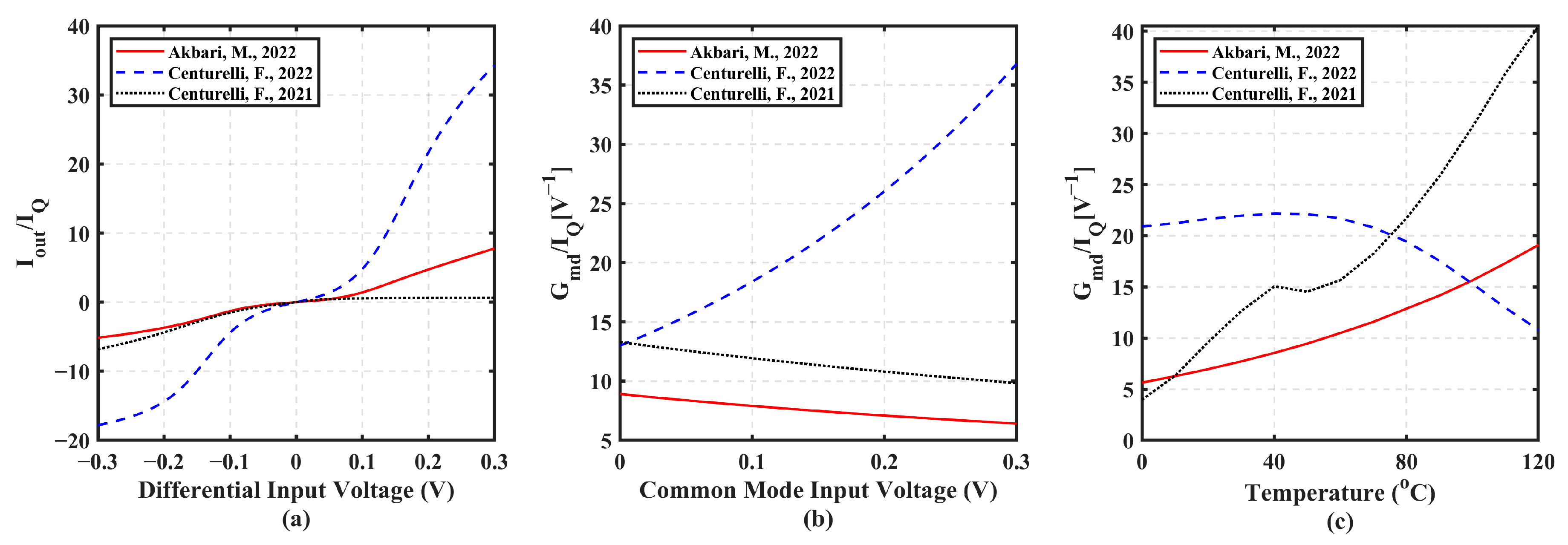

| Ref. | Differential Transconductance, Gmd | W/L of Input Transistors × Mult., Type | Standby Current, IQ [nA] | Class A/AB, | Gmd/IQ [V−1] | |

|---|---|---|---|---|---|---|

| Equation | Value [nA/V] @VCM = VDD/2 Simul. (Calc.) | Tailed(T)/ Tail-Less(TL) | ||||

| [47] | 44.5 (52.5) | 1.9/0.18 × 2, pMOS | 79 | A, T | 0.57 | |

| [49] | 800 (1100) | 40/0.18 × 2, pMOS and 2/0.18 × 2, pMOS | 93 | A, T | 8.6 | |

| [50] | , where k, m and p are current ratios in Figure 2c | 394 (356) | 60/2 × 4, pMOS | 145 | A, T | 2.7 |

| [52] | 74.6 (74.6) | 3/1 × 2, nMOS and 9/1 × 2, pMOS | 40 | A, TL | 1.9 | |

| [53] | 2760 (2927) | 7.5/0.18 × 2, pMOS | 386 | A, TL | 7.2 | |

| [54] | 123 (132) | 9/0.18 × 4, pMOS | 82 | A, TL | 1.5 | |

| [55] | 2420 (2500) | 8/0.18 × 2, nMOS | 1410 | A, TL | 1.7 | |

| [56] | 7550 (7700) | 70/3 × 4, pMOS | 1000 | AB, TL | 7.5 | |

| [57] | 4180 (4240) | 0.6/3 × 2, nMOS | 191 | AB, TL | 21.9 | |

| [58] | 2710 (3100) | 7/2 × 4, pMOS | 231 | AB, TL | 11.7 | |

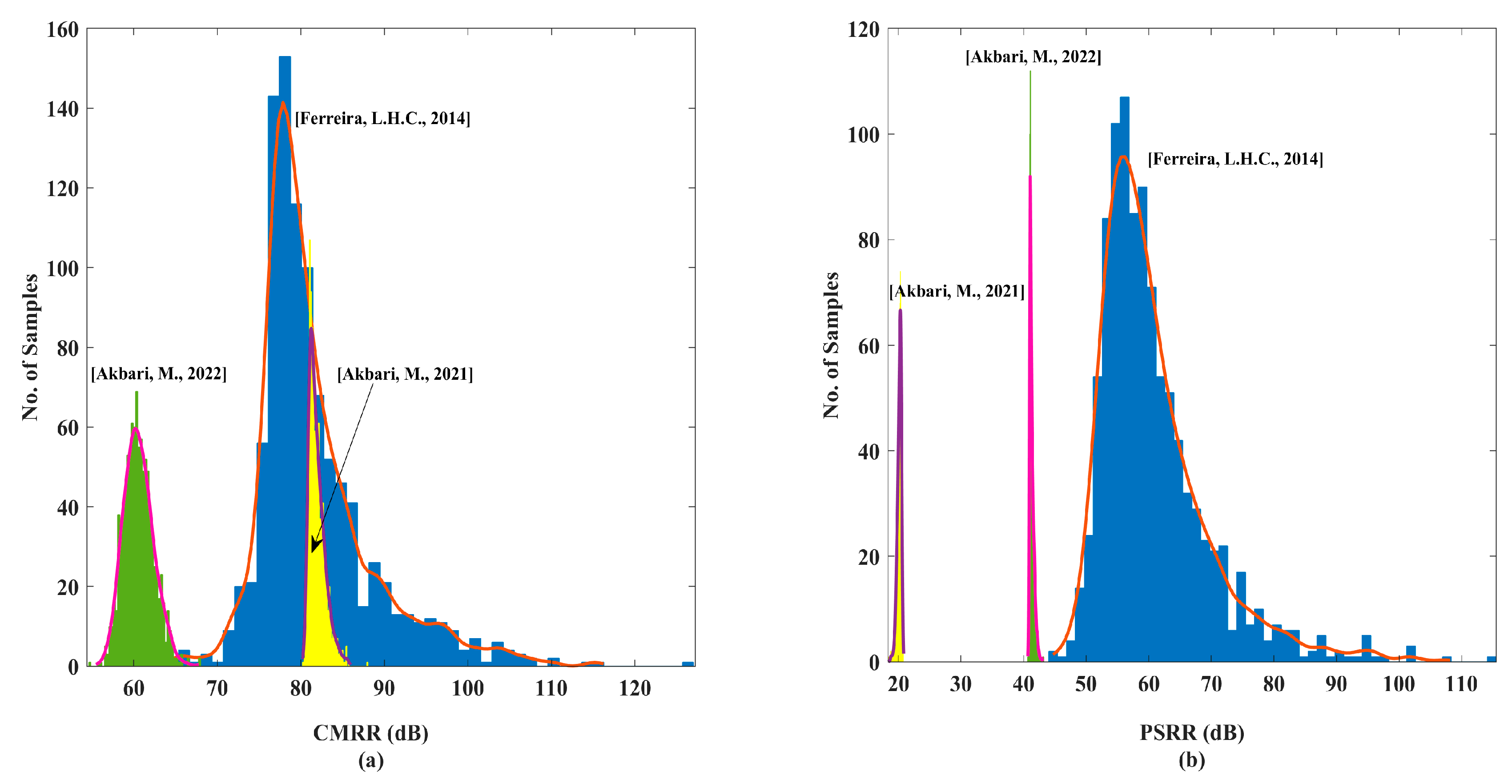

| Class A/AB Tailed(T), Tail-Less(TL) | Ref.# | Gmcm [nA/V] @VCM = VDD/2 | Gmdd [nA/V] @VCM = VDD/2 | CMRR [dB] Mean/σ | PSRR [dB] Mean/σ |

|---|---|---|---|---|---|

| A,T | [47] | 0.0545 | 1.2 | 59.3/6.6 | 32.4/8.5 |

| [49] | 0.067 | 0.78 | 81.6/7.1 | 60.8/8.9 | |

| [50] | 0.0613 | 37.9 | 81.95/0.9 | 20.15/0.3 | |

| A,TL | [52] | 3.78 * | 22.8 | 25.9 */0.5 | 10.3/0.17 |

| [53] | 40.3 | 438 | 37.5/5.4 | 15.7/0.58 | |

| [54] | 0.345 | 3.65 | 51.5/3.5 | 30.9/1.1 | |

| [55] | 49.7 | 50 | 34.96/6.4 | 33.8/1.3 | |

| AB,TL | [56] | 7.07 | 65.3 | 60.6/1.8 | 41.3/0.35 |

| [57] | 17.5 | 17.2 | 49.4/8.3 | 46.95/9.1 | |

| [58] | 13.6 | 46.3 | 42.4/4.1 | 29.7/5.8 |

| Ref.# | CMRR [dB] | PSRR [dB] | ||||||

|---|---|---|---|---|---|---|---|---|

| FF | FS | SF | SS | FF | FS | SF | SS | |

| [47] | 42.63 | 59.09 | 51.09 | 48.22 | 22.32 | 22.61 | 21.74 | 19.62 |

| [49] | 59.39 | 69.93 | 69.84 | 76.19 | 44.45 | 46.79 | 51.26 | 52.06 |

| [50] | 82.41 | 83.04 | 82.32 | 86.56 | 18.19 | 20.47 | 19.51 | 20.96 |

| [52] | 23.05 | 25.49 | 25.44 | 26.95 | 9.53 | 10.57 | 10 | 10.74 |

| [53] | 52.8 | 29.39 | 75.46 | 30.11 | 11.92 | 14.19 | 15.73 | 16.55 |

| [54] | 67.11 | 65.63 | 44.93 | 45.45 | 31.31 | 31.96 | 33.38 | 34.94 |

| [55] | 46.43 | 46.39 | 25.85 | 25.62 | 38.01 | 38.89 | 35.8 | 30.76 |

| [56] | 64.97 | 66.07 | 55.83 | 56.54 | 42.45 | 42.33 | 41.01 | 41.45 |

| [57] | 41.51 | 35.86 | 43.75 | 64.81 | 36.23 | 32.68 | 33.8 | 37.07 |

| [58] | 27.43 | 33.98 | 34.41 | 32.65 | 12.07 | 19.78 | 17.81 | 15.05 |

| Ref.# | FoM [Hz/V4] | |||||

|---|---|---|---|---|---|---|

| @ 10 Hz | @ 100 Hz | (White) @ 10 kHz | @ 10 Hz | @ 100 Hz | (White) @ 10 kHz | |

| [47] | 112 | 33 | 5.8 | 1.50 × 10−4 | 1.73 × 10−3 | 0.06 |

| [49] | 42.7 | 12.2 | 1.9 | 1.18 × 10−2 | 1.45 × 10−1 | 5.98 |

| [50] | 14 | 4.9 | 2.7 | 4.62 × 10−2 | 3.77 × 10−1 | 1.24 |

| [52] | 9 | 3 | 1.4 | 7.67 × 10−2 | 6.91 × 10−1 | 3.17 |

| [53] | 45.8 | 13.3 | 2.8 | 1.14 × 10−2 | 1.35 × 10−1 | 3.04 |

| [54] | 31.4 | 9.3 | 2.1 | 5.08 × 10−3 | 5.79 × 10−2 | 1.14 |

| [55] | 23 | 6.9 | 0.9 | 1.08 × 10−2 | 1.20 × 10−1 | 7.06 |

| [56] | 3 | 1.3 | 0.9 | 2.80 | 1.49 × 101 | 31.07 |

| [57] | 28.5 | 9.3 | 5 | 8.99 × 10−2 | 8.44 × 10−1 | 2.92 |

| [58] | 10.3 | 4 | 2.9 | 3.69 × 10−1 | 2.44 | 4.65 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shah, M.O.; Ballo, A.; Pennisi, S. Bulk-Driven CMOS Differential Stages for Ultra-Low-Voltage Ultra-Low-Power Operational Transconductance Amplifiers: A Comparative Analysis. Electronics 2025, 14, 2085. https://doi.org/10.3390/electronics14102085

Shah MO, Ballo A, Pennisi S. Bulk-Driven CMOS Differential Stages for Ultra-Low-Voltage Ultra-Low-Power Operational Transconductance Amplifiers: A Comparative Analysis. Electronics. 2025; 14(10):2085. https://doi.org/10.3390/electronics14102085

Chicago/Turabian StyleShah, Muhammad Omer, Andrea Ballo, and Salvatore Pennisi. 2025. "Bulk-Driven CMOS Differential Stages for Ultra-Low-Voltage Ultra-Low-Power Operational Transconductance Amplifiers: A Comparative Analysis" Electronics 14, no. 10: 2085. https://doi.org/10.3390/electronics14102085

APA StyleShah, M. O., Ballo, A., & Pennisi, S. (2025). Bulk-Driven CMOS Differential Stages for Ultra-Low-Voltage Ultra-Low-Power Operational Transconductance Amplifiers: A Comparative Analysis. Electronics, 14(10), 2085. https://doi.org/10.3390/electronics14102085