A 50 Gb/s 0.42 pJ/b Non-Return-to-Zero Transmitter for Extra-Short-Reach SerDes

Abstract

1. Introduction

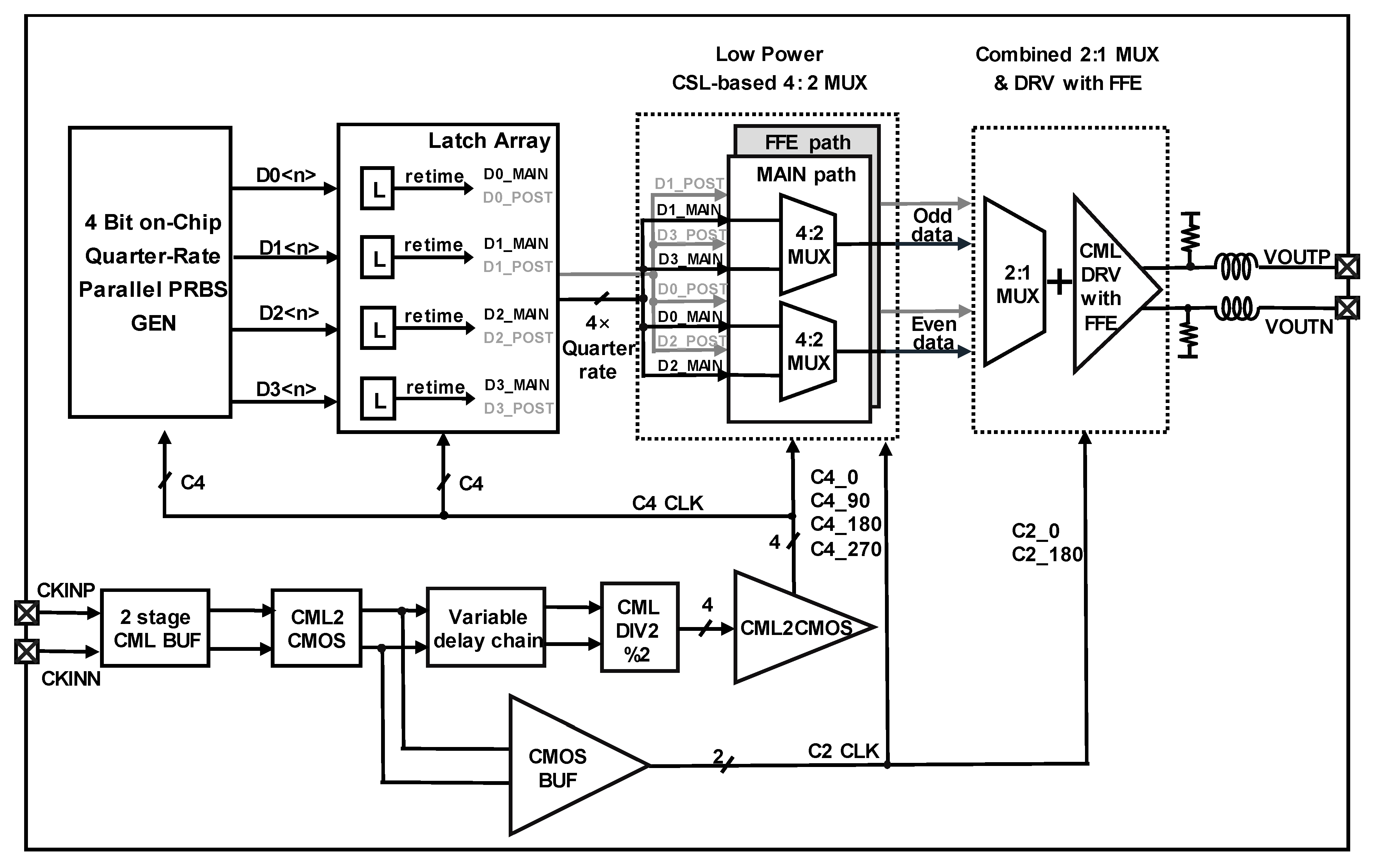

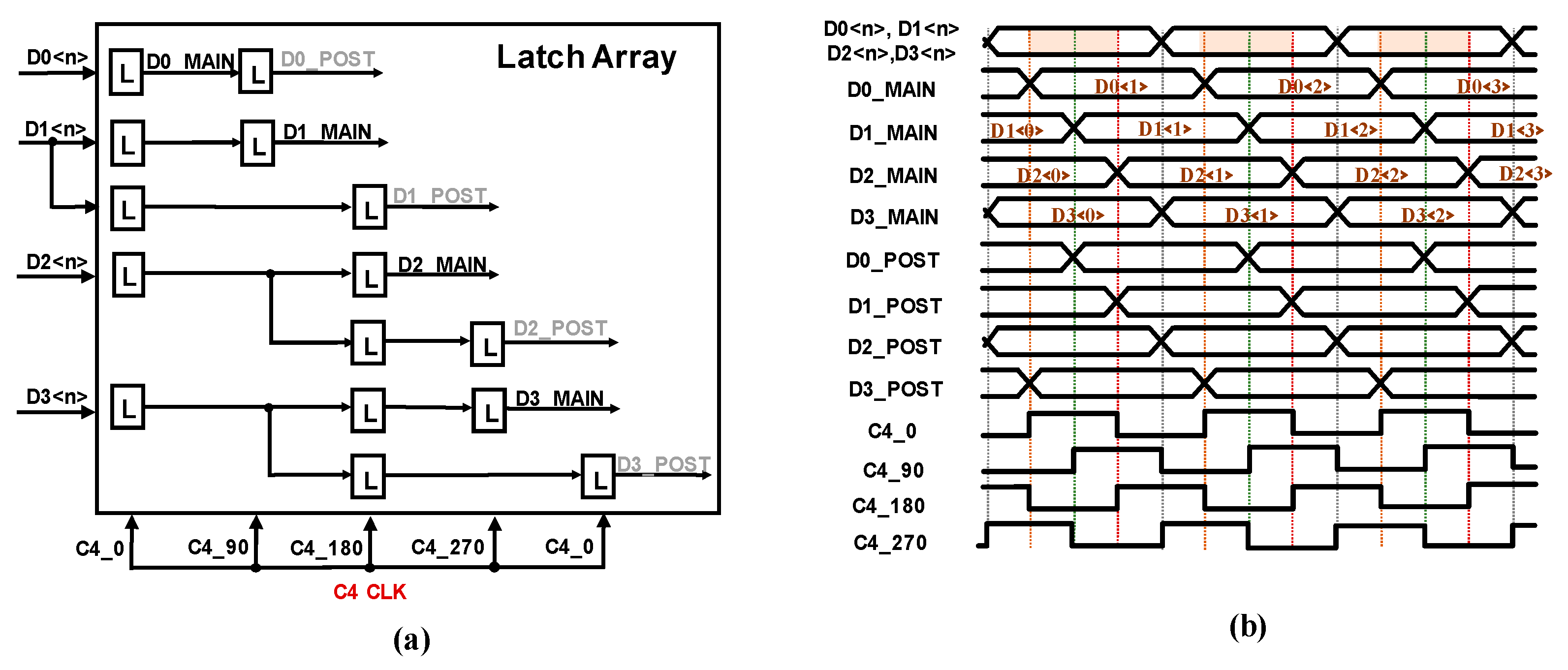

2. Architecture of Transmitter

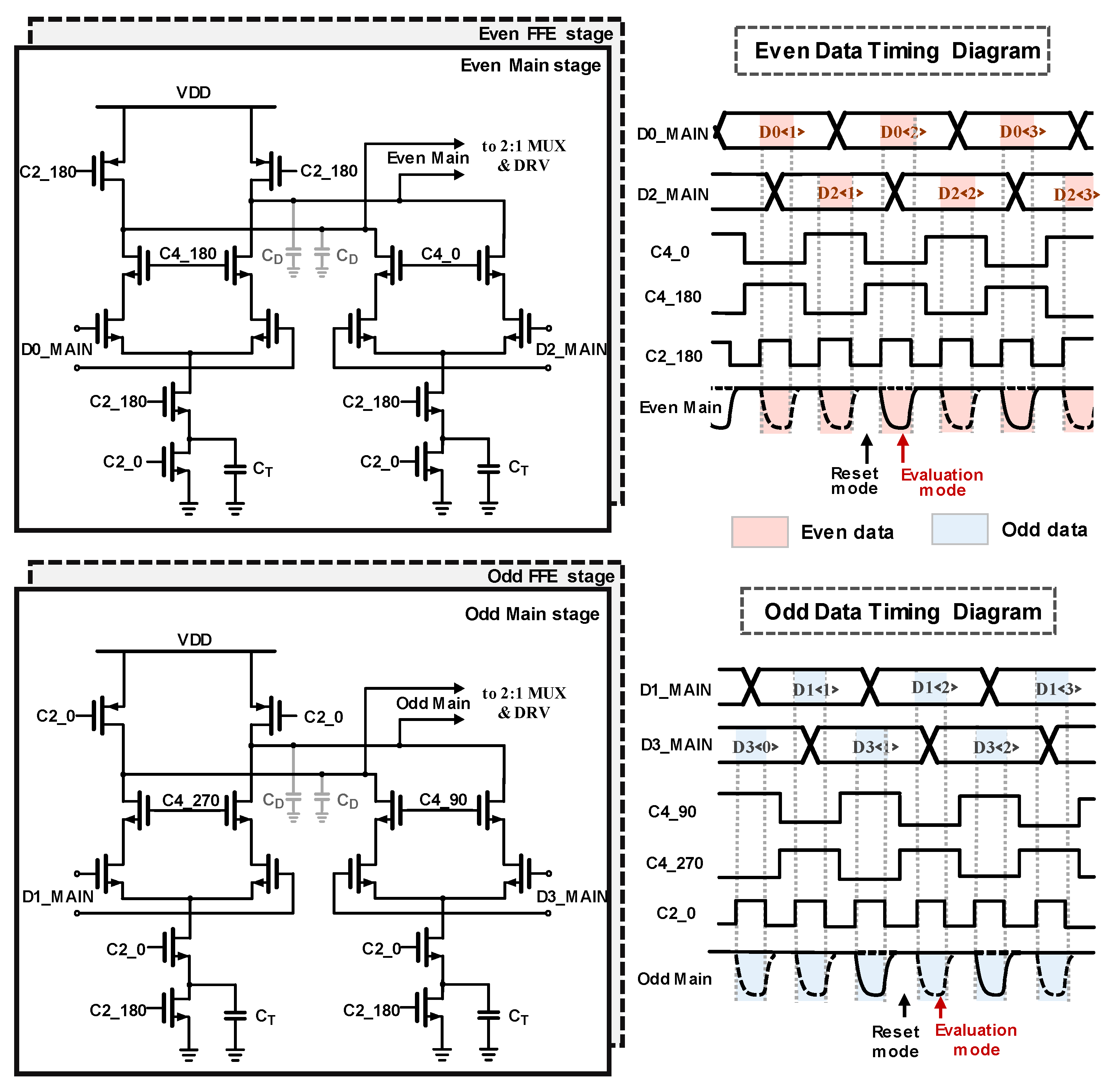

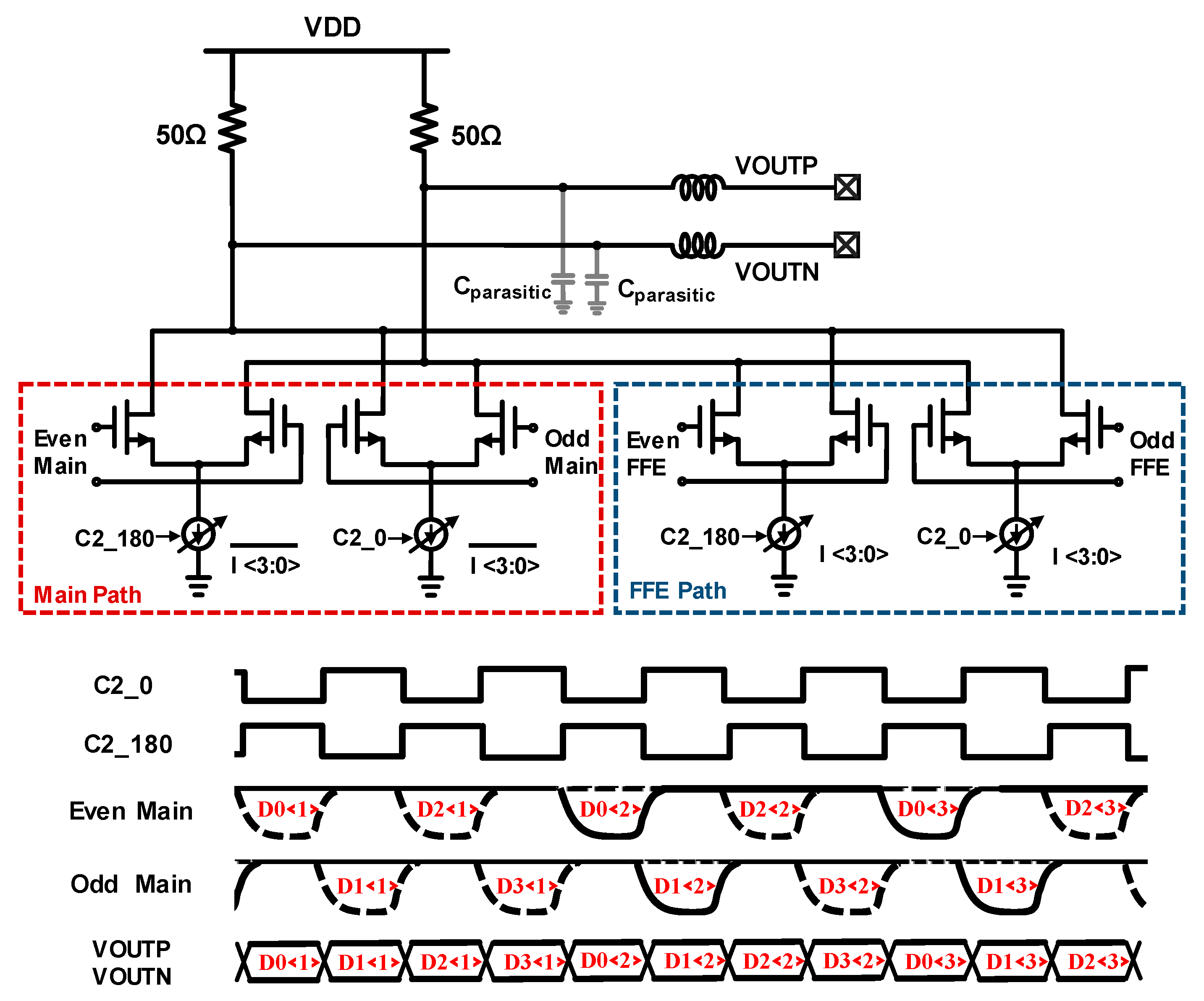

3. Circuit Implementation

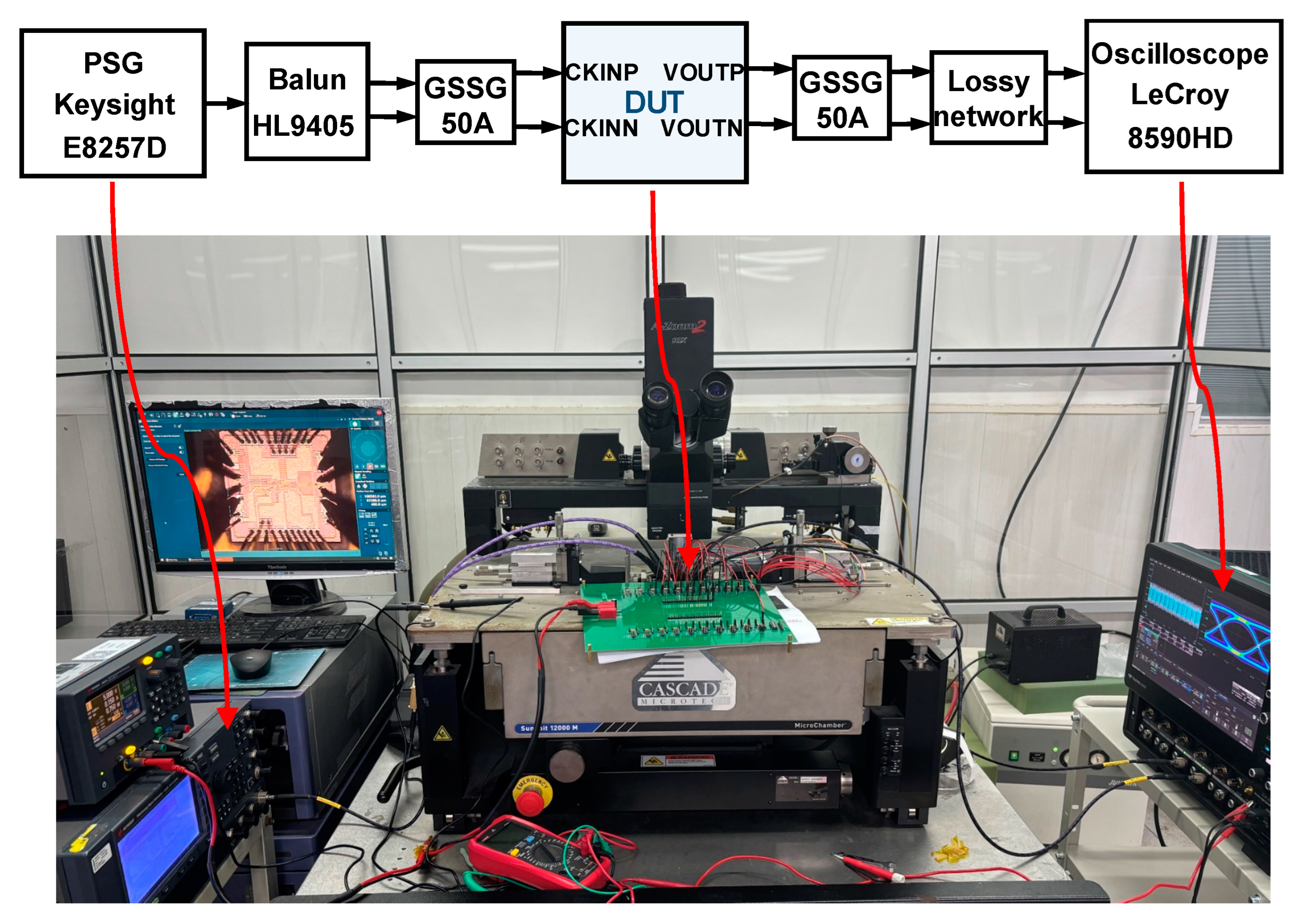

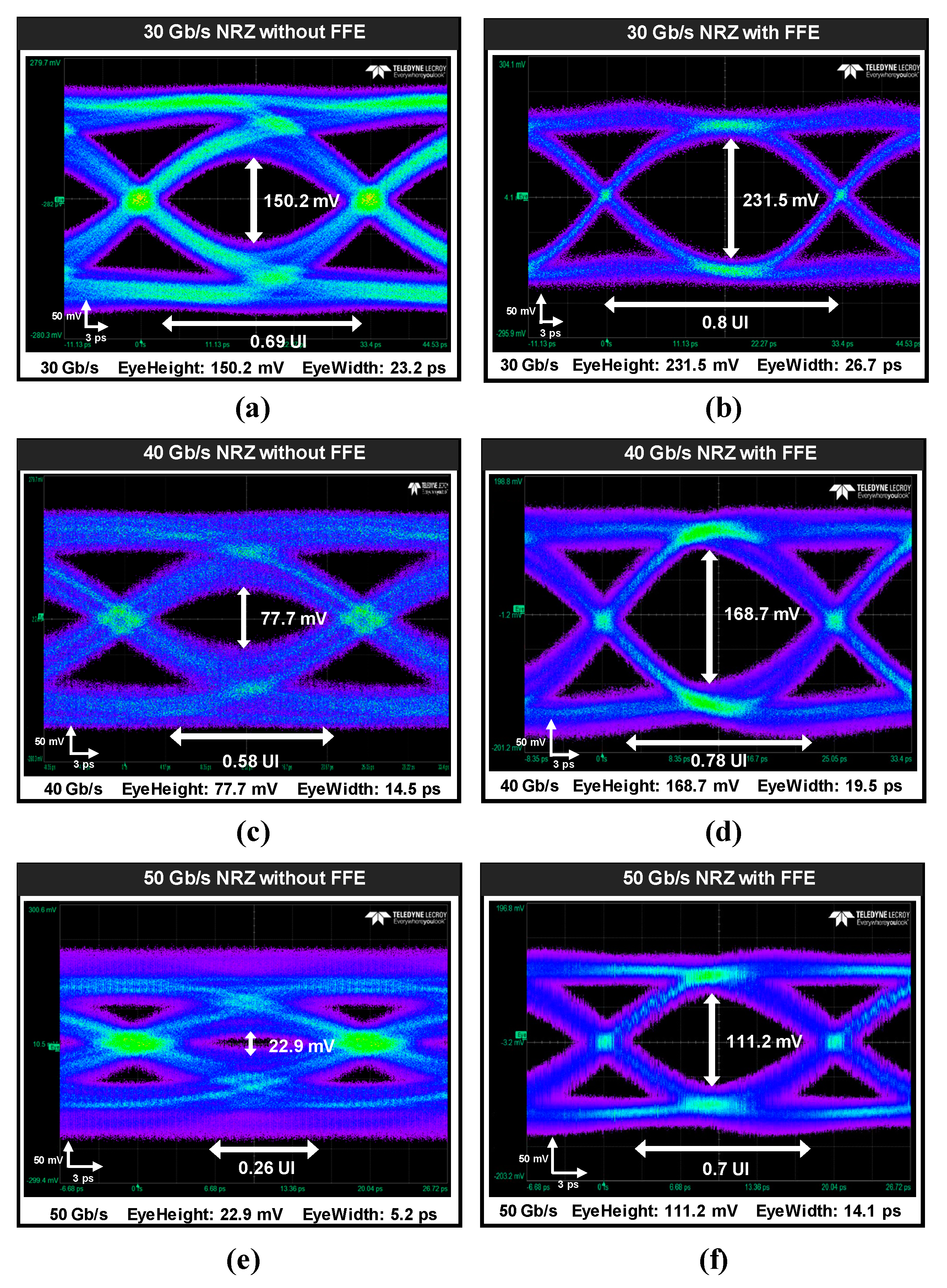

4. Measurement Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Seong, K.; Oh, W.; Lee, H.; Bae, G.; Suh, Y.; Lee, H.; Kim, J.; Kim, E.; Kang, Y.; Mo, G.; et al. 13.10 A 4 nm 48 Gb/s/wire Single-Ended NRZ Parallel Transceiver with Offset-Calibration and Equalization Schemes for Next-Generation Memory Interfaces and Chiplets. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; pp. 250–252. [Google Scholar]

- Liu, Q.; Wang, H.; Lyu, F.; Zhang, G.; Lyu, D. A low-latency, low-jitter retimer circuit for PCIe 6.0. Electronics 2023, 12, 3102. [Google Scholar] [CrossRef]

- Suhani S.H., A.A.; Prasad S., N.; Reddy, K.S.S. A 20 Gb/s Latency Optimized SerDes Transmitter for Data Centre Applications. In Proceedings of the IEEE International Conference on Electronics, Computing and Communication Technologies (CONECCT), Bangalore, India, 2–4 July 2020; pp. 1–4. [Google Scholar]

- Wu, J.Y.; Chen, C.H.; Lee, C.H.; Liu, C.S.; Yu, D.C.H. SoIS-An Ultra Large Size Integrated Substrate Technology Platform for HPC Applications. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; pp. 28–33. [Google Scholar]

- Seong, K.; Park, D.; Bae, G.; Lee, H.; Suh, Y.; Oh, W.; Lee, H.; Kim, J.; Lee, T.; Mo, G.; et al. A 4 nm 32 Gb/s 8Tb/s/mm Die-to-Die Chiplet Using NRZ Single-Ended Transceiver with Equalization Schemes And Training Techniques. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023; pp. 114–116. [Google Scholar]

- Park, J.H.; Lee, H.; Cho, H.; Lee, S.; Lee, K.H.; Ko, H.G.; Jeong, D.K. A 32 Gb/s/pin 0.51 pJ/b Single-Ended Resistor-less Impedance-Matched Transmitter with a T-Coil-Based Edge-Boosting Equalizer in 40 nm CMOS. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023; pp. 410–412. [Google Scholar]

- Hsu, Y.Y.; Kuo, P.C.; Chuang, C.L.; Chang, P.H.; Shen, H.H.; Chiang, C.F. A 7 nm 0.46 pJ/bit 20 Gbps with BER 1E-25 Die-to-Die Link Using Minimum Intrinsic Auto Alignment and Noise-Immunity Encode. In Proceedings of the 2021 Symposium on VLSI Circuits, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [Google Scholar]

- Lee, J.; Chiang, P.C.; Peng, P.J.; Chen, L.Y.; Weng, C.C. Design of 56 Gb/s NRZ and PAM4 SerDes Transceivers in CMOS Technologies. IEEE J.-Solid-State Circuits 2015, 50, 2061–2073. [Google Scholar] [CrossRef]

- Ye, B.; Wu, G.; Gai, W.; Sheng, K.; He, Y. A Five-Tap Delay-Line-Based Feed-Forward-Equalizer for 200-Gb/s Wireline Receiver in 28-nm CMOS. IEEE J.-Solid-State Circuits 2024, 59, 19–28. [Google Scholar] [CrossRef]

- Hafez, A.A.; Chen, M.S.; Yang, C.K.K. A 32–48 Gb/s Serializing Transmitter Using Multiphase Serialization in 65 nm CMOS Technology. IEEE J.-Solid-State Circuits 2015, 50, 763–775. [Google Scholar] [CrossRef]

- Zheng, X.; Zhang, C.; Lv, F.; Zhao, F.; Yuan, S.; Yue, S.; Wang, Z.; Li, F.; Wang, Z.; Jiang, H. A 40-Gb/s Quarter-Rate SerDes Transmitter and Receiver Chipset in 65-nm CMOS. IEEE J.-Solid-State Circuits 2017, 52, 2963–2978. [Google Scholar] [CrossRef]

- Sheng, K.; Gai, W.; Feng, Z.; Niu, H.; Ye, B.; Zhou, H. 6.7 A 128 Gb/s PAM-4 Transmitter with Programmable-Width Pulse Generator and Pattern-Dependent Pre-Emphasis in 28 nm CMOS. In Proceedings of the 2024 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023; pp. 120–122. [Google Scholar]

- Jung, J.W.; Razavi, B. A 25-Gb/s 5-mW CMOS CDR/Deserializer. IEEE J.-Solid-State Circuits 2013, 48, 684–697. [Google Scholar] [CrossRef]

- Song, E.; Han, J.; Seo, H.; Kim, H.; Im, H.; Han, J. A 35-Gb/s PAM-4 Transmitter with 7B4Q Full-Transition Avoidance and Area-Efficient Gm-Boosting Techniques. IEEE Trans. Circuits Syst. II Exp. Briefs 2024, 71, 46–50. [Google Scholar] [CrossRef]

- Gu, Y.; Chen, J.; Li, X.; Chen, Y.; Wu, J. A 32 Gb/s NRZ Wireline Transmitter with CMFB-Based CML Driver in 28 nm CMOS Technology. In Proceedings of the 2021 IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Lansing, MI, USA, 9–11 August 2021; pp. 14–17. [Google Scholar]

- Shekhar, S.; Walling, J.S.; Allstot, D.J. Bandwidth Extension Techniques for CMOS Amplifiers. IEEE J.-Solid-State Circuits 2006, 41, 2424–2439. [Google Scholar] [CrossRef]

- Toprak-Deniz, Z.; Proesel, J.E.; Bulzacchelli, J.F.; Ainspan, H.A.; Dickson, T.O.; Beakes, M.P. A 128-Gb/s 1.3-pJ/b PAM-4 Transmitter with Reconfigurable 3-Tap FFE in 14-nm CMOS. IEEE J.-Solid-State Circuits 2020, 55, 19–26. [Google Scholar] [CrossRef]

- Celik, F.; Akkaya, A.; Tajalli, A.; Leblebici, Y. A 32-Gb/s PAM-4 SST Transmitter with Four-Tap FFE Using High-Impedance Driver in 28-nm FDSOI. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2021, 29, 1132–1140. [Google Scholar] [CrossRef]

- Wu, W.; Wu, H.; Zhong, L.; Cheng, X.; Luo, X.; Xu, D.; Wang, C.; Li, Z.; Pan, Q. A 64 Gb/s/pin Single-Ended PAM-4 Transmitter with a Merged Preemphasis Capacitive-Peaking Crosstalk Cancellation Scheme for Memory Interfaces in 28-nm CMOS. IEEE J.-Solid-State Circuits 2025, 60, 205–216. [Google Scholar] [CrossRef]

| [11] | [12] | [14] | [17] | [18] | [19] | This Work | ||

|---|---|---|---|---|---|---|---|---|

| Process [nm] | 65 | 28 | 28 | 14 | 28 | 28 | 28 | |

| Data rate [Gb/s] | 40 | 128 | 35 | 64 | 32 | 32 | 64 | 50 |

| Supply [V] | 1.2 | N/A | 1.25 | 0.95 | 1 | N/A | 0.9 | |

| Signaling | NRZ | PAM4 | PAM4 | NRZ | PAM4 | NRZ | PAM4 | NRZ |

| Driver Type | CML | CML | SST | CML | SST | SST | CML | |

| Equalization | 4-tap FFE | 4-tap FFE | 2-tap FFE | 3-tap FFE | 4-tap FFE | 3-tap FFE | 2-tap FFE | |

| IL@Nyquist Frequency | 6 dB | 4 dB | 5.2 dB | 6 dB | N/A | 11 dB | 10 dB | |

| Test PRBS length | 7 | N/A | 7 | 31 | N/A | N/A | 7 | |

| Eye Height [mV] | 180 | 44 | 101 | N/A | 38 | 180 | 36 | 111.2 |

| Eye Width [UI] | 0.68 | 0.2 | 0.68 | N/A | 0.16 | 0.6 | 0.36 | 0.7 |

| Power * [mW] | 74 | 115 | 166.85 | 139 | 37.7 | 56 | 21 | |

| Energy Efficiency * [pJ/bit] | 1.85 | 0.9 | 4.76 | 2.1 | 1.178 | 0.875 | 0.42 | |

| Area [mm2] | 0.6 | 0.137 | 0.18 | 0.048 | 0.08 | 0.085 | 0.032 | |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sun, L.; Jin, Z.; Liu, Y.; Yu, X.; Ni, R. A 50 Gb/s 0.42 pJ/b Non-Return-to-Zero Transmitter for Extra-Short-Reach SerDes. Electronics 2025, 14, 1955. https://doi.org/10.3390/electronics14101955

Sun L, Jin Z, Liu Y, Yu X, Ni R. A 50 Gb/s 0.42 pJ/b Non-Return-to-Zero Transmitter for Extra-Short-Reach SerDes. Electronics. 2025; 14(10):1955. https://doi.org/10.3390/electronics14101955

Chicago/Turabian StyleSun, Lili, Zhongxu Jin, Yanchao Liu, Xiaohua Yu, and Ronghua Ni. 2025. "A 50 Gb/s 0.42 pJ/b Non-Return-to-Zero Transmitter for Extra-Short-Reach SerDes" Electronics 14, no. 10: 1955. https://doi.org/10.3390/electronics14101955

APA StyleSun, L., Jin, Z., Liu, Y., Yu, X., & Ni, R. (2025). A 50 Gb/s 0.42 pJ/b Non-Return-to-Zero Transmitter for Extra-Short-Reach SerDes. Electronics, 14(10), 1955. https://doi.org/10.3390/electronics14101955