A Scalable, Multi-Core, Multi-Function, Integrated CMOS/Memristor Sensor Interface for Neural Sensing Applications

Abstract

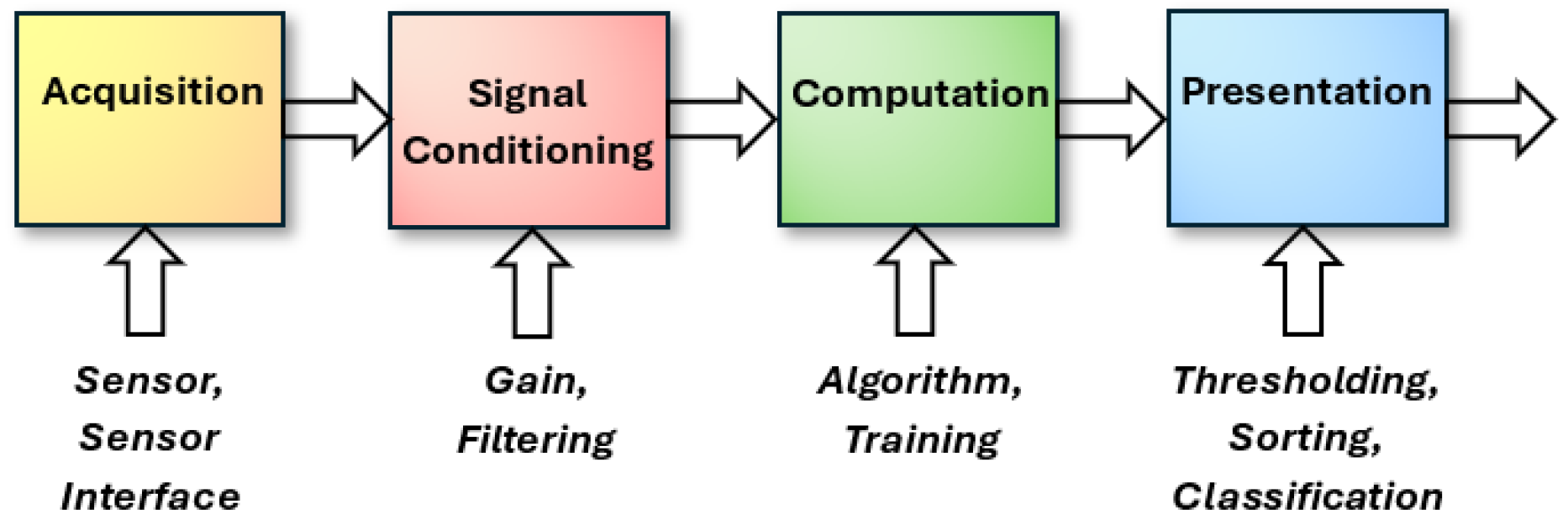

1. Introduction

2. Materials and Methods

2.1. Neural Analysis

- Delta, 0.5–4 Hz, deep sleep;

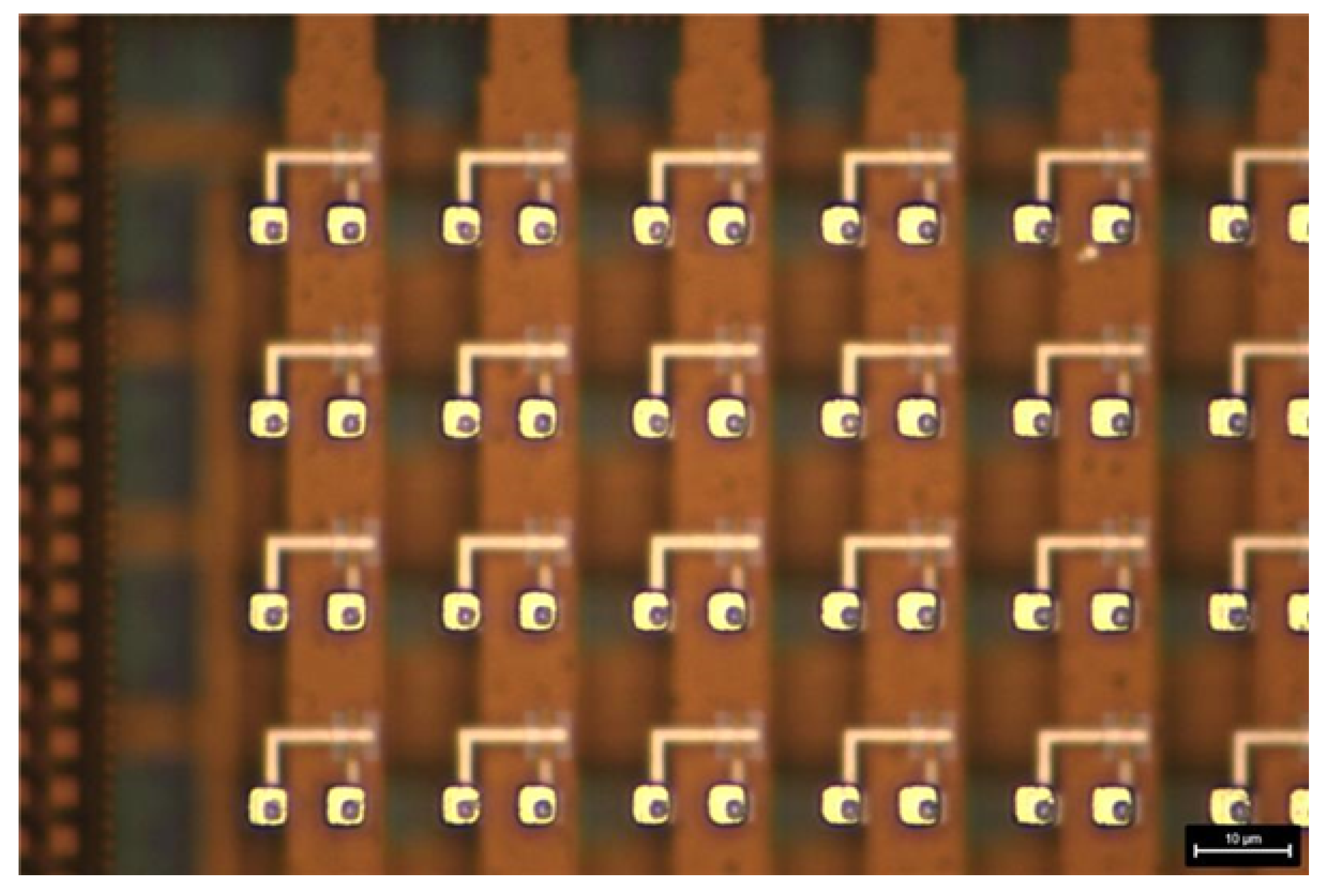

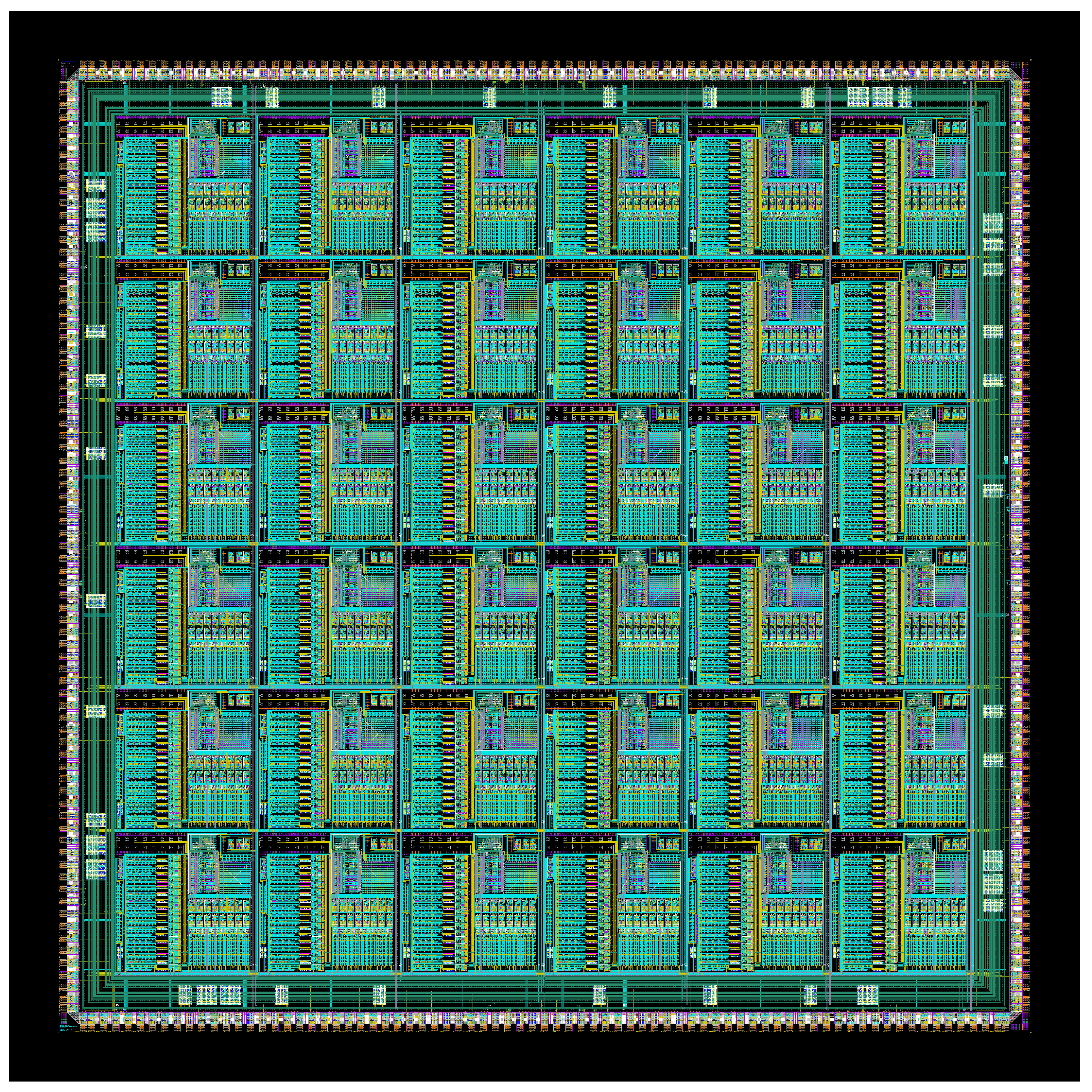

- Theta, 4–8 Hz, creativity, intuition, shallow sleep;

- Alpha, 8–12 Hz, relaxation, imagination, concentration;

- Beta, 12–30 Hz, reasoning, logic, alertness;

- Gamma, 30–100 Hz, memory, attention, schizophrenia.

2.2. Neural Analysis System Practicalities

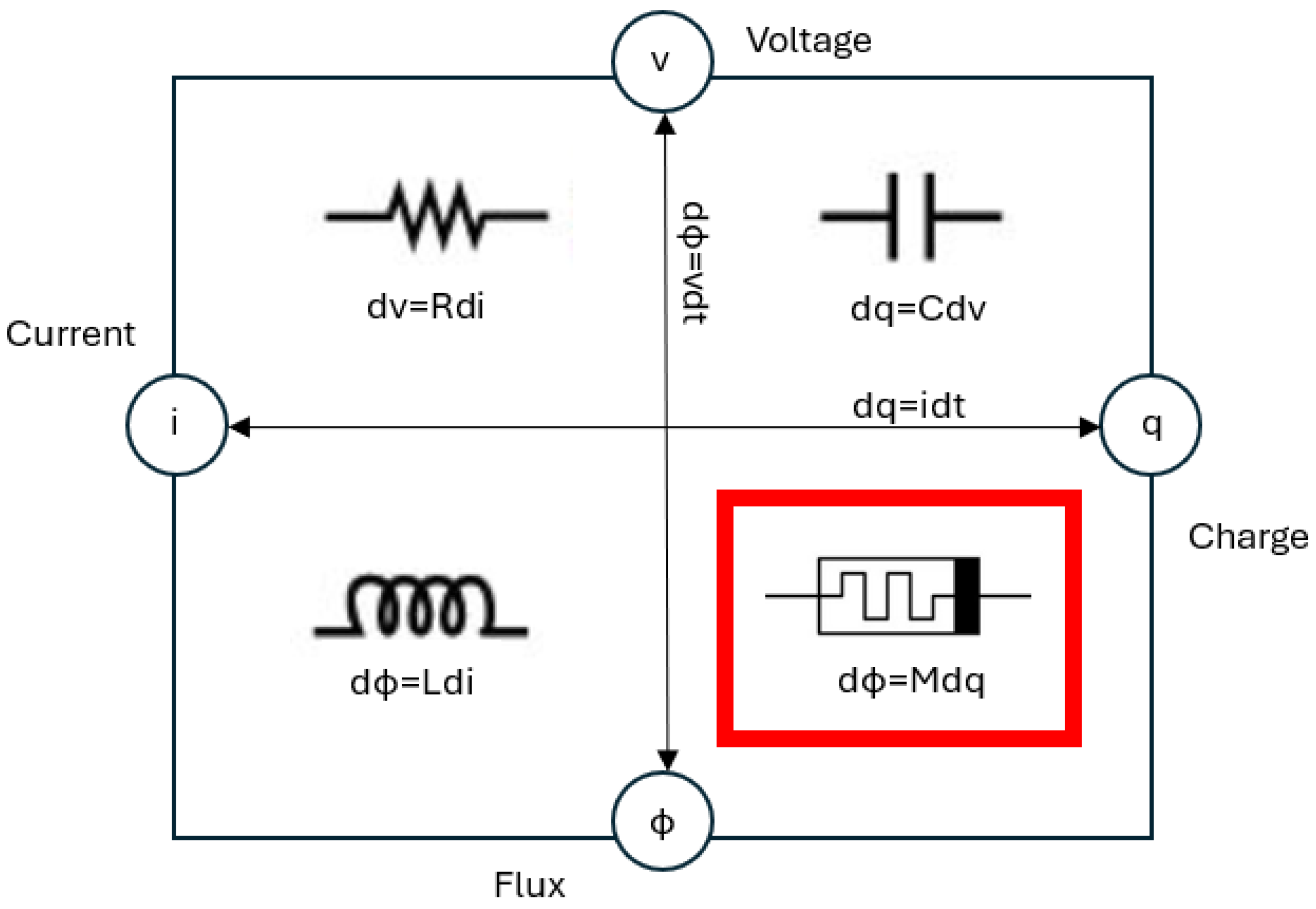

2.3. Memristors

3. Application of Memristors

3.1. Identification of Signal Types

3.1.1. Amplitude

3.1.2. Frequency

3.1.3. Waveform Shapes

3.1.4. Waveform Frequency Band

3.2. Sorting of Results to Extract Information

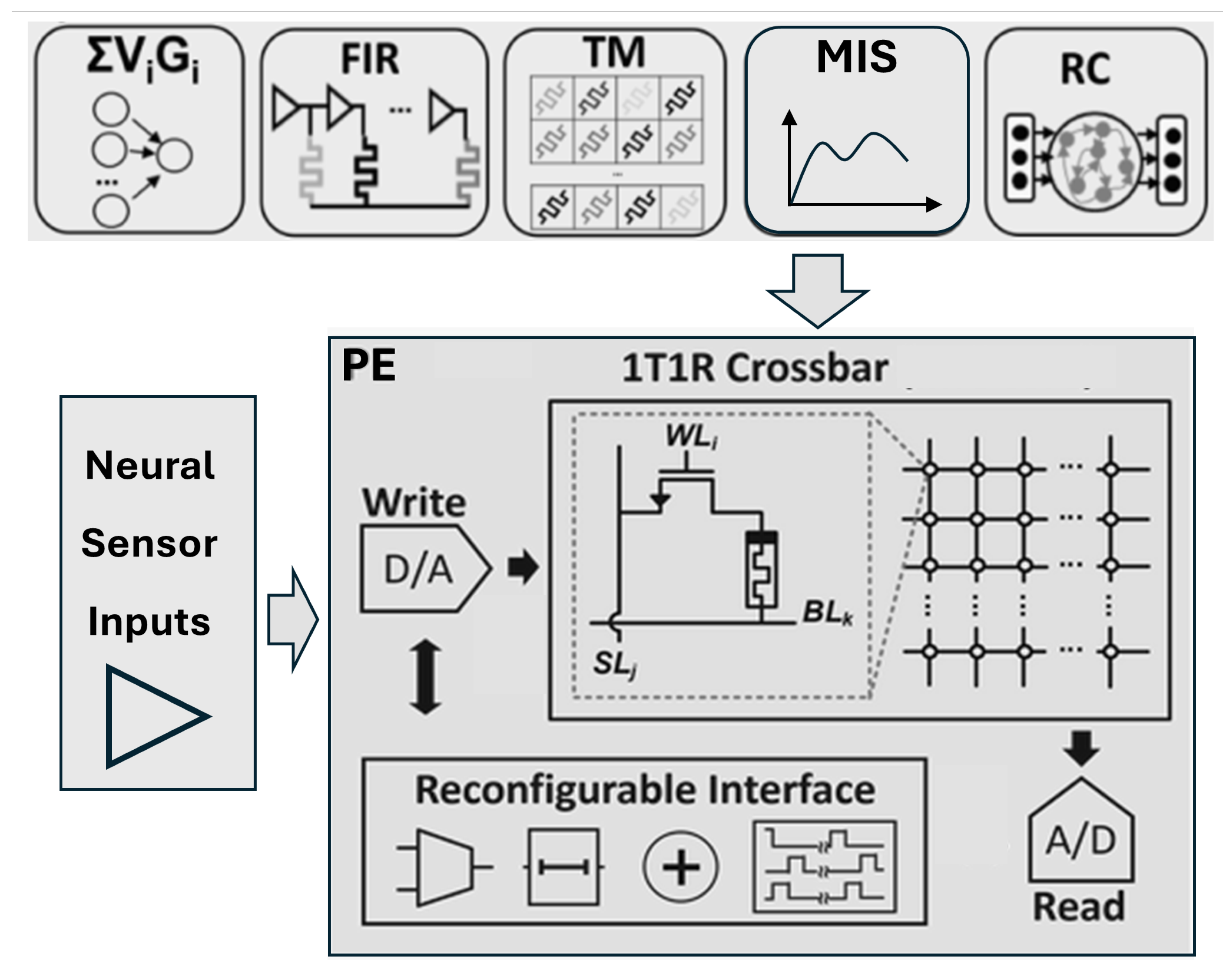

4. Development of a Memristor-Based System

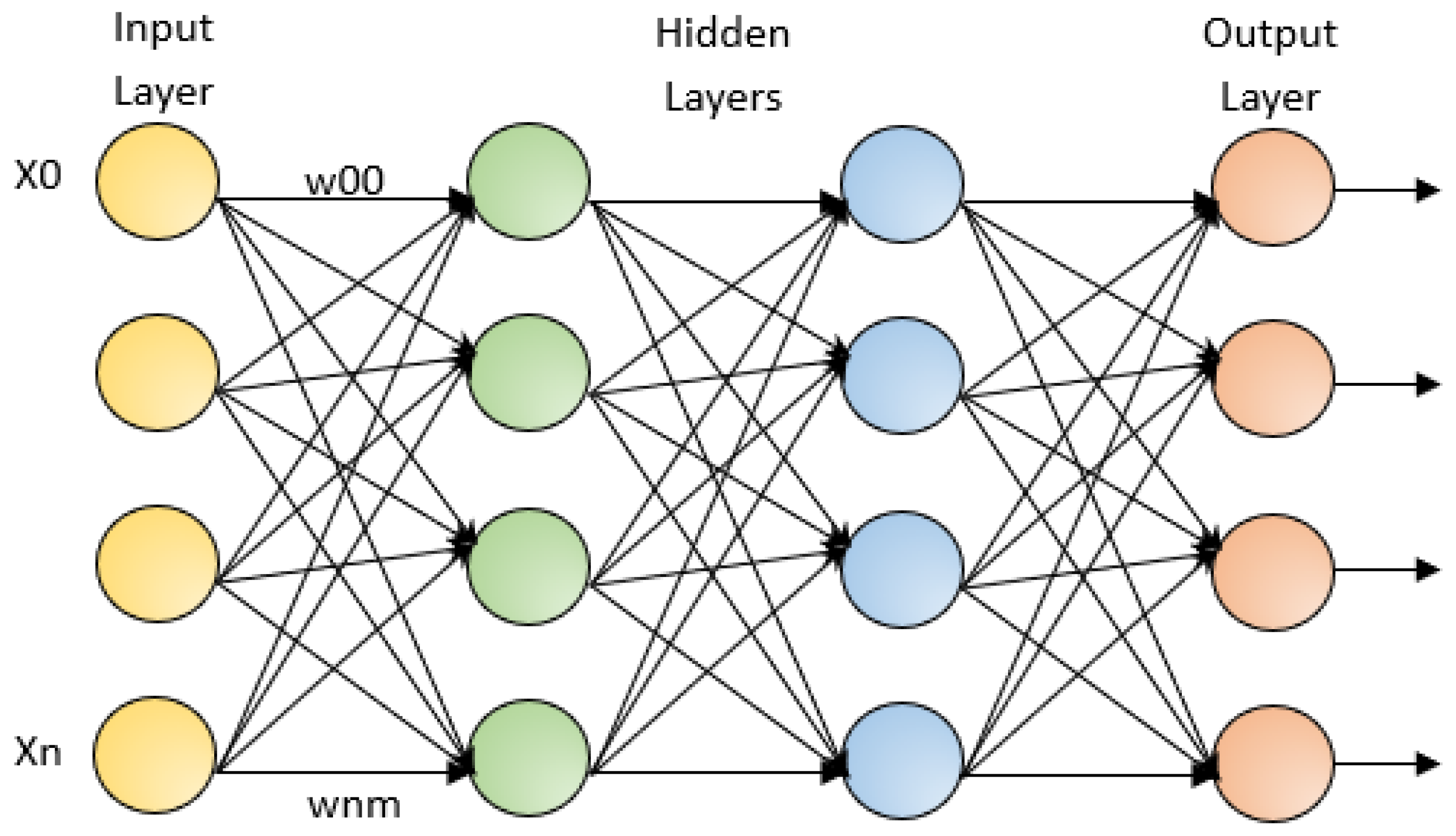

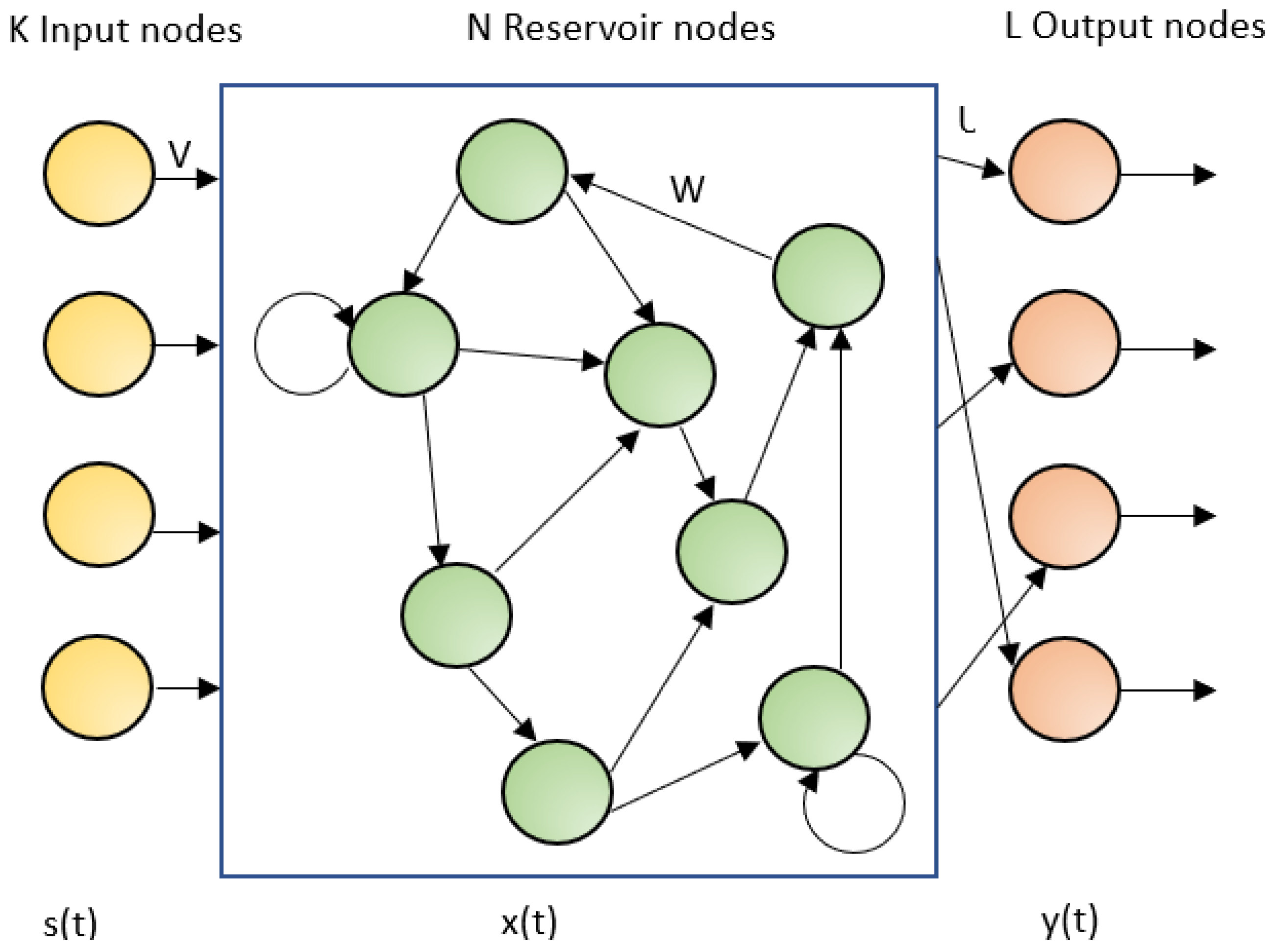

4.1. FFN/RCN

- s is the input vector (mapped to sensing channel outputs).

- V is the input connection weights (fixed unity value for all inputs, with random signs).

- x is the reservoir internal states (mapped to memristor resistance).

- W is the reservoir internal connection weights 0 or 1 (mapped to word line selection).

- H is the reservoir activation function mapped to the nonlinear memristor voltage/resistance dynamics.

- U is the trained weights for the output layer (mapped to source line selection).

- y is the reservoir output.

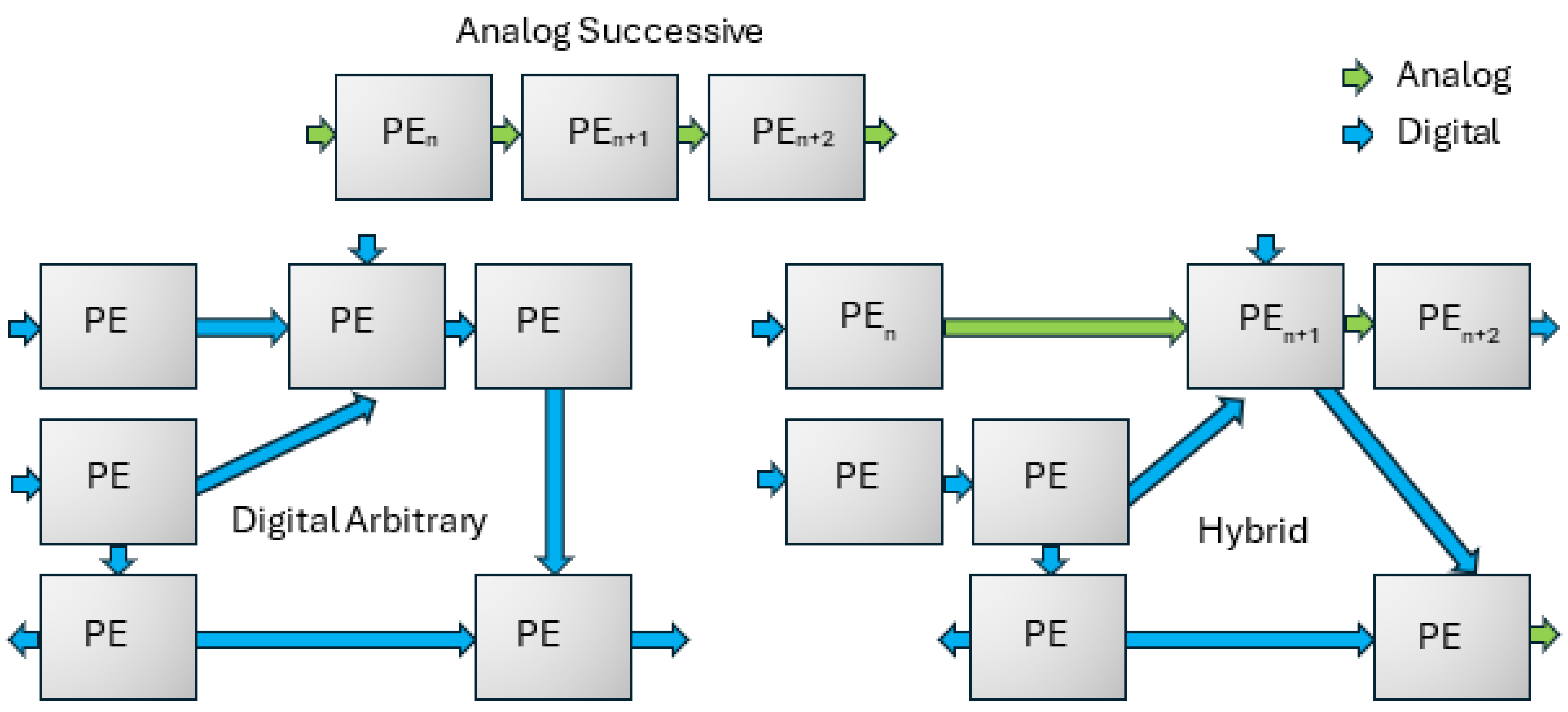

4.2. Interconnection

5. Operating Modes

5.1. Calibration

5.2. Initialization

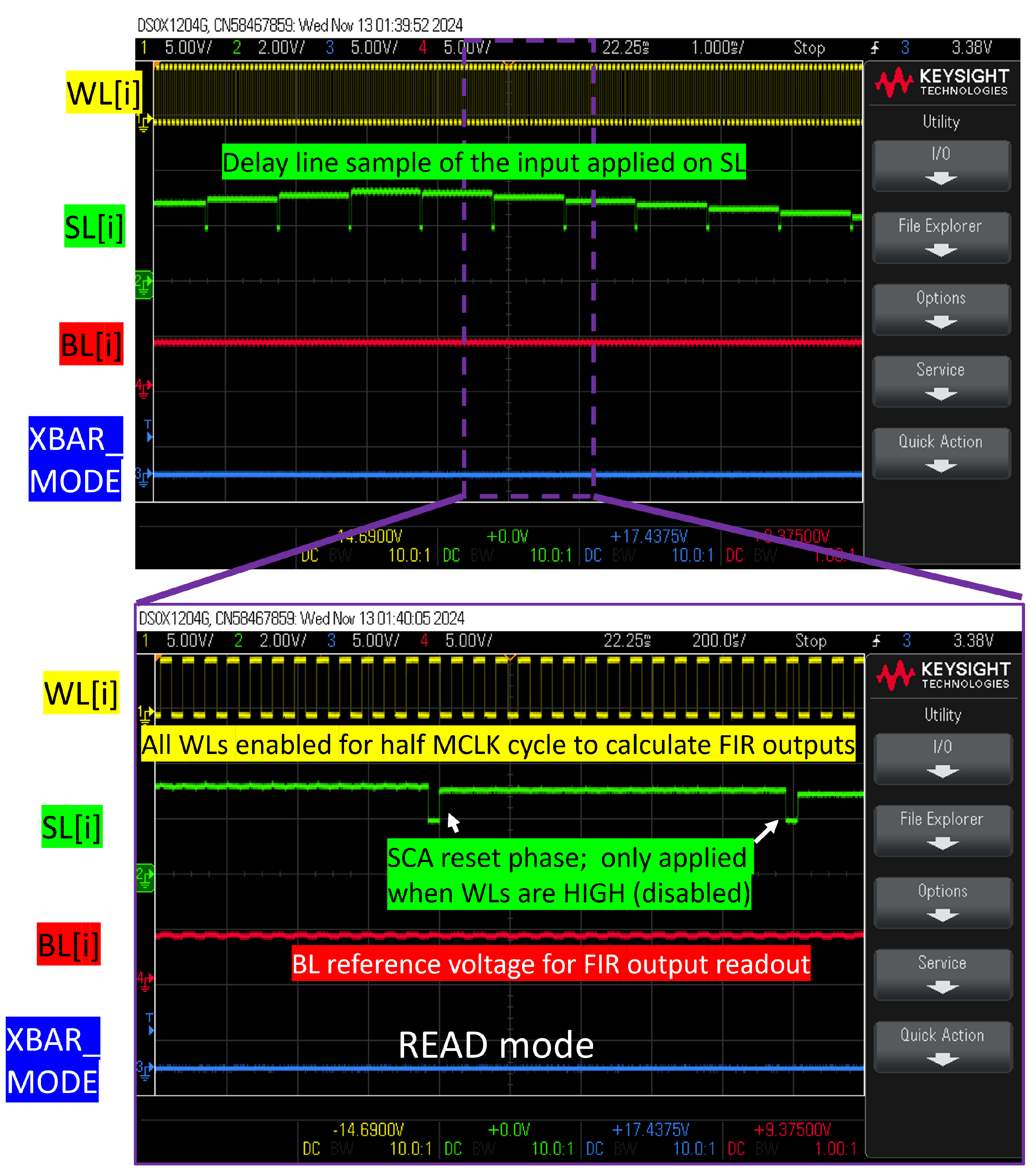

5.3. FIR

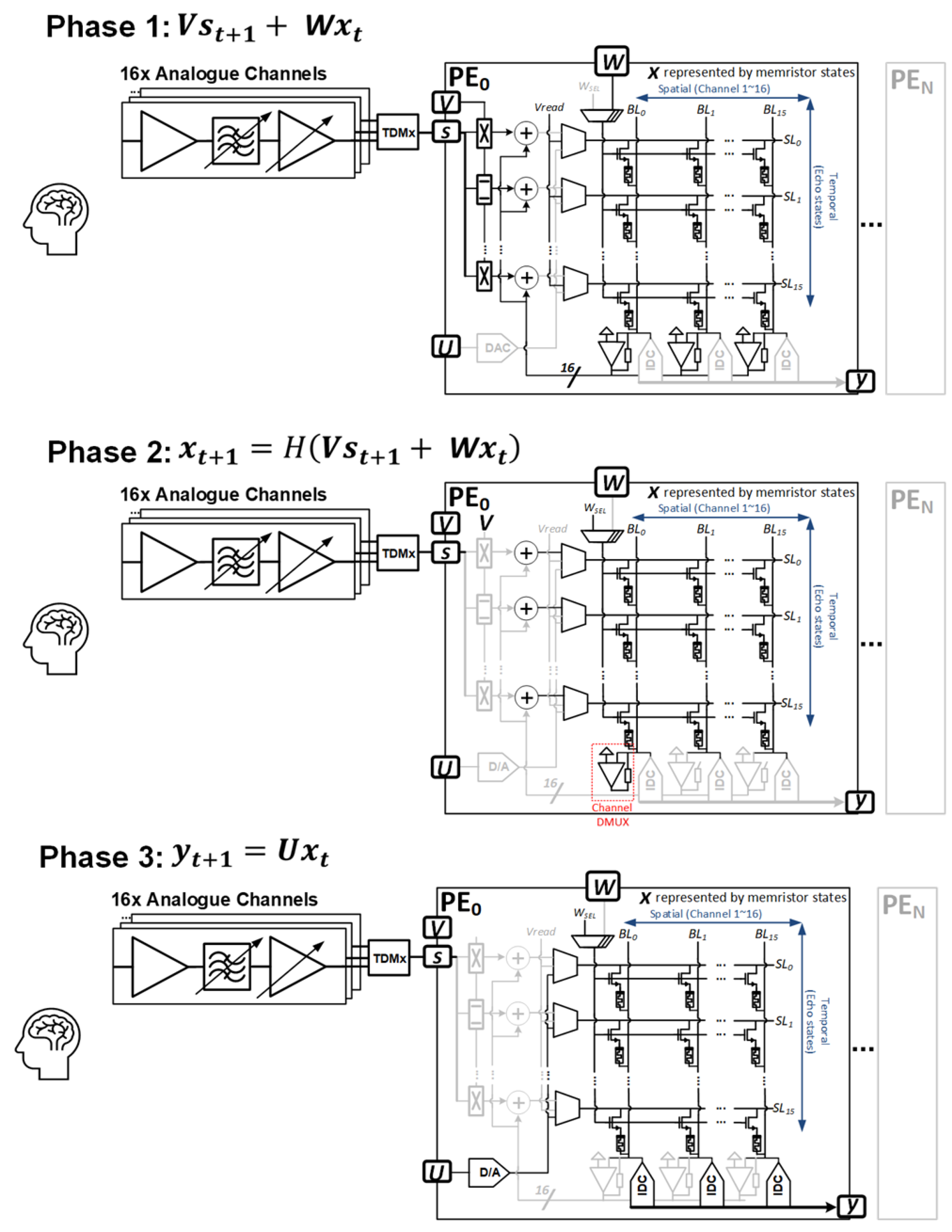

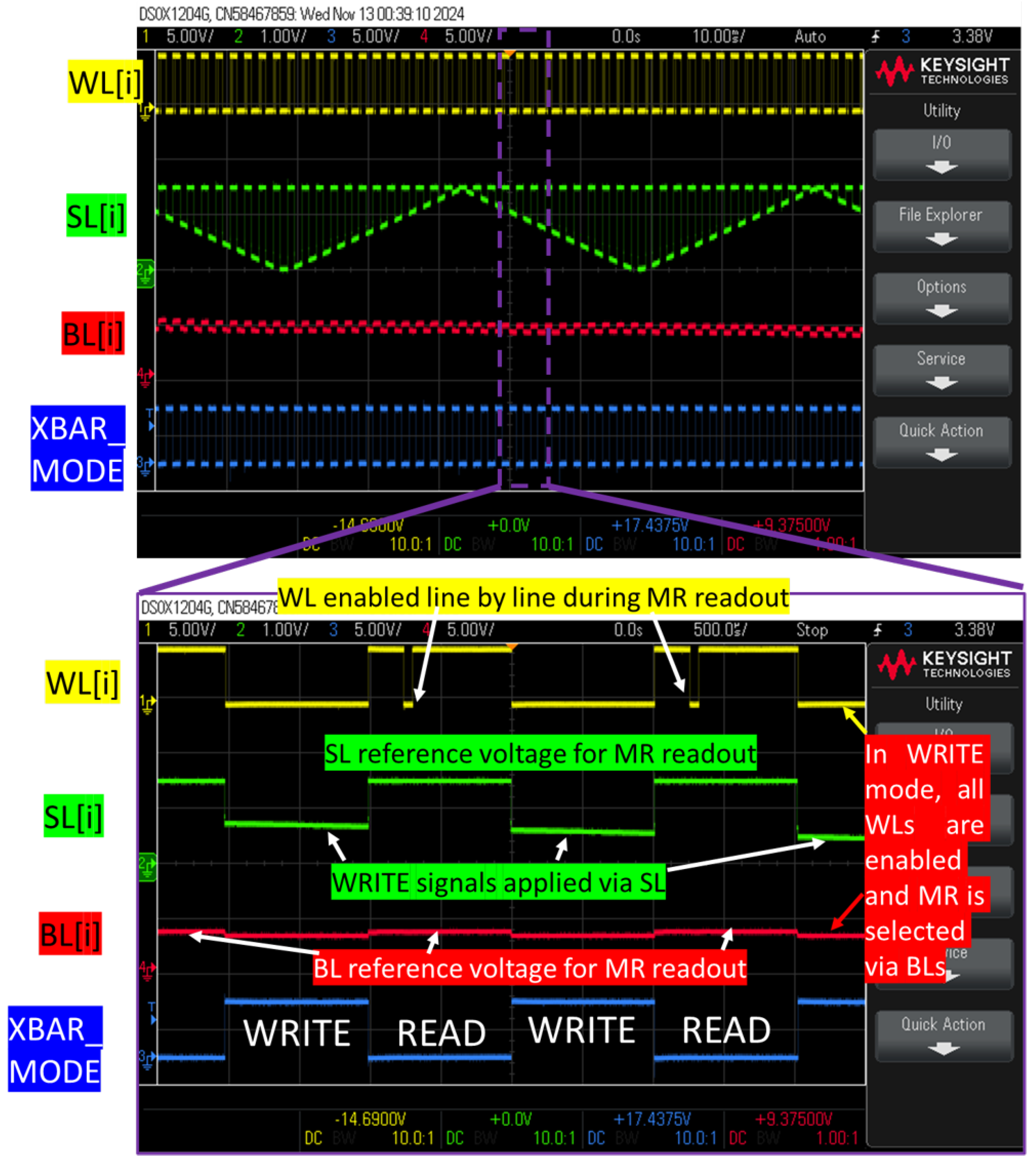

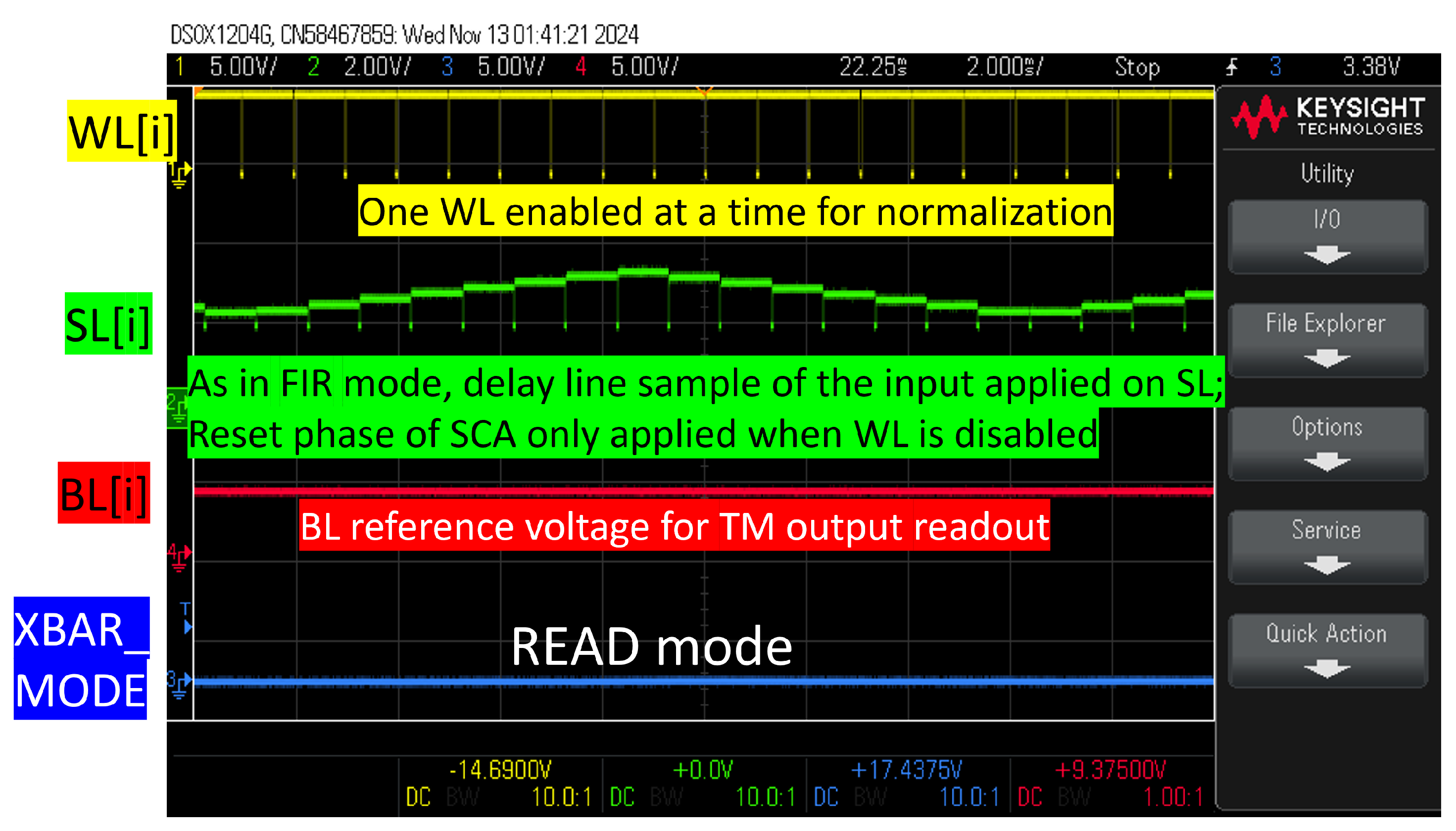

5.4. TM

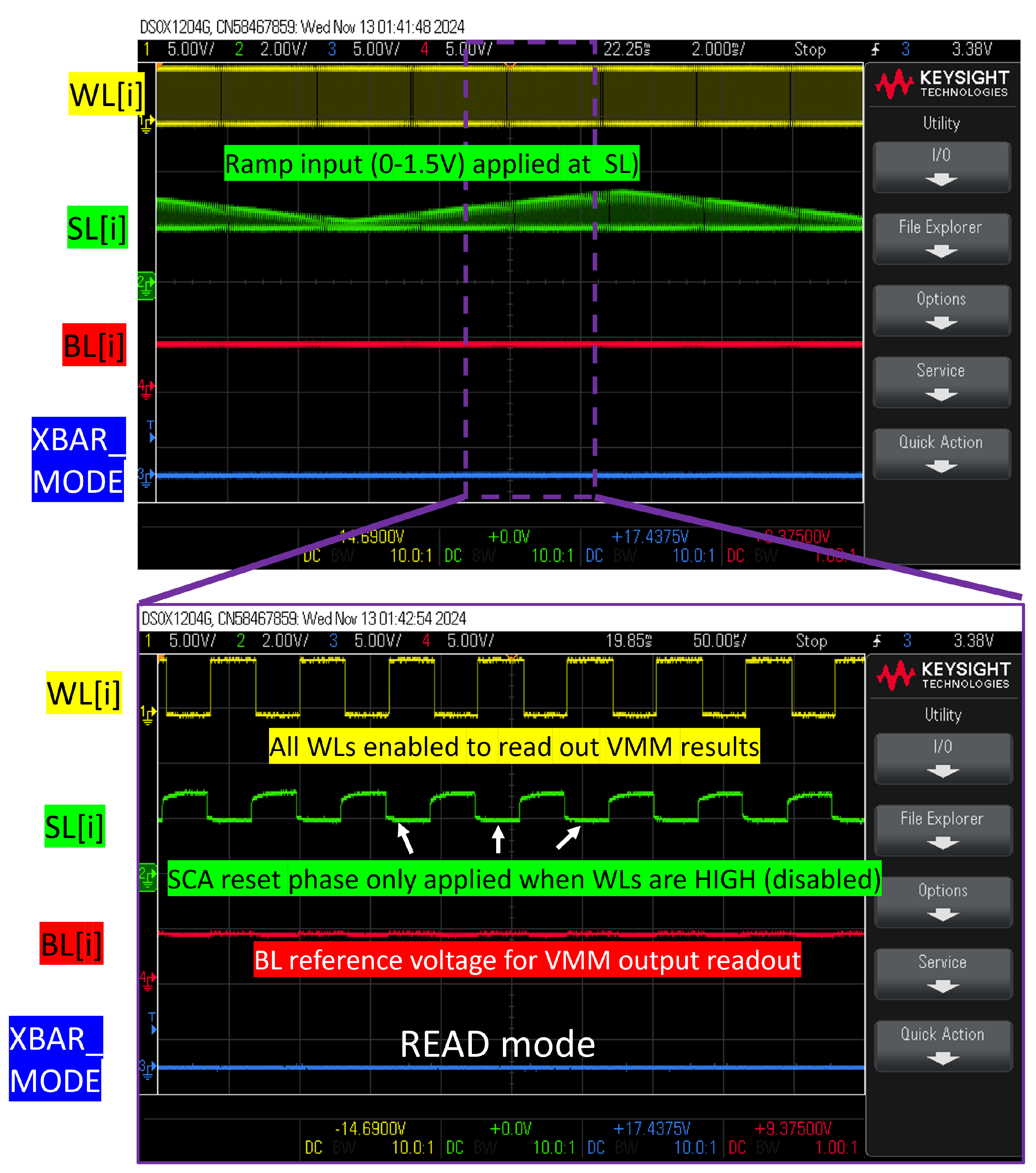

5.5. Feed Forward Network

5.6. MIS

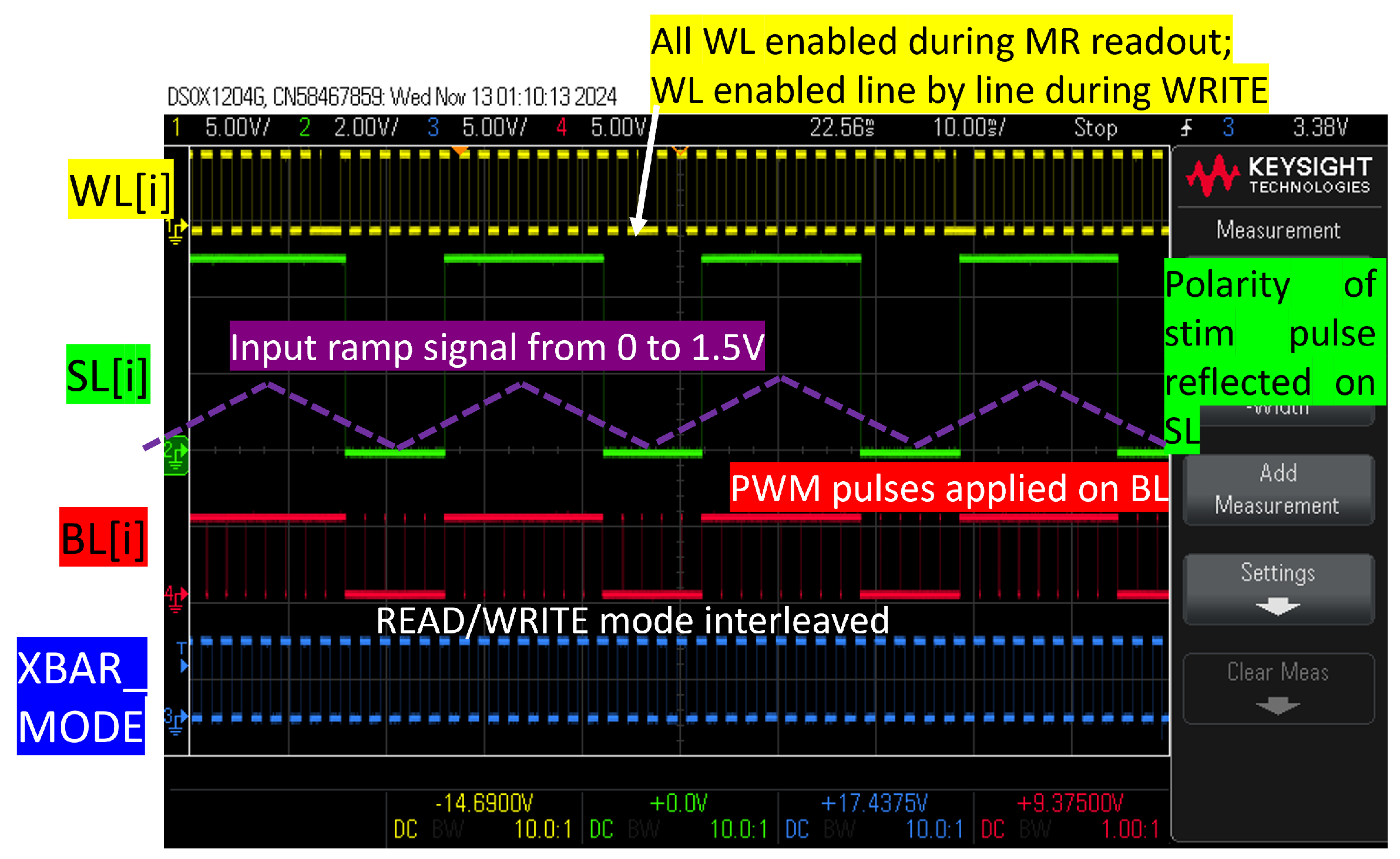

5.7. RC

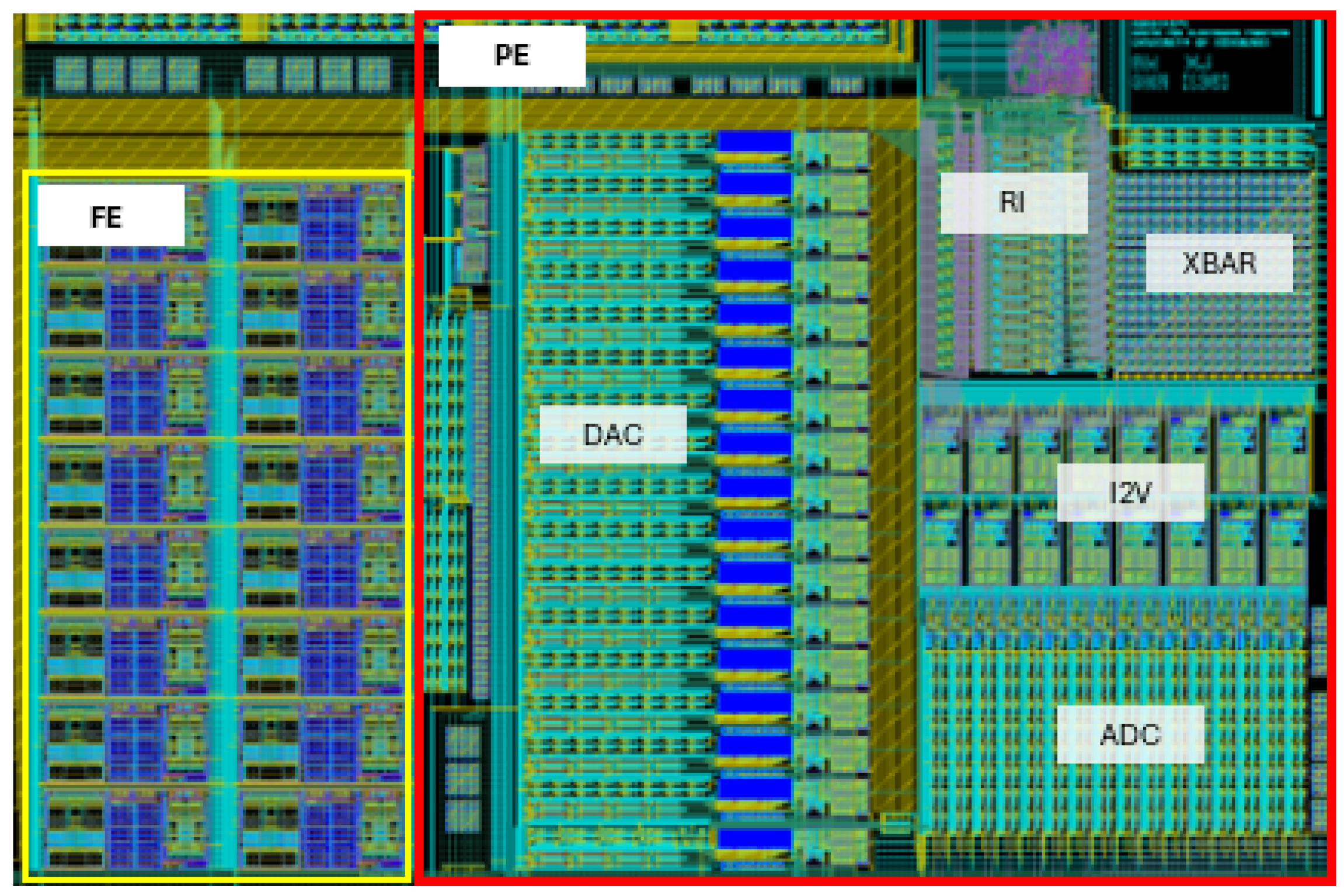

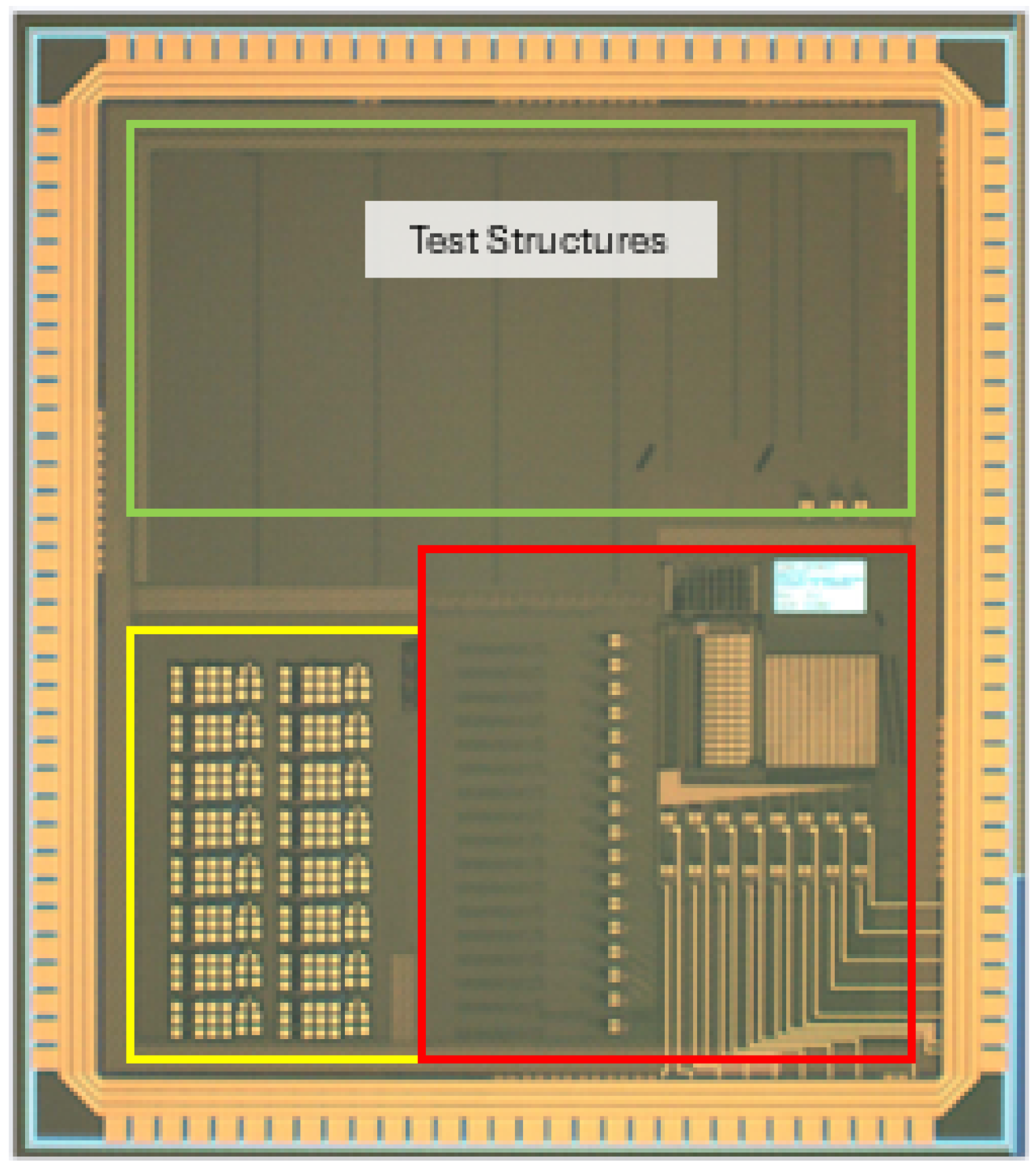

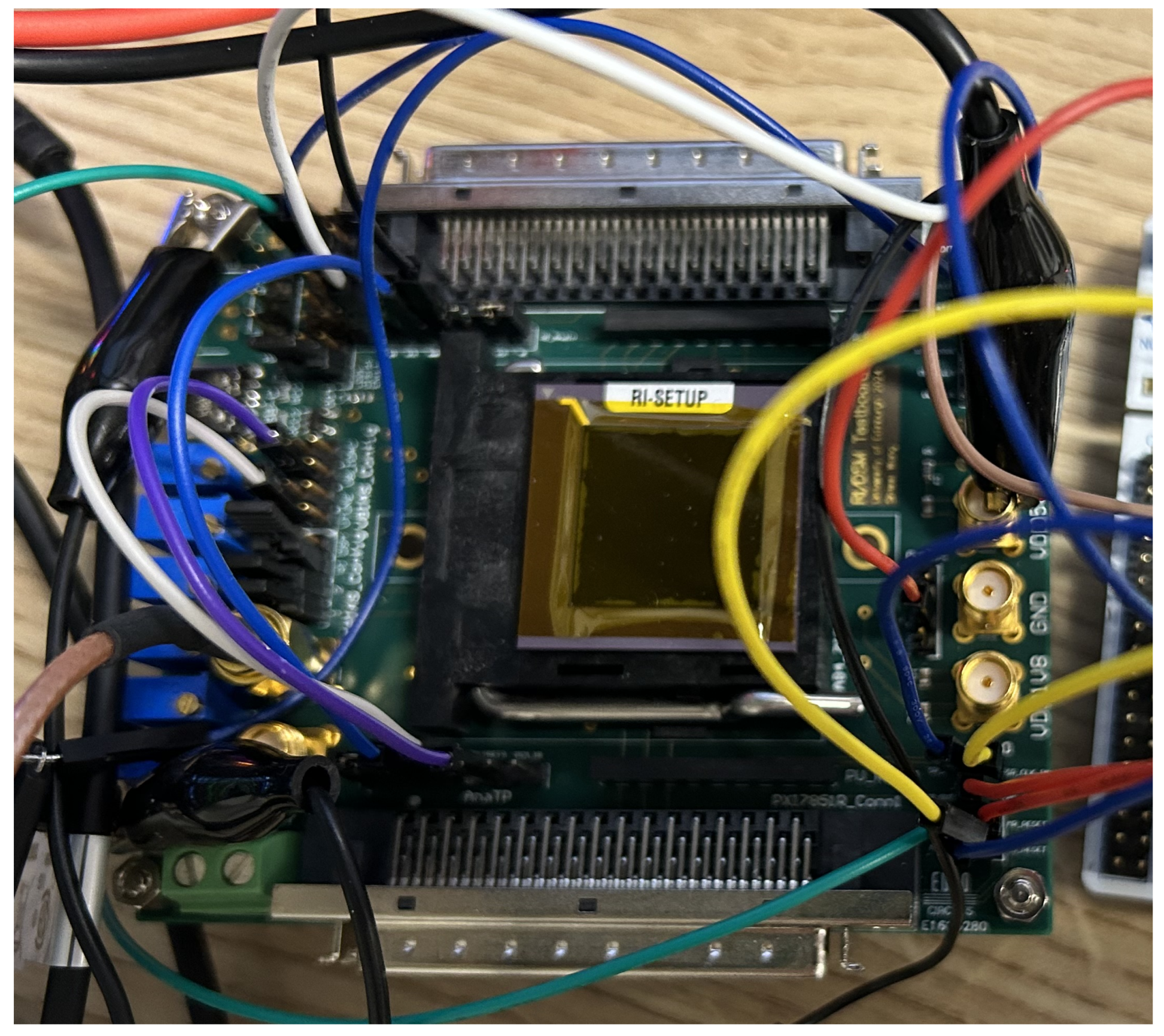

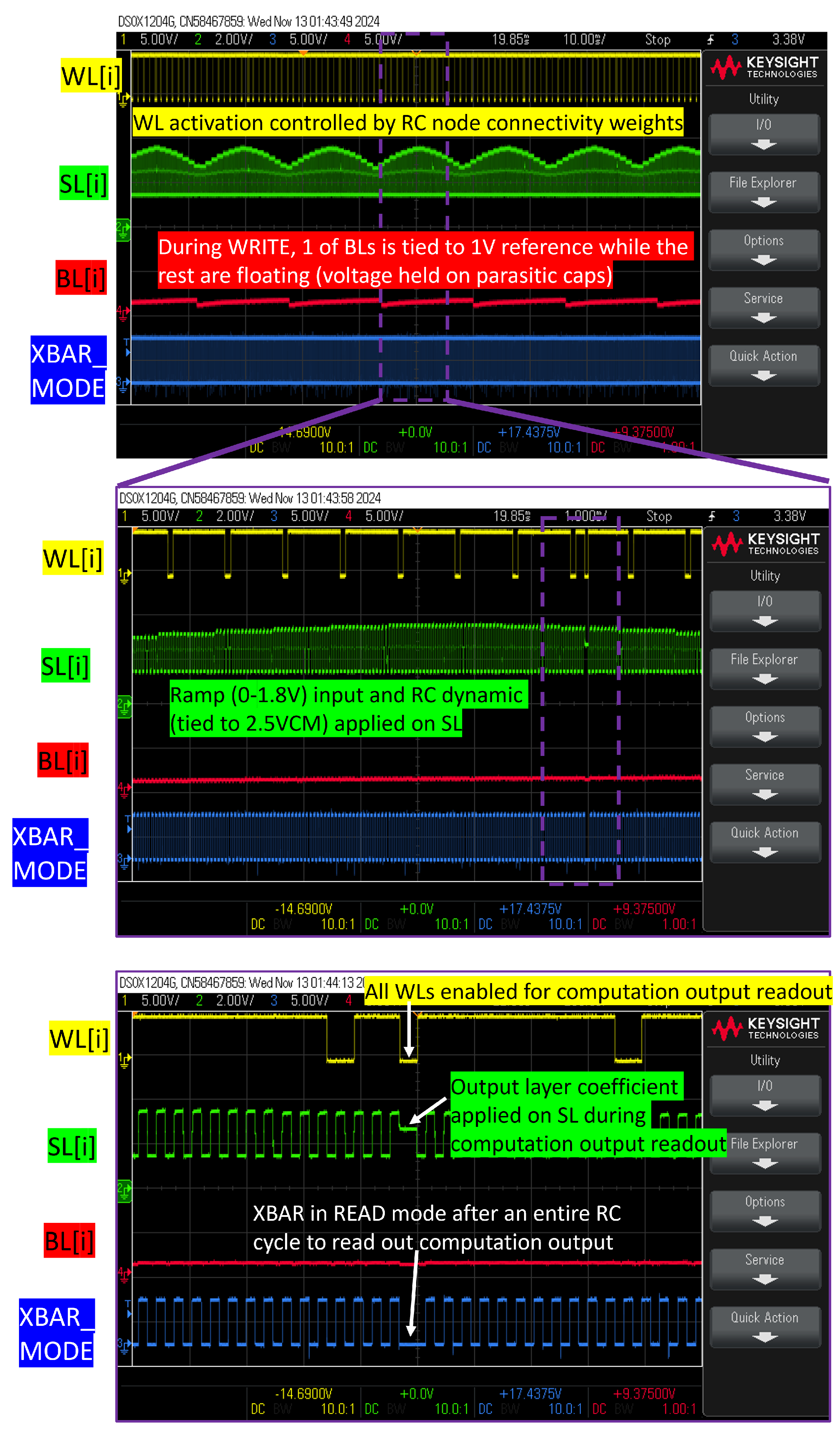

6. Implementation and Testing

7. Discussion and Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| AP | Action Potentials |

| BEOL | Back End of Line |

| CEF | Centre for Electronics Frontiers |

| ECoG | Electrocorticography |

| EEG | Electroencephalography |

| EP | Evoked Potentials |

| ERP | Event Related Potentials |

| FFN | Feed Forward Network |

| FIR | Finite Impulse Response |

| FORTE | Functional Oxide Reconfigurable Technologies |

| HF | High Frequency |

| LFP | Local Field Potentials |

| MIS | Memristive Integrated Sensing |

| PE | Process Element |

| RC | Reservoir Computing |

| RCN | Reservoir Compute Network |

| TM | Template Matching |

| VMM | Vector Matrix Multiplication |

References

- Drew, L. Decoding the business of brain–computer interfaces. Nat. Electron. 2023, 6, 90–95. [Google Scholar] [CrossRef]

- Pei, D.; Vinjamuri, R. Advances in Neural Signal Processing; IntechOpen: London, UK, 2020; ISBN 978-1-83968-396-1. [Google Scholar]

- Tsai, C.W.; Jiang, R.; Zhang, L.; Zhang, M.; Wu, L.; Guo, J.; Yan, Z.; Yoo, J. SciCNN: A 0-Shot-Retraining Patient-Independent Epilepsy-Tracking SoC. In Proceedings of the 2023 IEEE International Solid- State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023. [Google Scholar]

- Shin, U.; Ding, C.; Zhu, B.; Vyza, Y.; Trouillet, A.; Revol, E.C.; Lacour, S.P.; Shoaran, M. NeuralTree: A 256-Channel 0.227-μJ/Class Versatile Neural Activity Classification and Closed-Loop Neuromodulation SoC. IEEE J. Solid-State Circuits 2022, 57, 3243–3257. [Google Scholar] [CrossRef] [PubMed]

- Chua, A.; Jordan, M.I.; Muller, R. SOUL: An Energy-Efficient Unsupervised Online Learning Seizure Detection Classifier. IEEE J. Solid-State Circuits 2022, 57, 2532–2544. [Google Scholar] [CrossRef]

- Wang, Y.; Sun, Q.; Luo, H.; Chen, X.; Wang, X.; Zhang, H. 26.3 A Closed-Loop Neuromodulation Chipset with 2-Level Classification Achieving 1.5 Vpp CM Interference Tolerance, 35 dB Stimulation Artifact Rejection in 0.5ms and 97.8% Sensitivity Seizure Detection. In Proceedings of the 2020 IEEE International Solid- State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 406–408. [Google Scholar]

- O’Leary, G.; Groppe, D.M.; Valiante, T.A.; Verma, N.; Genov, R. NURIP: Neural Interface Processor for Brain-State Classification and Programmable-Waveform Neurostimulation. IEEE J. Solid-State Circuits 2018, 53, 3150–3162. [Google Scholar] [CrossRef]

- Appelbaum, L.G.; Shenasa, M.A.; Stolz, L.; Daskalakis, Z. Synaptic plasticity and mental health: Methods, challenges and opportunities. Neuropsychopharmacology 2022, 48, 113–120. [Google Scholar] [CrossRef]

- Seidl, A.H. Regulation of Conduction Time along Axons. Neuroscience 2014, 276, 126–134. [Google Scholar] [CrossRef] [PubMed]

- Clayton, M.S.; Yeung, N.; Kadosh, R.C. The roles of cortical oscillations in sustained attention. Trends Cogn. Sci. 2015, 19, 188–195. [Google Scholar] [CrossRef]

- Omar, E.; Aly, H.H.; Fedawy, M. A Brief introduction to Memristor Device. IJAEBS 2023, 4, 171–198. [Google Scholar] [CrossRef]

- Cavallini, M.; Hemmatian, Z.; Riminucci, A.; Prezioso, M.; Morandi, V.; Murgia, M. Regenerable Resistive Switching in Silicon Oxide Based Nanojunctions. Adv. Mater. 2012, 24, 1197–1201. [Google Scholar] [CrossRef]

- Gupta, I.; Serb, A.; Khiat, A.; Zeitler, R.; Vassanelli, S.; Prodromakis, T. Real-time encoding and compression of neuronal spikes by metal-oxide memristors. Nat. Commun. 2016, 7, 12805. [Google Scholar] [CrossRef] [PubMed]

- Liu, Z.; Tang, J.; Gao, B.; Li, X.; Yao, P.; Lin, Y.; Liu, D.; Hong, B.; Qian, H.; Wu, H. Multichannel parallel processing of neural signals in memristor arrays. Sci. Adv. 2020, 6, 2–10. [Google Scholar] [CrossRef] [PubMed]

- Mifsud, A.; Shen, J.; Feng, P.; Xie, L.; Wang, C.; Pan, Y.; Maheshwari, S.; Agwa, S.; Stathopoulos, S.; Wang, S.; et al. A CMOS-based Characterisation Platform for Emerging RRAM Technologies. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–1 June 2022. [Google Scholar]

- Jiang, X.; Sbandati, C.; Reynolds, G.; Wang, C.; Papavassiliou, C.; Serb, A.; Prodromakis, T.; Wang, S. A Neural Recording System With 16 Reconfigurable Front-end Channels and Memristive Processing/Memory Unit. In Proceedings of the 2023 IEEE NEWCAS Conference, Edinburgh, UK, 26–28 June 2023. [Google Scholar]

- Wan, W.; Kubendran, R.; Schaefer, C.; Eryilmaz, S.B.; Zhang, W.; Wu, D.; Deiss, S.; Raina, P.; Qian, H.; Gao, B.; et al. A compute-in-memory chip based on resistive random-access memory. Nature 2022, 608, 504–512. [Google Scholar] [CrossRef]

- Shi, Y.; Ananthakrishnan, A.; Oh, S.; Liu, X.; Hota, G.; Cauwenberghs, G.; Kuzum, D. High Throughput Neuromorphic Brain Interface with CuOx Resistive Crossbars for Real-time Spike Sorting. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–15 December 2021; pp. 16.5.1–16.5.4. [Google Scholar]

- Abhang, P.; Mehotra, S. Technological Basics of EEG Recording and Operation of Apparatus. In Introduction to EEG- and Speech-Based Emotion Recognition; Academic Press: Cambridge, MA, USA, 2016. [Google Scholar]

- Liu, Z.; Tang, J.; Gao, B.; Yao, P.; Li, X.; Liu, D.; Zhou, Y.; Qian, H.; Hong, B.; Wu, H. Neural signal analysis with memristor arrays towards high-efficiency brain–machine interfaces. Nat. Commun. 2020, 11, 4234. [Google Scholar] [CrossRef] [PubMed]

- Reynolds, G.; Jiang, X.; Serb, A.; Prodromakis, T.; Wang, S. An Integrated CMOS/Memristor Bio-Processor for Re-configurable Neural Signal Processing. In Proceedings of the 2023 IEEE Biomedical Circuits and Systems Conference (BioCAS), Toronto, ON, Canada, 19–21 October 2023. [Google Scholar]

- Moon, J.; Ma, W.; Shin, J.H.; Cai, F.; Du, C.; Lee, S.H.; Lu, W.D. Temporal data classification and forecasting using a memristor-based reservoir computing system. Nat. Electron. 2019, 2, 480–487. [Google Scholar] [CrossRef]

- Zhong, Y.; Tang, J.; Li, X.; Gao, B.; Qian, H.; Wu, H. Dynamic memristor-based reservoir computing for high-efficiency temporal signal processing. Nat. Commun. 2021, 12, 408. [Google Scholar] [CrossRef] [PubMed]

- Tanaka, G.; Yamane, T.; Héroux, J.B.; Nakane, R.; Kanazawa, N.; Takeda, S.; Numata, H.; Nakano, D.; Hirose, A. Recent advances in physical reservoir computing: A review. Neural Netw. 2019, 115, 100–123. [Google Scholar] [CrossRef] [PubMed]

- Rodan, A.; Tiňo, P. Minimum complexity echo state network. IEEE Trans. Neural Netw. 2011, 22, 131–144. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Reynolds, G.; Jiang, X.; Wang, S.; Serb, A.; Stathopolous, S.; Prodromakis, T. A Scalable, Multi-Core, Multi-Function, Integrated CMOS/Memristor Sensor Interface for Neural Sensing Applications. Electronics 2025, 14, 30. https://doi.org/10.3390/electronics14010030

Reynolds G, Jiang X, Wang S, Serb A, Stathopolous S, Prodromakis T. A Scalable, Multi-Core, Multi-Function, Integrated CMOS/Memristor Sensor Interface for Neural Sensing Applications. Electronics. 2025; 14(1):30. https://doi.org/10.3390/electronics14010030

Chicago/Turabian StyleReynolds, Grahame, Xiongfei Jiang, Shiwei Wang, Alex Serb, Spyros Stathopolous, and Themis Prodromakis. 2025. "A Scalable, Multi-Core, Multi-Function, Integrated CMOS/Memristor Sensor Interface for Neural Sensing Applications" Electronics 14, no. 1: 30. https://doi.org/10.3390/electronics14010030

APA StyleReynolds, G., Jiang, X., Wang, S., Serb, A., Stathopolous, S., & Prodromakis, T. (2025). A Scalable, Multi-Core, Multi-Function, Integrated CMOS/Memristor Sensor Interface for Neural Sensing Applications. Electronics, 14(1), 30. https://doi.org/10.3390/electronics14010030