An Energy-Efficient 12-Bit VCO-Based Incremental Zoom ADC with Fast Phase-Alignment Scheme for Multi-Channel Biomedical Applications

Abstract

1. Introduction

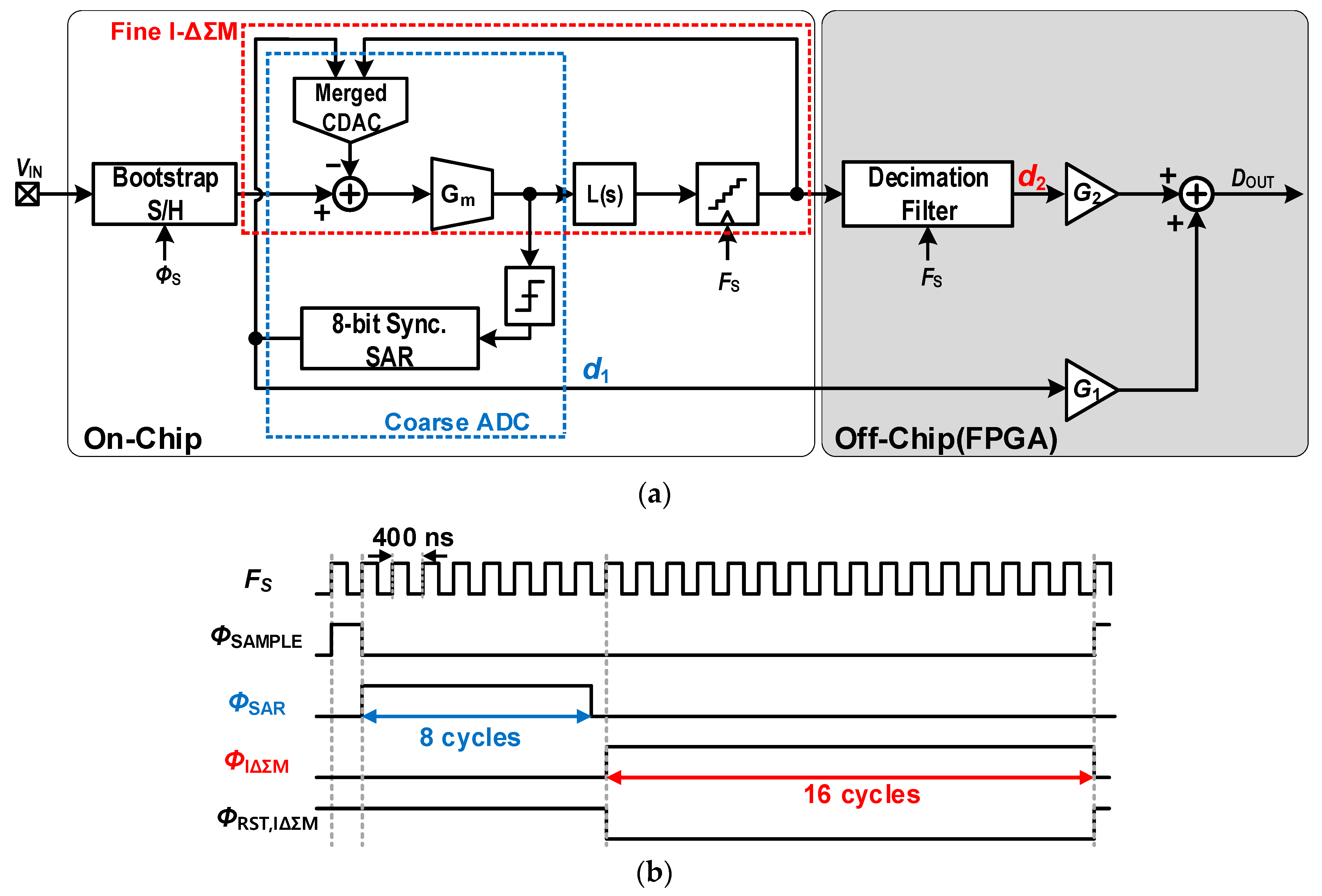

2. Zoom ADC Architecture

2.1. Coarse and Fine Operation

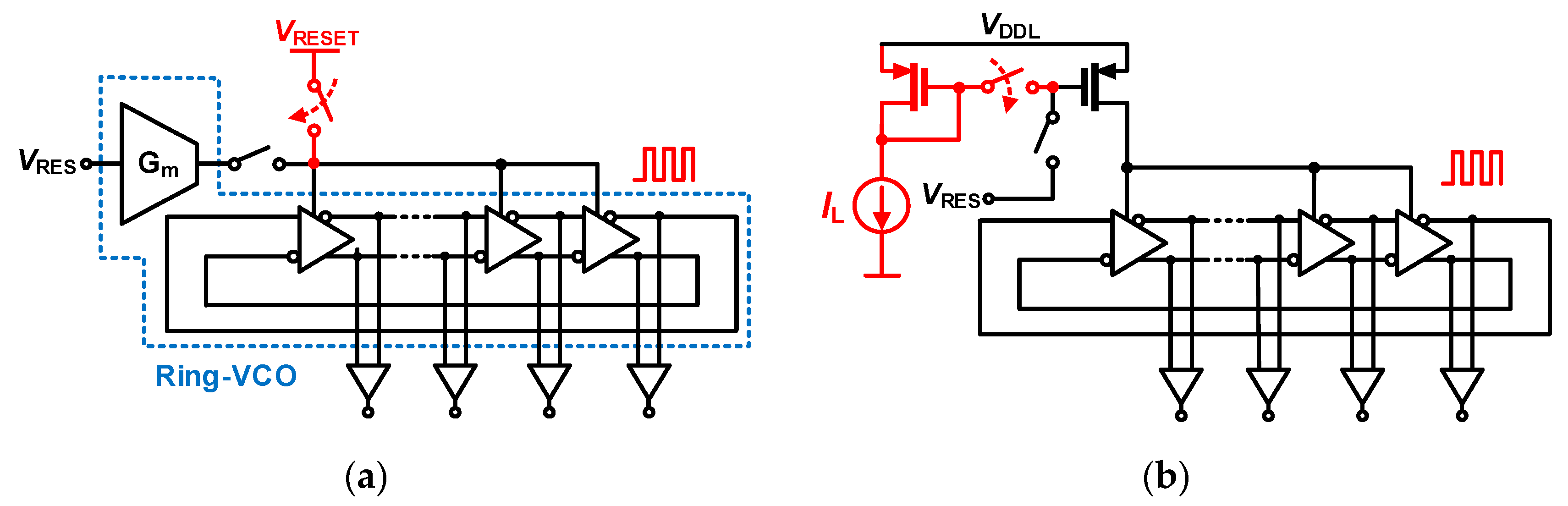

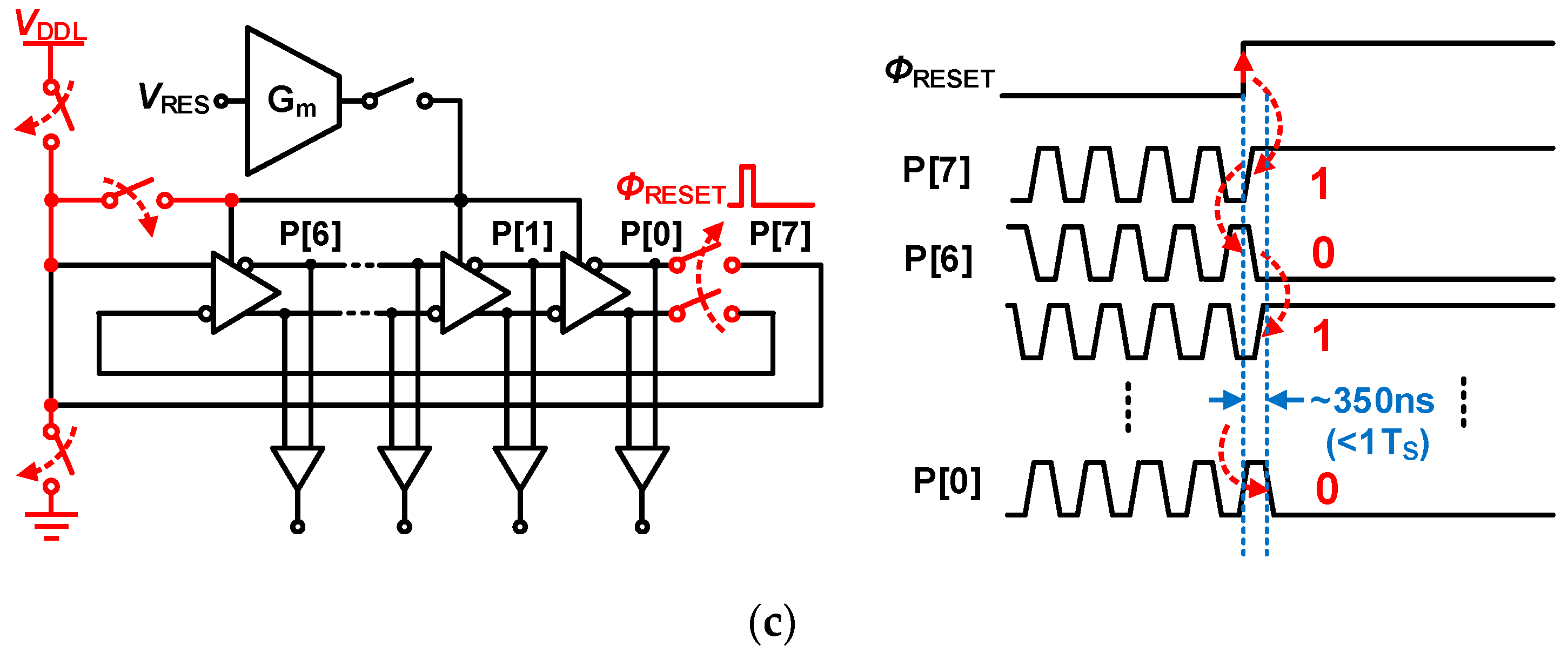

2.2. Ring-VCO-Based Time-Domain I-ΔΣM with Fast Phase-Reset

2.3. Noise Analysis

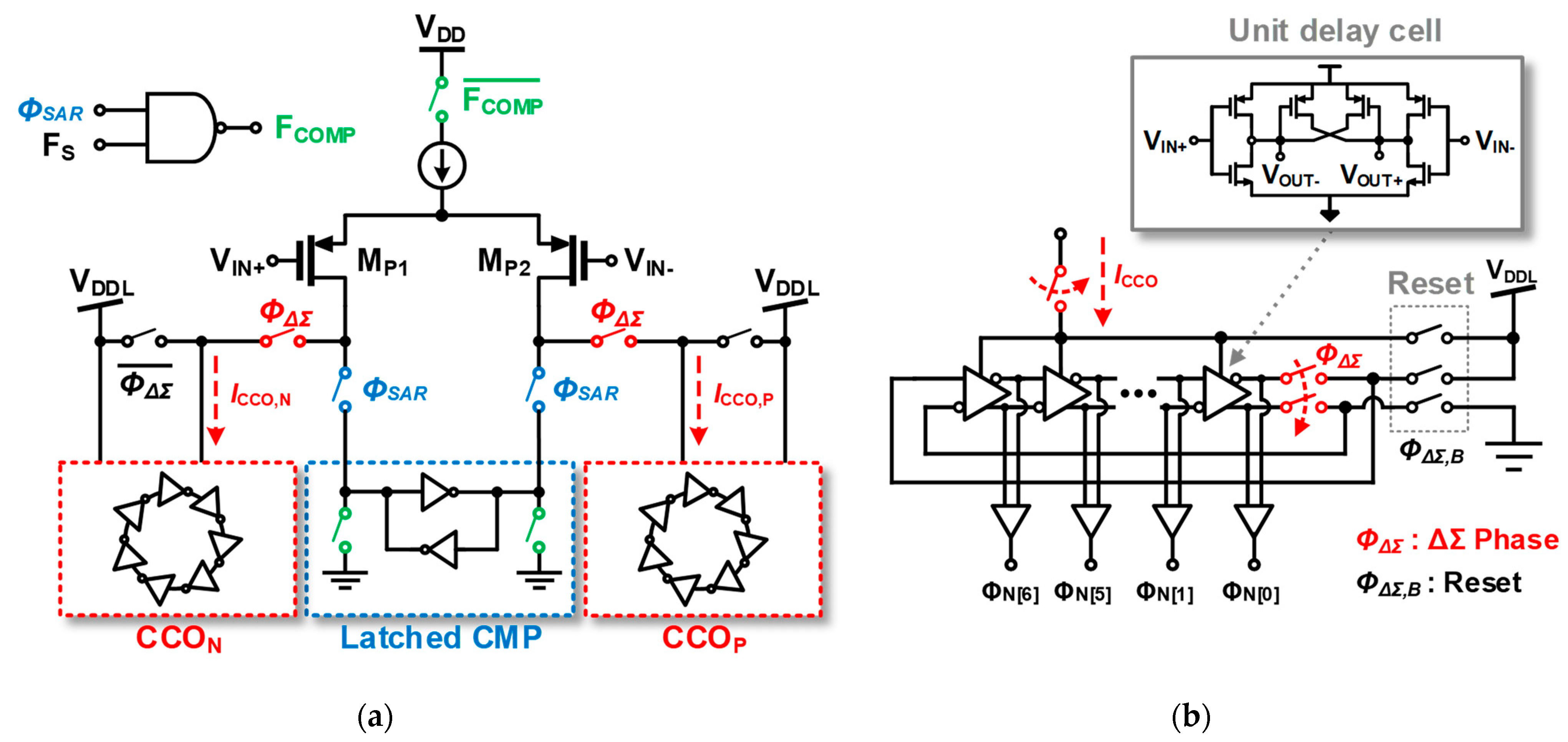

3. Circuit Implementations

3.1. Voltage-Controlled Oscillator

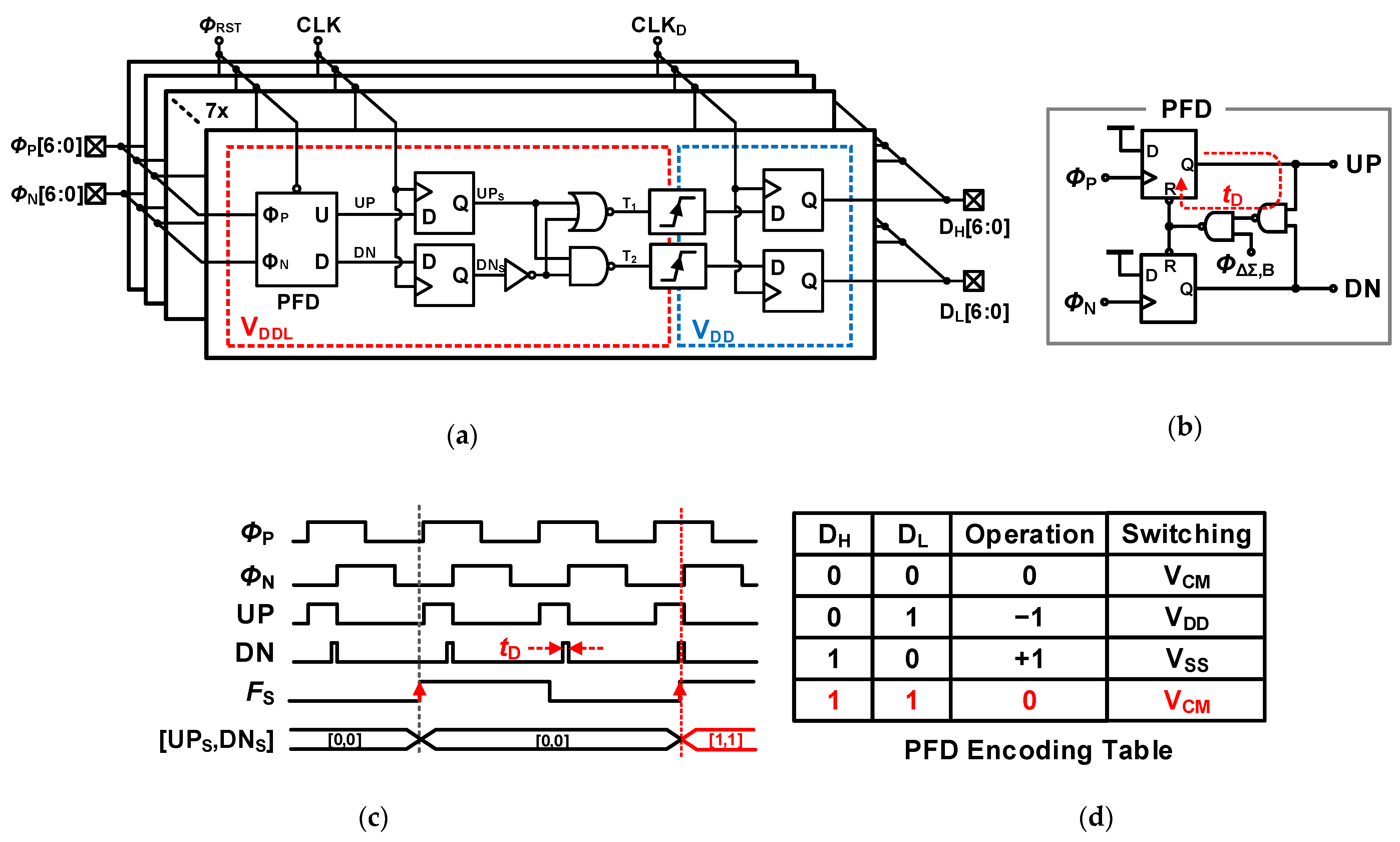

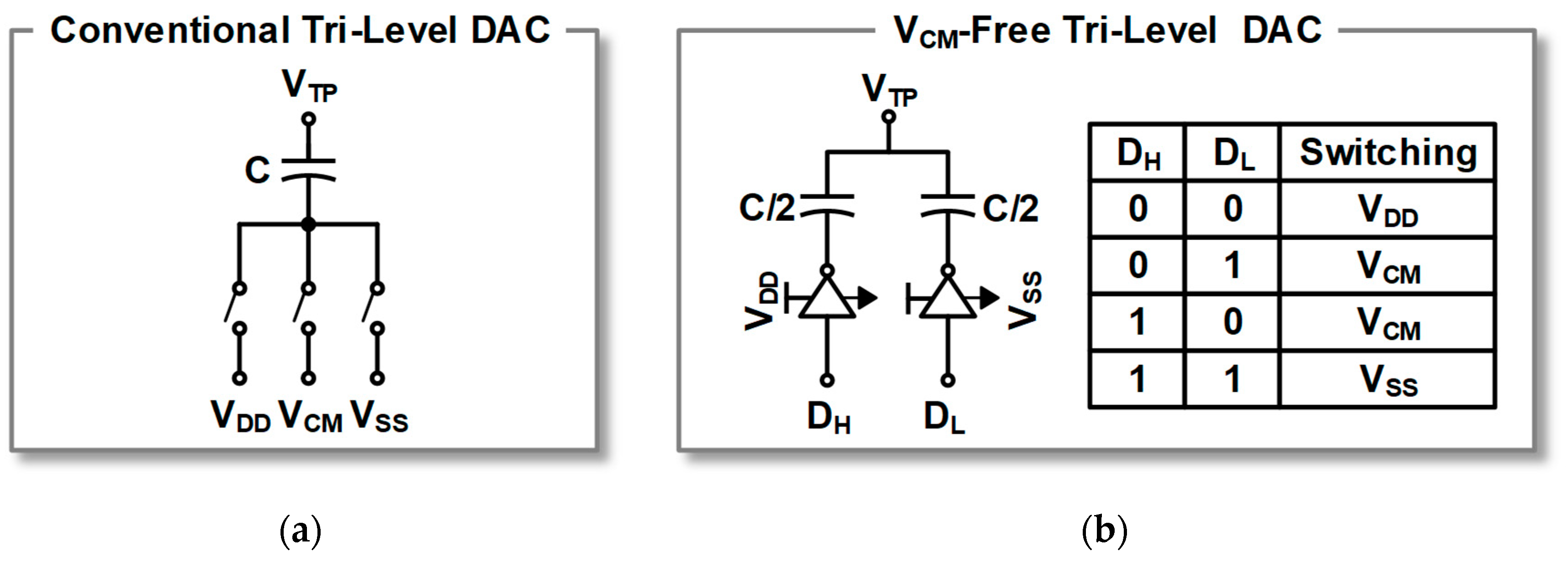

3.2. Phase Frequency Dectector-Based Phase Quantizer and VCM-Free Tri-Level Unit Capacitor

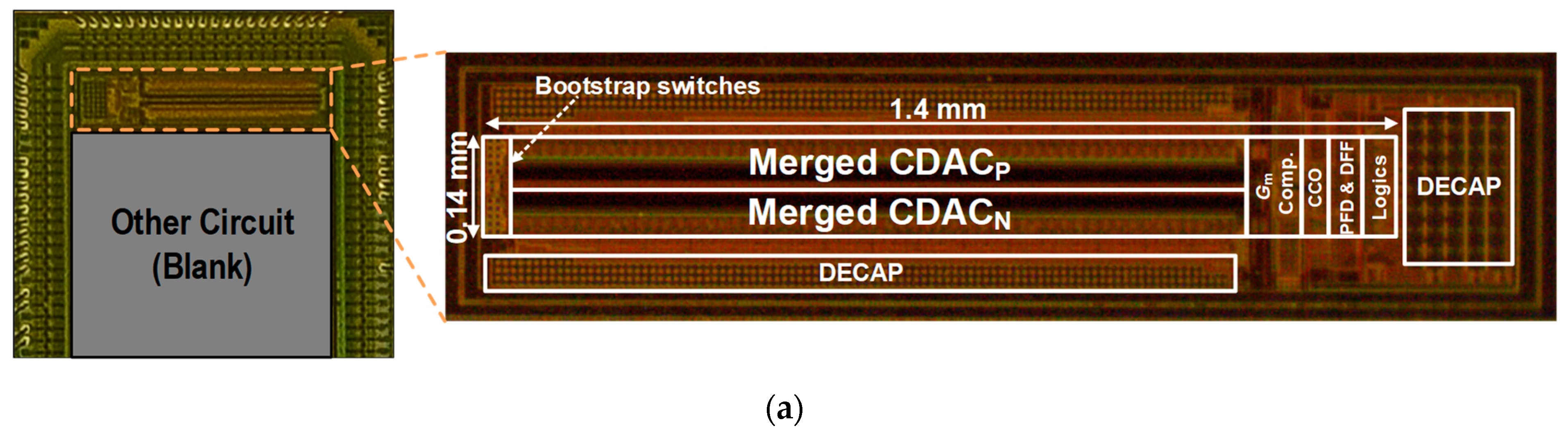

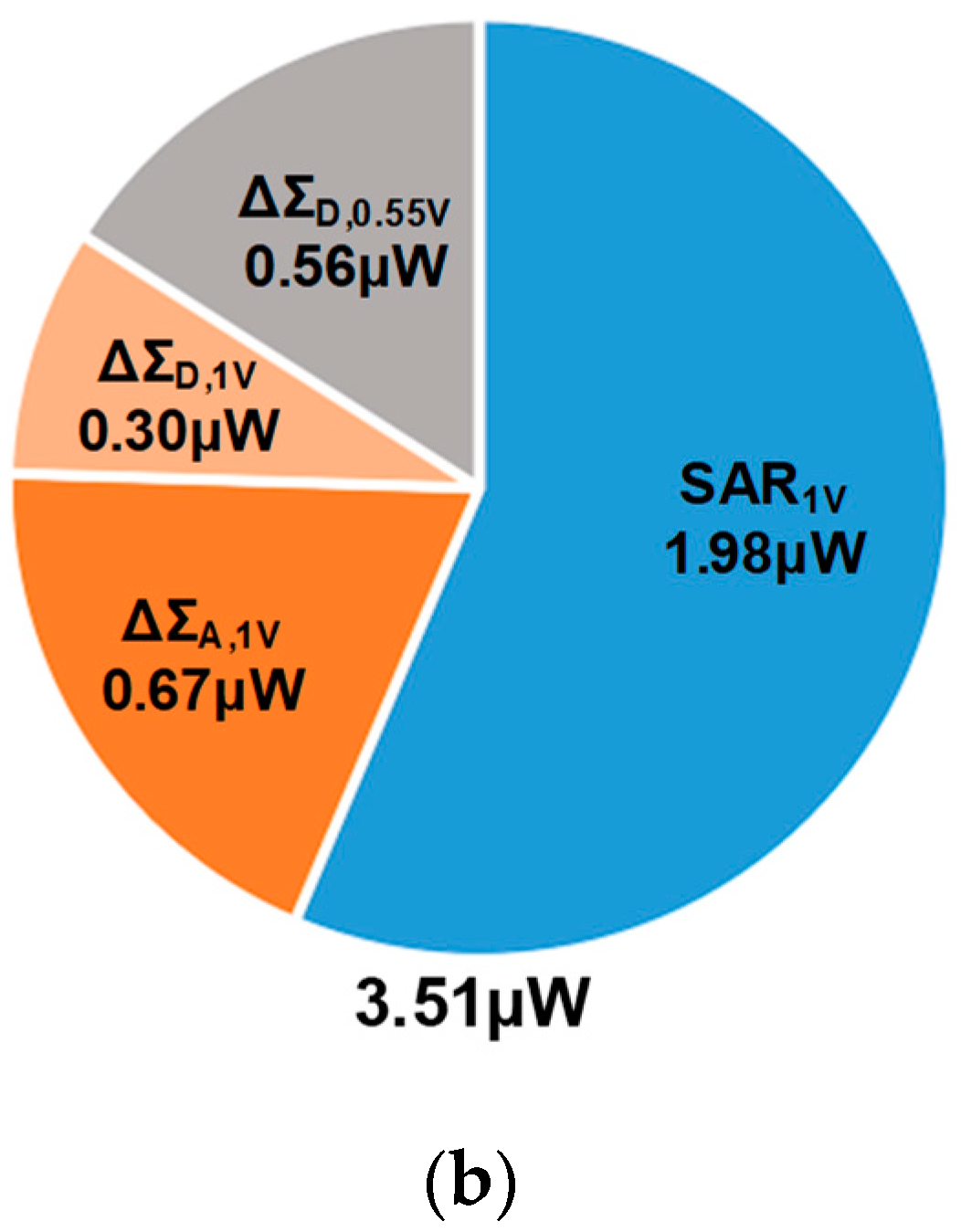

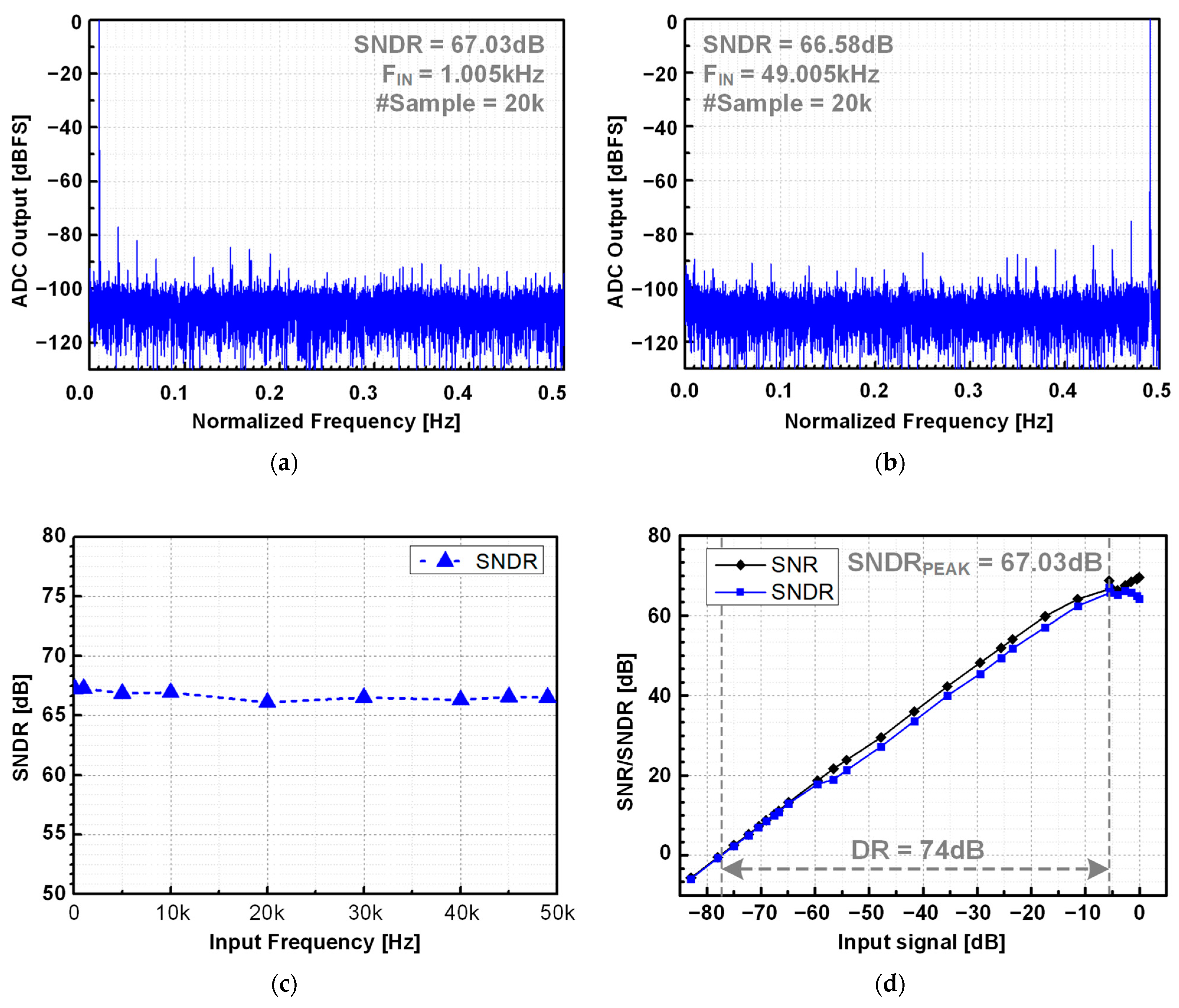

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Won, S.M.; Cai, L.; Gutruf, P.; Rogers, J.A. Wireless and battery-free technologies for neuroengineering. Nat. Biomed. Eng. 2021, 7, 405–423. [Google Scholar] [CrossRef] [PubMed]

- Yakovlev, A.; Kim, S.; Poon, A. Implantable biomedical devices: Wireless powering and communication. IEEE Commun. Mag. 2012, 50, 152–159. [Google Scholar] [CrossRef]

- Mendrela, A.E.; Park, S.-Y.; Voroslakos, M.; Flynn, M.P.; Yoon, E. A Battery-Powered Opto-Electrophysiology Neural Interface with Artifact-Preventing Optical Pulse Shaping. In Proceedings of the 2018 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–22 June 2018; pp. 125–126. [Google Scholar]

- Wang, H.; Wang, X.; Barfidokht, A.; Park, J.; Wang, J.; Mercier, P.P. A Battery-Powered Wireless Ion Sensing System Consuming 5.5 nW of Average Power. IEEE J. Solid-State Circuits 2018, 53, 2043–2053. [Google Scholar] [CrossRef]

- Azin, M.; Guggenmos, D.J.; Barbay, S.; Nudo, R.J.; Mohseni, P. A Battery-Powered Activity-Dependent Intracortical Microstimulation IC for Brain-Machine-Brain Interface. IEEE J. Solid-State Circuits 2011, 46, 731–745. [Google Scholar] [CrossRef]

- Seymour, J.P.; Wu, F.; Wise, K.D.; Yoon, E. State-of-the-art MEMS and microsystem tools for brain research. Microsyst. Nanoeng. 2017, 3, 16066. [Google Scholar] [CrossRef] [PubMed]

- Jochum, T.; Denison, T.; Wolf, P. Integrated Circuit Amplifiers for Multi-Electrode Intracortical Recording. J. Neural Eng. 2009, 6, 012001. [Google Scholar] [CrossRef]

- Oh, S.; Song, H.; Slager, N.; Ruiz, J.R.L.; Park, S.-Y.; Yoon, E. Power-Efficient LFP-Adaptive Dynamic Zoom-and-Track Incremental ΔΣ Front-End for Dual-Band Subcortical Recordings. IEEE Trans. Biomed. Circuits Syst. 2023, 17, 741–753. [Google Scholar] [CrossRef]

- Oh, S.; Kim, K.; Roberto, J.; Ruiz, L.; Slager, N.; Ko, E. A compact, ultrahigh-density headstage with high-fidelity hybrid integration for large-scale deep-brain opto-electrophysiology. bioRxiv 2023. [Google Scholar] [CrossRef]

- Park, S.-Y.; Cho, J.; Lee, K.; Yoon, E. Dynamic Power Reduction in Scalable Neural Recording Interface Using Spatiotemporal Correlation and Temporal Sparsity of Neural Signals. IEEE J. Solid-State Circuits 2018, 53, 1102–1114. [Google Scholar] [CrossRef]

- Park, S.-Y.; Cho, J.; Na, K.; Yoon, E. Modular 128-Channel Δ − ΔΣ Analog Front-End Architecture Using Spectrum Equalization Scheme for 1024-Channel 3-D Neural Recording Microsystems. IEEE J. Solid-State Circuits 2017, 53, 501–514. [Google Scholar] [CrossRef]

- Huang, X.; Londoño-Ramírez, H.; Ballini, M.; Van Hoof, C.; Genoe, J.; Haesler, S.; Gielen, G.; Van Helleputte, N.; Lopez, C.M. A 256-Channel Actively-Multiplexed μECoG Implant with Column-Parallel Incremental ΔΣ ADCs Employing Bulk-DACs in 22-nm FDSOI Technology. In Proceedings of the 2022 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 20–26 February 2023; pp. 22–24. [Google Scholar] [CrossRef]

- Sadollahi, M.; Hamashita, K.; Sobue, K.; Temes, G.C. An 11-Bit 250-nW 10-kS/s SAR ADC With Doubled Input Range for Biomedical Applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 65, 61–73. [Google Scholar]

- Hariprasath, V.; Guerber, J.; Lee, S.-H.; Moon, U.-K. Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electron. Lett. 2010, 46, 620–621. [Google Scholar] [CrossRef]

- Hsieh, S.-E.; Hsieh, C.-C. A 0.44-fJ/Conversion-Step 11-Bit 600-kS/s SAR ADC With Semi-Resting DAC. IEEE J. Solid-State Circuits 2018, 53, 2595–2603. [Google Scholar] [CrossRef]

- Chae, Y.; Souri, K.; Makinwa, K.A.A. A 6.3 µW 20 bit Incremental Zoom-ADC with 6 ppm INL and 1 µV Offset. IEEE J. Solid-State Circuits 2013, 48, 3019–3027. [Google Scholar] [CrossRef]

- Straayer, M.Z.; Perrott, M.H.; Concepts, A.B. A 12-Bit, 10-MHz Bandwidth, Continuous-Time Sigma-Delta ADC with a 5-Bit, 950-MS/s VCO-Based Quantizer. IEEE J. Solid-State Circuits 2009, 43, 805–814. [Google Scholar] [CrossRef]

- Lee, K.; Yoon, Y.; Sun, N. A Scaling-Friendly Low-Power Small-Area ΔΣ ADC With VCO-Based Integrator and Intrinsic Mismatch Shaping Capability. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 561–573. [Google Scholar] [CrossRef]

- Tang, X.; Li, S.; Yang, X.; Shen, L.; Zhao, W.; Williams, R.P.; Liu, J.; Tan, Z.; Hall, N.A.; Pan, D.Z.; et al. An Energy-Efficient Time-Domain Incremental Capacitance-to-Digital Converter. IEEE J. Solid-State Circuits 2020, 55, 3064–3075. [Google Scholar] [CrossRef]

- Sanyal, A.; Sun, N. An Energy-Efficient Hybrid SAR-VCO ΔΣ Capacitance-to-Digital Converter in 40-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 1966–1976. [Google Scholar] [CrossRef]

- Liu, H.; Guo, T.; Yan, P.; Qi, L.; Chen, M.; Wang, G.; Liu, Y. A Hybrid 1st/2nd-order VCO-based CTDSM with Rail-to-Rail Artifact Tolerance for Bidirectional Neural Interface. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 2682–2686. [Google Scholar] [CrossRef]

- Hsieh, S.-E.; Hsieh, C.-C. A 0.4-V 13-bit 270-kS/s SAR-ISDM ADC With Opamp-Less Time-Domain Integrator. IEEE J. Solid-State Circuits 2019, 54, 1648–1656. [Google Scholar] [CrossRef]

- Markus, J.; Silva, J.; Temes, G. Theory and Applications of Incremental ΔΣ Converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2004, 51, 678–690. [Google Scholar] [CrossRef]

- Hsieh, C.; Liu, S. A 0.3V 10bit 7.3fJ/conversion-step SAR ADC in 0.18 μm CMOS. In Proceedings of the 2014 IEEE Asian Solid-State Circuits Conference (A-SSCC), KaoHsiung, Taiwan, 10–12 November 2014; pp. 31–34. [Google Scholar] [CrossRef]

- Ham, D.; Hajimiri, A. Virtual damping and einstein relation in oscillators. IEEE J. Solid-State Circuits 2003, 38, 407–418. [Google Scholar] [CrossRef]

- Eland, E.; Karmakar, S.; Gonen, B.; van Veldhoven, R.; Makinwa, K.A.A. A 440-μW, 109.8-dB DR, 106.5-dB SNDR Discrete-Time Zoom ADC With a 20-kHz BW. IEEE J. Solid-State Circuits 2021, 56, 1207–1215. [Google Scholar] [CrossRef]

- Karmakar, S.; Gonen, B.; Sebastiano, F.; van Veldhoven, R.; Makinwa, K.A.A. A 280 µW Dynamic Zoom ADC With 120 dB DR and 118 dB SNDR in 1 kHz BW. IEEE J. Solid-State Circuits 2018, 53, 3497–3507. [Google Scholar] [CrossRef]

- Harpe, P.J.A.; Zhou, C.; Bi, Y.; van der Meijs, N.P.; Wang, X.; Philips, K.; Dolmans, G.; de Groot, H. A 26 μW 8 bit 10 MS/s Asynchronous SAR ADC for Low Energy Radios. IEEE J. Solid-State Circuits 2011, 46, 1585–1595. [Google Scholar] [CrossRef]

- Li, S.; Mukherjee, A.; Sun, N. A 174.3-dB FoM VCO-Based CT ΔΣ Modulator with a Fully-Digital Phase Extended Quantizer and Tri-Level Resistor DAC in 130-nm CMOS. IEEE J. Solid-State Circuits 2017, 52, 1940–1952. [Google Scholar] [CrossRef]

- Zhong, Y.; Tang, X.; Liu, J.; Zhao, W.; Li, S.; Sun, N. An 81.5dB-DR 1.25MHz-BW VCO-Based CT ΔΣ ADC with Double-PFD Quantizer. In Proceedings of the 2021 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 25–30 April 2021; pp. 5–6. [Google Scholar] [CrossRef]

- Omran, H.; Alahmadi, H.; Salama, K.N. Matching Properties of Femtofarad MOM Capacitors. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 763–772. [Google Scholar] [CrossRef]

- Zhao, W.; Li, S.; Xu, B.; Yang, X.; Tang, X.; Shen, L.; Lu, N.; Pan, D.Z.; Sun, N. A 0.025-mm2 0.8V 78.5dB VCO-Based Sensor Readout Circuit in a Hybrid PLL-ΔΣ M Structure. IEEE J. Solid-State Circuits 2019, 55, 666–679. [Google Scholar] [CrossRef]

- Hu, J.; Li, D.; Liu, M.; Zhu, Z. A 10-kS/s 625-Hz-Bandwidth 65-dB SNDR Second-Order Noise-Shaping SAR ADC for Biomedical Sensor Applications. IEEE Sens. J. 2019, 20, 13881–13891. [Google Scholar] [CrossRef]

- Moon, C.W.; Yoon, K.S.; Lee, J. A 12~14-Bit SAR-SS Hybrid ADC with SS Bit Shifting Resolution Reconfigurable Method for Bio-Signal Processing. Electronics 2023, 12, 4916. [Google Scholar] [CrossRef]

- Zhang, Q.; Ning, N.; Zhang, Z.; Li, J.; Wu, K.; Yu, Q. A 12-Bit Two-Step Single-Slope ADC With a Constant Input-Common-Mode Level Resistor Ramp Generator. IEEE Trans. Very Large Scale Integr. Syst. 2022, 30, 644–655. [Google Scholar] [CrossRef]

- Hu, Y.; Huang, Q.; Tang, B.; Chen, C.; Hu, L.; Yu, E.; Li, B.; Wu, Z. A Low-Power SAR ADC with Capacitor-Splitting Energy-Efficient Switching Scheme for Wearable Biosensor Applications. Micromachines 2023, 14, 2244. [Google Scholar] [CrossRef] [PubMed]

| [21] | [33] | [34] | [35] | [36] | This Work | |

|---|---|---|---|---|---|---|

| Process (nm) | 40 | 180 | 28 | 130 | 180 | 180 |

| Architecture | SAR + VCO | NS-SAR | SAR-SS | TS SS | SAR | SAR + I-ΔΣM |

| Supply (V) | 1.8 | 1 | 1 | 3.3/1.2 | 1 | 1.0(A)/0.55(D) |

| Power (μW) | 4100 | 0.09 | 34 | 62 | 4.45 | 3.51 |

| SNDR (dB) | 75.7 | 65 | 66.8 * | 60.78 | 61.77 | 67 |

| BW (kHz) | 3500 | 0.625 | 20 | 50 | 100 | 50 |

| ENOB (bits) | 12.28 | 10.5 | 10.81 | 9.8 | 9.97 | 10.84 |

| FoMW 1 (fJ/conv.) | 382 | 50 | 53 | 696 | 22.2 | 19.12 |

| FoMS 2 (dB) | 165 * | 163 * | 164 * | 150 * | 165 * | 168.5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, J.; Park, S.-Y. An Energy-Efficient 12-Bit VCO-Based Incremental Zoom ADC with Fast Phase-Alignment Scheme for Multi-Channel Biomedical Applications. Electronics 2024, 13, 1754. https://doi.org/10.3390/electronics13091754

Kim J, Park S-Y. An Energy-Efficient 12-Bit VCO-Based Incremental Zoom ADC with Fast Phase-Alignment Scheme for Multi-Channel Biomedical Applications. Electronics. 2024; 13(9):1754. https://doi.org/10.3390/electronics13091754

Chicago/Turabian StyleKim, Joongyu, and Sung-Yun Park. 2024. "An Energy-Efficient 12-Bit VCO-Based Incremental Zoom ADC with Fast Phase-Alignment Scheme for Multi-Channel Biomedical Applications" Electronics 13, no. 9: 1754. https://doi.org/10.3390/electronics13091754

APA StyleKim, J., & Park, S.-Y. (2024). An Energy-Efficient 12-Bit VCO-Based Incremental Zoom ADC with Fast Phase-Alignment Scheme for Multi-Channel Biomedical Applications. Electronics, 13(9), 1754. https://doi.org/10.3390/electronics13091754