Nonlinear Capacitance Compensation Method for Integrating a Metal–Semiconductor–Metal Varactor with a Gallium Nitride High Electron Mobility Transistor Power Amplifier

Abstract

1. Introduction

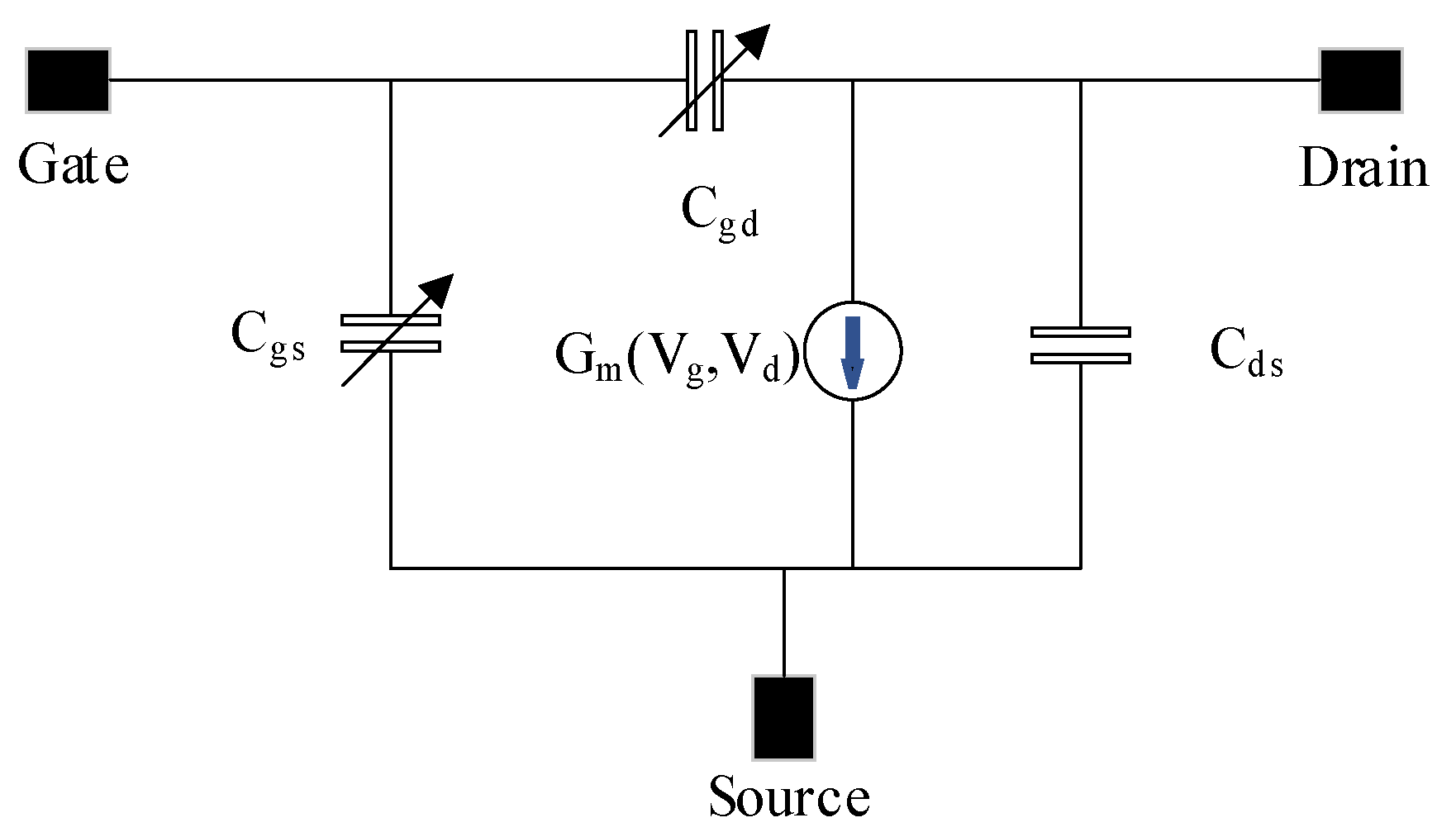

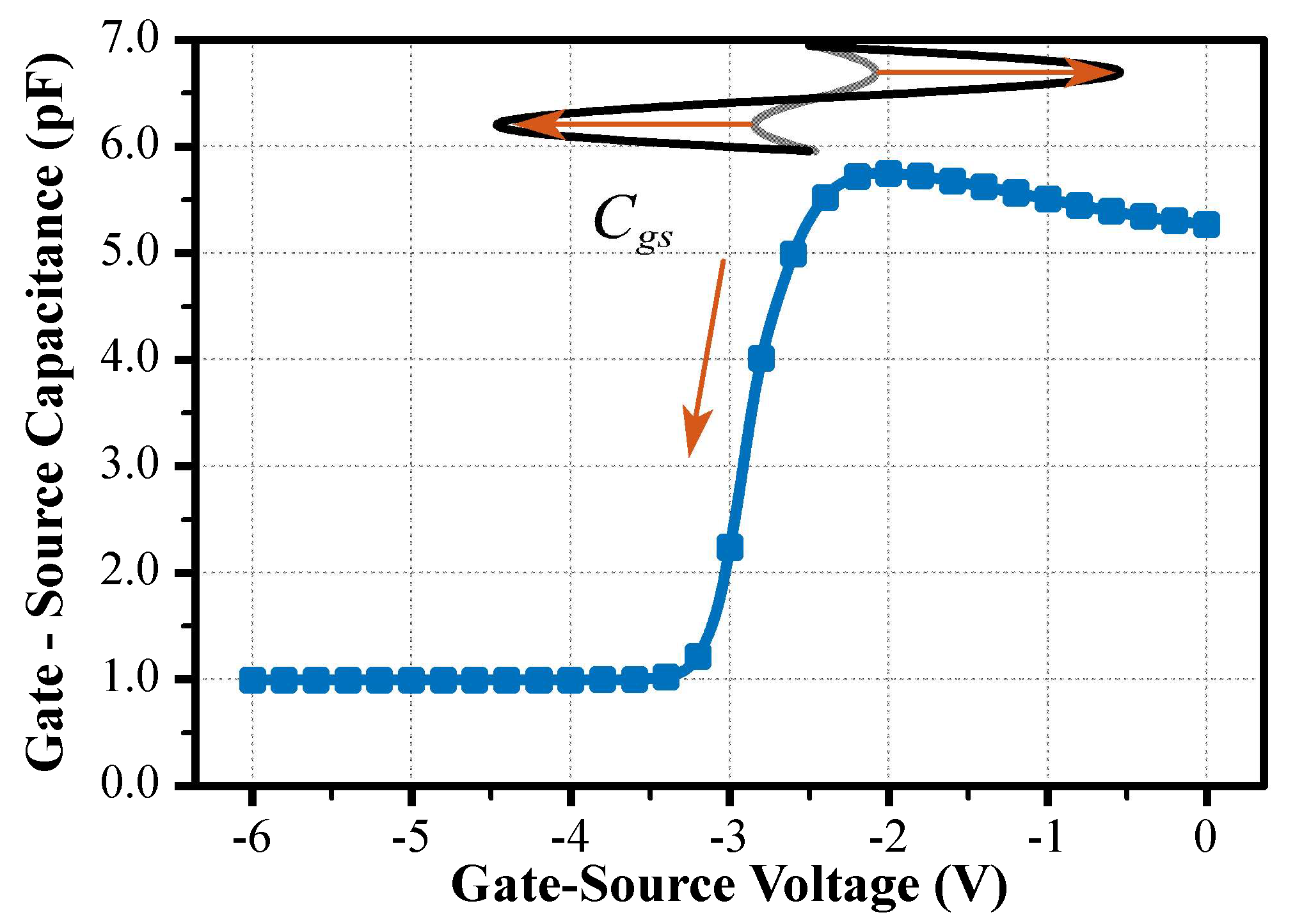

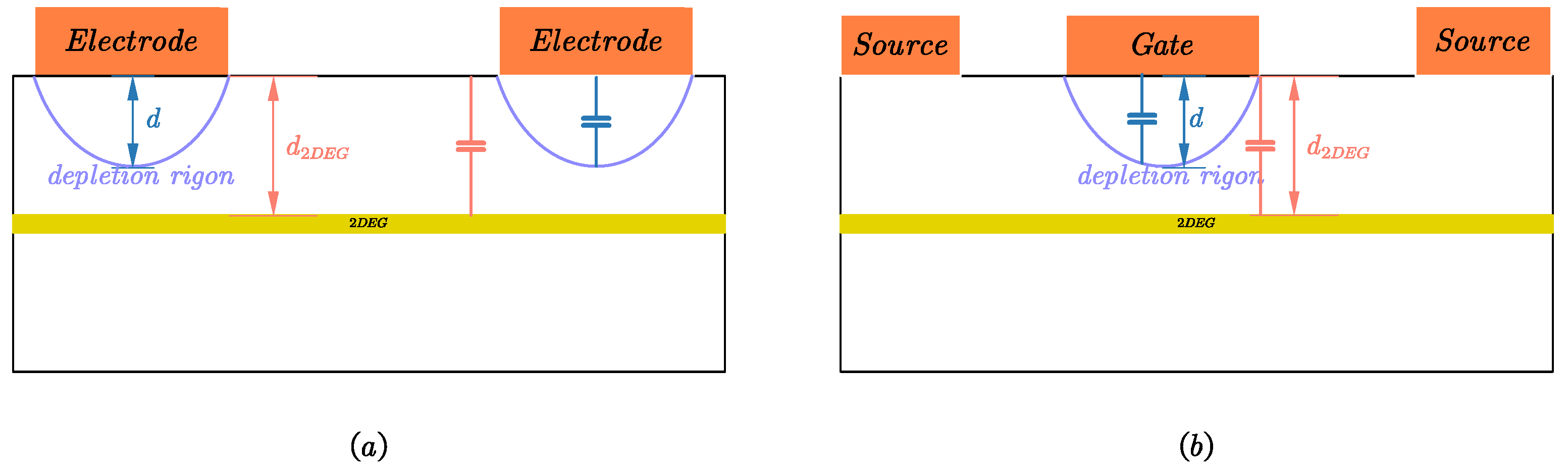

2. The Nonlinearity Generated by the Input Capacitance

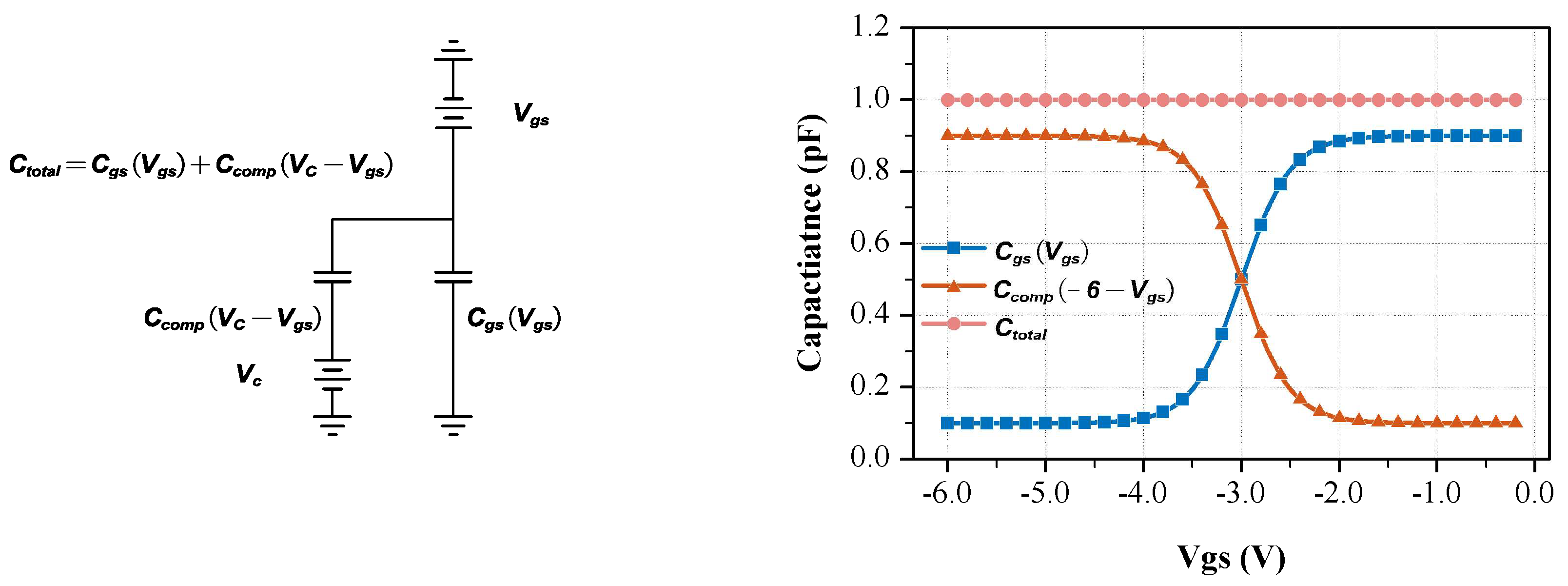

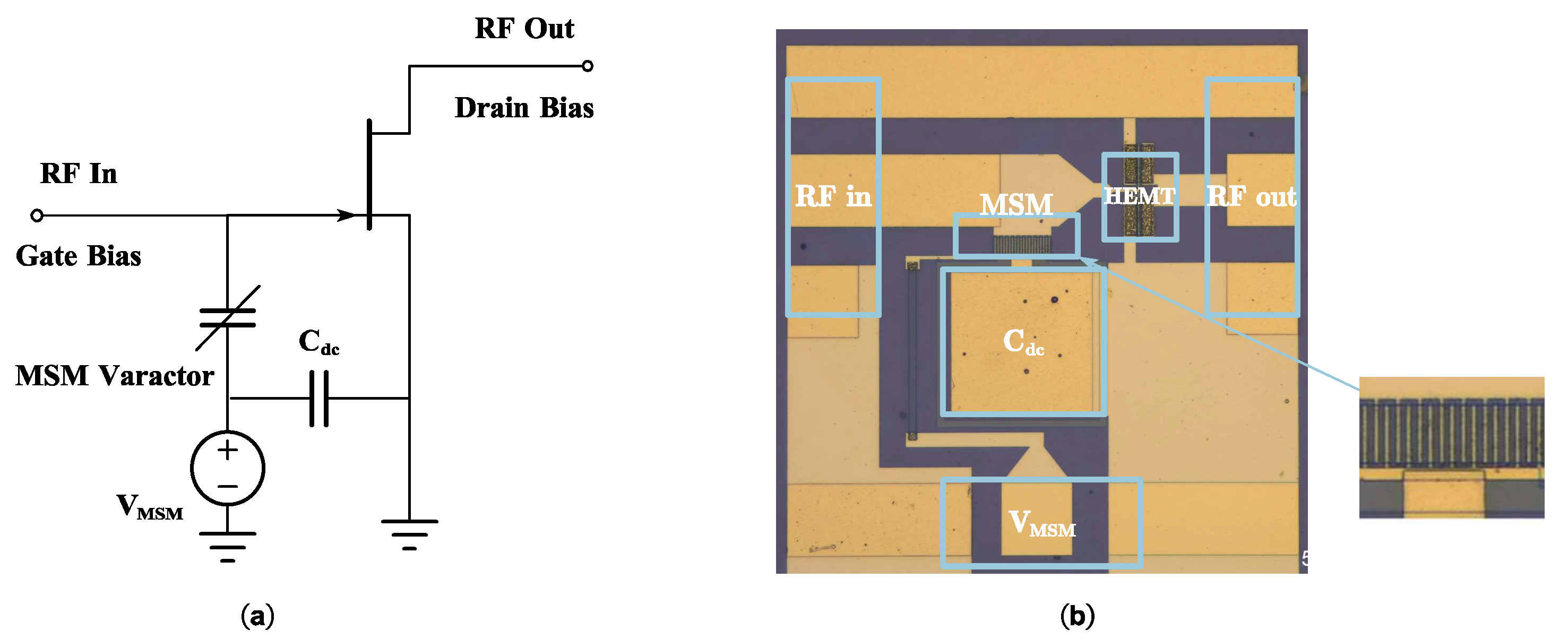

3. Proposed Capacitance Compensation Method

4. Implementation

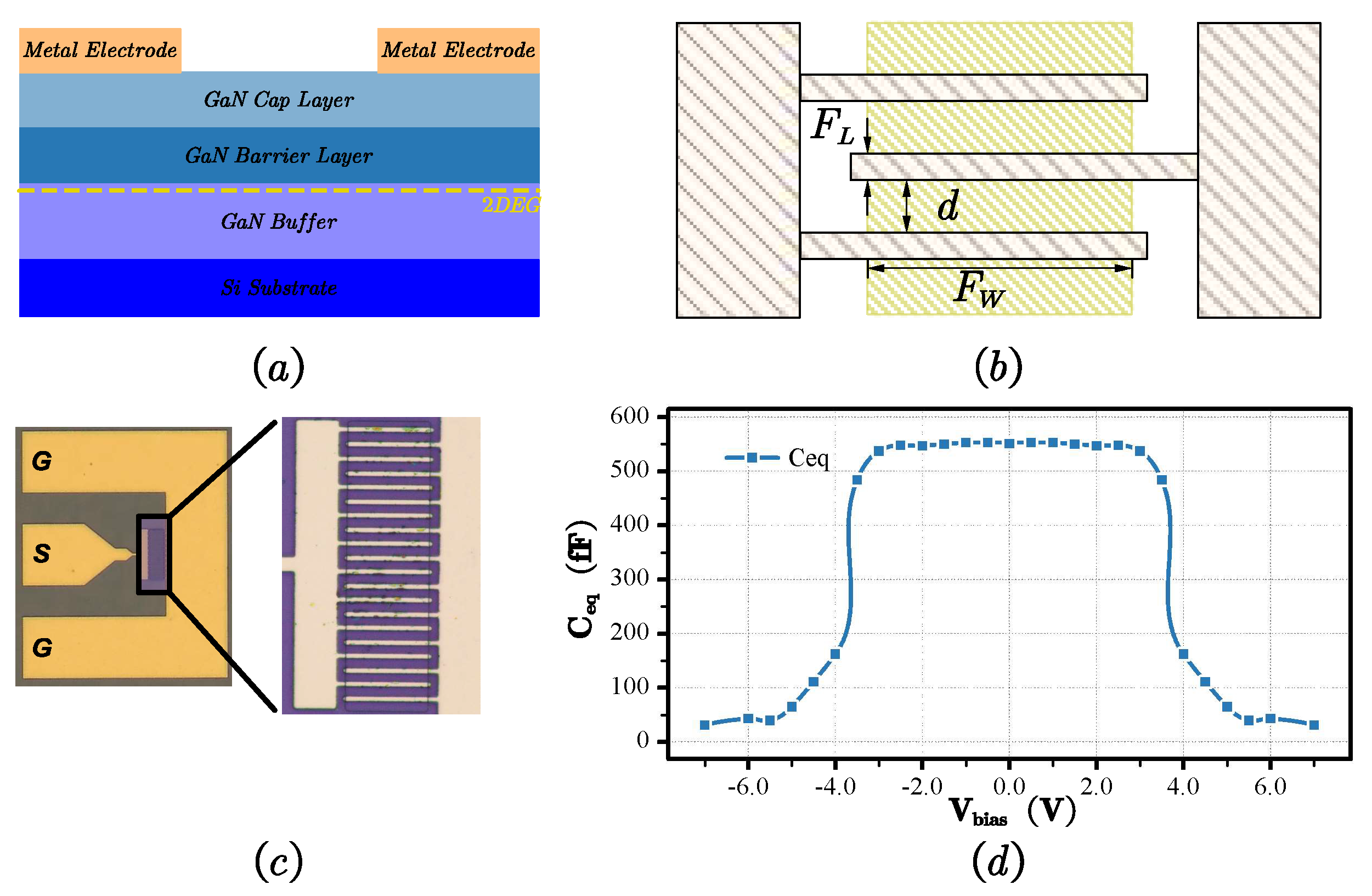

4.1. Fabrication

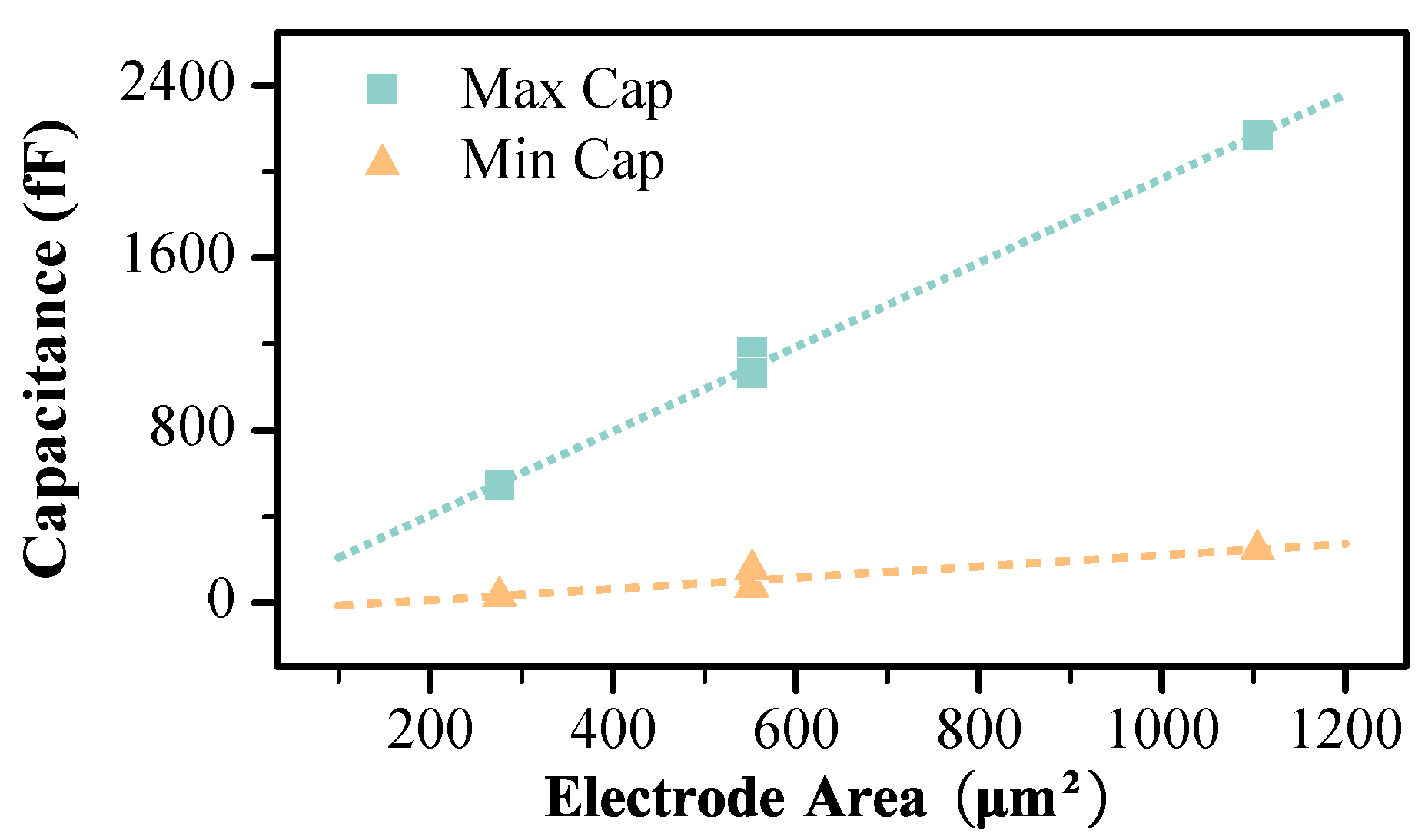

4.2. Device Design

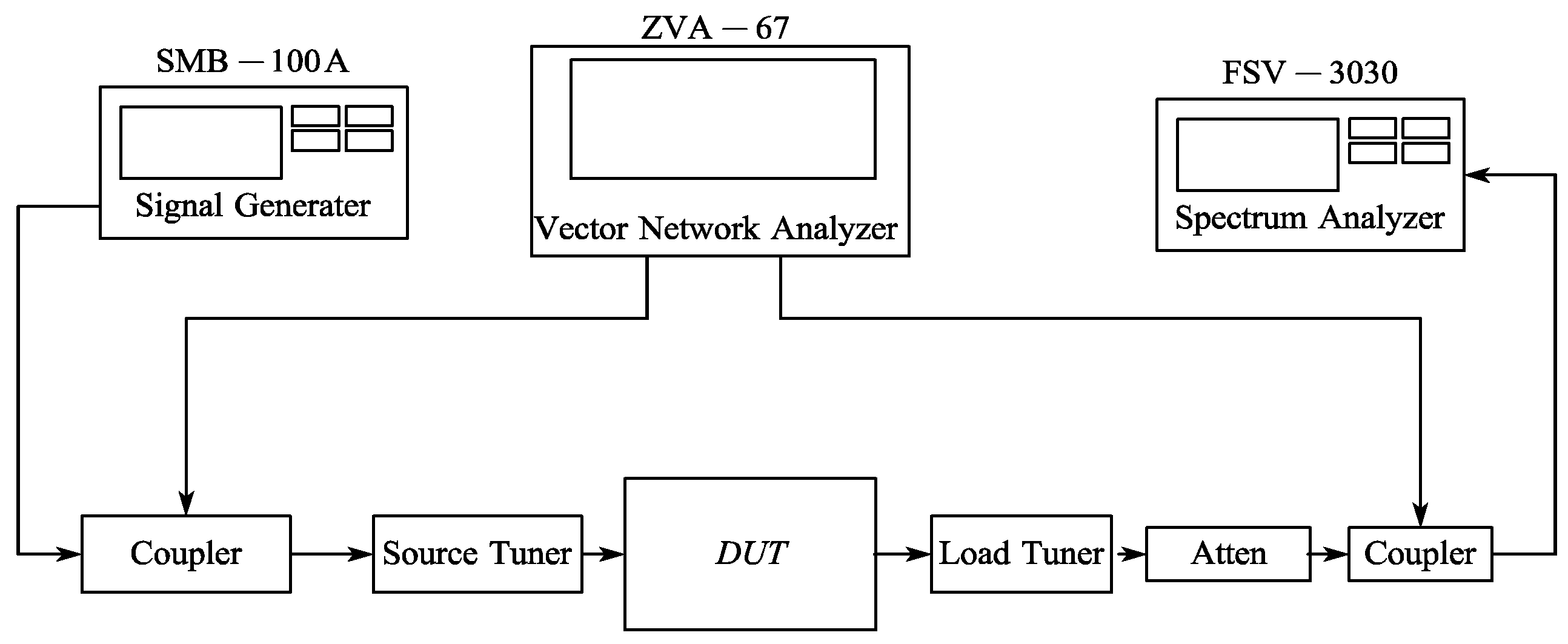

5. Measurement Results

5.1. Small-Signal Measurements

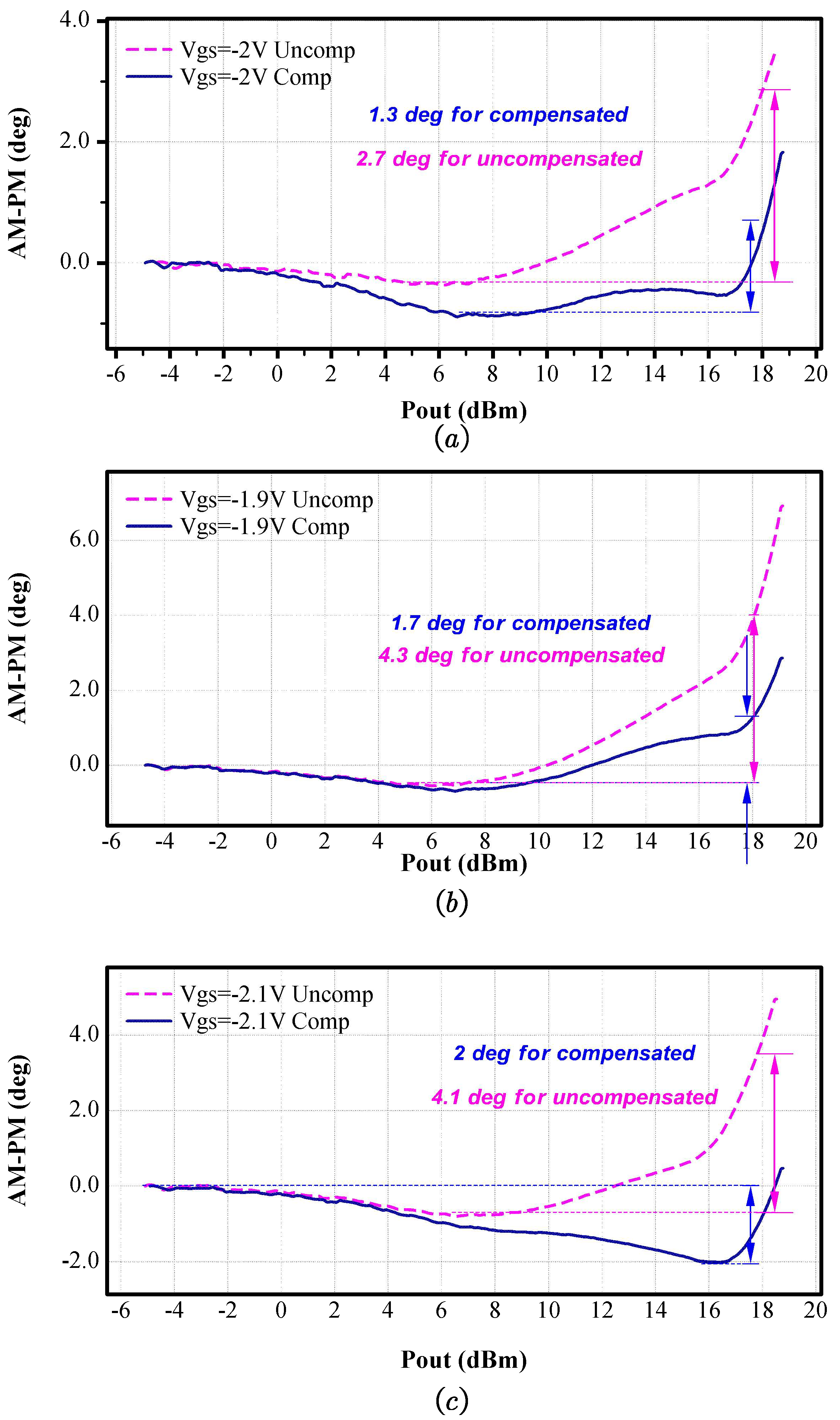

5.2. Single-Tone RF Power Measurement

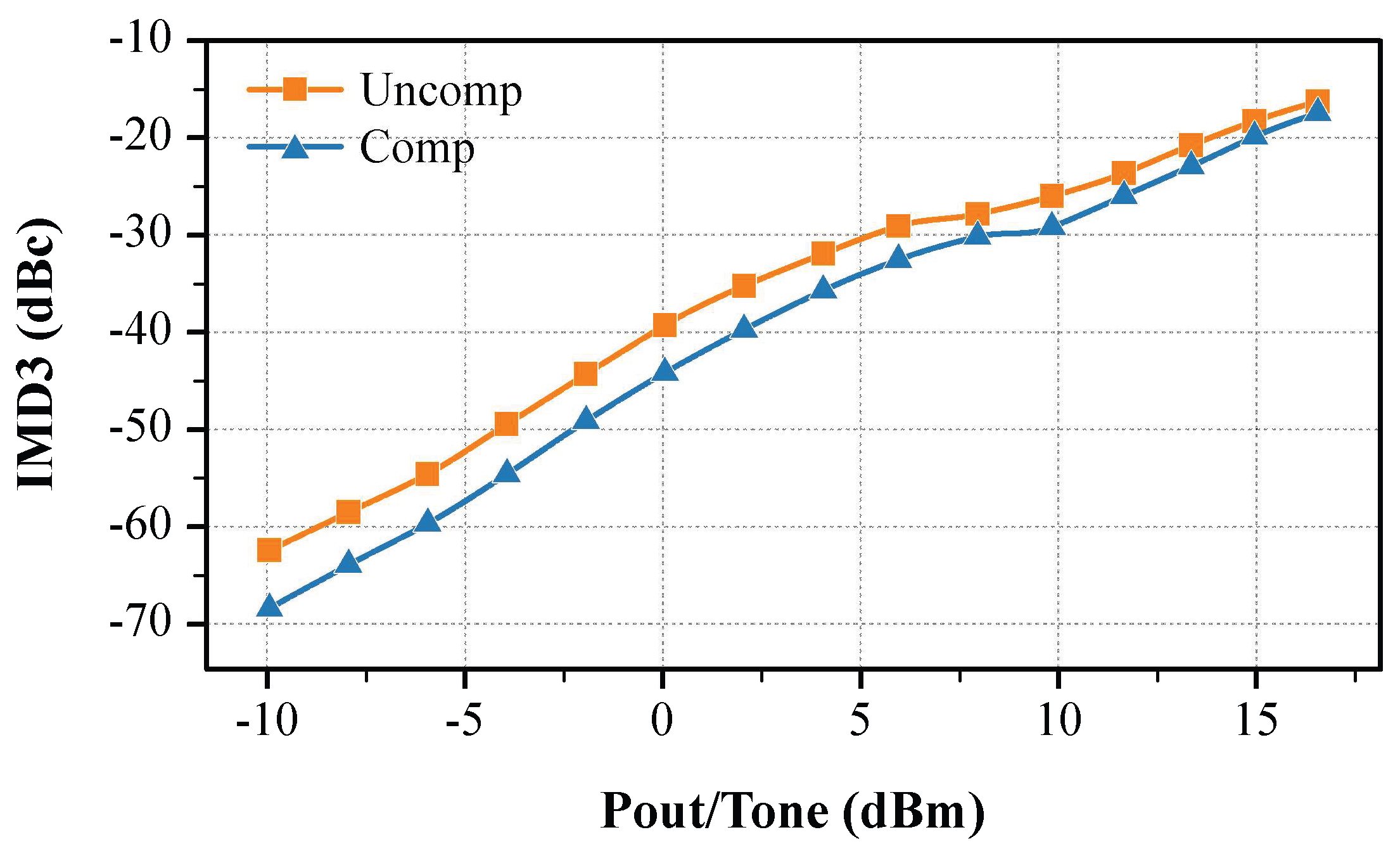

5.3. Two-Tone Measurement

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Inoue, A. Millimeter-Wave GaN Devices for 5G: Massive MIMO Antenna Arrays for Sub-6-Ghz and Mm-Wave Bandwidth. IEEE Microw. Mag. 2021, 22, 100–110. [Google Scholar] [CrossRef]

- Campbell, C.; Lee, C.; Williams, V.; Kao, M.-Y.; Tserng, H.-Q.; Saunier, P.; Balisteri, T. A Wideband Power Amplifier MMIC Utilizing GaN on SiC HEMT Technology. IEEE J. Solid-State Circuits 2009, 44, 2640–2647. [Google Scholar] [CrossRef]

- van Heijningen, M.; de Hek, P.; Dourlens, C.; Fellon, P.; Adamiuk, G.; Ayllon, N.; van Vliet, F. C-Band Single-Chip Radar Front-End in AlGaN/GaN Technology. IEEE Trans. Microw. Theory Tech. 2017, 65, 4428–4437. [Google Scholar] [CrossRef]

- Mengozzi, M.; Gibiino, G.P.; Angelotti, A.M.; Florian, C.; Santarelli, A. GaN Power Amplifier Digital Predistortion by Multi-Objective Optimization for Maximum RF Output Power. Electronics 2021, 10, 244. [Google Scholar] [CrossRef]

- Joo, T.; Koo, B.; Hong, S. A WLAN RF CMOS PA with Large-Signal MGTR Method. IEEE Trans. Microw. Theory Tech. 2013, 61, 1272–1279. [Google Scholar] [CrossRef]

- Cai, Q.; Che, W.; Ma, K.; Zhang, M. A Simplified Transistor-Based Analog Predistorter for a GaN Power Amplifier. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 326–330. [Google Scholar] [CrossRef]

- Lim, K.H.; Ahn, G.; Jung, S.; Park, H.C.; Kim, M.S.; Van, J.H.; Cho, H.; Jeong, J.-H.; Park, C.-S.; Yang, Y. A 60-W Multicarrier WCDMA Power Amplifier Using an RF Predistorter. IEEE Trans. Circuits Syst. II Express Briefs 2009, 56, 265–269. [Google Scholar] [CrossRef]

- Wang, C.; Vaidyanathan, M.; Larson, L.E. A Capacitance-Compensation Technique for Improved Linearity in CMOS Class-AB Power Amplifiers. IEEE J. Solid-State Circuits 2004, 39, 1927–1937. [Google Scholar] [CrossRef]

- Vigilante, M.; Reynaert, P. A Wideband Class-AB Power Amplifier With 29–57-GHz AM–PM Compensation in 0.9-V 28-Nm Bulk CMOS. IEEE J. Solid-State Circuits 2018, 53, 1288–1301. [Google Scholar] [CrossRef]

- Cripps, S.C. RF Power Amplifiers for Wireless Communications; Artech House Publishers: Norwood, MA, USA, 2006. [Google Scholar]

- Nunes, L.C.; Cabral, P.M.; Pedro, J.C. AM/AM and AM/PM Distortion Generation Mechanisms in Si LDMOS and GaN HEMT Based RF Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2014, 62, 799–809. [Google Scholar] [CrossRef]

- Golara, S.; Moloudi, S.; Abidi, A.A. Processes of AM-PM Distortion in Large-Signal Single-FET Amplifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 245–260. [Google Scholar] [CrossRef]

- Marso, M.; Wolter, M.; Javorka, P.; Fox, A.; Kordoš, P. AlGaN/GaN Varactor Diode for Integration in HEMT Circuits. Electron. Lett. 2001, 37, 1476. [Google Scholar] [CrossRef]

- Marso, M.; Fox, A.; Heidelberger, G.; Kordos, P.; Luth, H. Comparison of AlGaN/GaN MSM Varactor Diodes Based on HFET and MOSHFET Layer Structures. IEEE Electron Device Lett. 2006, 27, 945–947. [Google Scholar] [CrossRef][Green Version]

- Yoon, Y.J.; Seo, J.H.; Cho, M.S.; Kang, H.-S.; Won, C.-H.; Kang, I.M.; Lee, J.-H. TMAH-Based Wet Surface Pre-Treatment for Reduction of Leakage Current in AlGaN/GaN MIS-HEMTs. Solid-State Electron. 2016, 124, 54–57. [Google Scholar] [CrossRef]

- Lu, X.; Jiang, H.; Liu, C.; Zou, X.; Lau, K.M. Off-State Leakage Current Reduction in AlGaN/GaN High Electron Mobility Transistors by Combining Surface Treatment and Post-Gate Annealing. Semicond. Sci. Technol. 2016, 31, 055019. [Google Scholar] [CrossRef]

- San Chu, C.; Zhou, Y.; Chen, K.J.; Lau, K.M. Q-Factor Characterization of RF GaN-Based Metal-Semiconductor-Metal Planar Interdigitated Varactor. IEEE Electron Device Lett. 2005, 26, 432–434. [Google Scholar] [CrossRef]

- Hsieh, Y.-L.; Lo, H.-Z.; Nee, T.-E.; Chang, C.-N.; Yang, C.-H. Study on Epitaxial Structure and Substrate Material Variations for Improving Electrical Reliability of the MSM AlGaN/GaN 2DEG Varactors. Microelectron. Reliab. 2023, 142, 114905. [Google Scholar] [CrossRef]

- Sarbishaei, H.; Wu, D.Y.-T.; Boumaiza, S. Linearity of GaN HEMT RF Power Amplifiers—A Circuit Perspective. In Proceedings of the 2012 IEEE/MTT-S International Microwave Symposium Digest 2012, Montreal, QC, Canada, 17–22 June 2012. [Google Scholar] [CrossRef]

| N | FL (µm) | FW (µm) | Cmin (fF) | Cmax (fF) | Cmax/Cmin |

|---|---|---|---|---|---|

| 10 | 1.2 | 23 | 30 | 550 | 18.33 |

| 10 | 1.2 | 46 | 74.1 | 1160 | 15.65 |

| 20 | 1.2 | 23 | 154.8 | 1065 | 6.879 |

| 20 | 1.2 | 46 | 246.9 | 2170 | 8.788 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, K.; Gu, Y.; Guo, H.; Zou, X. Nonlinear Capacitance Compensation Method for Integrating a Metal–Semiconductor–Metal Varactor with a Gallium Nitride High Electron Mobility Transistor Power Amplifier. Electronics 2024, 13, 1265. https://doi.org/10.3390/electronics13071265

Li K, Gu Y, Guo H, Zou X. Nonlinear Capacitance Compensation Method for Integrating a Metal–Semiconductor–Metal Varactor with a Gallium Nitride High Electron Mobility Transistor Power Amplifier. Electronics. 2024; 13(7):1265. https://doi.org/10.3390/electronics13071265

Chicago/Turabian StyleLi, Ke, Yitian Gu, Haowen Guo, and Xinbo Zou. 2024. "Nonlinear Capacitance Compensation Method for Integrating a Metal–Semiconductor–Metal Varactor with a Gallium Nitride High Electron Mobility Transistor Power Amplifier" Electronics 13, no. 7: 1265. https://doi.org/10.3390/electronics13071265

APA StyleLi, K., Gu, Y., Guo, H., & Zou, X. (2024). Nonlinear Capacitance Compensation Method for Integrating a Metal–Semiconductor–Metal Varactor with a Gallium Nitride High Electron Mobility Transistor Power Amplifier. Electronics, 13(7), 1265. https://doi.org/10.3390/electronics13071265