A Reconfigurable SRAM CRP PUF with High Reliability and Randomness

Abstract

1. Introduction

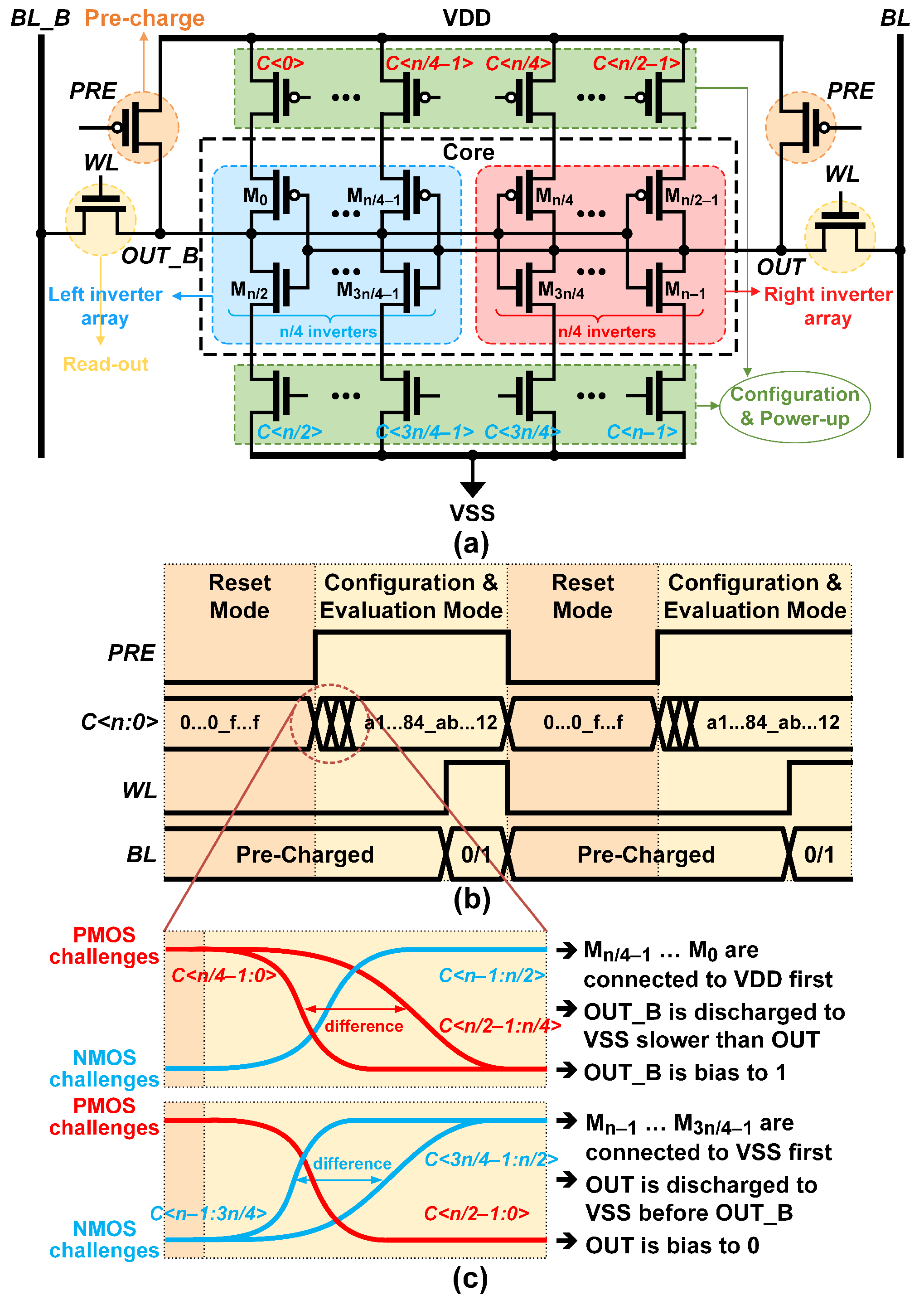

2. Conventional SRAM CRP PUF

2.1. Structure and Operation Principle

2.2. Existing Issue

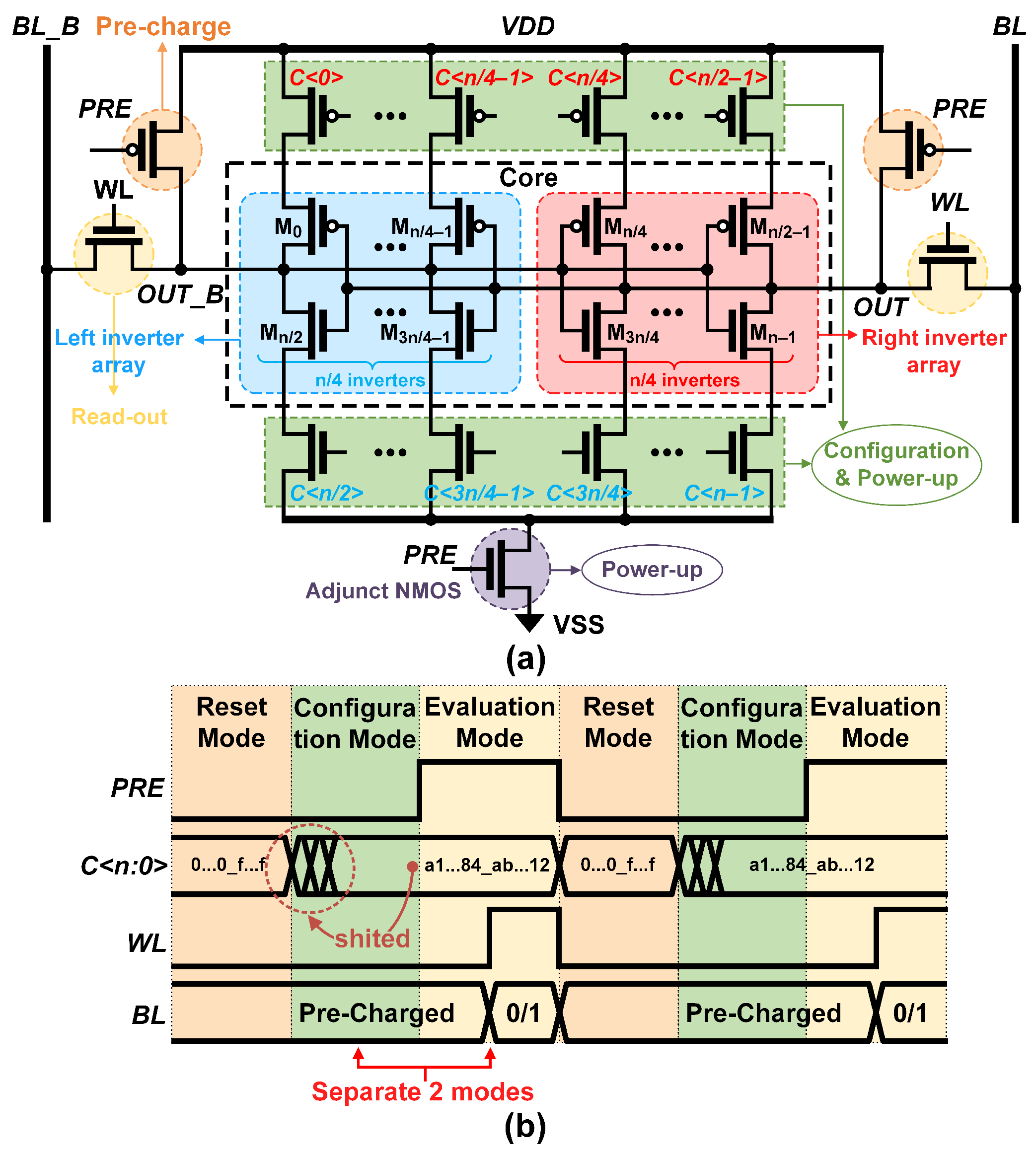

3. Proposed SRAM CRP PUF

3.1. Proposed Precise Timing Scheme for Ideal Random Response

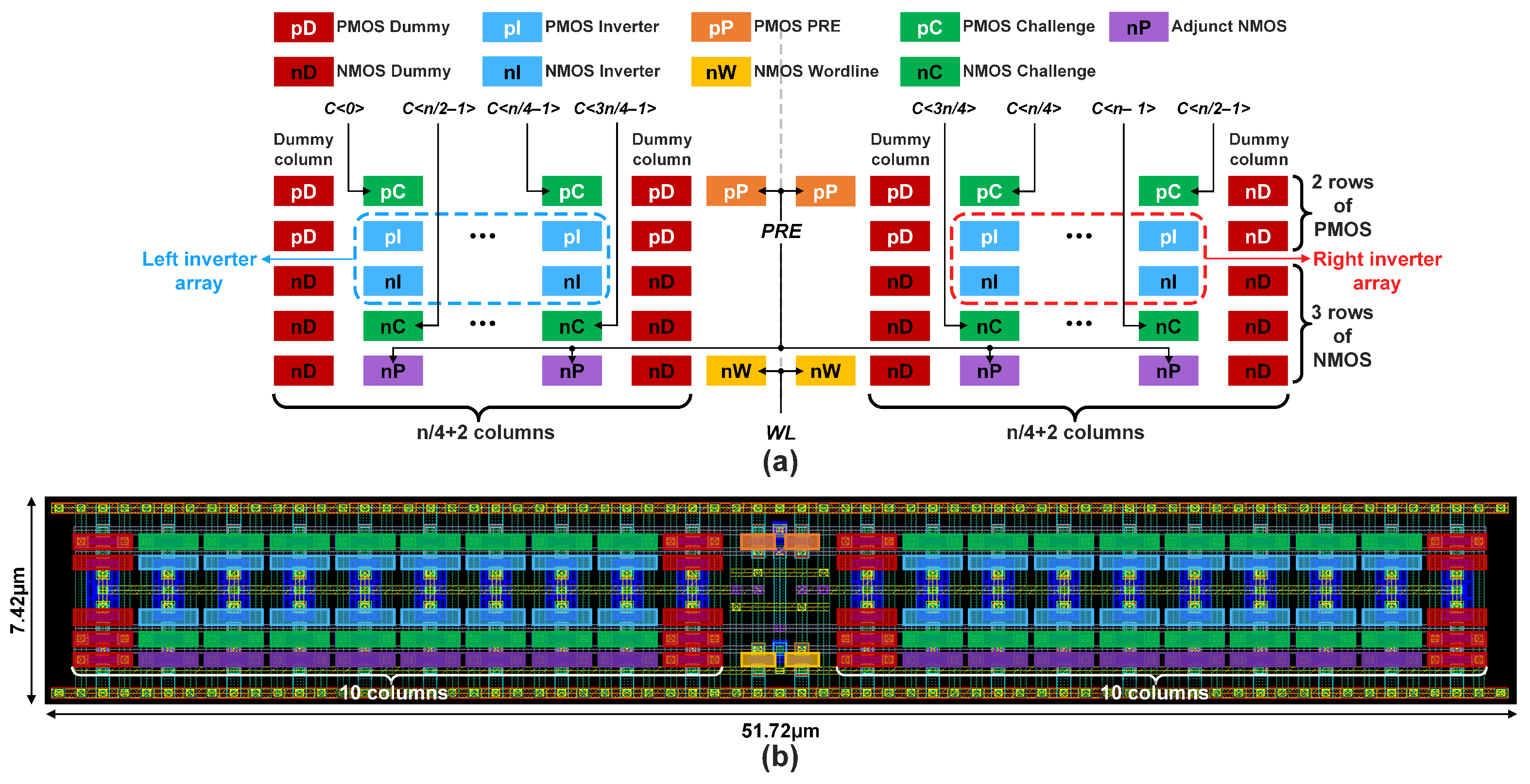

3.2. Symmetrical Layout Design Technique

3.3. Simulation Results Comparison

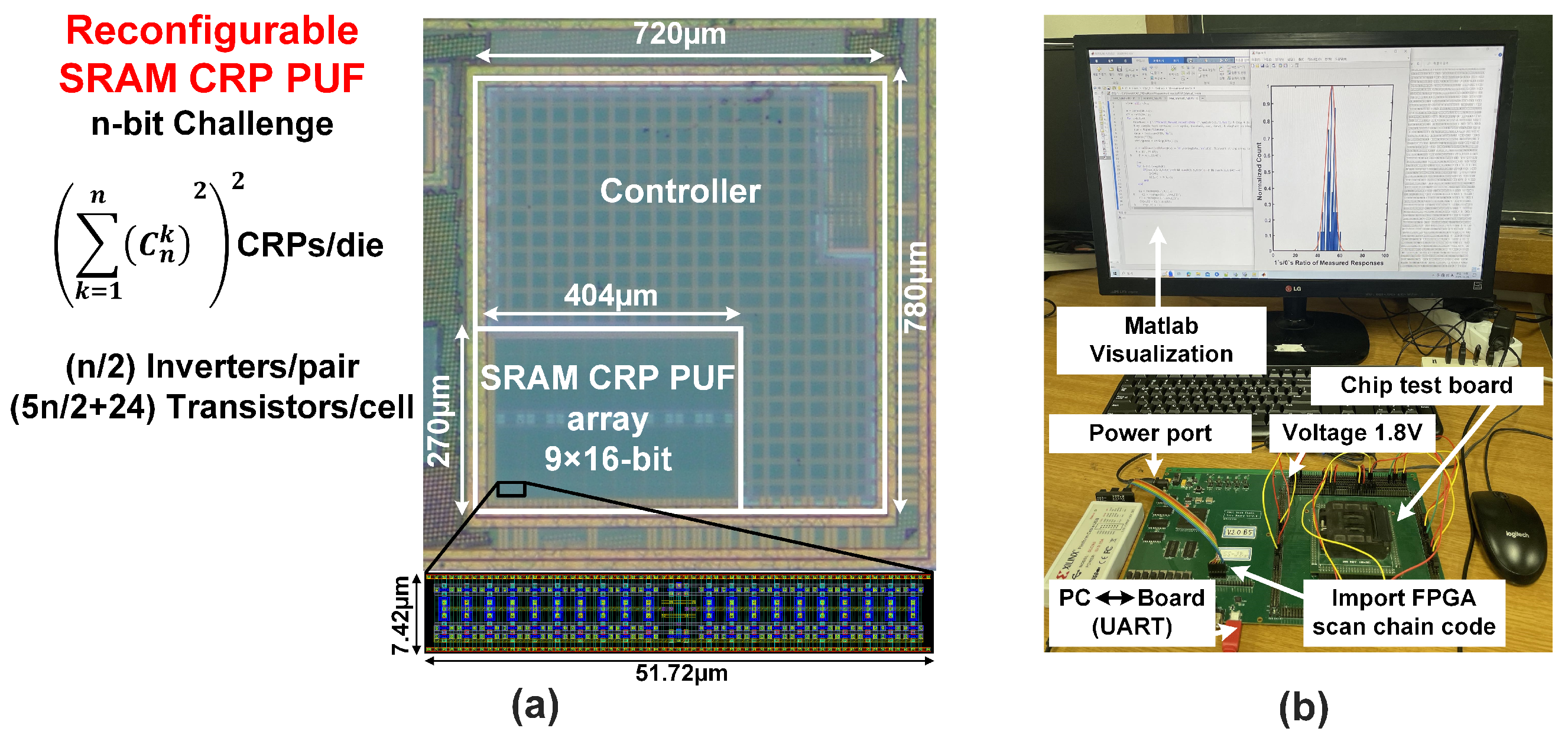

4. Implementation of SRAM CRP PUF System

5. Measurement Result

5.1. Evaluation Setup

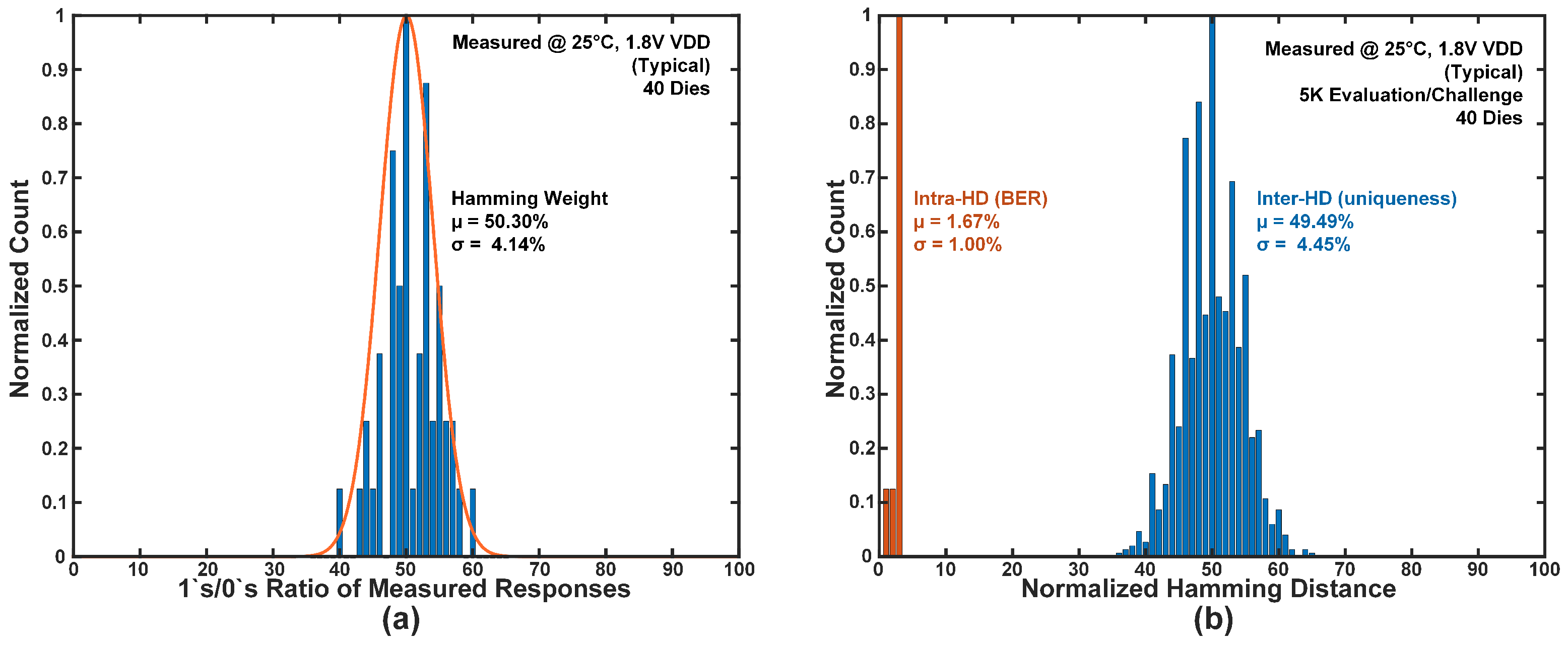

5.2. Hamming Weight

5.3. Inter and Intra Hamming Distance

5.4. Auto-Correlation Function

5.5. Performance Comparison

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Yang, Y.; Wu, L.; Yin, G.; Li, L.; Zhao, H. A survey on security and privacy issues in Internet-of-Things. IEEE Internet Things J. 2017, 4, 1250–1258. [Google Scholar] [CrossRef]

- Williams, P.; Dutta, I.K.; Daoud, H.; Bayoumi, M. A survey on security in Internet of Things with a focus on the impact of emerging technologies. Internet Things 2022, 19, 100564. [Google Scholar] [CrossRef]

- Ngo, C.T.; Eshraghian, J.K.; Hong, J.P. An Area-Optimized and Power-Efficient CBC-PRESENT and HMAC-PHOTON. Electronics 2022, 11, 2380. [Google Scholar] [CrossRef]

- Manifavas, C.; Hatzivasilis, G.; Fysarakis, K.; Rantos, K. Lightweight cryptography for embedded systems–A comparative analysis. In International Workshop on Data Privacy Management; Springer: Berlin/Heidelberg, Germany, 2013; pp. 333–349. [Google Scholar]

- Herder, C.; Yu, M.D.; Koushanfar, F.; Devadas, S. Physical Unclonable Functions and Applications: A Tutorial. Proc. IEEE 2014, 102, 1126–1141. [Google Scholar] [CrossRef]

- Choi, K.U.; Baek, S.; Heo, J.; Hong, J.P. A 100% stable sense-amplifier-based physically unclonable function with individually embedded non-volatile memory. IEEE Access 2019, 8, 21857–21865. [Google Scholar] [CrossRef]

- Shamsoshoara, A.; Korenda, A.; Afghah, F.; Zeadally, S. A survey on physical unclonable function (PUF)-based security solutions for Internet of Things. Comput. Netw. 2020, 183, 107593. [Google Scholar] [CrossRef]

- Hu, Y.W.; Zhang, T.P.; Wang, C.F.; Liu, K.K.; Sun, Y.; Li, L.; Lv, C.F.; Liang, Y.C.; Jiao, F.H.; Zhao, W.B.; et al. Flexible and biocompatible physical unclonable function anti-counterfeiting label. Adv. Funct. Mater. 2021, 31, 2102108. [Google Scholar] [CrossRef]

- Kursawe, K.; Sadeghi, A.R.; Schellekens, D.; Skoric, B.; Tuyls, P. Reconfigurable physical unclonable functions-enabling technology for tamper-resistant storage. In Proceedings of the 2009 IEEE International Workshop on Hardware-Oriented Security and Trust, San Francisco, CA, USA, 27 July 2009; IEEE: Piscataway, NJ, USA, 2009; pp. 22–29. [Google Scholar]

- Esidir, A.; Kiremitler, N.B.; Kalay, M.; Basturk, A.; Onses, M.S. Unclonable Features via Electrospraying of Bulk Polymers. ACS Appl. Polym. Mater. 2022, 4, 5952–5964. [Google Scholar] [CrossRef]

- Ibrahim, O.A.; Sciancalepore, S.; Di Pietro, R. MAG-PUF: Magnetic Physical Unclonable Functions for Device Authentication in the IoT. In Proceedings of the International Conference on Security and Privacy in Communication Systems, Virtual Event, 17–19 October 2022; Springer: Berlin/Heidelberg, Germany, 2022; pp. 130–149. [Google Scholar]

- Konigsmark, S.C.; Hwang, L.K.; Chen, D.; Wong, M.D. CNPUF: A carbon nanotube-based physically unclonable function for secure low-energy hardware design. In Proceedings of the 2014 19th Asia and South Pacific Design Automation Conference (ASP-DAC), Singapore, 20–23 January 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 73–78. [Google Scholar]

- Lu, X.; Hong, L.; Sengupta, K. 15.9 An integrated optical physically unclonable function using process-sensitive sub-wavelength photonic crystals in 65nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 5–9 February 2017; IEEE: Piscataway, NJ, USA, 2017; pp. 272–273. [Google Scholar]

- Taneja, S.; Alvarez, A.B.; Alioto, M. Fully synthesizable PUF featuring hysteresis and temperature compensation for 3.2% native BER and 1.02 fJ/b in 40 nm. IEEE J. Solid-State Circuits 2018, 53, 2828–2839. [Google Scholar] [CrossRef]

- McGrath, T.; Bagci, I.E.; Wang, Z.M.; Roedig, U.; Young, R.J. A PUF taxonomy. Appl. Phys. Rev. 2019, 6, 11303. [Google Scholar] [CrossRef]

- Che, W.; Saqib, F.; Plusquellic, J. PUF-based authentication. In Proceedings of the 2015 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, USA, 2–6 November 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 337–344. [Google Scholar]

- Chen, Q.; Csaba, G.; Lugli, P.; Schlichtmann, U.; Rührmair, U. The bistable ring PUF: A new architecture for strong physical unclonable functions. In Proceedings of the 2011 IEEE International Symposium on Hardware-Oriented Security and Trust, San Diego, CA, USA, 5–6 June 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 134–141. [Google Scholar]

- Delavar, M.; Mirzakuchaki, S.; Mohajeri, J. A ring oscillator-based PUF with enhanced challenge-response pairs. Can. J. Electr. Comput. Eng. 2016, 39, 174–180. [Google Scholar] [CrossRef]

- Govindaraj, R.; Ghosh, S.; Katkoori, S. Design, analysis and application of embedded resistive RAM based strong arbiter PUF. IEEE Trans. Dependable Secur. Comput. 2018, 17, 1232–1242. [Google Scholar] [CrossRef]

- He, Z.; Wan, M.; Deng, J.; Bai, C.; Dai, K. A reliable strong PUF based on switched-capacitor circuit. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 1073–1083. [Google Scholar] [CrossRef]

- Cao, Y.; Liu, C.Q.; Chang, C.H. A low power diode-clamped inverter-based strong physical unclonable function for robust and lightweight authentication. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 3864–3873. [Google Scholar] [CrossRef]

- Baek, S.; Yu, G.H.; Kim, J.; Ngo, C.T.; Eshraghian, J.K.; Hong, J.P. A reconfigurable SRAM-based CMOS PUF with challenge to response pairs. IEEE Access 2021, 9, 79947–79960. [Google Scholar] [CrossRef]

- Nam, J.W.; Kim, J.; Hong, J.P. Stochastic Cell-and Bit-Discard Technique to Improve Randomness of a TRNG. Electronics 2022, 11, 1735. [Google Scholar] [CrossRef]

- Agarwal, K.; Nassif, S. Characterizing process variation in nanometer CMOS. In Proceedings of the 44th Annual Design Automation Conference, San Diego, CA, USA, 4–8 June 2007; pp. 396–399. [Google Scholar]

- Bhargava, M.; Mai, K. An efficient reliable PUF-based cryptographic key generator in 65 nm CMOS. In Proceedings of the 2014 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 24–28 March 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 1–6. [Google Scholar]

- Hastings, A. The Art of Analog Layout; Prentice-Hall Inc.: Upper Saddle River, NJ, USA, 2001. [Google Scholar]

- Drennan, P.G.; McAndrew, C.C. Understanding MOSFET mismatch for analog design. IEEE J. Solid-State Circuits 2003, 38, 450–456. [Google Scholar] [CrossRef]

- Alheyasat, A.; Torrens, G.; Bota, S.A.; Alorda, B. Estimation during design phases of suitable SRAM cells for PUF applications using separatrix and mismatch metrics. Electronics 2021, 10, 1479. [Google Scholar] [CrossRef]

- Schrijen, G.J.; Van Der Leest, V. Comparative analysis of SRAM memories used as PUF primitives. In Proceedings of the 2012 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 12–16 March 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 1319–1324. [Google Scholar]

- Barbareschi, M.; Battista, E.; Mazzeo, A.; Mazzocca, N. Testing 90 nm microcontroller SRAM PUF quality. In Proceedings of the 2015 10th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Napoli, Italy, 21–23 April 2015; IEEE: Piscataway, NJ, USA, 2015; pp. 1–6. [Google Scholar]

- Böhm, C.; Hofer, M.; Pribyl, W. A microcontroller SRAM-PUF. In Proceedings of the 2011 5th International Conference on Network and System Security, Milan, Italy, 6–8 September 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 269–273. [Google Scholar]

- Nam, J.W.; Ahn, J.H.; Hong, J.P. Compact SRAM-based PUF chip employing body voltage control technique. IEEE Access 2022, 10, 22311–22319. [Google Scholar] [CrossRef]

- Venkatesh, A.; Venkatasubramaniyan, A.B.; Xi, X.; Sanyal, A. 0.3 pJ/bit machine learning resistant strong PUF using subthreshold voltage divider array. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 1394–1398. [Google Scholar] [CrossRef]

- Zhuang, H.; Xi, X.; Sun, N.; Orshansky, M. A strong subthreshold current array PUF resilient to machine learning attacks. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 67, 135–144. [Google Scholar] [CrossRef]

| This Work | [22] | [32] | [33] | [34] | |

|---|---|---|---|---|---|

| Technology (nm) | 180 | 65 | 65 | 65 | 130 |

| Bit-Width of Challenge (bit) | 32 | 32 | 32 | 60 | 65 |

| Type of PUF | Reconf. SRAM | Reconf. SRAM | SRAM | Voltage Array | SCA |

| Possible CRPs | 1.6 × 10 | 1.6 × 10 | 1.6 × 10 | 1.15 × 10 | 3.7 × 10 |

| Worst-case BER | 4.86% | 13.7% | 20.8% | 10.9% | 9% |

| Area/bit (F/bit) | 1.2 × 10 | 2.1 × 10 | 0.9 × 10 | 66.3 × 10 | 55.0 × 10 |

| Normalized Area * | 1 | 1.75 | 0.75 | 29.47 | 27.08 |

| Energy/bit (pJ/b) | 7 | 0.082 | 0.09 | 0.3 | 11 |

| Normalized Energy ** | 1 | 0.25 | 0.27 | 0.485 | 2.05 |

| Inter-HD | 0.4949 | 0.4893 | 0.4889 | 0.5026 | 0.499 |

| Intra-HD | 0.0167 | 0.024 | 0.0311 | 0.0466 | 0.058 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Pham, V.K.; Ngo, C.T.; Nam, J.-W.; Hong, J.-P. A Reconfigurable SRAM CRP PUF with High Reliability and Randomness. Electronics 2024, 13, 309. https://doi.org/10.3390/electronics13020309

Pham VK, Ngo CT, Nam J-W, Hong J-P. A Reconfigurable SRAM CRP PUF with High Reliability and Randomness. Electronics. 2024; 13(2):309. https://doi.org/10.3390/electronics13020309

Chicago/Turabian StylePham, Van Khanh, Chi Trung Ngo, Jae-Won Nam, and Jong-Phil Hong. 2024. "A Reconfigurable SRAM CRP PUF with High Reliability and Randomness" Electronics 13, no. 2: 309. https://doi.org/10.3390/electronics13020309

APA StylePham, V. K., Ngo, C. T., Nam, J.-W., & Hong, J.-P. (2024). A Reconfigurable SRAM CRP PUF with High Reliability and Randomness. Electronics, 13(2), 309. https://doi.org/10.3390/electronics13020309