Digital Functional Blocks Implementation of PWM and Control for a High-Frequency Interleaved Y-Inverter Motor Drive

Abstract

1. Introduction

- ■

- No bulky and reliability critical DC-link capacitor is required;

- ■

- Voltage boost capability is inherently possible;

- ■

- Output electro-magnetic signature is greatly improved, both in terms of harmonic content and dV/dt values;

- ■

- Switching losses are greatly reduced, enabling much higher switching frequencies;

- ■

- Selection and operation of input- and output-side devices can be tailored to optimum performance and cost in terms of semiconductor technology, voltage rating, and switching frequency.

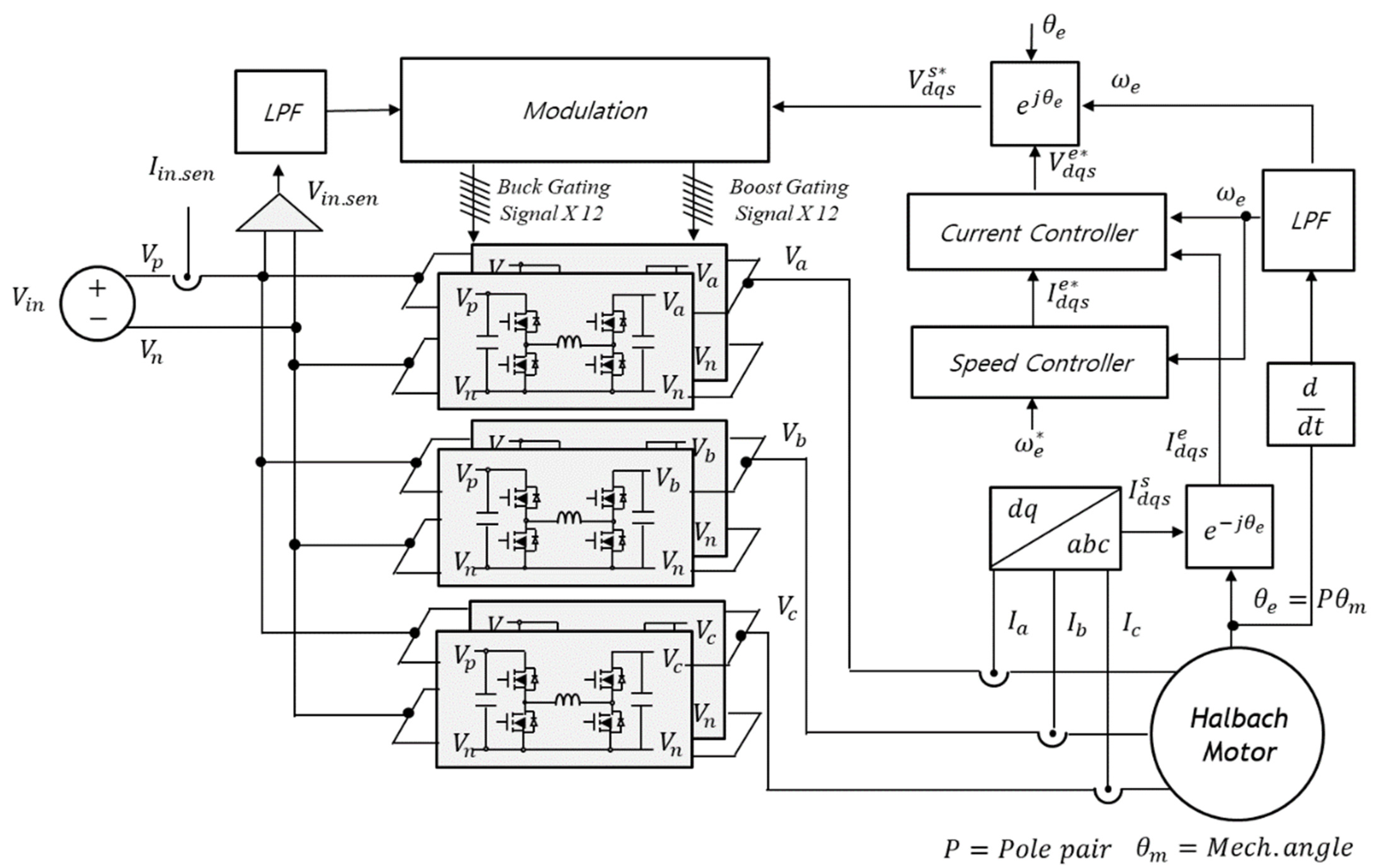

2. Inverter Architecture

2.1. Power Cell Design

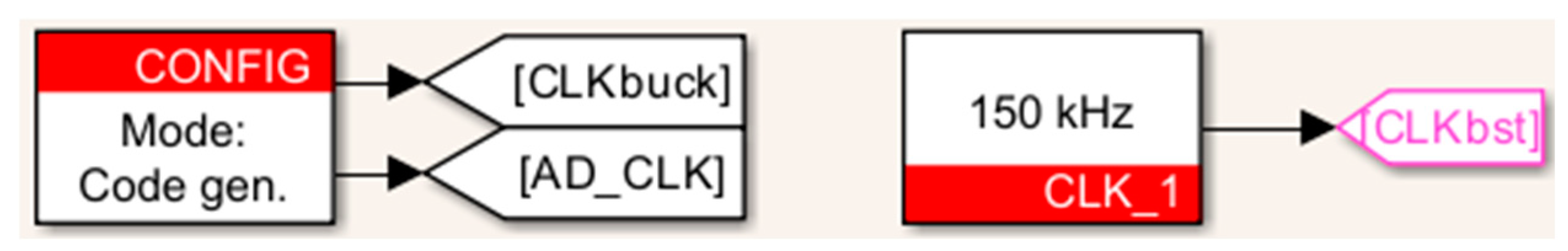

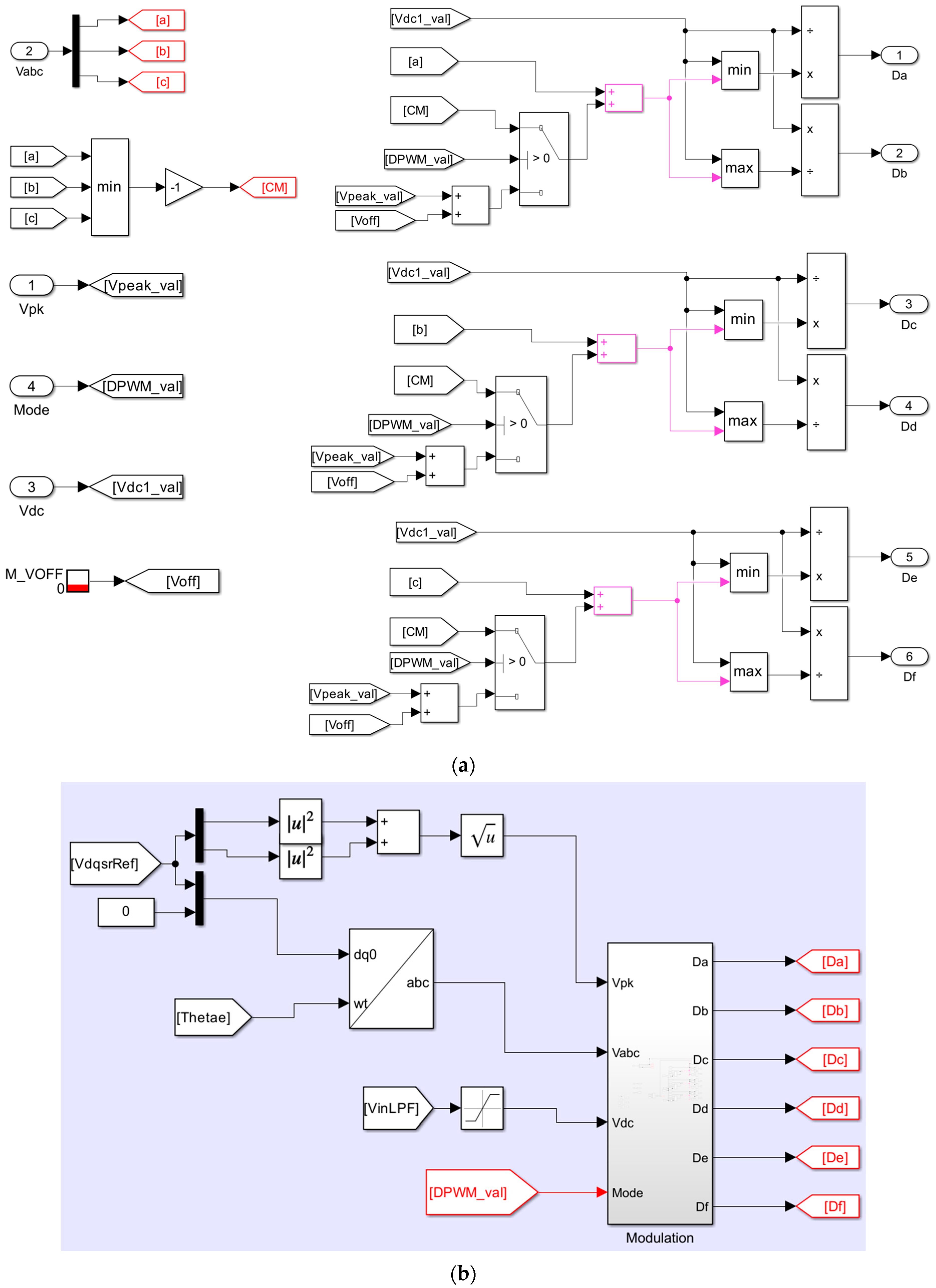

2.2. Modulation Strategy

- -

- Single-duty: If dBU = dBO = d, a single parameter modulation is achieved, with diagonal switch-pairs in the H-bridge cell jointly turned on and off;

- -

- Dual-duty: This is implemented by maintaining separate variable duty cycles for the buck and boost cells, setting dBU = 1 during boost-mode operation and, vice versa, setting dBOC = 1 during buck-mode operation;

- -

- Hybrid duty: Setting dBOC = k (with 0 < k < 1) and using only dBU as the control parameter means that the boost-side leg transistors are operated with constant duty and the buck-side ones with variable duty. Of course, the possibility to set a fixed dBU value and a variable dBOC also exists theoretically; however, in the case of sinusoidal modulation, the need to ensure 0 < dBOC < 1 implies increased complications.

- -

- The dual-duty solution is the one enabling the lowest maximum voltage across the inductor and thus, the highest power density. Moreover, it minimizes switching losses, as only two devices are switching at any given time, allowing for maximum power density.

- -

- Single-duty modulation implements a continuous switching pattern of all devices, and thus, of the inductor current controllability; it can be of interest for ensuring good harmonic performance at relatively high output fundamental frequencies.

- -

- The hybrid-duty approach results in a fully linear control equation and can thus be of interest when a high-performance dynamic response is required while maintaining control simplicity.

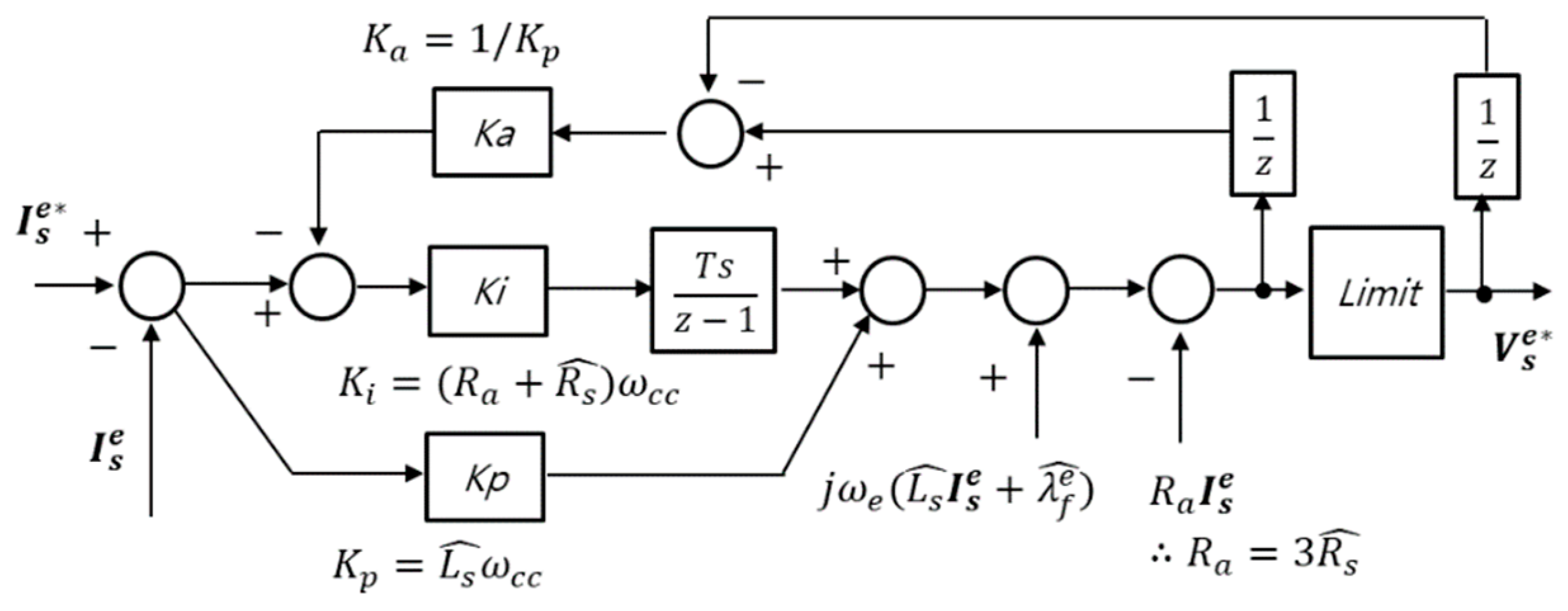

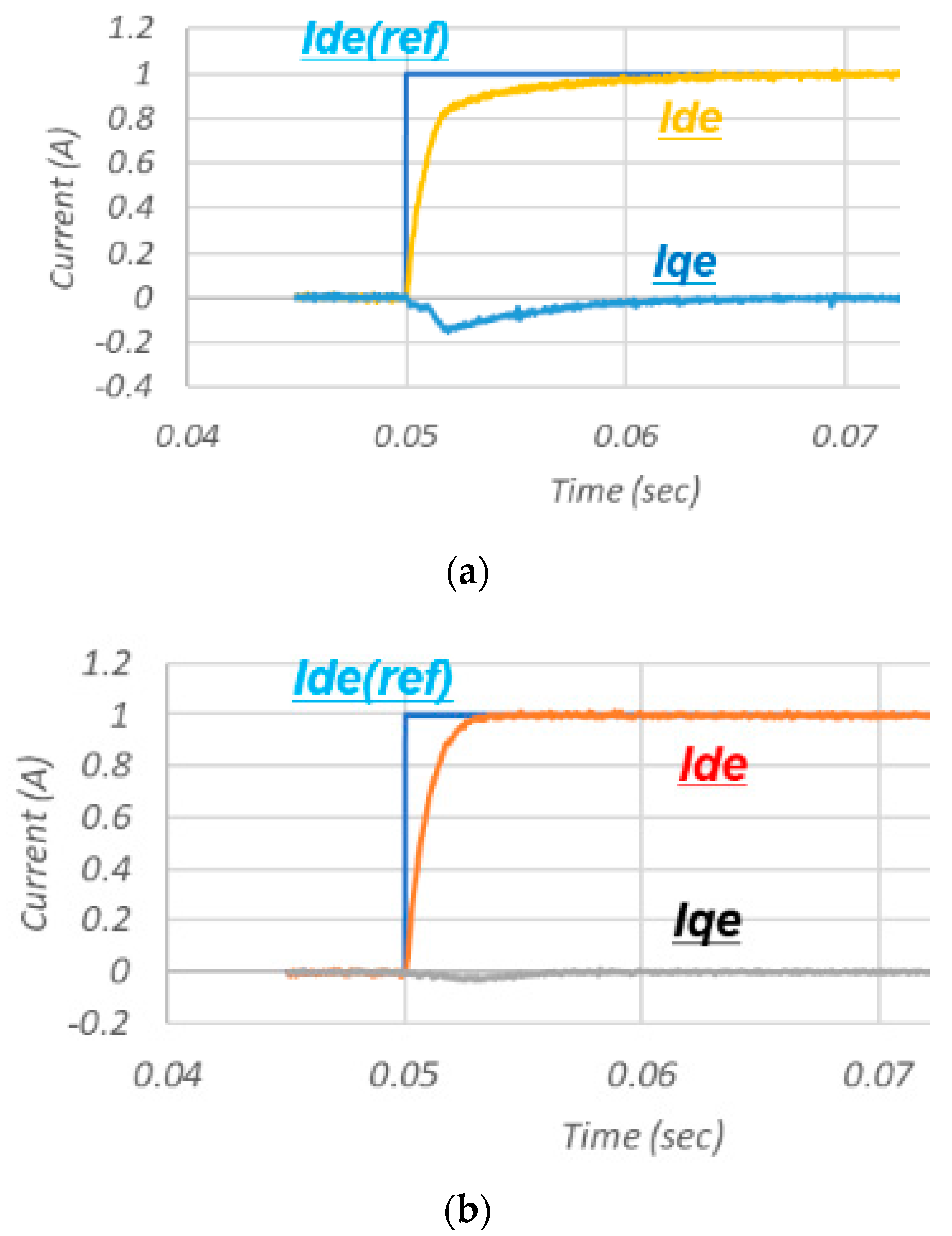

2.3. Control

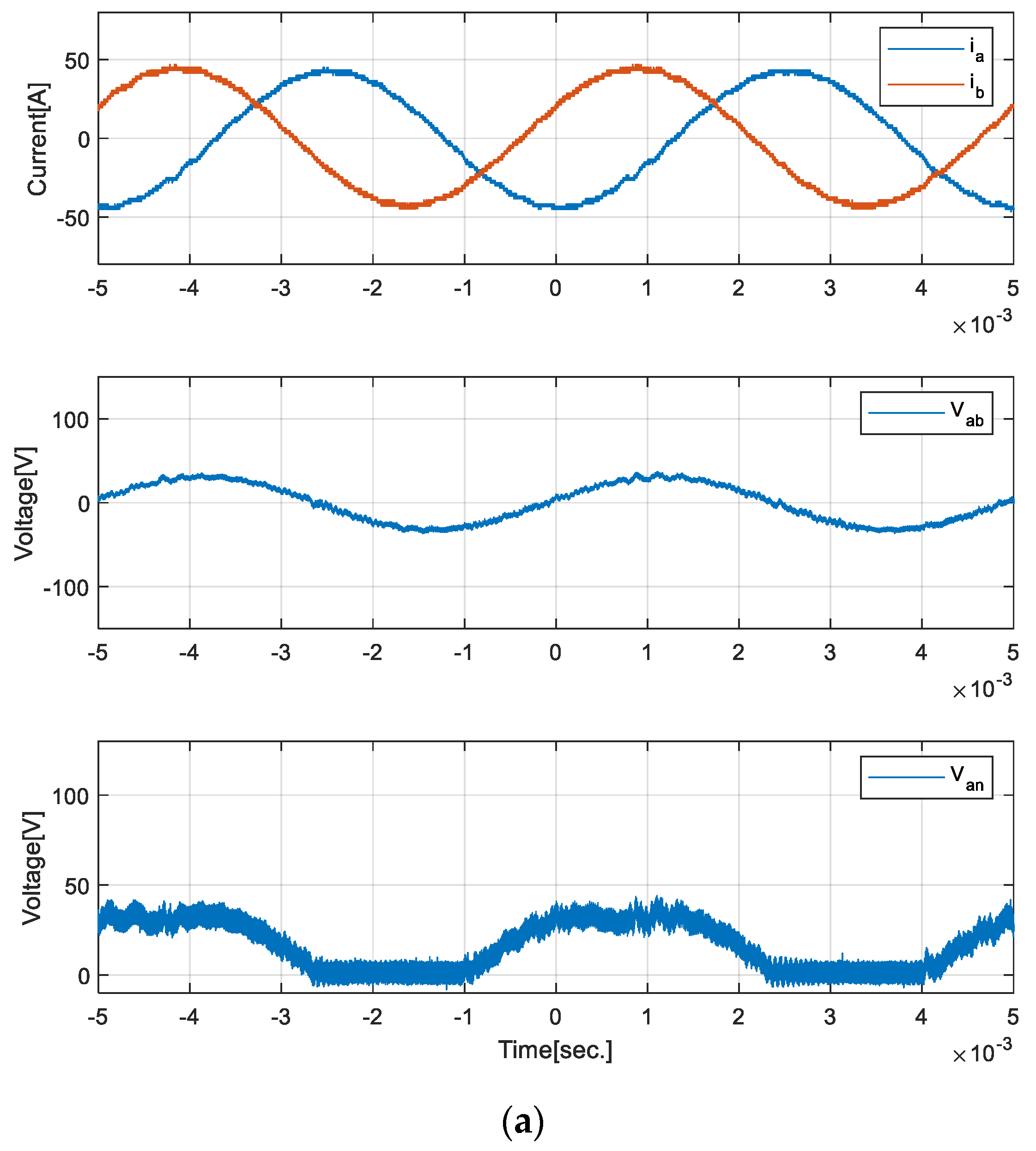

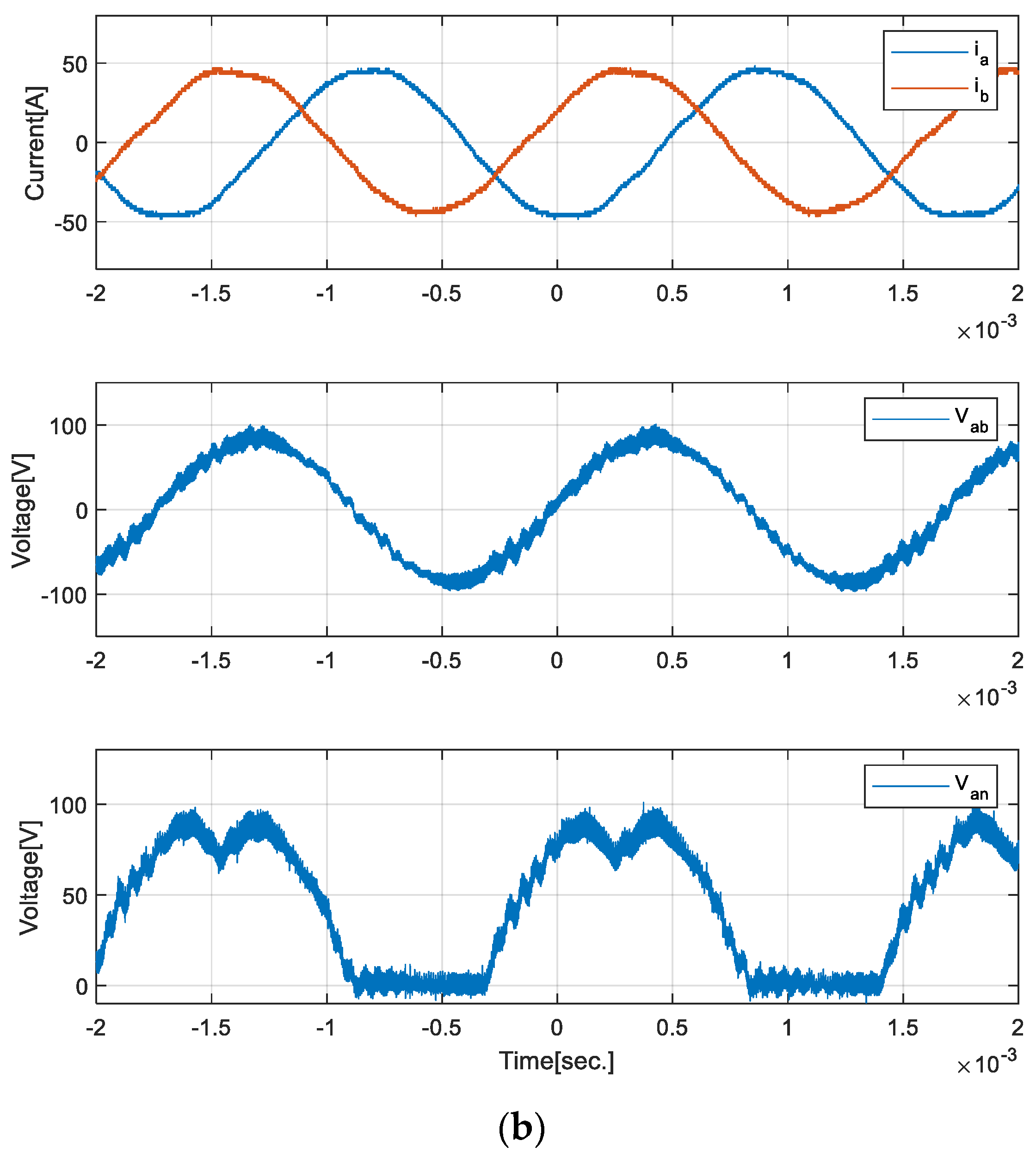

3. Hardware Implementation and Test

4. Discussion and Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Husain, I.; Ozpineci, B.; Islam, M.S.; Gurpinar, E.; Su, G.J.; Yu, W.; Chowdhury, S.; Xue, L.; Rahman, D.; Sahu, R. Electric drive technology trends, challenges, and opportunities for future electric vehicles. Proc. IEEE 2021, 109, 1039–1059. [Google Scholar] [CrossRef]

- Antivachis, M.; Bortis, D.; Schrittwieser, L.; Kolar, J.W. Three-phase buck-boost Y-inverter with wide DC input voltage range. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1492–1499. [Google Scholar]

- Melo, V.; Melo, A.; Santos, W.; Fardin, J.; Encarnação, L. Open-loop single-phase space state model and equivalent circuit of a non-conventional three-phase inverter. Electronics 2020, 9, 744. [Google Scholar] [CrossRef]

- Endo, Y.; Jaber, H.J.; Minami, M.; Castellazzi, A. Floating output series interleaved boost-only GaN Y-Inverter. In Proceedings of the 2022 25th International Conference on Electrical Machines and Systems (ICEMS), Chiang Mai, Thailand, 29 November–2 December 2022; pp. 1–4. [Google Scholar]

- Jaber, H.J.; Castellazzi, A. Frequency and Modulation Index Related Effects in Continuous and Discontinuous Modulated Y-Inverter for Motor-Drive Applications. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hanover, Germany, 5–9 September 2022; pp. 1–8. [Google Scholar]

- Jaber, H.J.; Horie, K.; Domae, S.; Castellazzi, A. Dual switching-frequency hybrid Si-SiC Y-Inverter. In Proceedings of the 2023 11th International Conference on Power Electronics and ECCE Asia (ICPE 2023-ECCE Asia), Jeju Island, Republic of Korea, 22–25 May 2023; pp. 757–763. [Google Scholar]

- Antivachis, M.; Bortis, D.; Menzi, D.; Kolar, J.W. Comparative evaluation of Y-inverter against three-phase two-stage buck-boost DC-AC converter systems. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 181–189. [Google Scholar]

- Kolar, J.W.; Huber, J. Next-generation SiC/GaN three-phase variable-speed drive inverter concepts. In Proceedings of the PCIM Europe Digital Days 2021, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Online, 3–7 May 2021; VDE: Frankfurt am Main, Germany; pp. 1–5. [Google Scholar]

- Trang, H.; Castellazzi, A.; Domae, S.; Dong, T.; Nakamura, T. Light electric vehicle motor-drive design based on hybrid Si/SiC Y-inverter and dual-rotor Halbach machine. J. Electr. Eng. Technol. 2023, 18, 367–376. [Google Scholar] [CrossRef]

- Endo, Y.; Minami, M.; Jaber, H.J.; Castellazzi, A. Experimental study of interleaved Y-Inverter performance. In Proceedings of the 2022 24th European Conference on Power Electronics and Applications (EPE’22 ECCE Europe), Hanover, Germany, 5–9 September 2022; pp. 1–8. [Google Scholar]

- Hava, A.M.; Kerkman, R.J.; Lipo, T.A. A high-performance generalized discontinuous PWM algorithm. IEEE Trans. Ind. Appl. 1998, 2, 1059–1071. [Google Scholar] [CrossRef]

- Hava, A.M.; Çetin, N.O. A Generalized Scalar PWM Approach With Easy Implementation Features for Three-Phase, Three-Wire Voltage-Source Inverters. IEEE Trans. Power Electron. 2011, 26, 1385–1395. [Google Scholar] [CrossRef]

- Available online: https://imperix.com/products/control/inverter-control-board/ (accessed on 22 June 2024).

- Available online: https://www.plexim.com/products/rt_box (accessed on 22 June 2024).

- Dong, T.; Kwak, J.; Wei, L.; Castellazzi, A.; Nakamura, T. High power-density high-efficiency electric drive design with halbach-rotor pmsm and wbg-based high-frequency inverter. In Proceedings of the 2021 24th International Conference on Electrical Machines and Systems (ICEMS), Gyeongju, Republic of Korea, 31 October 2021–3 November 2021; pp. 1759–1762. [Google Scholar]

- Lee, Y.; Castellazzi, A.; Domae, S.; Nakamura, T. Regenerative Halbach-motor traction drive powered by an active-damping controlled interleaved Y-inverter. In Proceedings of the 2024 10th International Power Electronics and Motion Control Conference ECCE Asia (IPEMC 2024-ECCE Asia), Chengdu, China, 17–20 May 2024. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, Y.; Castellazzi, A.; Domae, S. Digital Functional Blocks Implementation of PWM and Control for a High-Frequency Interleaved Y-Inverter Motor Drive. Electronics 2024, 13, 2610. https://doi.org/10.3390/electronics13132610

Lee Y, Castellazzi A, Domae S. Digital Functional Blocks Implementation of PWM and Control for a High-Frequency Interleaved Y-Inverter Motor Drive. Electronics. 2024; 13(13):2610. https://doi.org/10.3390/electronics13132610

Chicago/Turabian StyleLee, Yonghwa, Alberto Castellazzi, and Shinichi Domae. 2024. "Digital Functional Blocks Implementation of PWM and Control for a High-Frequency Interleaved Y-Inverter Motor Drive" Electronics 13, no. 13: 2610. https://doi.org/10.3390/electronics13132610

APA StyleLee, Y., Castellazzi, A., & Domae, S. (2024). Digital Functional Blocks Implementation of PWM and Control for a High-Frequency Interleaved Y-Inverter Motor Drive. Electronics, 13(13), 2610. https://doi.org/10.3390/electronics13132610