Communication-Free Interleaving Control of Parallel-Connected DC-DC Converters

Abstract

:1. Introduction

- (1)

- No requirement for communication lines.

- (2)

- Compatibility with the current sharing control.

- (3)

- Compatibility with non-uniform converter parameters.

- (4)

- Plug-and-play feature.

- (1)

- Relaxed sampling requirements.

- (2)

- Simple control implementation.

- (3)

- Elimination of higher harmonics.

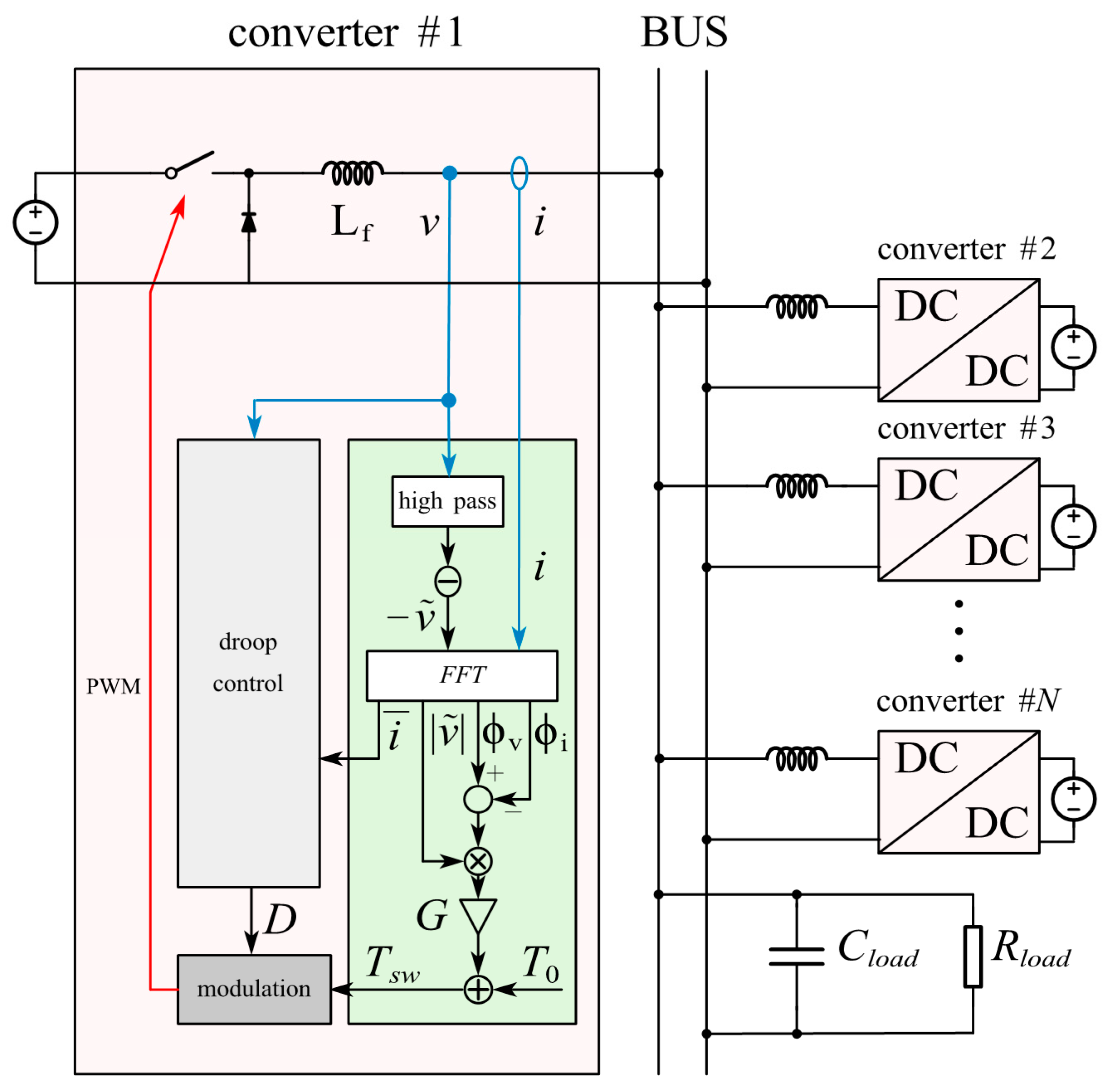

2. System Description and Control Method

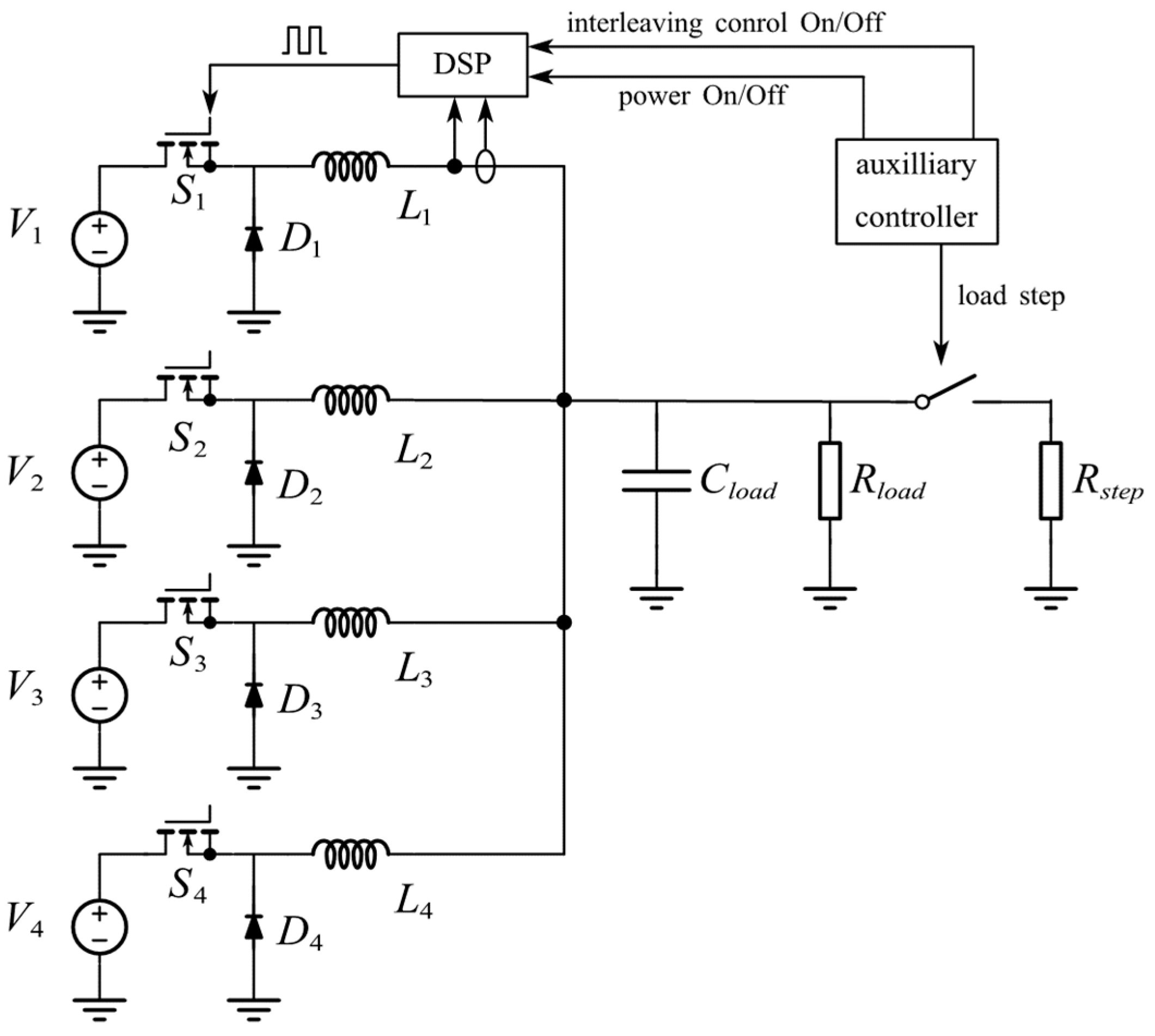

2.1. System of Parallel-Connected Converters

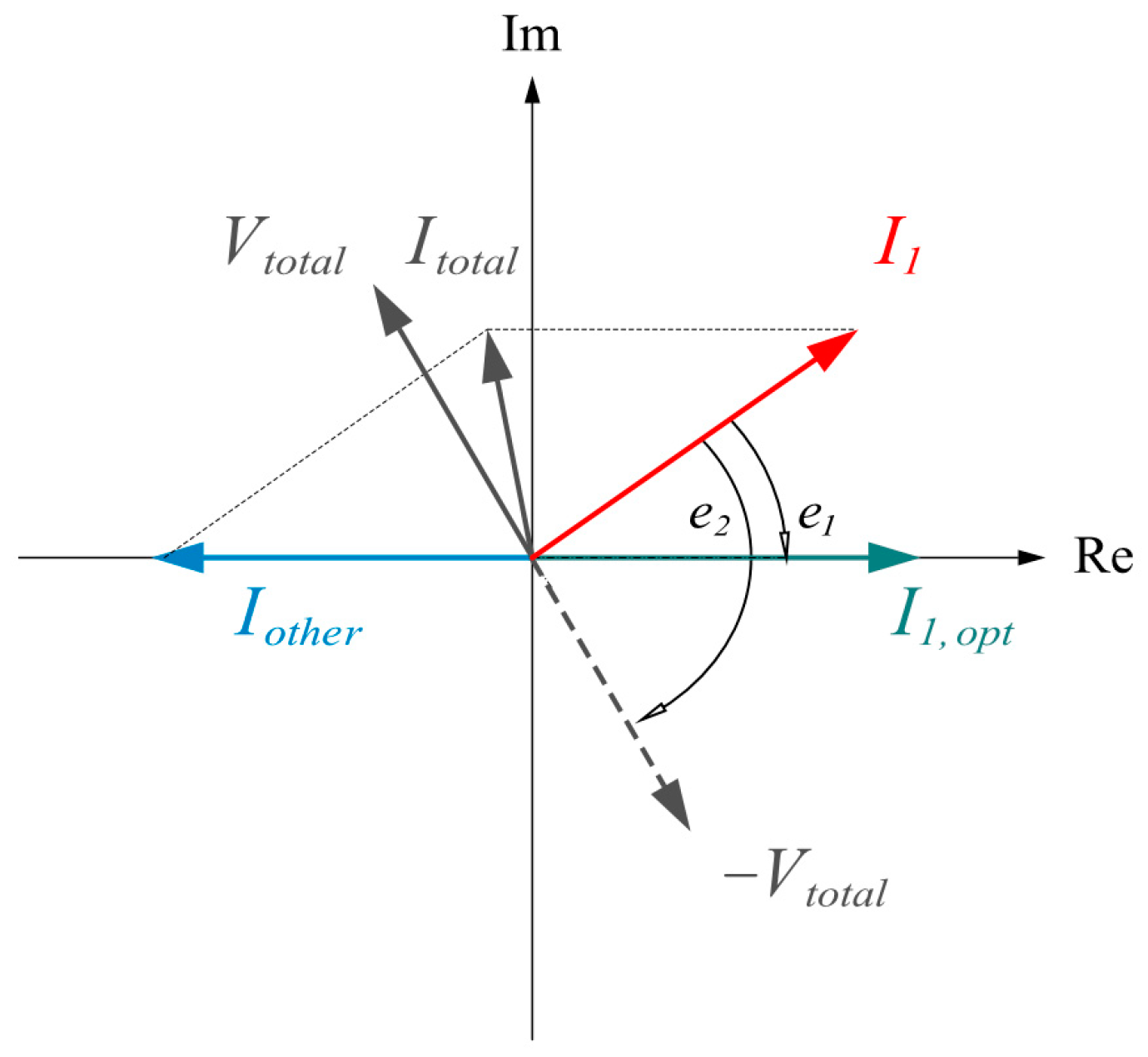

2.2. Principle of Interleaving Control

2.3. Higher Harmonics

2.4. Method Compatibility

3. Stability Analysis

3.1. Proof of Stability

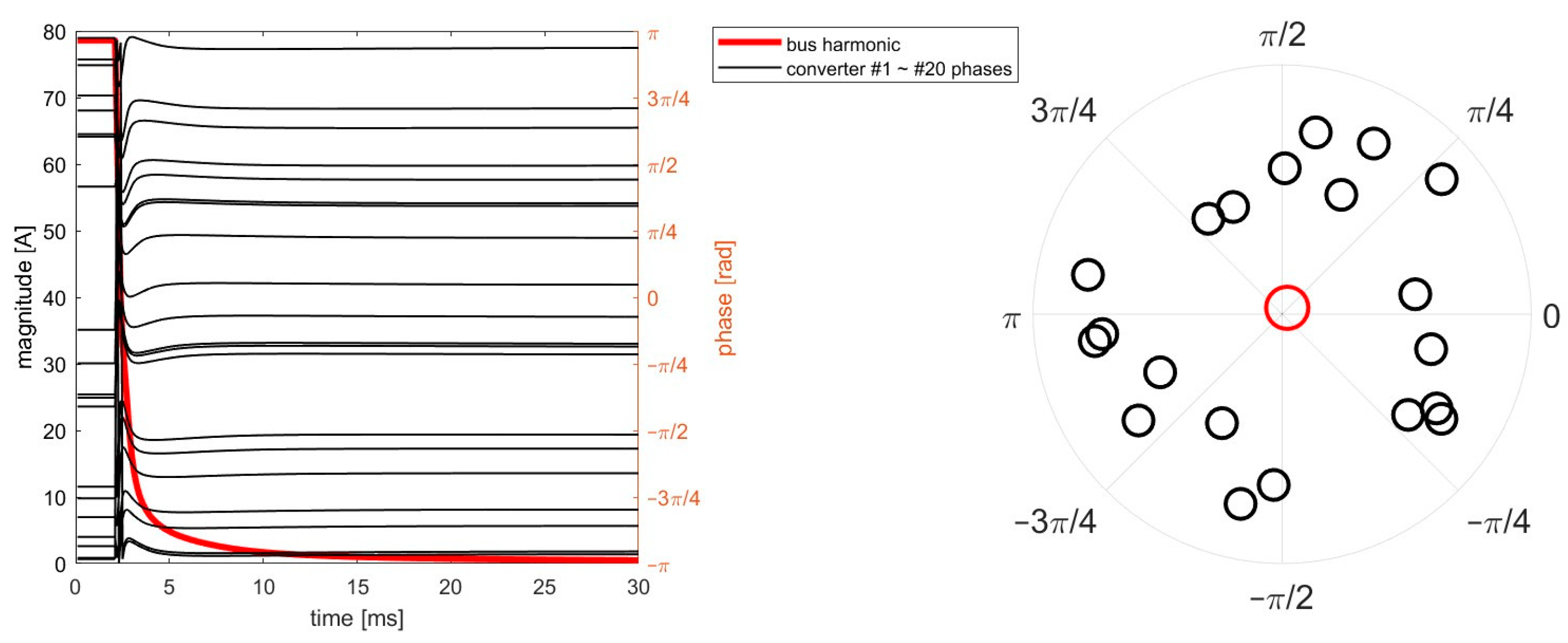

3.2. Phasor Simulation

3.2.1. Asymmetric Converters

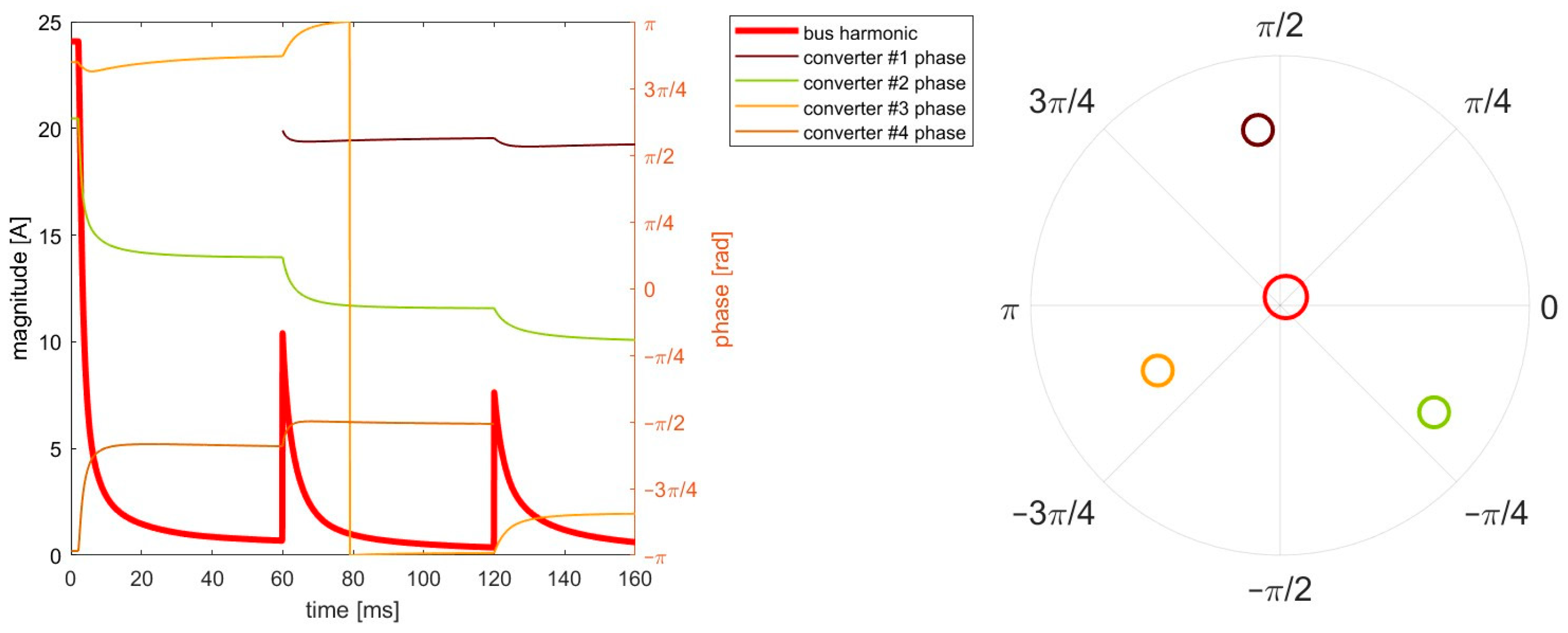

3.2.2. Converter Addition and Subtraction

3.3. Converter Simulation

3.3.1. Startup of Phase-Shifting Control

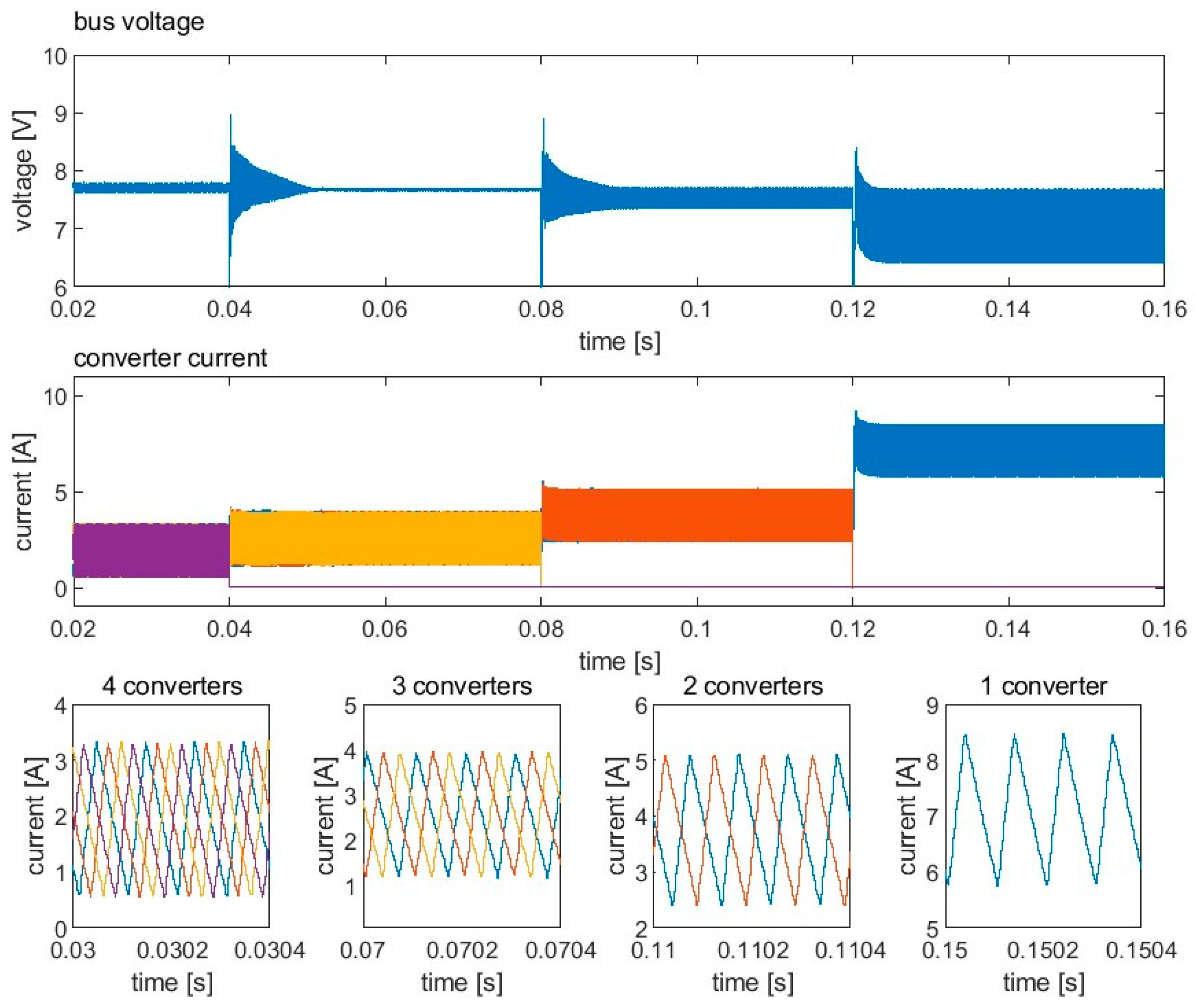

3.3.2. Unit Addition and Subtraction

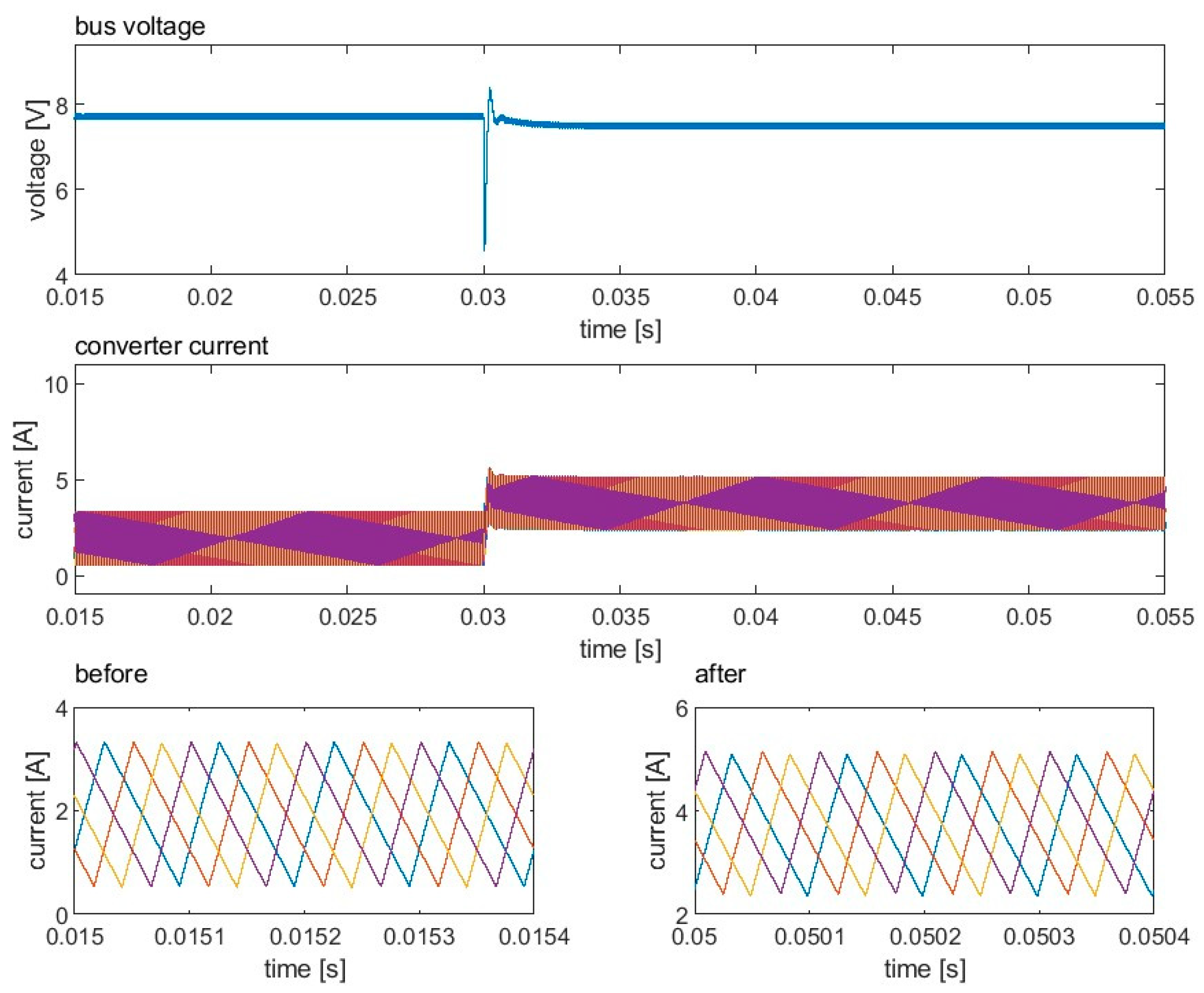

3.3.3. Load Step

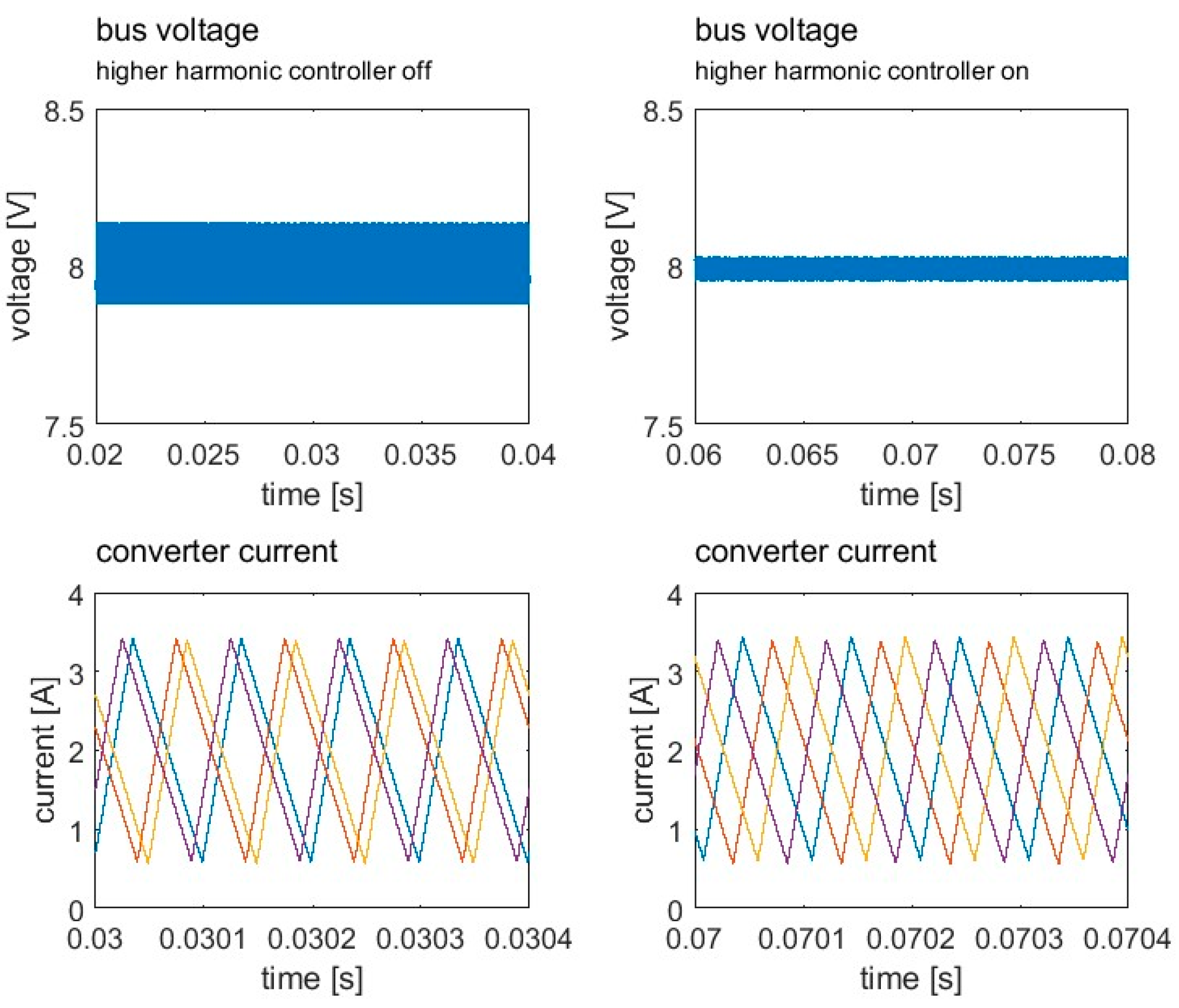

3.3.4. Higher Harmonic Controller

4. Experimental Validation

4.1. Startup of Phase-Shifting Control

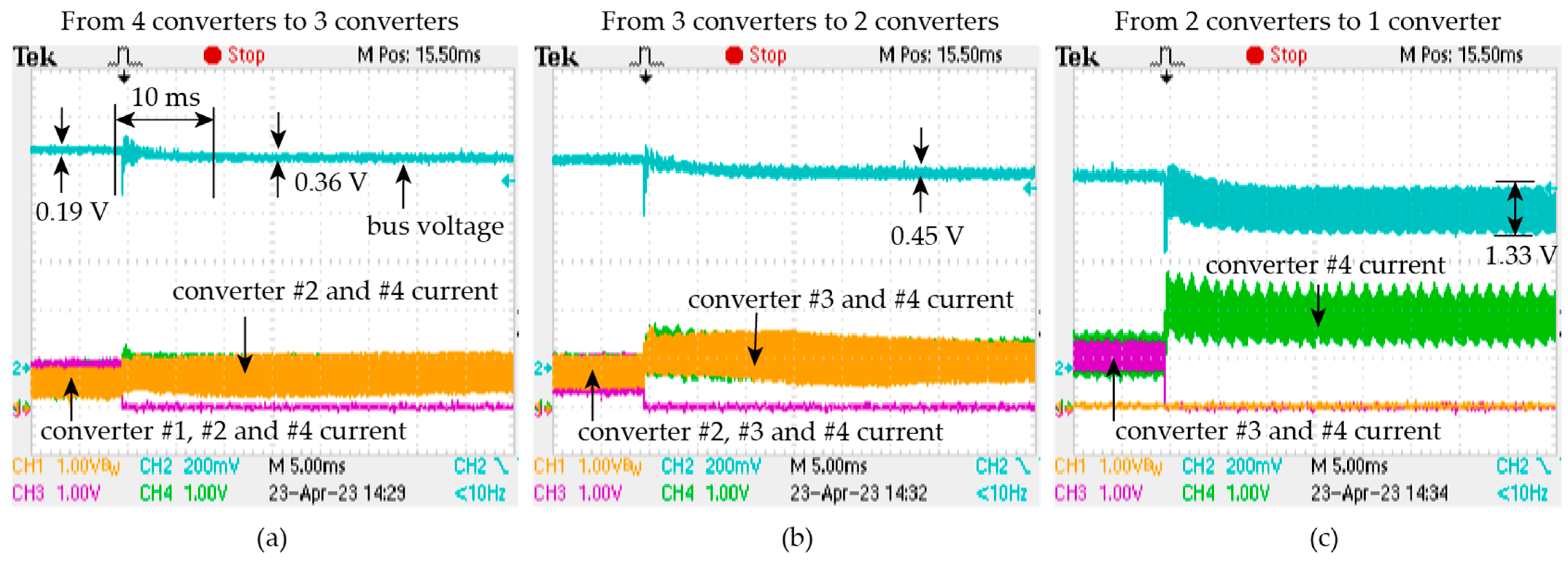

4.2. Unit Addition and Subtraction

4.3. Load Step

4.4. Summary and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Poursafar, N.; Hossain, M.J.; Taghizadeh, S. Distributed DC-Bus Signaling Control of Photovoltaic Systems in Islanded DC Microgrid. CSEE J. Power Energy Syst. 2022, 8, 1741–1750. [Google Scholar]

- Du, W.; Ma, Z.; Wang, Y.; Wang, H.F. Harmonic oscillations in a grid-connected PV generation farm caused by increased number of parallel-connected PV generating units and damping control. CSEE J. Power Energy Syst. 2020. [Google Scholar] [CrossRef]

- ENajm, M.; Huang, A.Q. Integrated DC/DC parallel PnP PV architecture method for powering residential buildings. In Proceedings of the 2015 IEEE First International Conference on DC Microgrids (ICDCM), Atlanta, GA, USA, 7–10 June 2015; pp. 371–376. [Google Scholar]

- GCao; Guo, Z.; Wang, Y.; Sun, K.; Kim, H.-J. A DC-DC conversion system for high power HVDC-connected photovoltaic power system. In Proceedings of the 2017 20th International Conference on Electrical Machines and Systems (ICEMS), Sydney, NSW, Australia, 11–14 August 2017; pp. 1–6. [Google Scholar]

- Zhang, L.; Sun, K.; Xing, Y.; Feng, L.; Ge, H. A Modular Grid-Connected Photovoltaic Generation System Based on DC Bus. IEEE Trans. Power Electron. 2011, 26, 523–531. [Google Scholar] [CrossRef]

- Deng, F.; Chen, Z. Control of Improved Full-Bridge Three-Level DC/DC Converter for Wind Turbines in a DC Grid. IEEE Trans. Power Electron. 2013, 28, 314–324. [Google Scholar] [CrossRef]

- Chen, S.; Yang, Q.; Zhou, J.; Chen, X. A model predictive control method for hybrid energy storage systems. CSEE J. Power Energy Syst. 2020, 7, 329–338. [Google Scholar]

- Al-Ismail, F.S. DC Microgrid Planning, Operation, and Control: A Comprehensive Review. IEEE Access 2021, 9, 36154–36172. [Google Scholar] [CrossRef]

- Ghanbari, N.; Bhattacharya, S. Disturbance Rejection Analysis of a Droop-Controlled DC Microgrid Through a Novel Mathematical Modeling. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 1507–1518. [Google Scholar] [CrossRef]

- Pires, V.F.; Cordeiro, A.; Roncero-Clemente, C.; Rivera, S.; Dragicevic, T. DC–DC Converters for Bipolar Microgrid Voltage Balancing: A Comprehensive Review of Architectures and Topologies. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 981–998. [Google Scholar] [CrossRef]

- Shah, S.S.; Rastogi, S.K.; Bhattacharya, S. Paralleling of LLC Resonant Converters. IEEE Trans. Power Electron. 2021, 36, 6276–6287. [Google Scholar] [CrossRef]

- Drobnic, K.; Grandi, G.; Hammami, M.; Mandrioli, R.; Ricco, M.; Viatkin, A.; Vujacic, M. An Output Ripple-Free Fast Charger for Electric Vehicles Based on Grid-Tied Modular Three-Phase Interleaved Converters. IEEE Trans. Ind. Appl. 2019, 55, 6102–6114. [Google Scholar] [CrossRef]

- Sha, D.; Xu, G.; Xu, Y. Utility Direct Interfaced Charger/Discharger Employing Unified Voltage Balance Control for Cascaded H-Bridge Units and Decentralized Control for CF-DAB Modules. IEEE Trans. Ind. Electron. 2017, 64, 7831–7841. [Google Scholar] [CrossRef]

- Tarisciotti, L.; Costabeber, A.; Chen, L.; Walker, A.; Galea, M. Current-Fed Isolated DC/DC Converter for Future Aerospace Microgrids. IEEE Trans. Ind. Appl. 2019, 55, 2823–2832. [Google Scholar] [CrossRef]

- Magne, P.; Nahid-Mobarakeh, B.; Pierfederici, S. Active Stabilization of DC Microgrids Without Remote Sensors for More Electric Aircraft. IEEE Trans. Ind. Appl. 2013, 49, 2352–2360. [Google Scholar] [CrossRef]

- Xu, L.; Guerrero, J.M.; Lashab, A.; Wei, B.; Bazmohammadi, N.; Vasquez, J.C.; Abusorrah, A. A Review of DC Shipboard Microgrids—Part I: Power Architectures, Energy Storage, and Power Converters. IEEE Trans. Power Electron. 2022, 37, 5155–5172. [Google Scholar] [CrossRef]

- Ma, Y.; Corzine, K.; Maqsood, A.; Gao, F.; Wang, K. Stability Assessment of Droop Controlled Parallel Buck Converters in Zonal Ship DC Microgrid. In Proceedings of the 2019 IEEE Electric Ship Technologies Symposium (ESTS), Washington, DC, USA, 14–16 August 2019. [Google Scholar]

- Xie, P.; Guerrero, J.M.; Tan, S.; Bazmohammadi, N.; Vasquez, J.C.; Mehrzadi, M.; Al-Turki, Y. Optimization-Based Power and Energy Management System in Shipboard Microgrid: A Review. IEEE Syst. J. 2022, 16, 578–590. [Google Scholar] [CrossRef]

- Xu, L.; Guerrero, J.M.; Lashab, A.; Wei, B.; Bazmohammadi, N.; Vasquez, J.C.; Abusorrah, A. A Review of DC Shipboard Microgrids—Part II: Control Architectures, Stability Analysis, and Protection Schemes. IEEE Trans. Power Electron. 2022, 37, 4105–4120. [Google Scholar] [CrossRef]

- Su, M.; Liu, Z.; Sun, Y.; Han, H.; Hou, X. Stability Analysis and Stabilization Methods of DC Microgrid With Multiple Parallel-Connected DC–DC Converters Loaded by CPLs. IEEE Trans. Smart Grid 2018, 9, 132–142. [Google Scholar] [CrossRef]

- Kakigano, H.; Miura, Y.; Ise, T. Low-Voltage Bipolar-Type DC Microgrid for Super High Quality Distribution. IEEE Trans. Power Electron. 2010, 25, 3066–3075. [Google Scholar] [CrossRef]

- Zhang, X.; Huang, A.Q. A novel distributed control and its tolerance analysis for microprocessor power management. In Proceedings of the Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, 2006, APEC ‘06, Dallas, TX, USA, 19–23 March 2006; p. 7. [Google Scholar]

- Kudtongngam, J.; Sangkarak, K.; Lopattanakij, P.; Liutanakul, P.; Chunkag, V. Implementation of automatic interleaving and load current sharing techniques using single interleaving bus. IET Power Electron. 2016, 9, 1496–1504. [Google Scholar] [CrossRef]

- Gateau, G.; Cousineau, M.; Mannes-Hillesheim, M.; Dung, P.Q. Digital Decentralized Current Control for Parallel Multiphase Converter. In Proceedings of the 2019 IEEE International Conference on Industrial Technology (ICIT), Melbourne, Australia, 13–15 February 2019; pp. 1761–1766. [Google Scholar]

- Nguyen, P.C.; Phan, Q.D. The Development of Decentralized Space Vector PWM Method for Multilevel Multiphase Converters. In Proceedings of the 2020 IEEE Eighth International Conference on Communications and Electronics (ICCE), Phu Quoc Island, Vietnam, 13–15 January 2021; pp. 163–168. [Google Scholar]

- Luc-Andre, G.; Marc, C.; Isaac, S.; Philippe, L. Real-Time Simulation of Interleaved Converters with Decentralized Control. In Proceedings of the International Conference on Renewable Energies and Power Quality, Madrid, Spain, 4–6 May 2016. [Google Scholar]

- Cousineau, M.; Xiao, Z. Fully decentralized modular approach for parallel converter control. In Proceedings of the 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 17–21 March 2013; pp. 237–243. [Google Scholar]

- Phan, Q.D.; Gateau, G.; Nguyen, M.T.; Cousineau, M.; Ngoc, T.P.T. Decentralized Interleaving and Current Control for Multicellular Serial-Parallel Converters. In Proceedings of the 2019 International Symposium on Electrical and Electronics Engineering (ISEE), Ho Chi Minh City, Vietnam, 10–12 October 2019; pp. 1–6. [Google Scholar]

- Sinha, M.; Poon, J.; Johnson, B.B.; Rodriguez, M.; Dhople, S.V. Decentralized Interleaving of Parallel-connected Buck Converters. IEEE Trans. Power Electron. 2019, 34, 4993–5006. [Google Scholar] [CrossRef]

- Dutta, S.; Johnson, B. A Practical Digital Implementation of Completely Decentralized Ripple Minimization in Parallel-Connected DC–DC Converters. IEEE Trans. Power Electron. 2022, 37, 14422–14433. [Google Scholar] [CrossRef]

| Parameter | Description | Value |

|---|---|---|

| Vin | Input voltage | 24 V |

| Vout | Output voltage | 8 V |

| fsw | Nominal switching frequency | 10 kHz |

| Cf | Output capacitance | 23.5 μF |

| Rload | Load resistance | 1 Ω |

| Lf | Buck filter inductance | 200 μH |

| m | Droop coefficient | 0.5 V/A |

| Simulation time step | 50 ns | |

| Sample rate | 40 kHz |

| Parameter | Description | Value |

|---|---|---|

| Vin | Input voltage | 24 V |

| Vout | Output voltage | 8 V |

| fsw | Nominal switching frequency | 10 kHz |

| Cf | Output capacitance | 23.5 μF |

| Rload | Load resistance | 5 Ω |

| Lf | Buck filter inductance | 220 μH |

| G | Phase-shifting gain | 1000 rad/(V·rad·s) |

| M | Droop coefficient | 0.5 V/A |

| Controller time step | 100 μs | |

| ADC sample rate | 40 kHz | |

| Description | Part number | Manufacturer |

| DSP | TMS320F28335 | Texas Instr. |

| MOSFET | NCE6005AS | NCE |

| Gate driver | TF2184-TAH | Telefunken |

| Scenario | Indicator | Simulation | Experiment |

|---|---|---|---|

| Startup | Transient time | 10 ms | 15 ms |

| Unit addition | Transient time | 13 ms | 10 ms |

| Unit subtraction | Transient time | 13 ms | 10 ms |

| Load step | Transient time | 10 ms | 15 ms |

| Single converter | Ripple (peak-to-peak) | 1.31 V | 1.50 V |

| 1.21 V | |||

| 1.20 V | |||

| 1.33 V | |||

| 2-parallel | Ripple (peak-to-peak) | 0.32 V | 0.45 V |

| 3-parallel | Ripple (peak-to-peak) | 0.01 V | 0.30 V |

| 4-parallel | Ripple (peak-to-peak) | 0.14 V | 0.25 V |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, H.; Fu, Q.; Wang, B.; Chen, Y.; Su, Y. Communication-Free Interleaving Control of Parallel-Connected DC-DC Converters. Electronics 2023, 12, 2111. https://doi.org/10.3390/electronics12092111

Yang H, Fu Q, Wang B, Chen Y, Su Y. Communication-Free Interleaving Control of Parallel-Connected DC-DC Converters. Electronics. 2023; 12(9):2111. https://doi.org/10.3390/electronics12092111

Chicago/Turabian StyleYang, Hang, Qing Fu, Benfei Wang, Yishan Chen, and Yixing Su. 2023. "Communication-Free Interleaving Control of Parallel-Connected DC-DC Converters" Electronics 12, no. 9: 2111. https://doi.org/10.3390/electronics12092111

APA StyleYang, H., Fu, Q., Wang, B., Chen, Y., & Su, Y. (2023). Communication-Free Interleaving Control of Parallel-Connected DC-DC Converters. Electronics, 12(9), 2111. https://doi.org/10.3390/electronics12092111