On the Minimum Value of Split DC Link Capacitances in Three-Phase Three-Level Grid-Connected Converters Operating with Unity Power Factor with Limited Zero-Sequence Injection

Abstract

1. Introduction

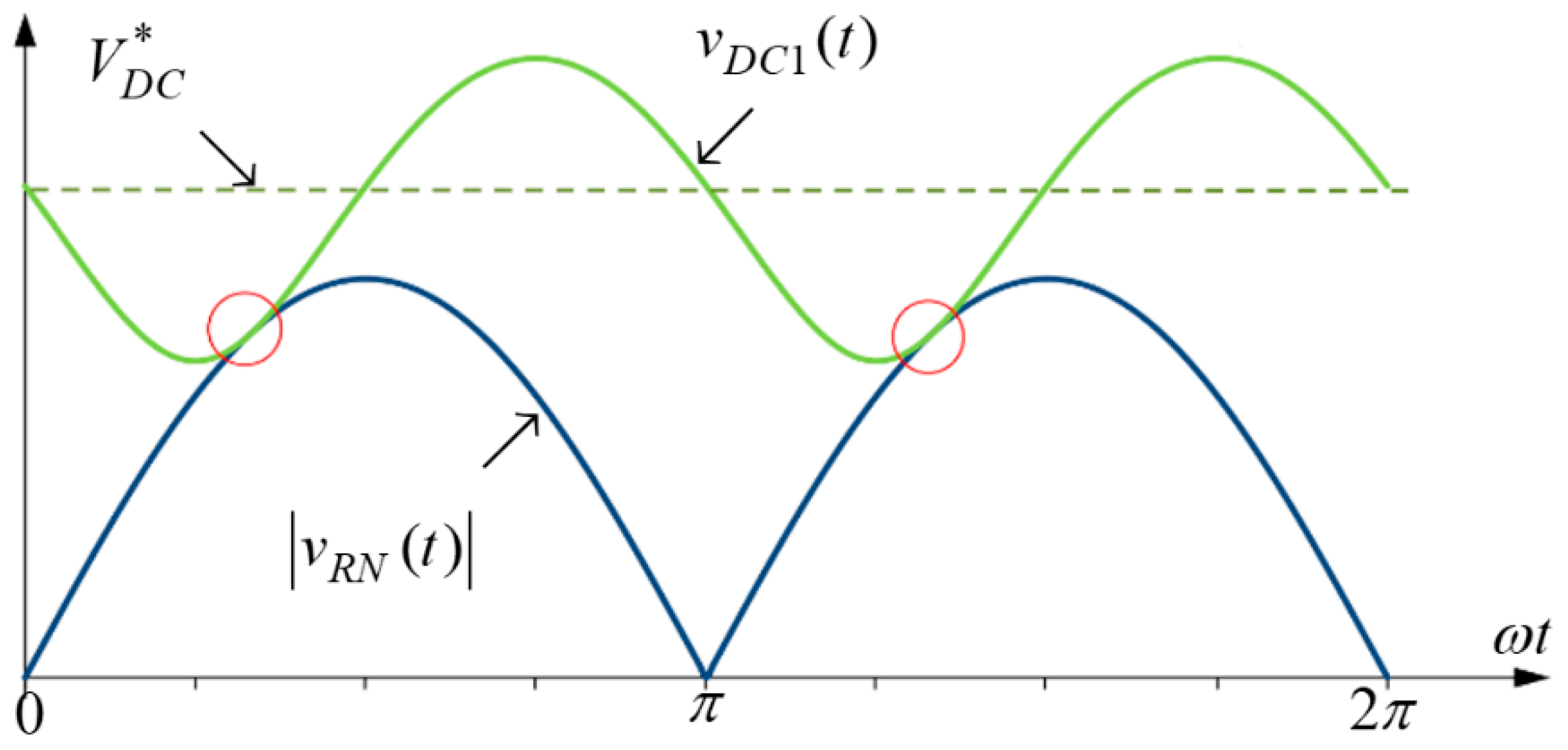

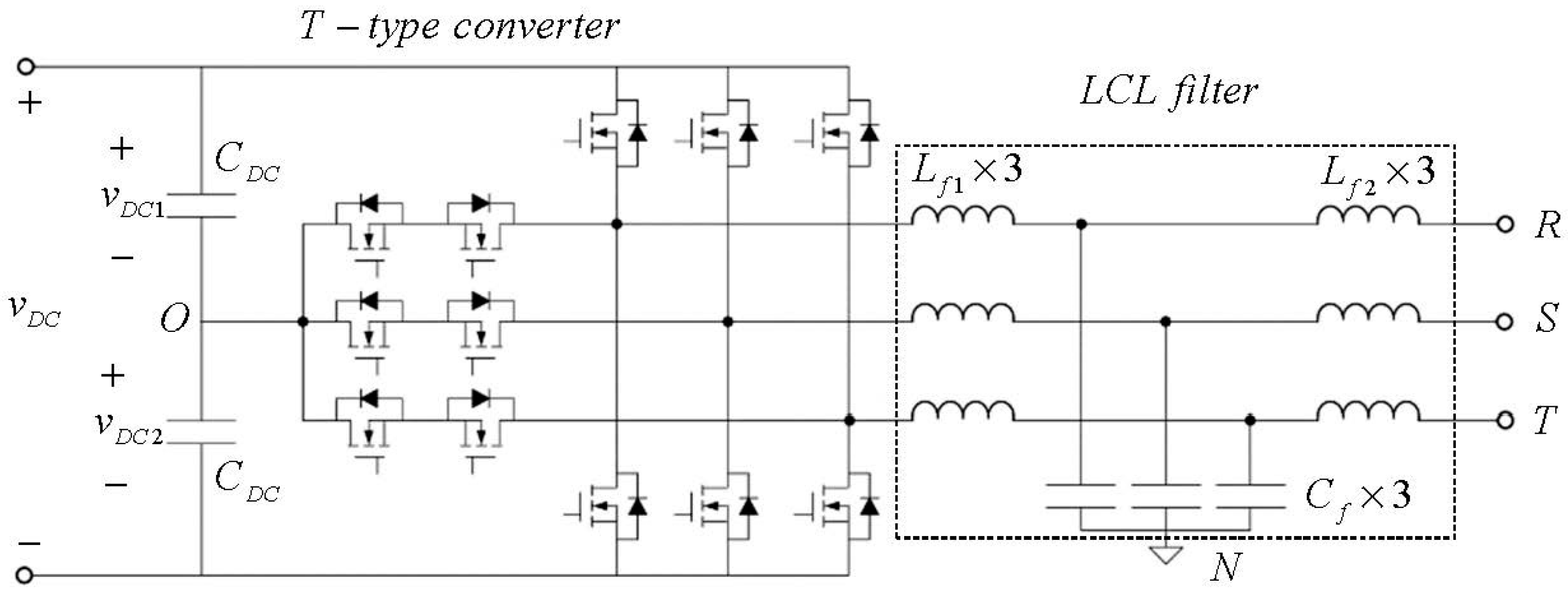

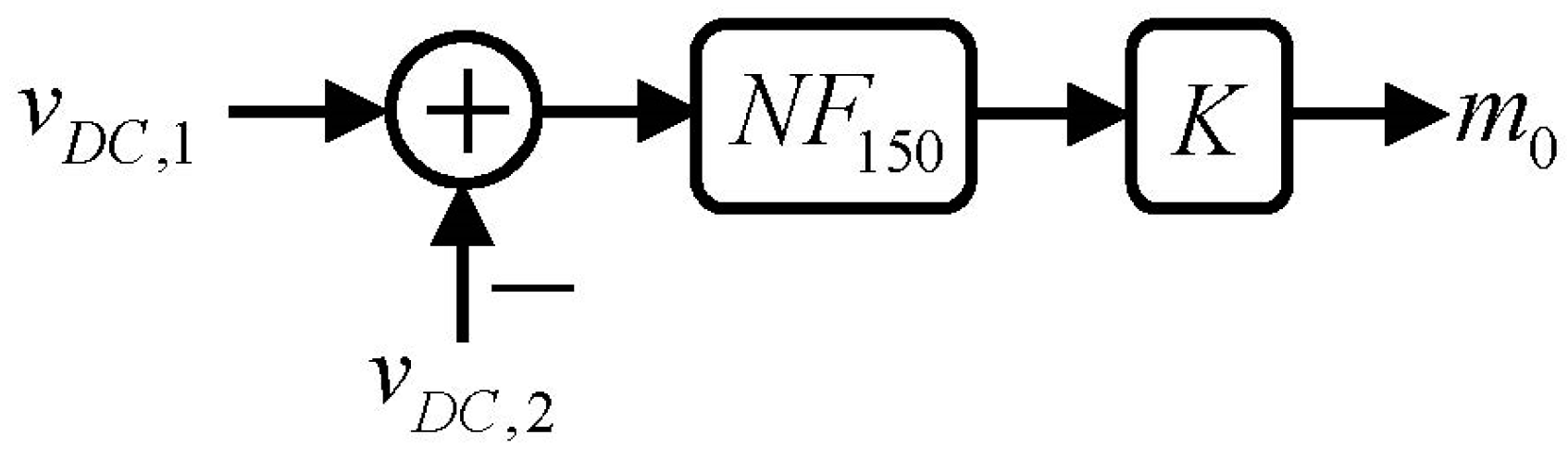

2. Materials and Methods

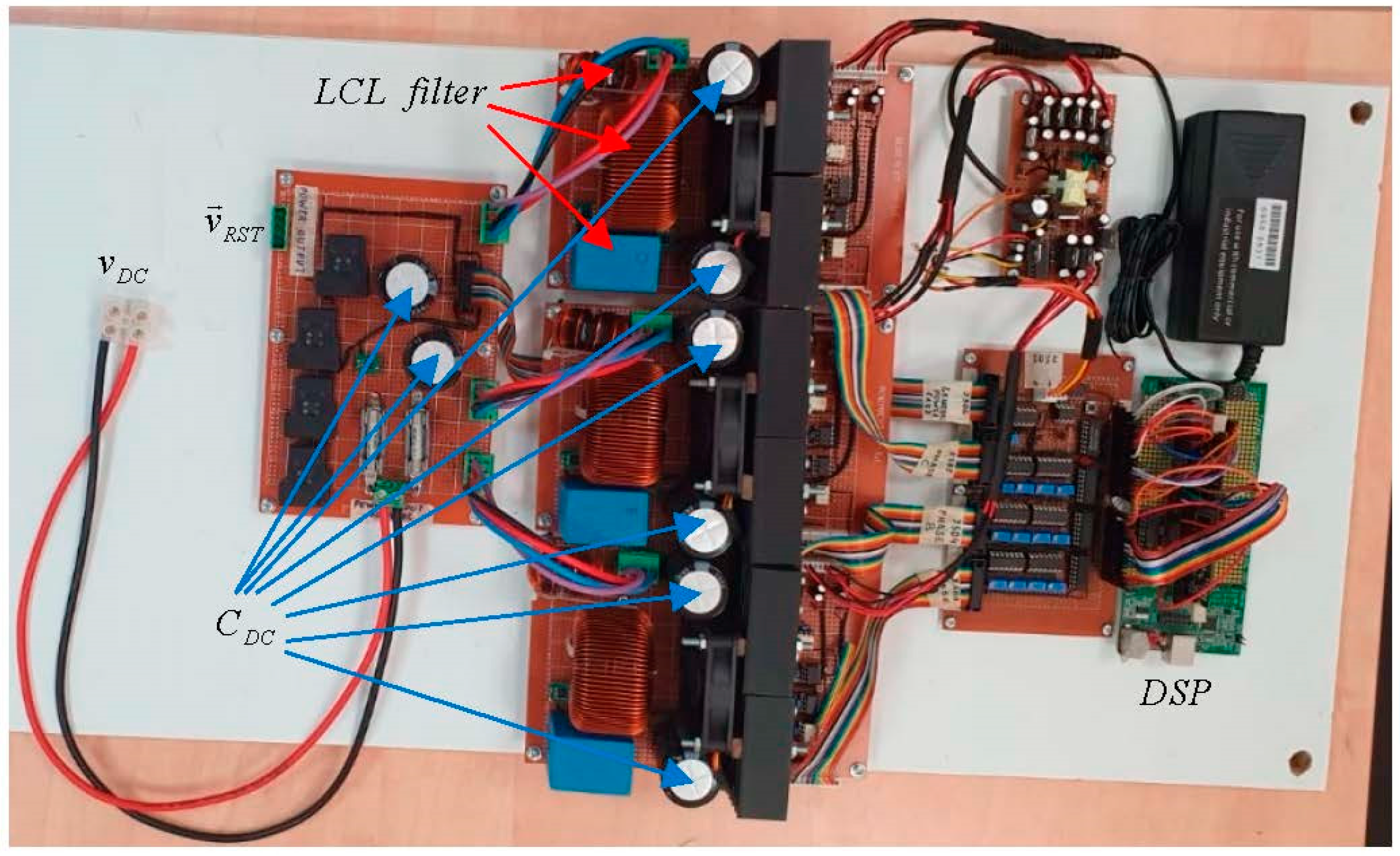

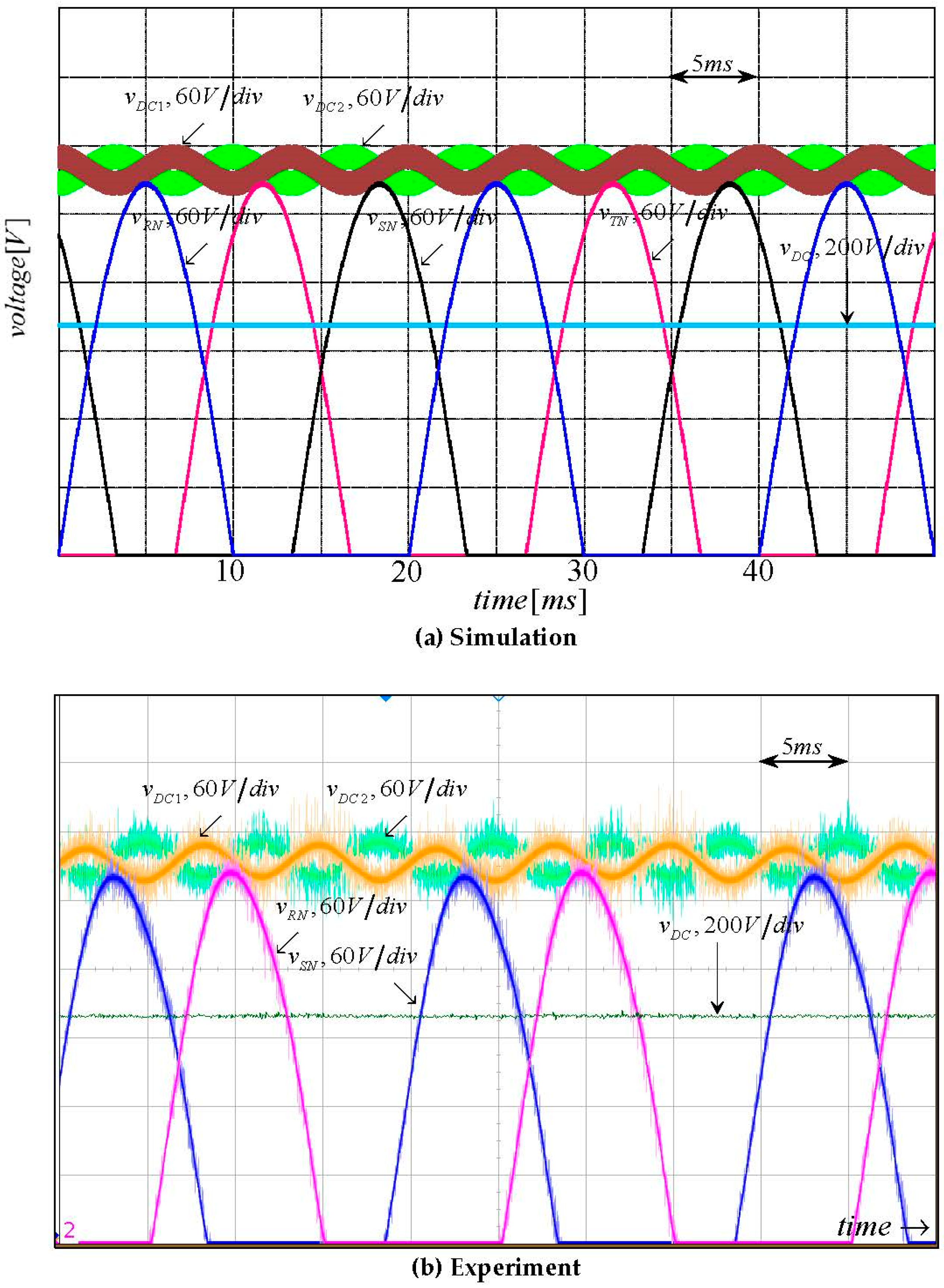

3. Verification

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Gazafrudi, S.; Langerudy, A.; Fuchs, E.; Al-Haddad, K. Power quality issues in railway electrification: A comprehensive perspective. IEEE Trans. Ind. Electron. 2015, 62, 3081–3090. [Google Scholar] [CrossRef]

- Taul, M.G.; Wang, X.; Davari, P.; Blaabjerg, F. Current reference generation based on next-generation grid code requirements of grid-tied converters during asymmetrical faults. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 3784–3797. [Google Scholar] [CrossRef]

- Singh, B.; Singh, B.N.; Chandra, A.; Al-Haddad, K.; Pandey, A.; Kothari, D.P. A review of three-phase improved power quality AC-DC converters. IEEE Trans. Ind. Electron. 2004, 51, 641–660. [Google Scholar] [CrossRef]

- Mellincovsky, M.; Yuhimenko, V.; Peretz, M.M.; Kuperman, A. Low-frequency DC-link ripple elimination in power converters with reduced capacitance by multiresonant direct voltage regulation. IEEE Trans. Ind. Electron. 2017, 64, 2015–2023. [Google Scholar] [CrossRef]

- Mutovkin, A.; Mellincovsky, M.; Yuhimenko, V.; Schacham, S.; Kuperman, A. Conditions for direct applicability of electronic capacitors to dual-stage grid-connected power conversion systems. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1805–1814. [Google Scholar] [CrossRef]

- Baek, J.; Lee, J.-B.; Kim, J.-K. Effective hold-up time extension method using fan control in server power systems. IEEE Trans. Ind. Electron. 2020, 67, 5820–5824. [Google Scholar] [CrossRef]

- Huai, W.; Blaabjerg, F. Reliability of capacitors for DC-link applications in power electronic converters—An overview. IEEE Trans. Ind. Appl. 2014, 50, 3569–3578. [Google Scholar]

- Wang, H.; Wang, H.; Zhu, G.; Blaabjerg, F. An overview of capacitive DC links: Topology derivation and scalability analysis. IEEE Trans. Power Electron. 2019, 35, 1805–1829. [Google Scholar] [CrossRef]

- Wang, H.; Wang, H. Capacitive DC links in power electronic systems—Reliability and circuit design. Chin. J. Electr. Eng. 2018, 4, 29–36. [Google Scholar]

- Mutovkin, A.; Yuhimenko, V.; Schacham, S.; Kuperman, A. Simple and straightforward realization of an electronic capacitor. Electron. Lett. 2019, 55, 220–222. [Google Scholar] [CrossRef]

- Mutovkin, A.; Yuhimenko, V.; Mellinkovsky, M.; Schacham, S.; Kuperman, A. Control of direct voltage regulated active DC-link capacitance reduction circuits to allow plug-and-play operation. IEEE Trans. Ind. Electron. 2019, 66, 6527–6537. [Google Scholar] [CrossRef]

- Mutovkin, A.; Yuhimenko, V.; Schacham, S.; Kuperman, A. Nonlinear control of electronic capacitor for enhanced stability and dynamic response. IEEE Trans. Ind. Electron. 2021, 68, 6881–6892. [Google Scholar] [CrossRef]

- Lamar, D.G.; Sebastian, J.; Arias, M.; Fernandez, A. On the limit of the output capacitor reduction in power factor correctors by distorting the line input current. IEEE Trans. Power Electron. 2012, 27, 1168–1176. [Google Scholar] [CrossRef]

- Hanson, A.J.; Martin, A.F.; Perreault, D.J. Energy and size reduction of grid-interfaced energy buffers through line waveform control. IEEE Trans. Power Electron. 2019, 34, 11442–11453. [Google Scholar] [CrossRef]

- Marcos-Pastor, A.; Vidal-Idiarte, E.; Cid-Pastor, A.; Martinez-Salamero, L. Minimum DC-link capacitance for single-phase applications with power factor correction. IEEE Trans. Ind. Electron. 2020, 67, 5204–5208. [Google Scholar] [CrossRef]

- Strajnikov, P.; Kuperman, A. On the minimum DC link capacitance in practical PFC rectifiers considering THD requirements and load transients. IEEE Trans. Ind. Electron. 2022, 69, 11067–11075. [Google Scholar] [CrossRef]

- Krein, P.T.; Balog, R.S.; Mirjafari, M. Minimum energy and capacitance requirements for single-phase inverters and rectifiers using a ripple port. IEEE Trans. Power Electron. 2012, 27, 4690–4698. [Google Scholar] [CrossRef]

- Strajnikov, P.; Kuperman, A. DC link capacitance reduction in PFC rectifiers employing PI+Notch voltage controllers. IEEE Trans. Power Electron. 2023, 38, 977–986. [Google Scholar] [CrossRef]

- Erickson, R.W.; Maksimovic, D. Fundamentals of Power Electronics; Springer: New York, NY, USA, 2001. [Google Scholar]

- Malesani, L.; Rossetto, L.; Tenti, P.; Tomasin, P. AC/DC/AC PWM converter with reduced energy storage in the DC link. IEEE Trans. Ind. Appl. 1995, 31, 287–292. [Google Scholar] [CrossRef]

- Messo, T.; Jokipii, J.; Puukko, J.; Suntio, T. Determining the value of DC-link capacitance to ensure stable operation of a three-phase photovoltaic inverter. IEEE Trans. Power Electron. 2014, 29, 665–673. [Google Scholar] [CrossRef]

- Stecca, M.; Soeiro, T.B.; Elizondo, L.R.; Bauer, P.; Palensky, P. Comparison of two and three-level DC-AC converters for a 100 kW battery energy storage system. In Proceedings of the 2020 IEEE 29th International Symposium on Industrial Electronics (ISIE), Delft, The Netherlands, 17–19 June 2020; pp. 677–682. [Google Scholar]

- Tehrani, K.A.; Rasoanarivo, I.; Andriatsioharana, H.; Sargos, F.M. A new multilevel inverter model NP without clamping diodes. In Proceedings of the 2008 34th Annual Conference of IEEE Industrial Electronics, Orlando, FL, USA, 10–13 November 2008; pp. 466–472. [Google Scholar]

- Debnath, T.; Gopakumar, K.; Umanand, L.; Zielinski, D.; Rajashekara, K. A nine-level inverter with single DC link and low-voltage capacitors as stacked voltage sources with capacitor voltage control irrespective of load power factor. IEEE Open J. Ind. Electron. Soc. 2022, 3, 522–536. [Google Scholar] [CrossRef]

- Song, Q.; Liu, W.; Yu, Q.; Xie, X.; Wang, Z. A neutral-point potential balancing algorithm for three-level NPC inverters using analytically injected zero-sequence voltage. In Proceedings of the APEC ’03, Eighteenth Annual IEEE Applied Power Electronics Conference and Exposition, 2003, Miami Beach, FL, USA, 9–13 February 2003; pp. 228–233. [Google Scholar]

- Pou, J.; Zaragoza, J.; Rodriguez, P.; Ceballos, S.; Sala, V.M.; Burgos, R.P.; Boroyevich, D. Fast-processing modulation strategy for the neutral-point-clamped converter with total elimination of low-frequency voltage oscillations in the neutral point. IEEE Trans. Ind. Electron. 2007, 54, 2288–2294. [Google Scholar] [CrossRef]

- Alemi, P.; Jeung, Y.-C.; Lee, D.-C. DC-link capacitance minimization in T-type three-level AC/DC/AC PWM converters. IEEE Trans. Ind. Electron. 2015, 62, 1382–1391. [Google Scholar] [CrossRef]

- Sangwongwanich, A.; Novak, M.; Sangwongwanich, S.; Blaabjerg, F. Reliability of DC-link capacitors in three-level NPC inverters under different PWM methods. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 1804–1811. [Google Scholar]

- Srinivas, V.L.; Singh, B.; Mishra, S. Enhanced power quality PV inverter with leakage current suppression for three-phase SECS. IEEE Trans. Ind. Electron. 2022, 69, 5756–5767. [Google Scholar] [CrossRef]

- Zielinski, C.; Stefanczak, B.; Jedrus, K. Phase-independent reactive power compensation based on four-wire power converter in the presence of angular asymmetry between voltage vectors. Energies 2022, 15, 497. [Google Scholar] [CrossRef]

- Cao, D.P.; Song, W.X.; Xi, H.; Chen, G.C.; Chen, C. Research on zero-sequence signal of space-vector modulation for three-level neutral-point-clamped inverter based on vector diagram partition. In Proceedings of the 2009 IEEE 6th International Power Electronics and Motion Control Conference, Wuhan, China, 17–20 May 2009; pp. 1435–1439. [Google Scholar]

- Siton, Y.; Yuhimenko, V.; Baimel, D.; Kuperman, A. Baseline for split DC-link design in three-phase three-level converters operating with unity power factor based on low-frequency partial voltage oscillations. Machines 2022, 10, 722. [Google Scholar] [CrossRef]

- Schechter, N.; Kuperman, A. Zero-sequence manipulation to maintain correct operation of NPC-PFC rectifier upon neutral line disconnection and reconnection. IEEE Trans. Ind. Electron. 2017, 61, 866–872. [Google Scholar] [CrossRef]

- Kolar, J.W.; Friedli, T. The essence of three-phase PFC rectifier systems—Part I. IEEE Trans. Power Electron. 2013, 28, 176–198. [Google Scholar] [CrossRef]

- Friedli, T.; Hartmann, M.; Kolar, J.W. The essence of three-phase PFC rectifier systems—Part II. IEEE Trans. Power Electron. 2014, 29, 543–560. [Google Scholar] [CrossRef]

- Gadelovits, S.; Kuperman, A. Modeling and classical control of unidirectional VIENNA rectifiers. In Proceedings of the 2012 Electric Power Quality and Supply Reliability, Tartu, Estonia, 11–13 June 2012; pp. 1–4. [Google Scholar]

- Singer, S.; Erickson, R.W. Power-source element and its properties. IEEE Proc. Circ. Dev. Syst. 1994, 141, 220–226. [Google Scholar] [CrossRef]

- Available online: https://www.ti.com/lit/ug/tidue53f/tidue53f.pdf (accessed on 13 March 2023).

| Parameter | Value | Units |

|---|---|---|

| VM | V | |

| ω | rad/s | |

| Lf1 | μH | |

| Cf | μF | |

| Lf2 | μH | |

| ESR(Lf1) | mΩ | |

| ESR(Cf) | mΩ | |

| ESR(Lf2) | mΩ | |

| PL | kW | |

| VR | V | |

| α | 0.97 | - |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Siton, Y.; Sitbon, M.; Aharon, I.; Lineykin, S.; Baimel, D.; Kuperman, A. On the Minimum Value of Split DC Link Capacitances in Three-Phase Three-Level Grid-Connected Converters Operating with Unity Power Factor with Limited Zero-Sequence Injection. Electronics 2023, 12, 1994. https://doi.org/10.3390/electronics12091994

Siton Y, Sitbon M, Aharon I, Lineykin S, Baimel D, Kuperman A. On the Minimum Value of Split DC Link Capacitances in Three-Phase Three-Level Grid-Connected Converters Operating with Unity Power Factor with Limited Zero-Sequence Injection. Electronics. 2023; 12(9):1994. https://doi.org/10.3390/electronics12091994

Chicago/Turabian StyleSiton, Yarden, Moshe Sitbon, Ilan Aharon, Simon Lineykin, Dmitry Baimel, and Alon Kuperman. 2023. "On the Minimum Value of Split DC Link Capacitances in Three-Phase Three-Level Grid-Connected Converters Operating with Unity Power Factor with Limited Zero-Sequence Injection" Electronics 12, no. 9: 1994. https://doi.org/10.3390/electronics12091994

APA StyleSiton, Y., Sitbon, M., Aharon, I., Lineykin, S., Baimel, D., & Kuperman, A. (2023). On the Minimum Value of Split DC Link Capacitances in Three-Phase Three-Level Grid-Connected Converters Operating with Unity Power Factor with Limited Zero-Sequence Injection. Electronics, 12(9), 1994. https://doi.org/10.3390/electronics12091994