An 18–19.2 GHz Voltage-Controlled Oscillator with a Compact Varactor-Only Capacitor Array

Abstract

1. Introduction

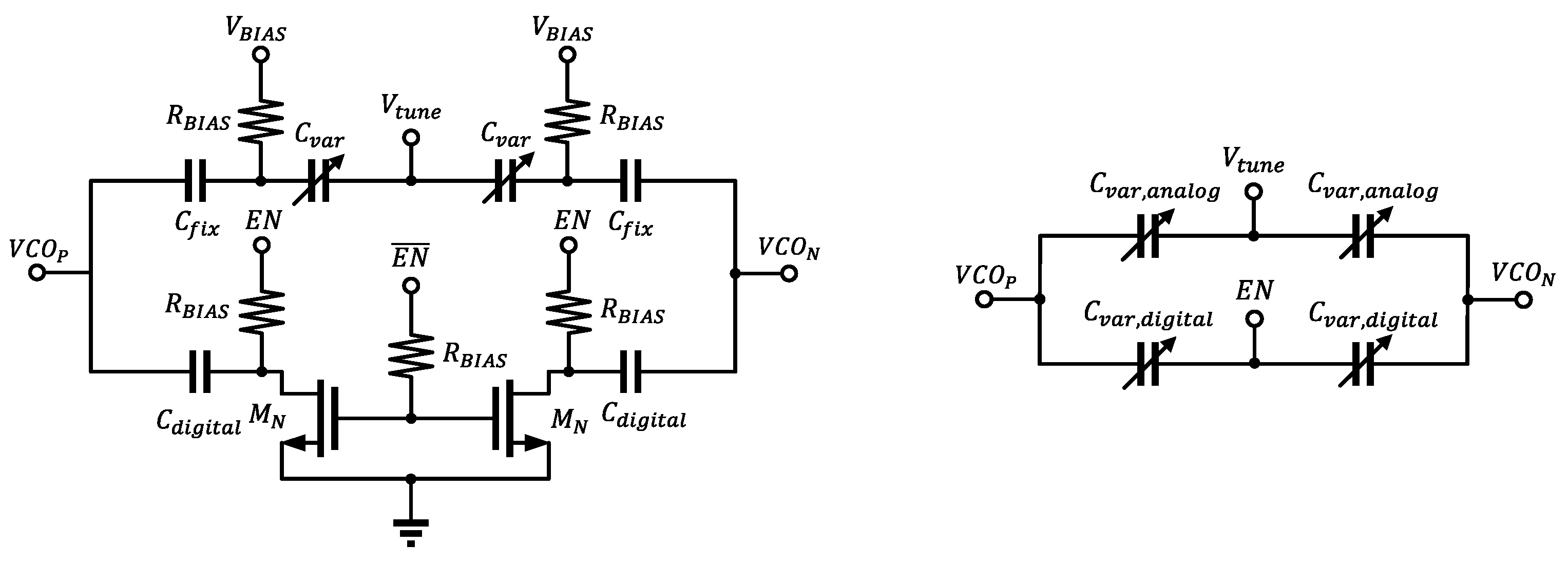

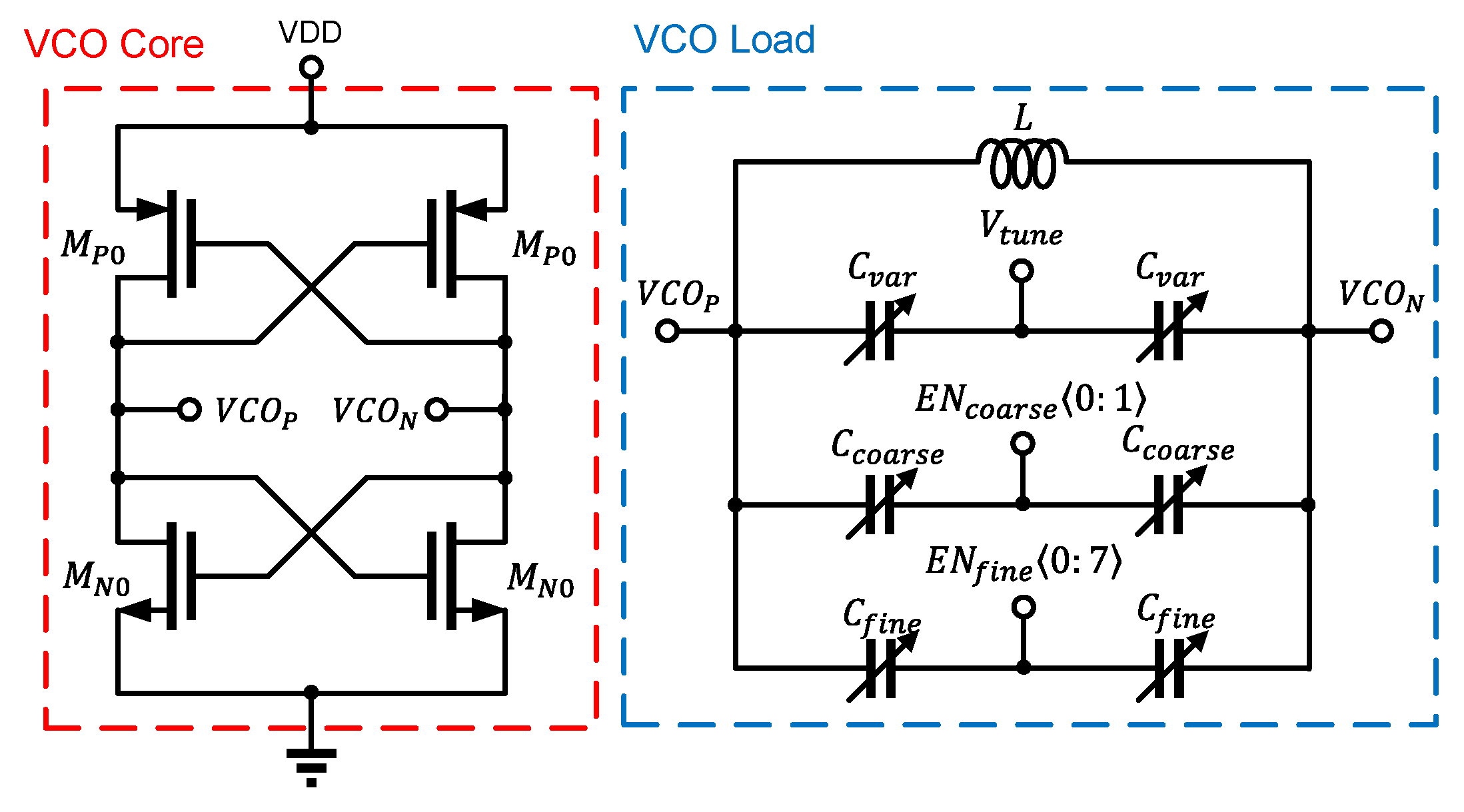

2. Proposed Architecture

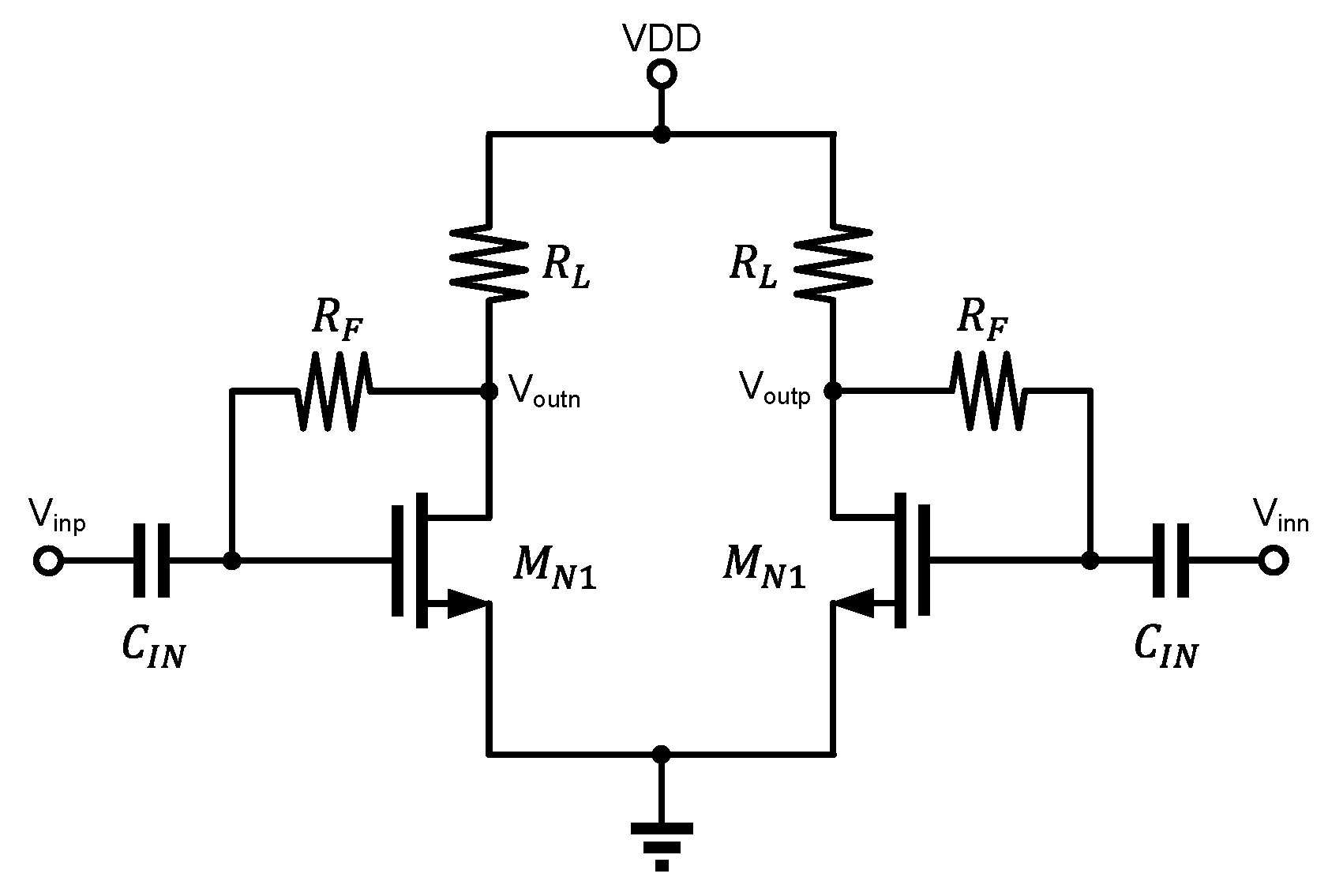

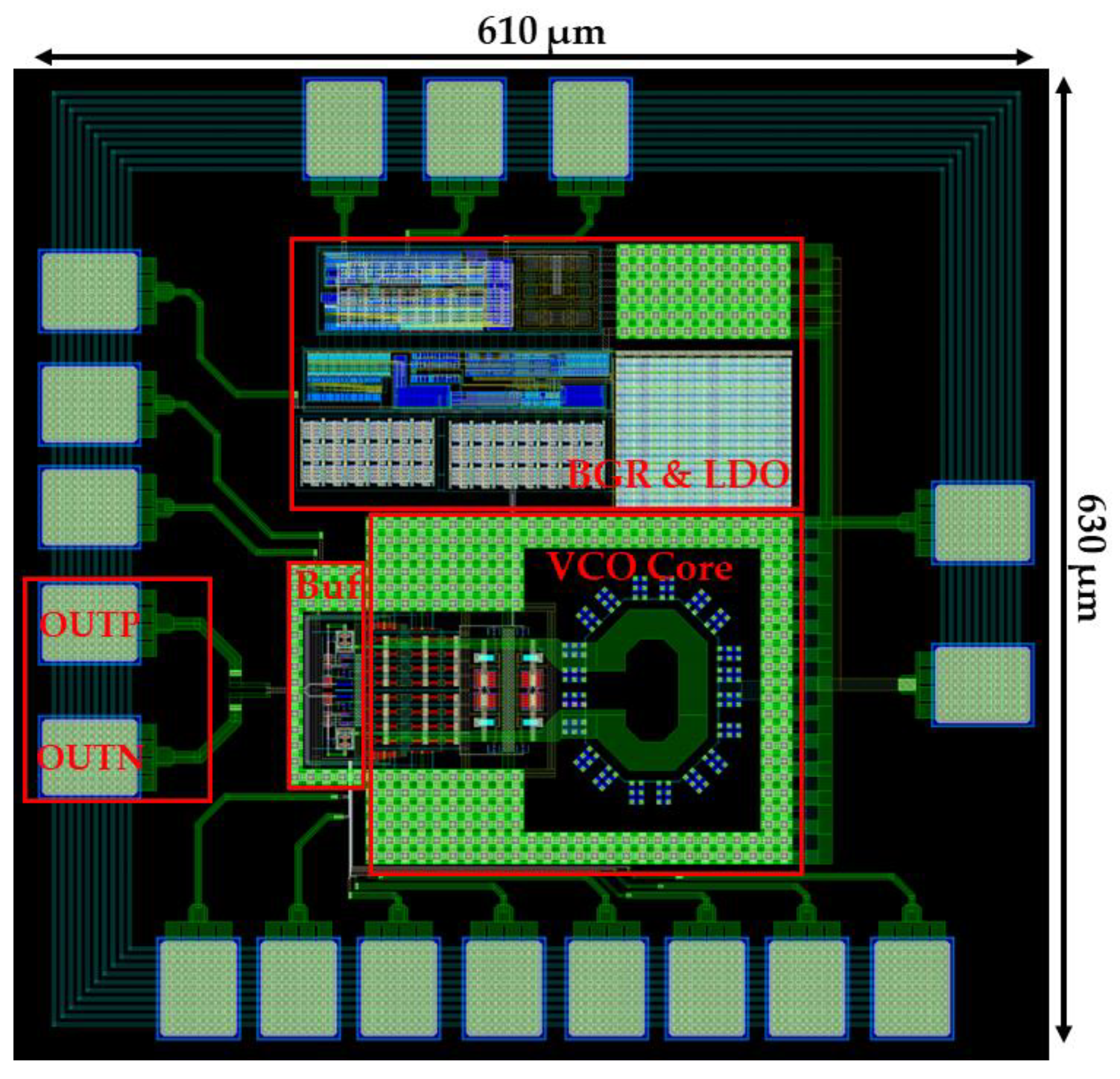

3. Circuit Implementation

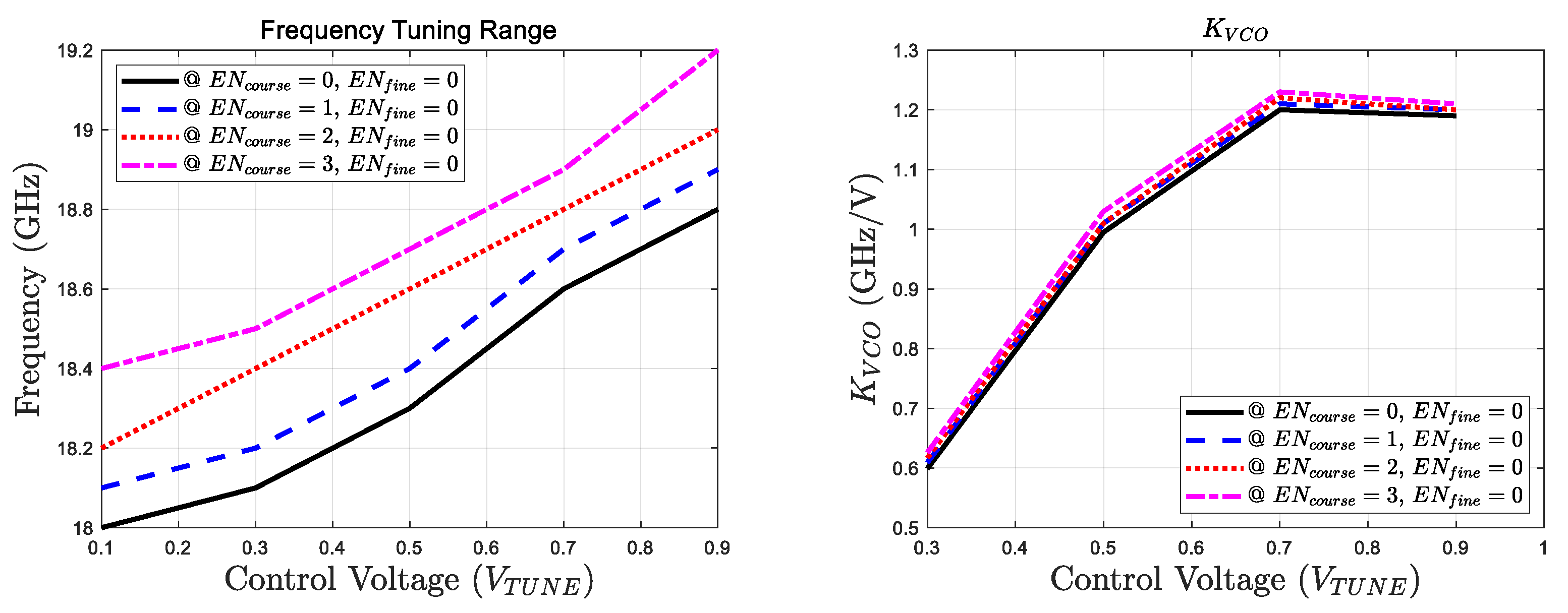

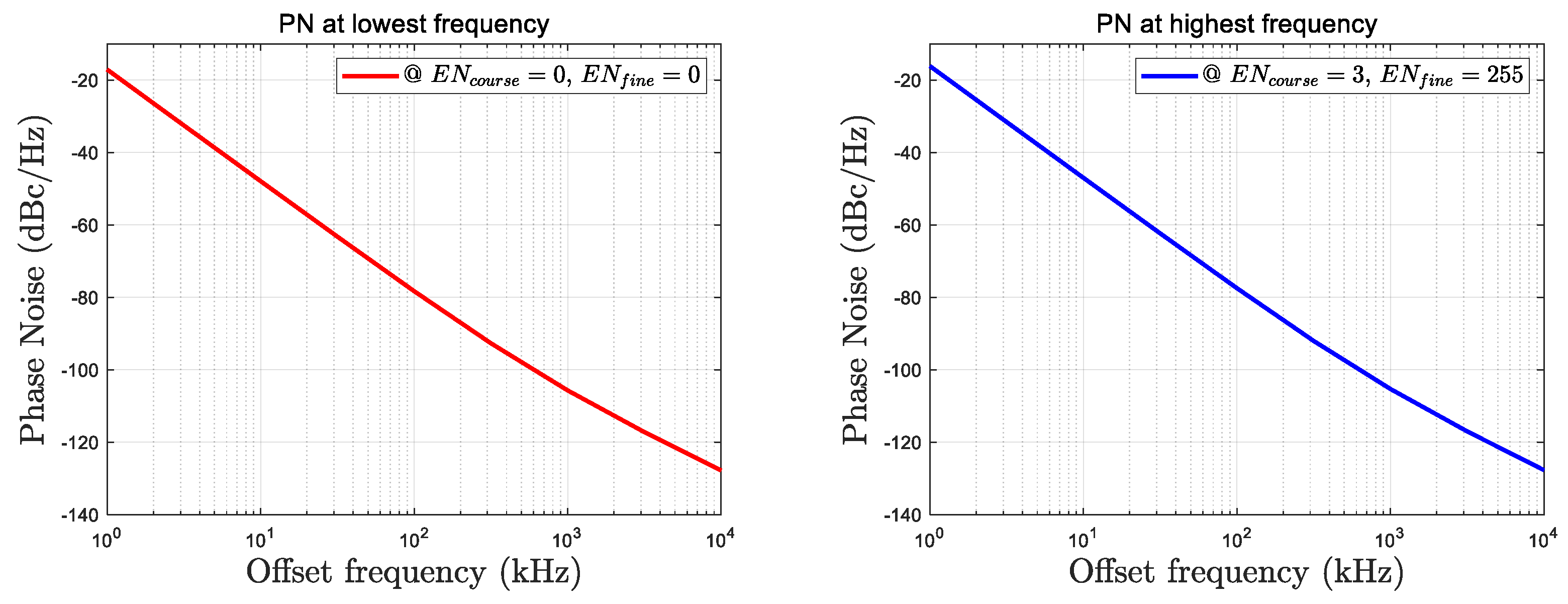

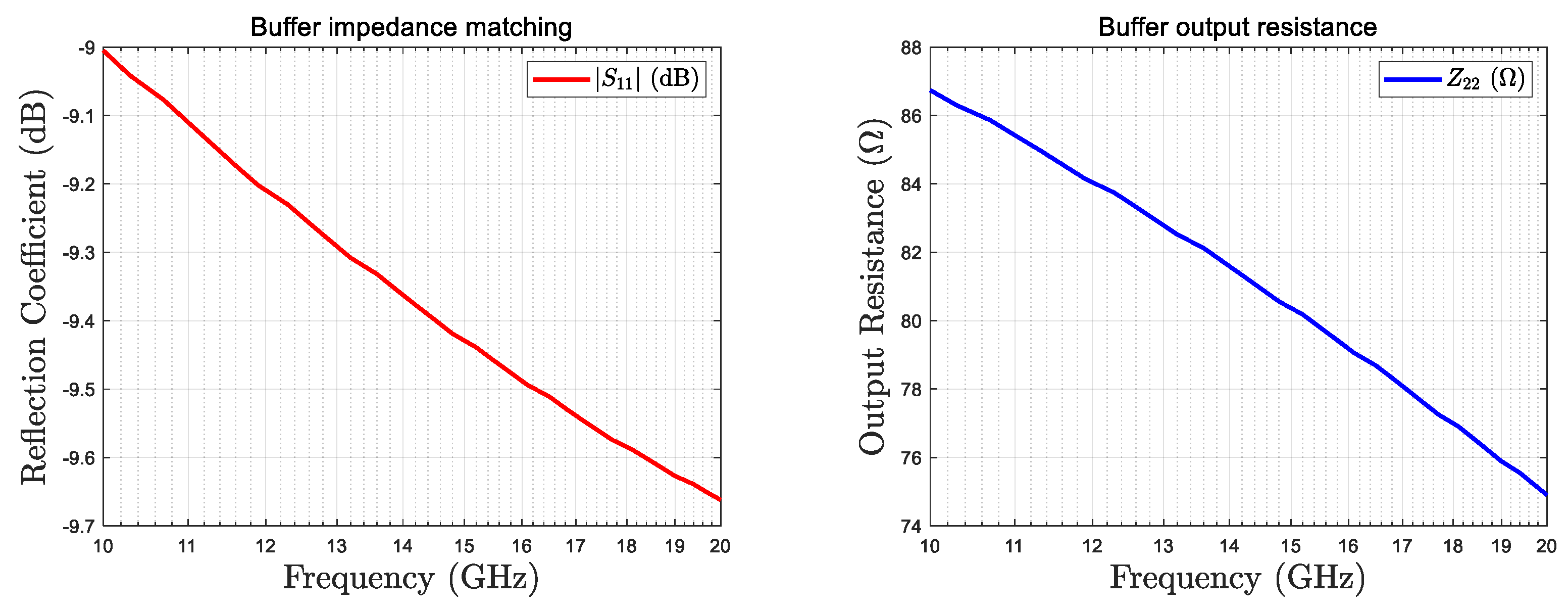

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Tan, W.; Wu, T.; Xing, Z.; Peng, Y.; Liu, H.; Kang, K. A 21.95–24.25 GHz class-C VCO for 24 GHz FMCW radar applications. In Proceedings of the 2019 IEEE MTT-S International Wireless Symposium (IWS), Guangzhou, China, 19–22 May 2019; pp. 1–3. [Google Scholar]

- Cho, Y.-K.; Nam, J.-W.; Lee, S.-W. A Low-Power Class-C Voltage-Controlled Oscillator With Robust Start-Up and Compact High-Q Capacitor Array. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 819–823. [Google Scholar] [CrossRef]

- Yang, J.; Kim, C.Y.; Kim, D.W.; Hong, S. Design of a 24-GHz CMOS VCO With an Asymmetric-Width Transformer. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 173–177. [Google Scholar]

- Kwok, K.; Luong, H.C. Ultra-low-voltage high-performance CMOS VCOs using transformer feedback. IEEE J. Solid State Circuits 2005, 40, 652–660. [Google Scholar] [CrossRef]

- Shahmohammadi, M.; Babaie, M.; Staszewski, R.B. A 1/f noise upconversion reduction technique for voltage-biased RF CMOS oscillators. IEEE J. Solid State Circuits 2016, 51, 2610–2624. [Google Scholar] [CrossRef]

- Hu, Y.; Siriburanon, T.; Staszewski, R.B. Oscillator flicker phase noise: A tutorial. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 538–544. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Prentice Hall Communications Engineering and Emerging Technologies Series; Prentice Hall Press: Hoboken, NJ, USA, 2011. [Google Scholar]

- Wang, X.; Bakkaloglu, B. A 2.4-GHz LC-Tank VCO with Minimum Supply Pushing Regulation Technique. In Proceedings of the 2007 IEEE Radio Frequency Integrated Circuits Symposium, Honolulu, HI, USA, 3–5 June 2007; pp. 303–306. [Google Scholar] [CrossRef]

- Teo, T.H.; Xiong, Y.Z.; Fu, J.S.; Tan, E.L. LC oscillator design at 10-GHz using substrate capacitance with scalable varactor parameters extraction technique. In Proceedings of the 2005 European Microwave Conference, Paris, France, 4–6 October 2005; pp. 1–4. [Google Scholar] [CrossRef]

- Havrlik, M.; Libra, M.; Poulek, V.; Kowrim, P. Analysis of Output Signal Distortion of Galvanic Isolation Circuits for Monitoring the Mains Voltage Waveform. Sensors 2022, 22, 7769. [Google Scholar] [CrossRef] [PubMed]

- Gray, P.R.; Hurst, P.J.; Lewis, S.H.; Meyer, R.G. Analysis and Design of Analog Integrated Circuits, 4th ed.; Wiley: New York, NY, USA, 2001. [Google Scholar]

- Doan, C.H.; Emami, S.; Niknejad, A.M.; Brodersen, R.W. Millimeter-wave CMOS design. IEEE J. Solid State Circuits 2005, 40, 144–155. [Google Scholar] [CrossRef]

- Agarwal, P.; Sah, S.P.; Molavi, R.; Mirabbasi, S.; Pande, P.P.; Oh, S.E.; Kim, J.H.; Heo, D. Switched Substrate-Shield-Based Low-Loss CMOS Inductors for Wide Tuning Range VCOs. IEEE Trans. Microw. Theory Tech. 2017, 65, 2964–2976. [Google Scholar] [CrossRef]

- Chen, Z.; Wang, M.; Chen, J.X.; Liang, W.F.; Yan, P.P.; Zhai, J.F.; Hong, W. Linear CMOS LC -VCO Based on Triple-Coupled Inductors and Its Application to 40-GHz Phase-Locked Loop. IEEE Trans. Microw. Theory Tech. 2017, 65, 2977–2989. [Google Scholar] [CrossRef]

- Xu, T.; Chen, J.; Du, L.; Song, C.; Gu, Q.J.; Xu, Z. An Inverted Complementary Cross-Coupled VCO to Reduce Phase Noise Sensitivity to KVCO. IEEE Microw. Wirel. Technol. Lett. 2023. [Google Scholar] [CrossRef]

- Hejazi, A.; Pu, Y.; Lee, K.-Y. A Design of Wide-Range and Low Phase Noise Linear Transconductance VCO with 193.76 dBc/Hz FoMT for mm-Wave 5G Transceivers. Electronics 2020, 9, 935. [Google Scholar] [CrossRef]

- Ullah, F.; Liu, Y.; Li, Z.; Wang, X.; Sarfraz, M.M.; Zhang, H. A Bandwidth-Enhanced Differential LC-Voltage Controlled Oscillator (LC-VCO) and Superharmonic Coupled Quadrature VCO for K-Band Applications. Electronics 2018, 7, 127. [Google Scholar] [CrossRef]

| Device (VCO) | Dimension | Device (Buffer) | Dimension |

|---|---|---|---|

| MN0 MP0 | MN1 | ||

| Cvar | 280 | CIN | 150 |

| Ccoarse | 27 | RF | |

| Cfine | 15 | RL | |

| L | 100 |

| Parameter | This Work S | [1] M | [2] M | [3] M | [13] M | [14] M | [15] M | [16] S | [17] M |

|---|---|---|---|---|---|---|---|---|---|

| Frequency [GHz] | 18–19.2 | 21.9–24.2 | 19.3–22 | 24.27 | 21–31.6 | 20.85 | 18.7–20.3 | 13–19 | 25.5 |

| PN @ 1 MHz [dBc/Hz] | −105.9 | −100.8 | −106.3 | −100.3 | −89.5 | −100.7 | −107.24 | −110 | −96 |

[V] | 1 | 1 | 1 | 0.65 | 1 | 1 | 1.8 | 0.8 | 1.2 |

| Power [mW] | 21 | 8 | 3.8 | 7.8 | 4.1 | 8.1 | 23.4 | 24 | 12 |

| Area ] | 0.378 a 0.0596 b | 0.19 b | 0.06 b | 0.42 a | 0.25 a | 0.48 a | 0.19 b | 0.14 b | 0.45 a |

| FOM [dBc/Hz] | −178.34 | −179.4 | −186.4 | −179.11 | −171.4 | −178 | −179 | −181.3 | −173.3 |

| Technology | 65 nm CMOS | 65 nm CMOS | 65 nm CMOS | 40 nm CMOS | 65 nm bulk CMOS | 90 nm CMOS | 28 nm CMOS | 40 nm CMOS | 0.13 μm SiGe BiCMOS |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, J.; Mauludin, M.F.; Azzahra, H.A.; Jhon, H.; Lee, S.; Cho, K. An 18–19.2 GHz Voltage-Controlled Oscillator with a Compact Varactor-Only Capacitor Array. Electronics 2023, 12, 1532. https://doi.org/10.3390/electronics12071532

Kim J, Mauludin MF, Azzahra HA, Jhon H, Lee S, Cho K. An 18–19.2 GHz Voltage-Controlled Oscillator with a Compact Varactor-Only Capacitor Array. Electronics. 2023; 12(7):1532. https://doi.org/10.3390/electronics12071532

Chicago/Turabian StyleKim, Jusung, Muhammad Fakhri Mauludin, Hapsah Aulia Azzahra, Heesauk Jhon, Sanghun Lee, and Kunhee Cho. 2023. "An 18–19.2 GHz Voltage-Controlled Oscillator with a Compact Varactor-Only Capacitor Array" Electronics 12, no. 7: 1532. https://doi.org/10.3390/electronics12071532

APA StyleKim, J., Mauludin, M. F., Azzahra, H. A., Jhon, H., Lee, S., & Cho, K. (2023). An 18–19.2 GHz Voltage-Controlled Oscillator with a Compact Varactor-Only Capacitor Array. Electronics, 12(7), 1532. https://doi.org/10.3390/electronics12071532