Fully Integrated 1.8 V Output 300 mA Load LDO with Fast Transient Response

Abstract

1. Introduction

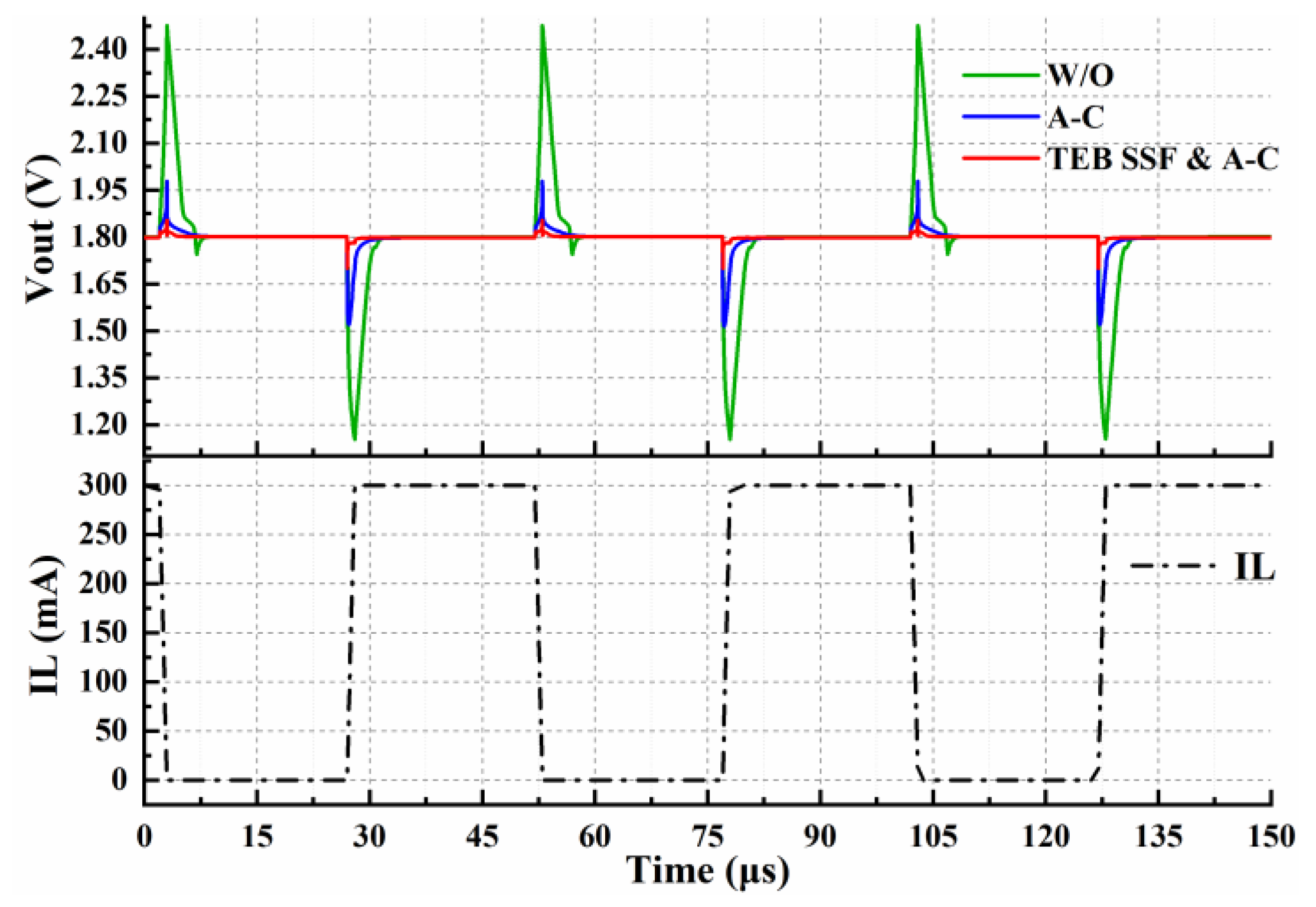

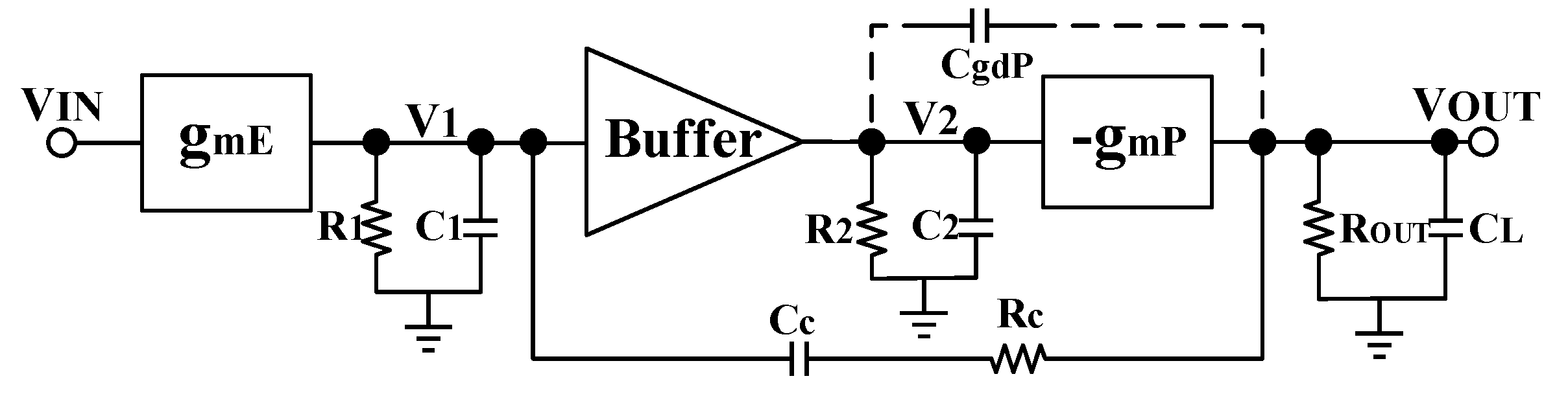

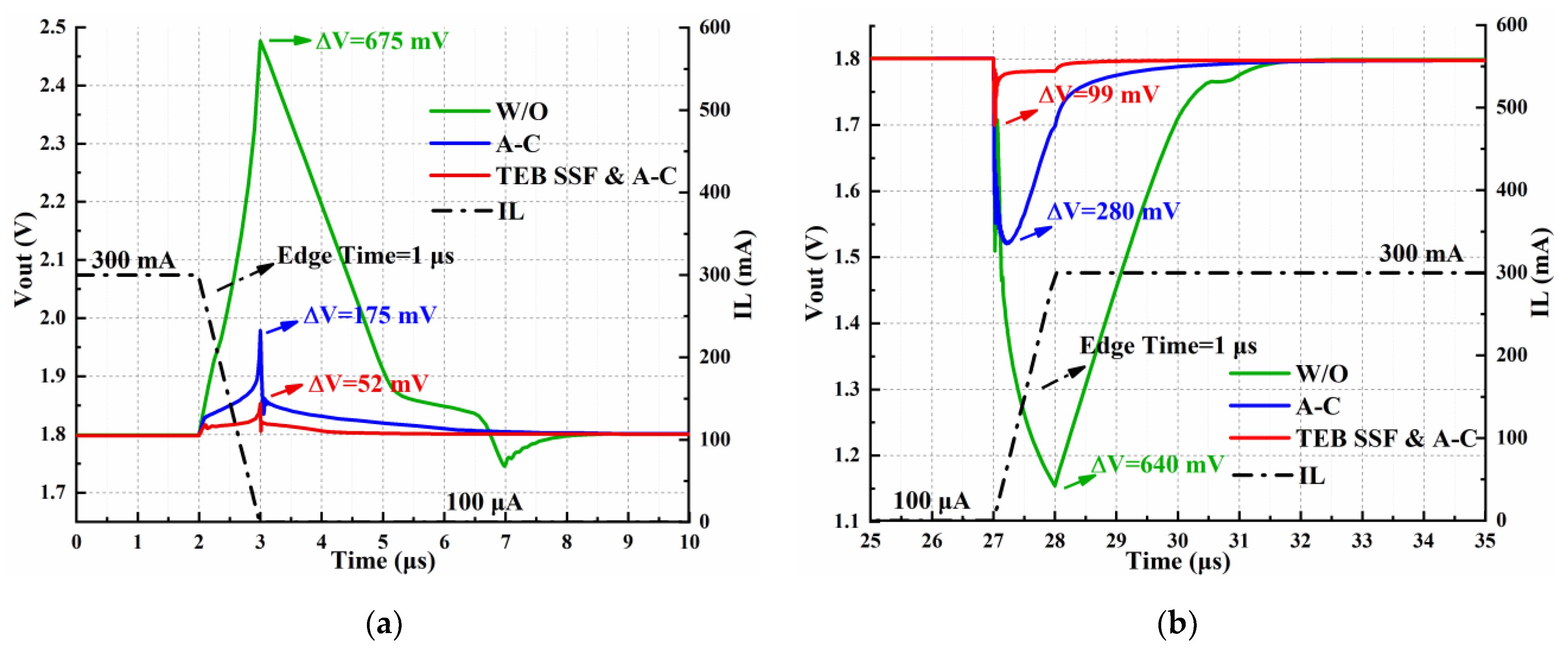

2. Proposed Transient Enhancement Technology and Fully Integrated LDO

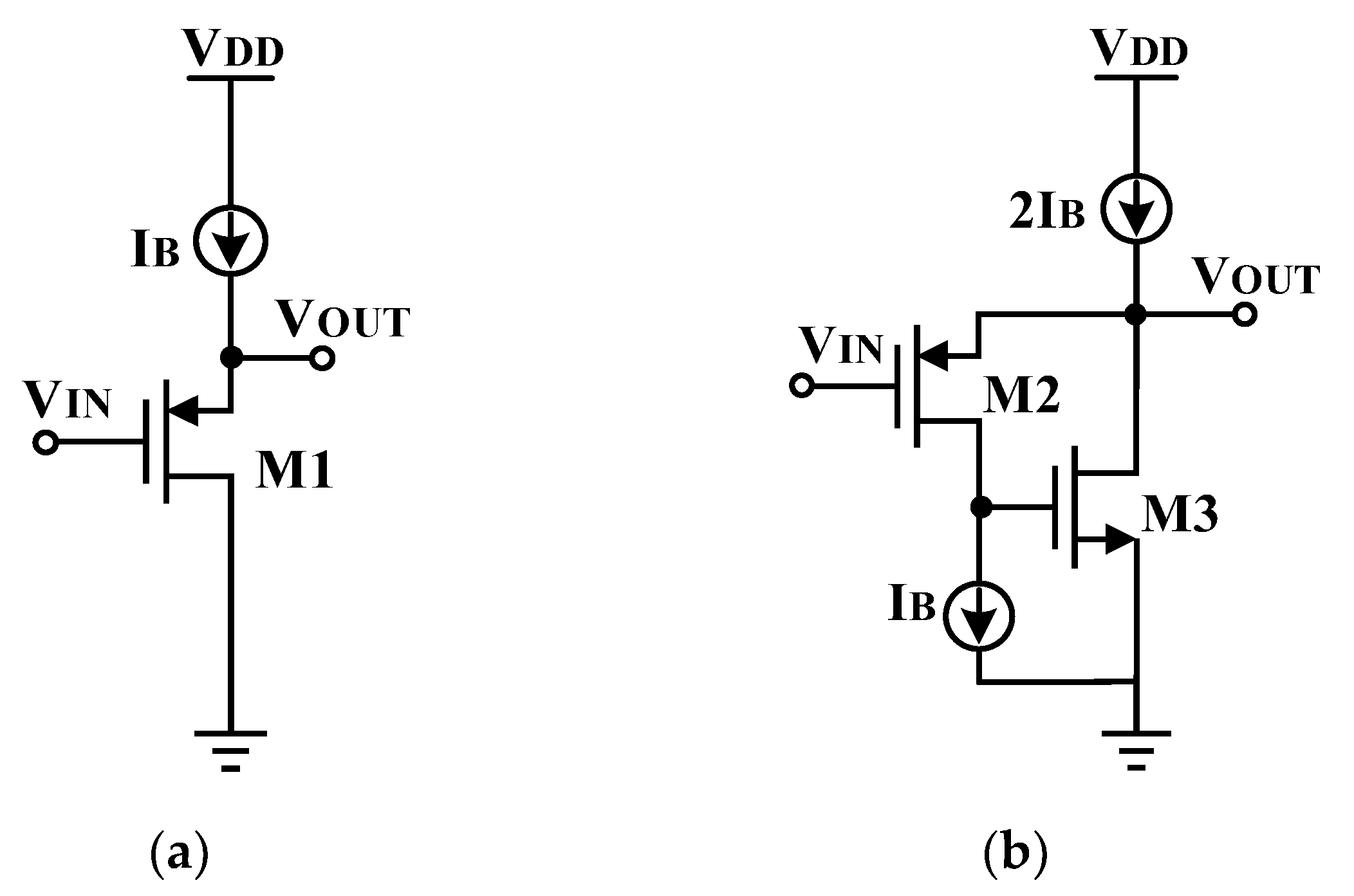

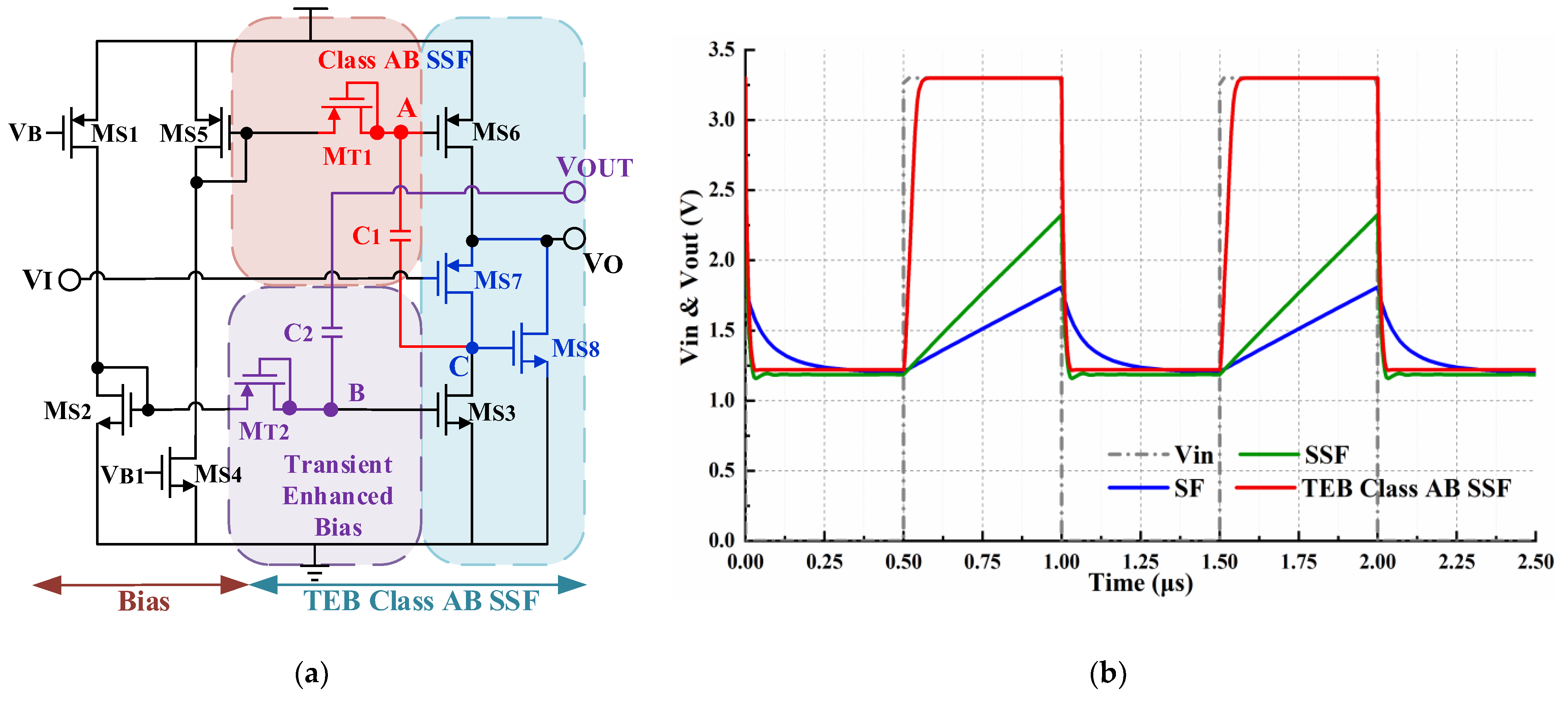

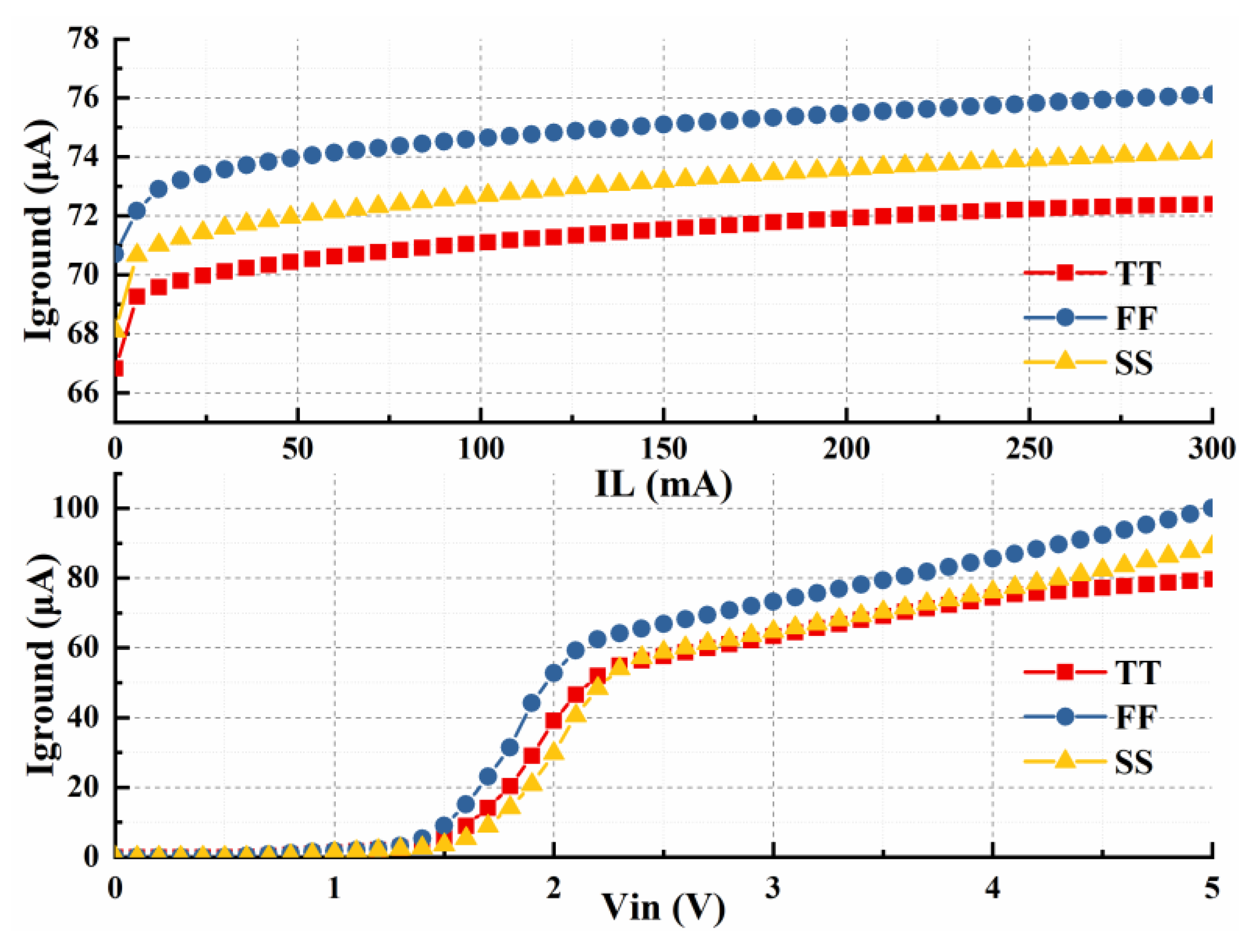

2.1. Transient-Enhanced Biased Class AB Super Source Follower

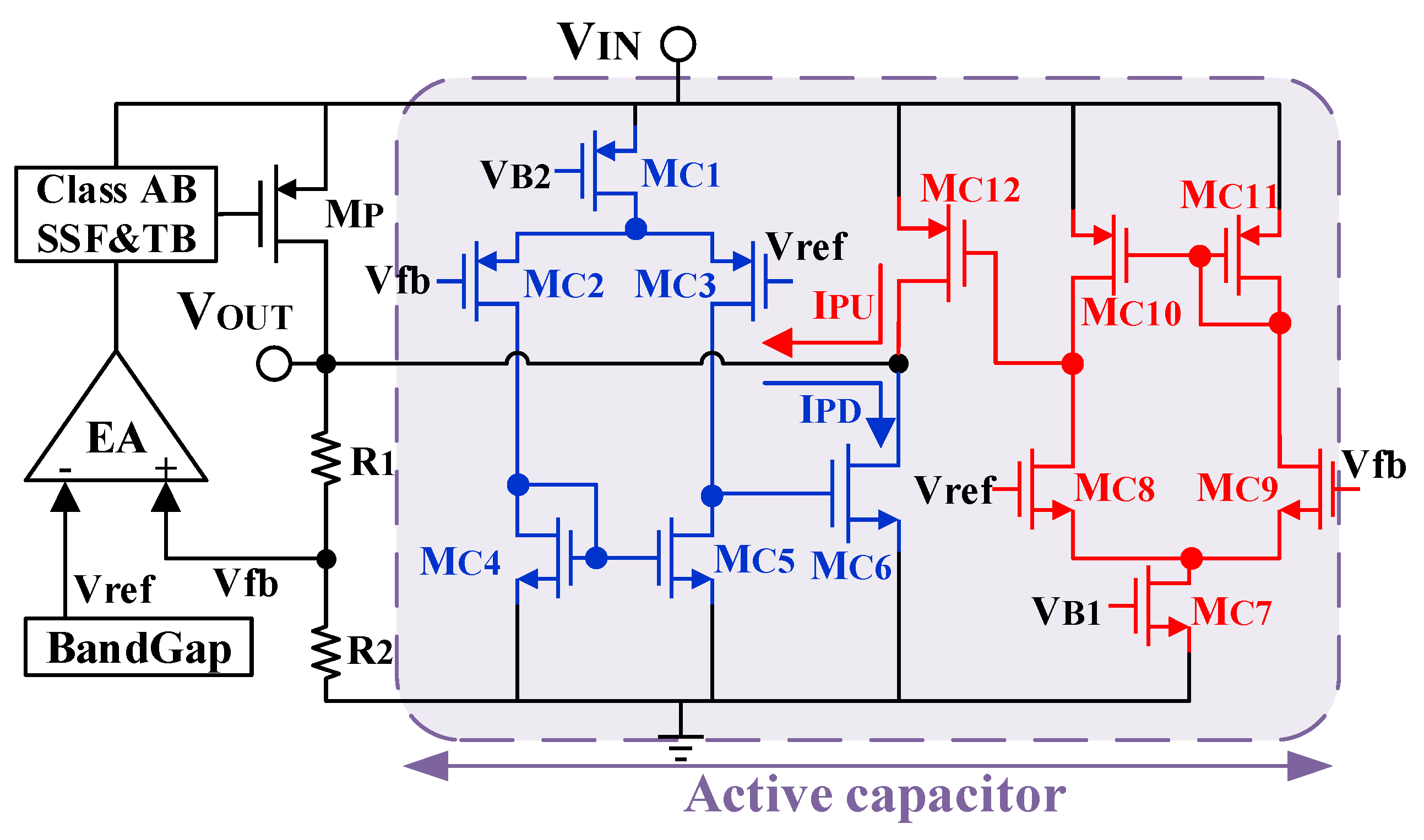

2.2. Proposed Active Capacitor Circuit

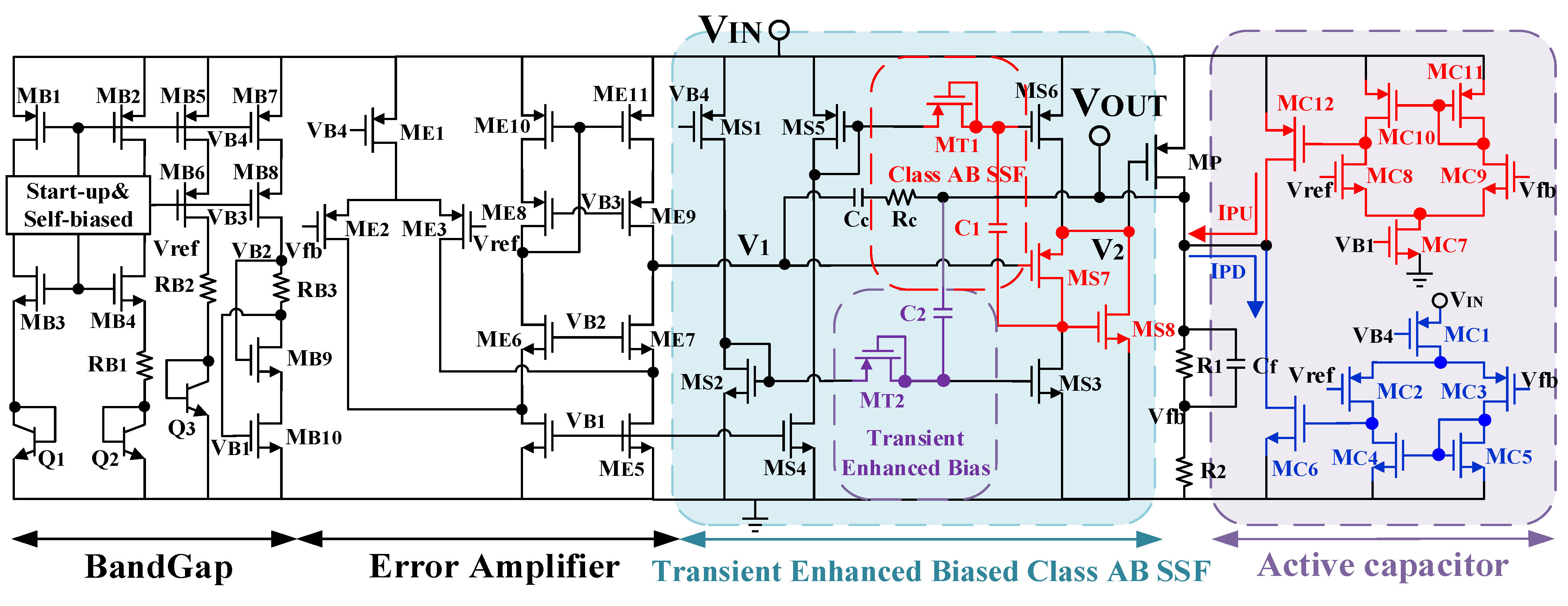

2.3. Proposed Fully Integrated Low Dropout Linear Regulator with Fast Transient Response

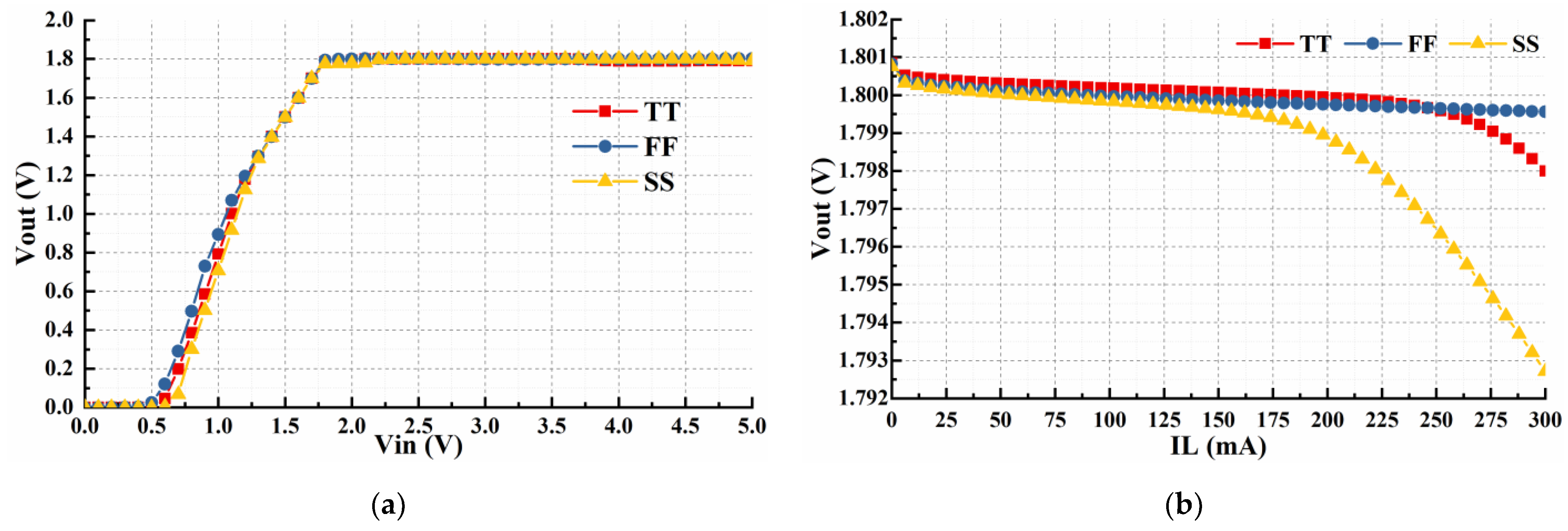

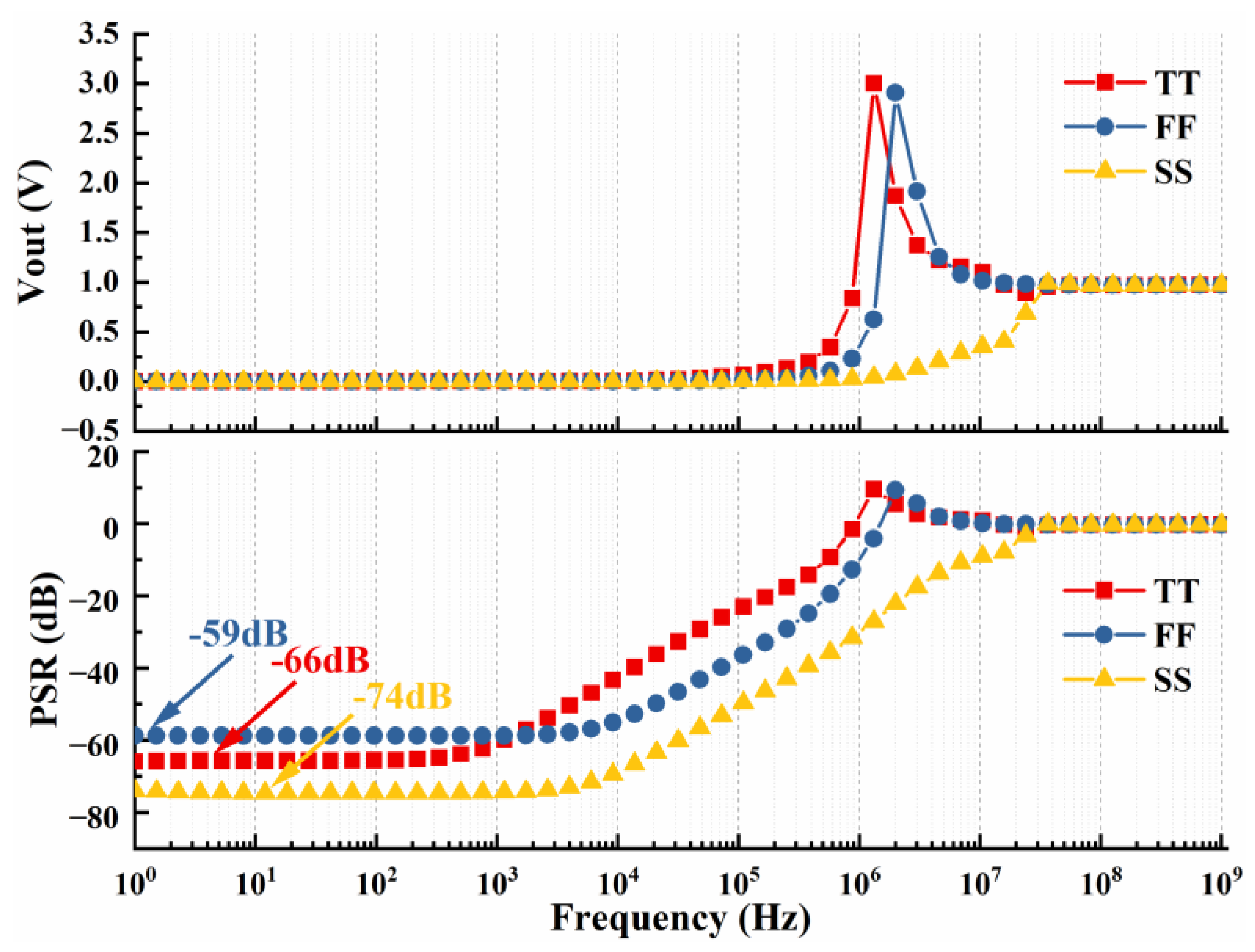

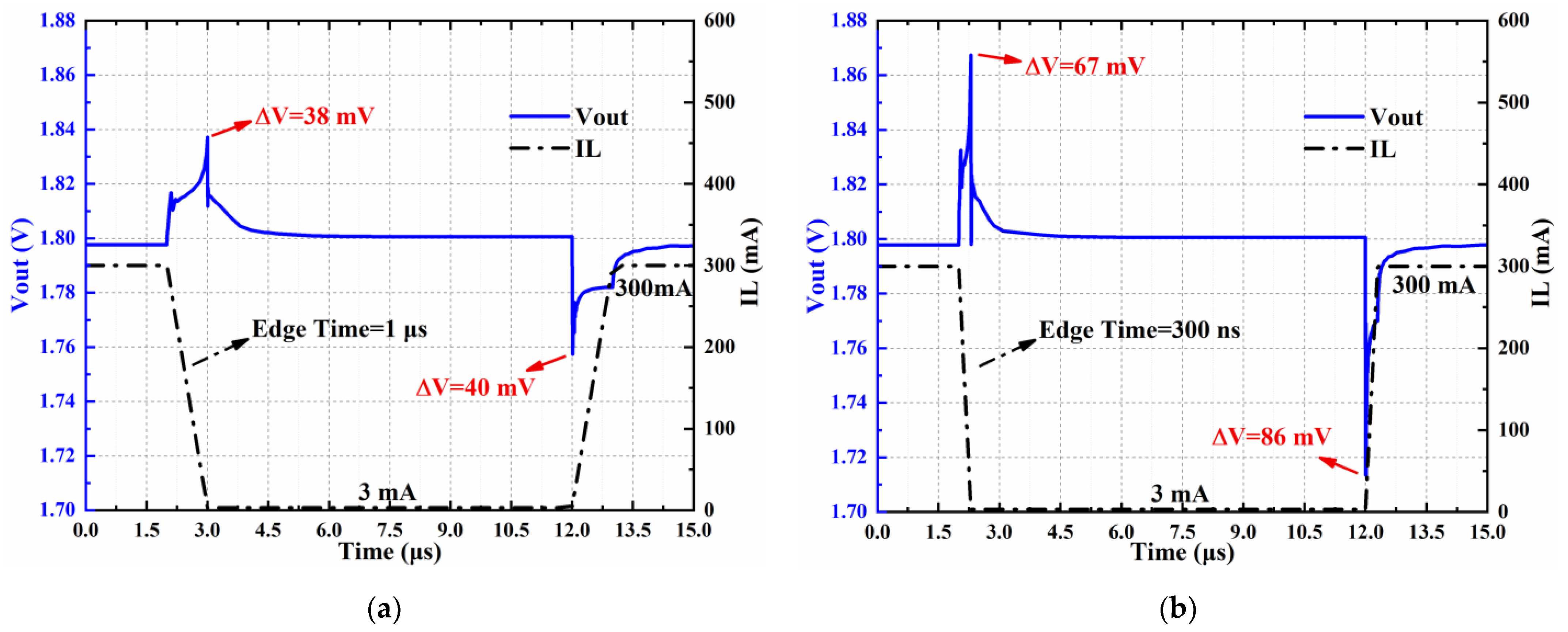

3. Layout and Simulation Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Data Availability Statement

Conflicts of Interest

References

- Hong, S.-W.; Cho, G.-H. High-Gain Wide-Bandwidth Capacitor-Less Low-Dropout Regulator (LDO) for Mobile Applications Utilizing Frequency Response of Multiple Feedback Loops. IEEE Trans. Circuits Syst. I 2016, 63, 46–57. [Google Scholar] [CrossRef]

- Guo, J.; Leung, K.N. A 6-μW Chip-Area-Efficient Output-Capacitorless LDO in 90-Nm CMOS Technology. IEEE J. Solid State Circuits 2010, 45, 1896–1905. [Google Scholar] [CrossRef]

- Jiang, Y.; Wang, L.; Wang, Y.; Wang, S.; Guo, M. A High-Loop-Gain Low-Dropout Regulator with Adaptive Positive Feedback Compensation Handling 1-A Load Current. Electronics 2022, 11, 949. [Google Scholar] [CrossRef]

- Jiang, Y.; Wang, L.; Wang, S.; Cui, M.; Zheng, Z.; Li, Y. A Low-Power, Fast-Transient Output-Capacitorless LDO with Transient Enhancement Unit and Current Booster. Electronics 2022, 11, 701. [Google Scholar] [CrossRef]

- Liu, K.; Xie, Y.; Li, X.; Zhang, L. An Ultra-Low Power Fast Transient LDO with Dynamic Bias. Electronics 2022, 11, 3655. [Google Scholar] [CrossRef]

- Zawawi, R.B.A.; Choi, H.; Kim, J. High-PSRR Wide-Range Supply-Independent CMOS Voltage Reference for Retinal Prosthetic Systems. Electronics 2020, 9, 2028. [Google Scholar] [CrossRef]

- Oh, W.; Bakkaloglu, B. A CMOS Low-Dropout Regulator with Current-Mode Feedback Buffer Amplifier. IEEE Trans. Circuits Syst. II 2007, 54, 922–926. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhan, C.; Wang, L.; Law, M.-K. A −40~125 °C 0.4 μA Low Noise Bandgap Voltage Reference with 0.8 mA Load Driving Capability Using Shared Feedback Resistors. IEEE Trans. Circuits Syst. II 2022, 69, 4033–4037. [Google Scholar] [CrossRef]

- Man, T.Y.; Mok, P.K.T.; Chan, M. A High Slew-Rate Push & Pull Output Amplifier for Low-Quiescent Current Low-Dropout Regulators with Transient-Response Improvement. IEEE Trans. Circuits Syst. II 2007, 54, 755–759. [Google Scholar]

- Mandal, D.; Desai, C.; Bakkaloglu, B.; Kiaei, S. Adaptively Biased Output Cap-Less NMOS LDO With 19 Ns Settling Time. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 167–171. [Google Scholar] [CrossRef]

- Tang, J.; Lee, J.; Roh, J. Low-Power Fast-Transient Capacitor-Less LDO Regulator with High Slew-Rate Class-AB Amplifier. IEEE Trans. Circuits Syst. II 2019, 66, 462–466. [Google Scholar] [CrossRef]

- Wang, L.; Mao, W.; Wu, C.; Chang, A.; Lian, Y. A Fast Transient LDO Based on Dual Loop FVF with High PSRR. In Proceedings of the 2016 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Republic of Korea, 25–28 October 2016; pp. 99–102. [Google Scholar]

- Du, H.; Lai, X.; Chi, Y. A High Voltage LDO with Dynamic Compensation Network. Analog. Integr. Circ. Sig. Process 2014, 80, 233–241. [Google Scholar] [CrossRef]

- Yang, X.; Lu, T.; Zhang, J.; Zong, Y. A Low-Quiescent Current Low-Dropout Regulator with Wide Input Range. Int. J. Electron. Electr. Eng. 2014, 3, 182–186. [Google Scholar] [CrossRef]

- Al-Shyoukh, M.; Lee, H.; Perez, R. A Transient-Enhanced Low-Quiescent Current Low-Dropout Regulator With Buffer Impedance Attenuation. IEEE J. Solid State Circuits 2007, 42, 1732–1742. [Google Scholar] [CrossRef]

- Yin, J.; Huang, S.; Duan, Q.; Cheng, Y. An 800 MA Load Current LDO with Wide Input Voltage Range. In Proceedings of the 2017 International Conference on Circuits, Devices and Systems (ICCDS), Chengdu, China, 5–8 September 2017; pp. 174–178. [Google Scholar]

- Fathipour, R. High Slew Rate Current Mode Transconductance Error Amplifier for Low Quiescent Current Output-Capacitorless CMOS LDO Regulator. Integration 2014, 47, 204–212. [Google Scholar] [CrossRef]

- Garimella, A.; Rashid, M.W.; Furth, P.M. Reverse Nested Miller Compensation Using Current Buffers in a Three-Stage LDO. IEEE Trans. Circuits Syst. II 2010, 57, 250–254. [Google Scholar] [CrossRef]

- Liu, N.; Johnson, B.; Nadig, V.; Chen, D. A Transient-Enhanced Fully-Integrated LDO Regulator for SoC Application. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Abuishmais, I.; Shahroury, F.R.; Ahmad, H. A Design Methodology of High-Efficiency Dimmable Current Sink for Current-Regulated Drivers. Electronics 2022, 11, 2566. [Google Scholar] [CrossRef]

- Khan, D.; Basim, M.; ul Ain, Q.; Shah, S.A.A.; Shehzad, K.; Verma, D.; Lee, K.-Y. Design of a Power Regulated Circuit with Multiple LDOs for SoC Applications. Electronics 2022, 11, 2774. [Google Scholar] [CrossRef]

- Tong, X.; Wei, K. A Fully Integrated Fast-Response LDO Voltage Regulator with Adaptive Transient Current Distribution. In Proceedings of the 2017 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Bochum, Germany, 3–5 July 2017; pp. 651–654. [Google Scholar]

- Zhang, H.; Wan, P.; Geng, J.; Liu, Z.; Chen, Z. A Fast Transient Response Digital LDO with a TDC-Based Signal Converter. Electronics 2020, 9, 132. [Google Scholar] [CrossRef]

- Grajdeanu, A.-T.; Raducan, C.; Plesa, C.-S.; Neag, M.; Varzaru, L.; Topa, M.D. Fast LDO Handles a Wide Range of Load Currents and Load Capacitors, up to 100 MA and Over 1 μF. IEEE Access 2022, 10, 9124–9141. [Google Scholar] [CrossRef]

- Lim, C.-C.; Lai, N.-S.; Tan, G.-H.; Ramiah, H. A Low-Power Fast Transient Output Capacitor-Free Adaptively Biased LDO Based on Slew Rate Enhancement for SoC Applications. Microelectron. J. 2015, 46, 740–749. [Google Scholar] [CrossRef]

- Lavalle-Aviles, F.; Torres, J.; Sanchez-Sinencio, E. A High Power Supply Rejection and Fast Settling Time Capacitor-Less LDO. IEEE Trans. Power Electron. 2019, 34, 474–484. [Google Scholar] [CrossRef]

- Abugharbieh, K.; Yaseen, B.; Deeb, A. A Fully Integrated 1.2 V LDO Regulator. In Proceedings of the 2020 32nd International Conference on Microelectronics (ICM), Aqaba, Jordan, 14–17 December 2020; pp. 1–4. [Google Scholar]

- Yosef-Hay, Y.; Larsen, D.Ø.; Muntal, P.L.; Jørgensen, I.H.H. Fully Integrated, Low Drop-out Linear Voltage Regulator in 180 Nm CMOS. Analog. Integr. Circ. Sig. Process 2017, 92, 427–436. [Google Scholar] [CrossRef]

- Lu, Y.; Li, C.; Zhu, Y.; Huang, M.; U, S.-P.; Martins, R.P. A 312 Ps Response-time LDO with Enhanced Super Source Follower in 28 Nm CMOS. Electron. Lett. 2016, 52, 1368–1370. [Google Scholar] [CrossRef]

- Han, W.; Lee, H. A 340-NA-Quiescent 80-MA-Load 0.02-Fs-FOM Active-Capacitor-Based Low-Dropout Regulator in Standard 0.18-μm CMOS. IEEE Solid State Circuits Lett. 2021, 4, 125–128. [Google Scholar] [CrossRef]

- Han, W.; Luo, Z.; Chen, C.; Liu, J.; Lee, H. A 200 mA-Load 0.62fs-FOM Active-Capacitor-Assisted Dual-Loop Output Capacitorless Low-Dropout Regulator in Standard 65nm CMOS. In Proceedings of the 2022 IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–1 June 2022; pp. 1906–1909. [Google Scholar]

- Pérez-Bailón, J.; Calvo, B.; Medrano, N. A Fully-Integrated 180 Nm CMOS 1.2 V Low-Dropout Regulator for Low-Power Portable Applications. Electronics 2021, 10, 2108. [Google Scholar] [CrossRef]

- Lu, Y.; Chen, M.; Wang, K.; Yang, Y.; Wang, H. A Capacitorless Flipped Voltage Follower LDO with Fast Transient Using Dynamic Bias. Electronics 2022, 11, 3009. [Google Scholar] [CrossRef]

- Huang, S.; Duan, Q.; Guo, T.; Cheng, Y.; Yin, J.; Ding, Y.M. A 300-mA Load CMOS Low-Dropout Regulator without an External Capacitor for SoC and Embedded Applications: A 300-mA Regulator Without an External Capacitor. Int. J. Circ. Theor. Appl. 2017, 45, 2281–2289. [Google Scholar] [CrossRef]

- Guo, Z.; Li, H.; Li, D.; Fan, S.; Gui, X.; Xue, Z.; Chen, Z.; Geng, L. Topological Classification-Based Splitting–Combining Methodology for Analysis of Complex Multi-Loop Systems and Its Application in LDOs. IEEE Trans. Power Electron. 2019, 34, 7025–7039. [Google Scholar] [CrossRef]

- Ramırez-Angulo, J.; López-Martín, A.J.; Carvajal, R.G.; Torralba, A.; Jiménez, M. Simple Class-AB Voltage Follower with Slew Rate and Bandwidth Enhancement and No Extra Static Power or Supply Requirements. Electron. Lett. 2006, 42, 784. [Google Scholar] [CrossRef]

- Wangtaphan, S.; Kasemsuwan, V. A 0.6 Volt Class-AB CMOS Voltage Follower with Bulk-Driven Quasi-Floating Gate Super Source Follower. In Proceedings of the 2012 9th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology, Phetchaburi, Thailand, 16–18 May 2012; pp. 1–4. [Google Scholar]

- Sharma, P.; Sharma, K.; Jatana, H.S.; Sharma, R. A Low Power Biopotential Amplifier Based on Bulk Driven Quasi Floating Gate Technique. In Proceedings of the 2019 Devices for Integrated Circuit (DevIC), Kalyani, India, 23–24 March 2019; pp. 424–427. [Google Scholar]

- Aloui, I.; Hassen, N.; Nouet, P.; Besbes, K. Low-Voltage Low-Power Current-Mode Square-Root Circuit Based on Quasi-Floating Gate Technique. In Proceedings of the 2020 17th International Multi-Conference on Systems, Signals & Devices (SSD), Monastir, Tunisia, 20–23 July 2020; pp. 761–764. [Google Scholar]

- Martincorena-Arraiza, M.; De La Cruz-Blas, C.A.; Lopez-Martin, A.; Carlosena, A. Micropower Class AB Low-Pass Analog Filter Based on the Super-Source Follower. IEEE Trans. Circuits Syst. II 2022, 69, 3684–3688. [Google Scholar] [CrossRef]

| Parameter | [1] | [21] | [32] | [34] | This Work |

|---|---|---|---|---|---|

| Process (μm) | 0.5 | 0.13 | 0.18 | 0.5 | 0.18 |

| Area (mm2) | 0.279 | 1.634 | 0.109 | 0.4 | 0.085 |

| Supply Voltage (V) | 2.3–5.5 | 5.3 | 1.31–3.3 | 3.5–5.5 | 2–5 |

| Output Voltage (V) | 1.2–5.4 | 5 | 1.2 | 3.3 | 1.8 |

| Dropout Voltage (mV) | 100 | 300 | 110 | 200 | 200 |

| Maximum IL (mA) | 150 | 300 | 50 | 300 | 300 |

| IQ (μA) | >40 | 38 | 8.6 | 380 | 66.4 |

| ΔVOUT (mV) | 354 | 214 | 666 | 200 | 153 |

| ΔIOUT (mA) | 150 | 100 | 50 | 299 | 297 |

| Edge Time Δt (μs) | 1 | NA | 1 | 5 | 0.3 |

| Setting Time(μs) | 5 | NA | 3 | 8 | 0.4 |

| Load Regulation (μV/mA) | NA | 430 | 5.6 | 33.4 | 1.94 |

| Line Regulation (mV/V) | NA | 25 | 4.13 | 1.66 | 0.55 |

| PSR (dB) at 1 kHz | −50 | −51.9 | −36.3 | −65 | −60 |

| Minimum Required CTOT (pF) | 29 | 1000 | 50 | 10 | 5 |

| FOM (fs) | >18.251 | NA | 381.84 | 141.684 | 0.576 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gao, M.; Cai, X.; Gao, Y.; Xia, R.; Li, B. Fully Integrated 1.8 V Output 300 mA Load LDO with Fast Transient Response. Electronics 2023, 12, 1409. https://doi.org/10.3390/electronics12061409

Gao M, Cai X, Gao Y, Xia R, Li B. Fully Integrated 1.8 V Output 300 mA Load LDO with Fast Transient Response. Electronics. 2023; 12(6):1409. https://doi.org/10.3390/electronics12061409

Chicago/Turabian StyleGao, Mali, Xiaowu Cai, Yuexin Gao, Ruirui Xia, and Bo Li. 2023. "Fully Integrated 1.8 V Output 300 mA Load LDO with Fast Transient Response" Electronics 12, no. 6: 1409. https://doi.org/10.3390/electronics12061409

APA StyleGao, M., Cai, X., Gao, Y., Xia, R., & Li, B. (2023). Fully Integrated 1.8 V Output 300 mA Load LDO with Fast Transient Response. Electronics, 12(6), 1409. https://doi.org/10.3390/electronics12061409