Research on Five-Level PFC Circuit Topology Based on Switch-Diode-Capacitor Network

Abstract

1. Introduction

2. Topology Deduction and Operation Principle

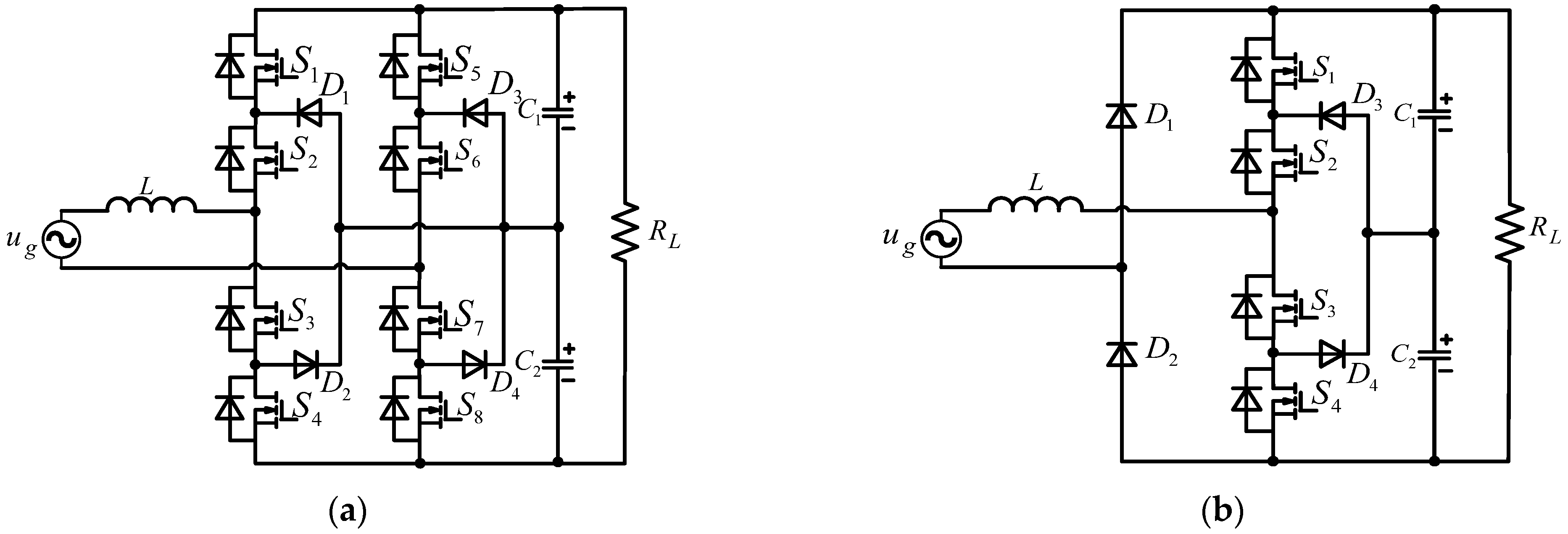

2.1. Deduction Process of Novel PFC Topologies

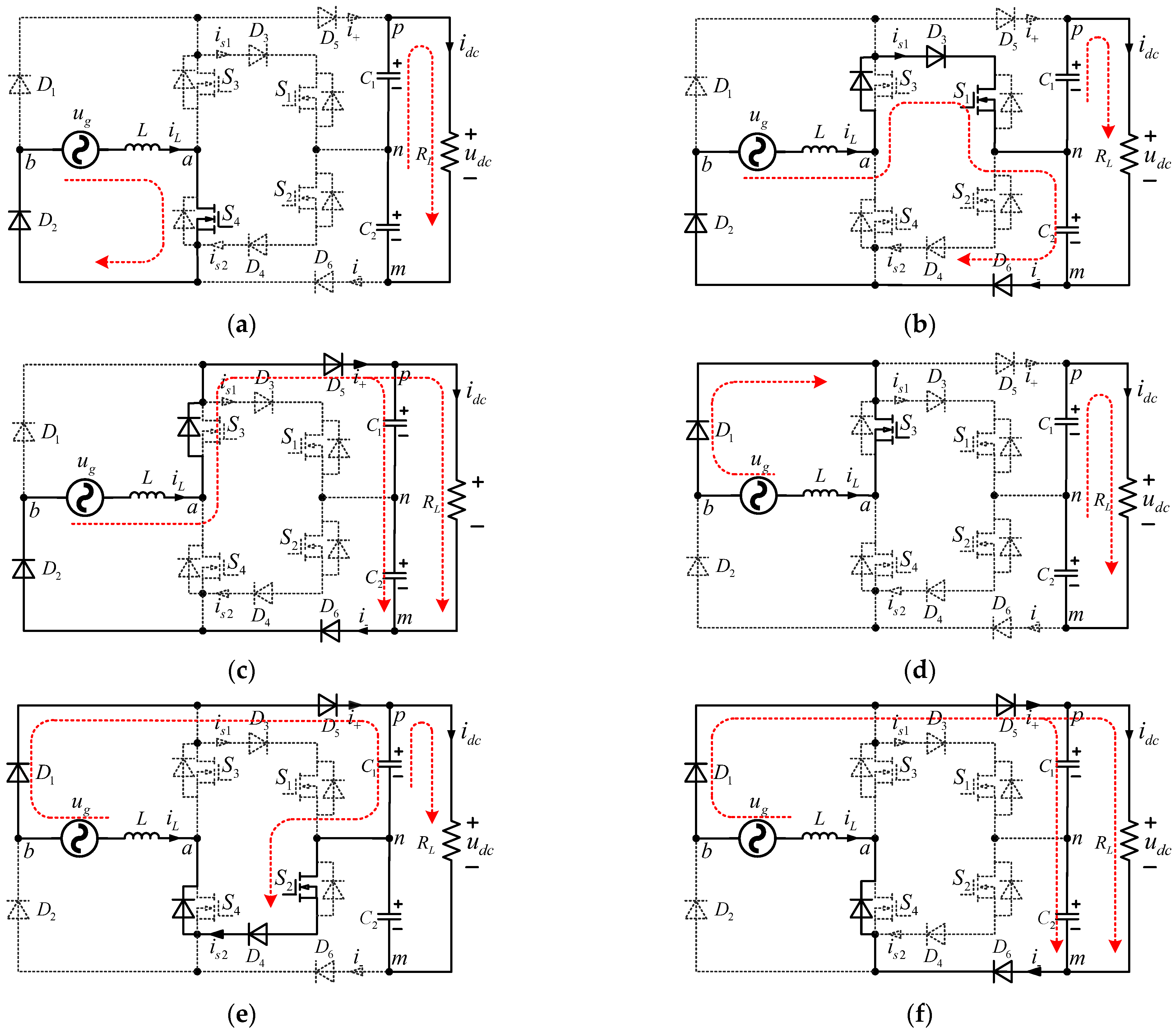

2.2. Operation Principle of Novel PFC Topologies

2.3. Equivalent Circuit Model

3. Performance Analysis of the Proposed Topologies

3.1. Analysis of Voltage Stresses of Switching Devices

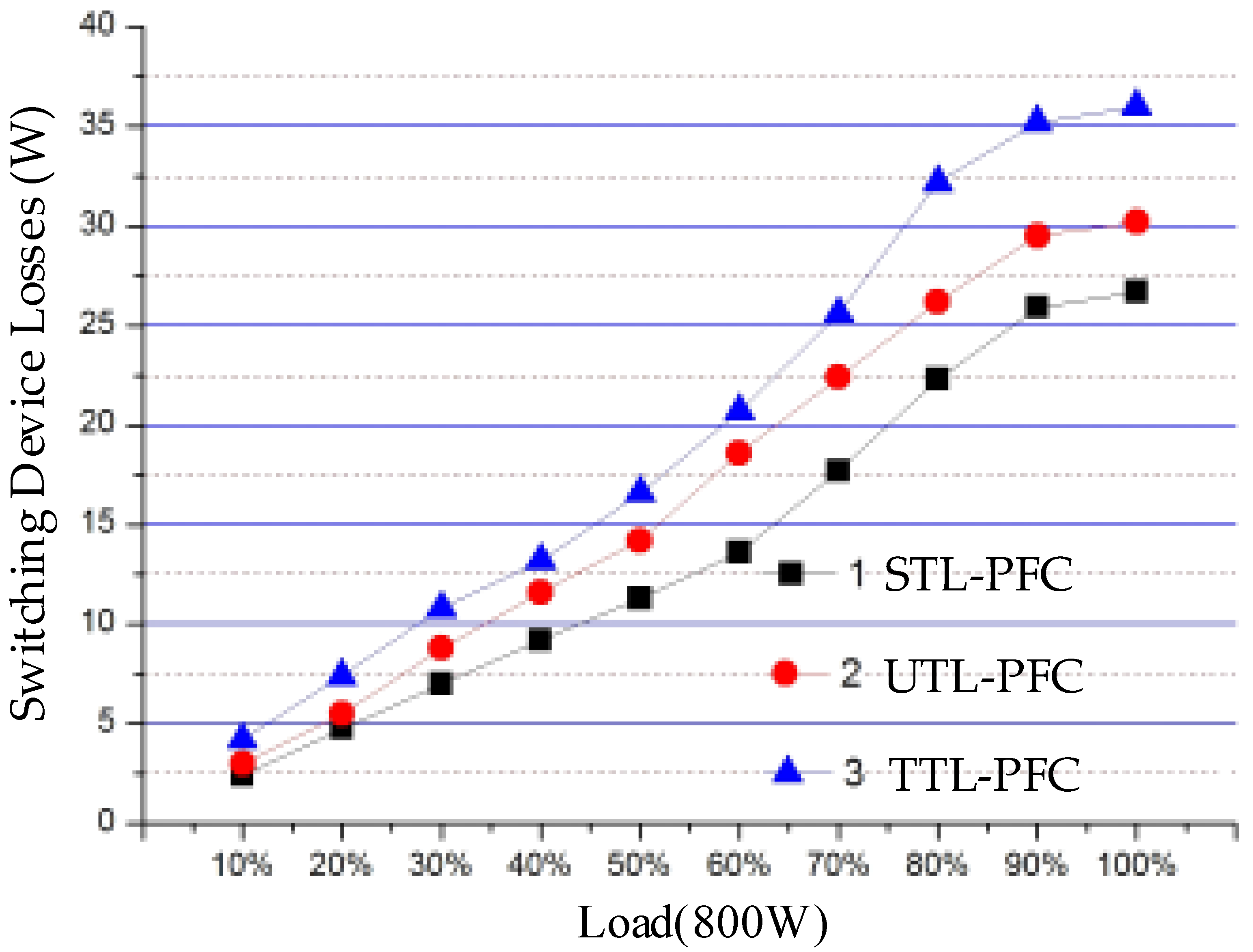

3.2. Calculation and Comparison of the Switching Device Losses

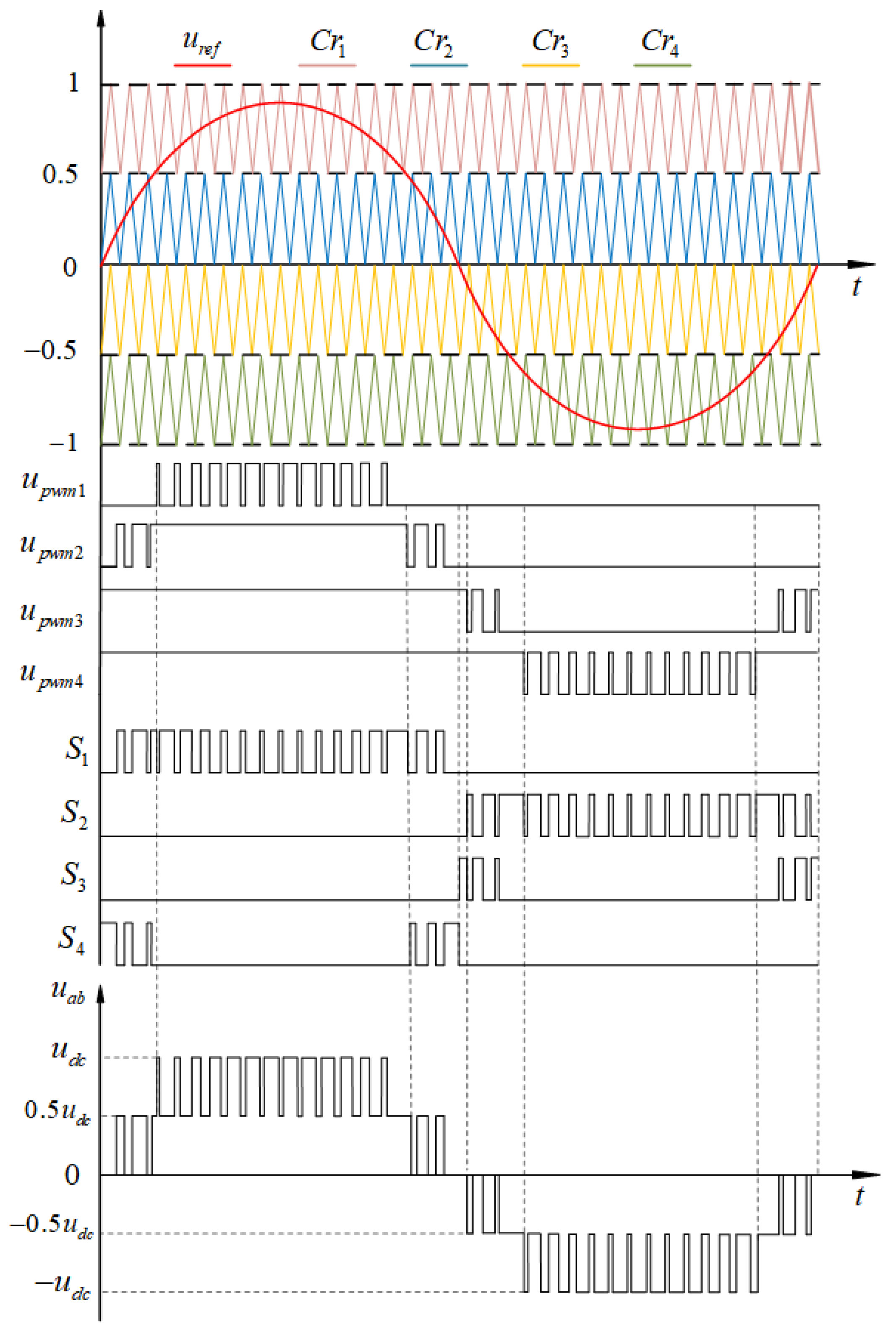

4. Multicarrier Modulation Technology Based on Capacitor Voltage Balancing

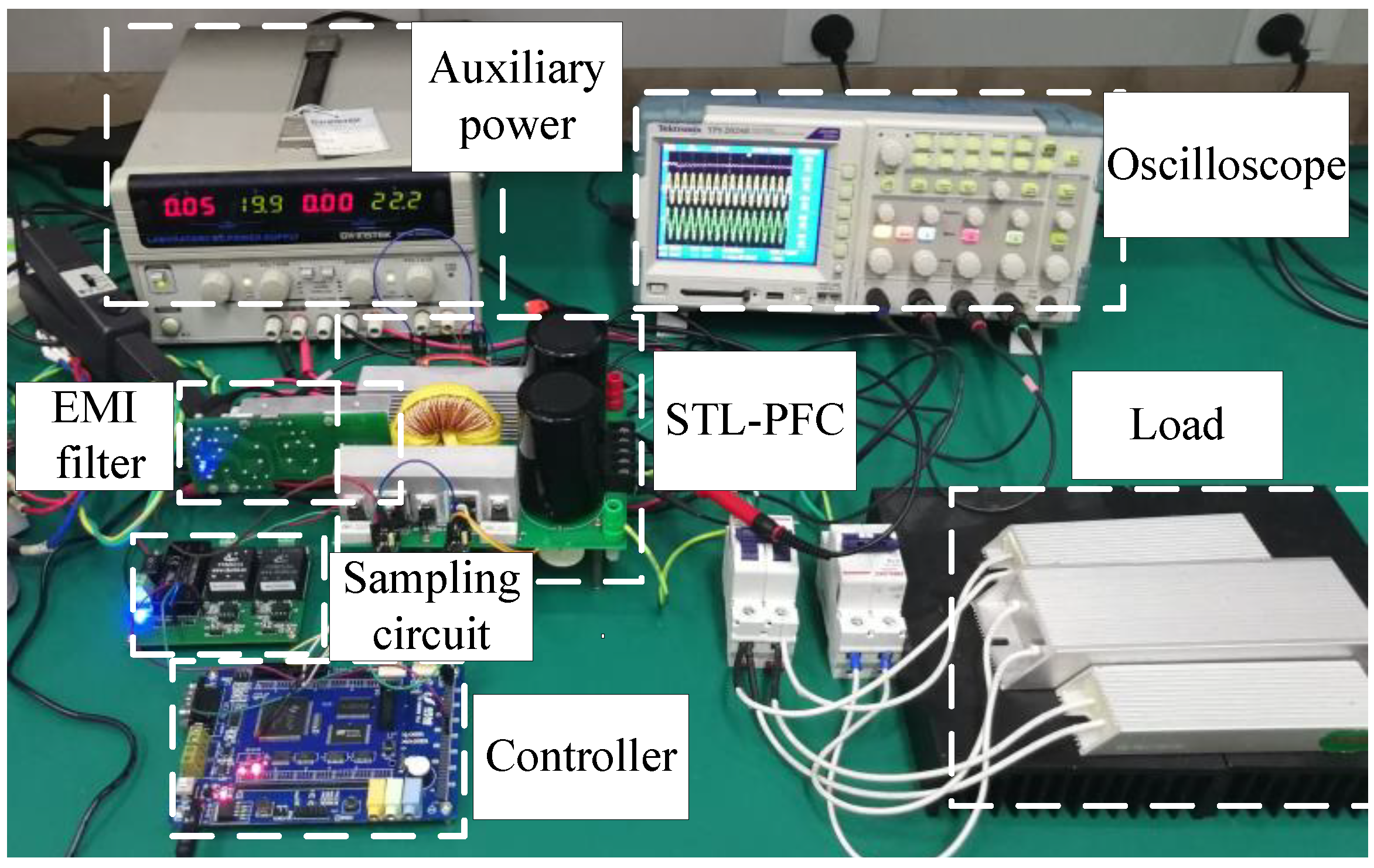

5. Experimental Validation

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Chang, C.-H.; Cheng, C.-A.; Chang, E.-C.; Cheng, H.-L.; Yang, B.-E. An Integrated High-Power-Factor Converter with ZVS Transition. IEEE Trans. Power Electron. 2016, 31, 2362–2371. [Google Scholar] [CrossRef]

- Singh, S.; Singh, B.; Bhuvaneswari, G.; Bist, V. Power Factor Corrected Zeta Converter Based Improved Power Quality Switched Mode Power Supply. IEEE Trans. Ind. Electron. 2015, 62, 5422–5433. [Google Scholar] [CrossRef]

- Amiri, P.; Eberle, W.; Gautam, D.; Botting, C. An Adaptive Method for DC Current Reduction in Totem Pole Power Factor Correction Converters. IEEE Trans. Power Electron. 2021, 36, 11900–11909. [Google Scholar] [CrossRef]

- Madishetti, S.; Singh, B.; Bhuvaneswari, G. Three-Level NPC-Inverter-Based SVM-VCIMD With Feedforward Active PFC Rectifier for Enhanced AC Mains Power Quality. IEEE Trans. Ind. Appl. 2016, 52, 1865–1873. [Google Scholar] [CrossRef]

- Jang, Y.; Jovanović, M.M.; Kumar, M.; Ruiz, J.M. Three-Level TAIPEI Rectifier—Analysis of Operation, Design Considerations, and Performance Evaluation. IEEE Trans. Power Electron. 2017, 32, 942–956. [Google Scholar] [CrossRef]

- Jain, A.; Gupta, K.K.; Jain, S.K.; Bhatnagar, P. A Bidirectional Five-Level Buck PFC Rectifier with Wide Output Range for EV Charging Application. IEEE Trans. Power Electron. 2022, 37, 13439–13455. [Google Scholar] [CrossRef]

- Lee, J.-S.; Lee, K.-B. Open-Circuit Fault-Tolerant Control for Outer Switches of Three-Level Rectifiers in Wind Turbine Systems. IEEE Trans. Power Electron. 2016, 31, 3806–3815. [Google Scholar] [CrossRef]

- de Souza Kohler, M.A.F.; Cortez, D.F. Single-Phase Five-Level Flying-Capacitor Rectifier Using Three Switches. IEEE Open J. Power Electron. 2020, 1, 383–392. [Google Scholar] [CrossRef]

- Ebrahimi, J.; Karshenas, H.; Bakhshai, A. A Five-Level Nested Diode-Clamped Converter for Medium-Voltage Applications. IEEE Trans. Power Electron. 2022, 69, 6471–6483. [Google Scholar] [CrossRef]

- Mukherjee, D.; Kastha, D. A Reduced Switch Hybrid Multilevel Unidirectional Rectifier. IEEE Trans. Power Electron. 2019, 34, 2070–2081. [Google Scholar] [CrossRef]

- Kim, J.-S.; Lee, S.-H.; Cha, W.-J.; Kwon, B.-H. High-Efficiency Bridgeless Three-Level Power Factor Correction Rectifier. IEEE Trans. Ind. Electron. 2017, 64, 1130–1136. [Google Scholar] [CrossRef]

- Vahedi, H.; Shojaei, A.A.; Chandra, A.; Al-Haddad, K. Five-Level Reduced-Switch-Count Boost PFC Rectifier with Multicarrier PWM. IEEE Trans. Ind. Appl. 2016, 52, 4201–4207. [Google Scholar] [CrossRef]

- Monteiro, V.; Pinto, J.G.; Meléndez, A.A.N.; Afonso, J.L. A novel single-phase five-level active rectifier for on-board EV battery chargers. In Proceedings of the 2017 IEEE 26th International Symposium on Industrial Electronics (ISIE), Edinburgh, UK, 19–21 June 2017; pp. 582–587. [Google Scholar] [CrossRef]

- Rashidi, N.; Wang, Q.; Burgos, R.; Roy, C.; Boroyevich, D. Multi-objective Design and Optimization of Power Electronics Converters with Uncertainty Quantification—Part I: Parametric Uncertainty. IEEE Trans. Power Electron. 2021, 36, 1463–1474. [Google Scholar] [CrossRef]

- Zhang, X.; Tan, G.; Liu, Z.; Wang, Q.; Zhang, W.; Xia, T. Finite Control Set Model Predictive Direct Power Control of Single-Phase Three-Level PWM Rectifier Based on Satisfactory Optimization. IEEE Access 2021, 9, 11479–11491. [Google Scholar] [CrossRef]

- Mehrabadi, N.R.; Wang, Q.; Burgos, R.; Boroyevich, D. Multi-objective design and optimization of a Vienna rectifier with parametric uncertainty quantification. In Proceedings of the 2017 IEEE 18th Workshop on Control and Modeling for Power Electronics (COMPEL), Stanford, CA, USA, 9–12 July 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Zhang, X.; Tan, G.; Xia, T.; Wang, Q.; Wu, X. Optimized Switching Finite Control Set Model Predictive Control of NPC Single-Phase Three-Level Rectifiers. IEEE Trans. Power Electron. 2020, 35, 10097–10108. [Google Scholar] [CrossRef]

- Qi, W.; Li, S.; Yuan, H.; Tan, S.C.; Hui, S.Y. High-Power-Density Single-Phase Three-Level Flying-Capacitor Buck PFC Rectifier. IEEE Trans. Power Electron. 2019, 34, 10833–10844. [Google Scholar] [CrossRef]

- Lee, M.; Lai, J.S. Fixed-Frequency Hybrid Conduction Mode Control for Three-Level Boost PFC Converter. IEEE Trans. Power Electron. 2021, 36, 8334–8346. [Google Scholar] [CrossRef]

- Lee, M.; Kim, J.W.; Lai, J.S. Digital-Based Critical Conduction Mode Control for Three-Level Boost PFC Converter. IEEE Trans. Power Electron. 2020, 35, 7689–7701. [Google Scholar] [CrossRef]

- Najjar, M.; Kouchaki, A.; Nielsen, J.; Lazar, R.D.; Nymand, M. Design Procedure and Efficiency Analysis of a 99.3% Efficient 10 kW Three-Phase Three-Level Hybrid GaN/Si Active Neutral Point Clamped Converter. IEEE Trans. Power Electron. 2022, 37, 6698–6710. [Google Scholar] [CrossRef]

- Zhang, L.; Sun, K.; Xing, Y.; Zhao, J. A Family of Five-Level Dual-Buck Full-Bridge Inverters for Grid-Tied Applications. IEEE Trans. Power Electron. 2016, 31, 7029–7042. [Google Scholar] [CrossRef]

- Iqbal, A.; Meraj, M.; Tariq, M.; Lodi, K.A.; Maswood, A.I.; Rahman, S. Experimental Investigation and Comparative Evaluation of Standard Level Shifted Multi-Carrier Modulation Schemes with a Constraint GA Based SHE Techniques for a Seven-Level PUC Inverter. IEEE Access 2019, 7, 100605–100617. [Google Scholar] [CrossRef]

- He, X.; Yu, H.; Han, P.; Zhao, Z.; Peng, X.; Shu, Z.; Koh, L.; Wang, P. Fixed and Smooth-Switch-Sequence Modulation for Voltage Balancing Based on Single-Phase Three-Level Neutral-Point-Clamped Cascaded Rectifier. IEEE Trans. Ind. Electron. 2020, 56, 3889–3903. [Google Scholar] [CrossRef]

- Zhang, P.; Wu, X.; Chen, Z.; Xu, W.; Liu, J.; Qi, J. A Multizero-Sequence Component Injection Algorithm for a Five-Level Flying Capacitor Rectifier Under Unbalanced DC-Link Voltages. IEEE Trans. Power Electron. 2021, 36, 11967–11983. [Google Scholar] [CrossRef]

- de Freitas, I.S.; Bandeira, M.M.; de Macedo Barros, L.; Jacobina, C.B.; dos Santos, E.C.; Salvadori, F.; da Silva, S.A. A Carrier-Based PWM Technique for Capacitor Voltage Balancing of Single-Phase Three-Level Neutral-Point-Clamped Converters. IEEE Trans. Ind. Appl. 2015, 51, 3227–3235. [Google Scholar] [CrossRef]

- Dargahi, V.; Sadigh, A.K.; Khorasani, R.R.; Rodriguez, J. Active Voltage Balancing Control of a Seven-Level Hybrid Multilevel Converter Topology. IEEE Trans. Ind. Electron. 2022, 69, 74–89. [Google Scholar] [CrossRef]

| Modes | Switching States | System Parameters | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | ||||

| 2 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||

| 3 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||

| 4 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||||

| 5 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | |||||||

| 6 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||

| Switching Devices | STL-PFC | UATL-PFC | LATL-PFC |

|---|---|---|---|

| S1 | 0.5udc | 0.5udc | 0.5udc |

| S2 | 0.5udc | 0.5udc | 0.5udc |

| S3 | udc | udc | udc |

| S4 | udc | udc | udc |

| D1, D2 | udc | udc | udc |

| D3, D4 | 0.5udc | 0.5udc | 0.5udc |

| D5, D6 | udc | udc | udc |

| Operating Modes | Devices(Number × Rated Voltage) | Voltage | ||

|---|---|---|---|---|

| STL-PFC | UATL-PFC | LATC-PFC | ||

| Mode 1 | 1 × D6,1 × M6 | 1 × D6,1 × M6 | 1 × D6,1 × M6 | +0 |

| Mode 2 | 1 × D4,3 × D6,1 × M4 | 1 × D4,3 × D6,1 × M4 | 1 × D4,2 × D6,1 × M4 | +0.5udc |

| Mode 3 | 4 × D6 | 4 × D6 | 4 × D6 | +udc |

| Mode 4 | 1 × D6,1 × M6 | 1 × D6,1 × M6 | 1 × D6,1 × M6 | 0 |

| Mode 5 | 1 × D4,3 × D6,1 × M4 | 1 × D4,2 × D6,1 × M4 | 1 × D4,3 × D6,1 × M4 | −0.5udc |

| Mode 6 | 4 × D6 | 4 × D6 | 4 × D6 | −udc |

| Description | Label | Value |

|---|---|---|

| Input voltage | uAC | 220 Vrms |

| Output rated voltage | udc | 400 V |

| Rated output power | Po | 800 W |

| Switching frequency | f | 50 kHz |

| Inductor | L | 2 mH |

| Capacitor | C1/C2 | 1000 μF |

| MOSFETs | S1~S4 | STW26NM60N |

| Diodes | D1~D6 | RHPR3060 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lu, Y.; Ma, H.; Wei, Y.; Pan, Y.; Chen, X.; Huang, Y. Research on Five-Level PFC Circuit Topology Based on Switch-Diode-Capacitor Network. Electronics 2023, 12, 1286. https://doi.org/10.3390/electronics12061286

Lu Y, Ma H, Wei Y, Pan Y, Chen X, Huang Y. Research on Five-Level PFC Circuit Topology Based on Switch-Diode-Capacitor Network. Electronics. 2023; 12(6):1286. https://doi.org/10.3390/electronics12061286

Chicago/Turabian StyleLu, Yun, Hui Ma, Yewen Wei, Yu Pan, Xi Chen, and Yuehua Huang. 2023. "Research on Five-Level PFC Circuit Topology Based on Switch-Diode-Capacitor Network" Electronics 12, no. 6: 1286. https://doi.org/10.3390/electronics12061286

APA StyleLu, Y., Ma, H., Wei, Y., Pan, Y., Chen, X., & Huang, Y. (2023). Research on Five-Level PFC Circuit Topology Based on Switch-Diode-Capacitor Network. Electronics, 12(6), 1286. https://doi.org/10.3390/electronics12061286