Ka-Band Three-Stack CMOS Power Amplifier with Split Layout of External Gate Capacitor for 5G Applications

Abstract

1. Introduction

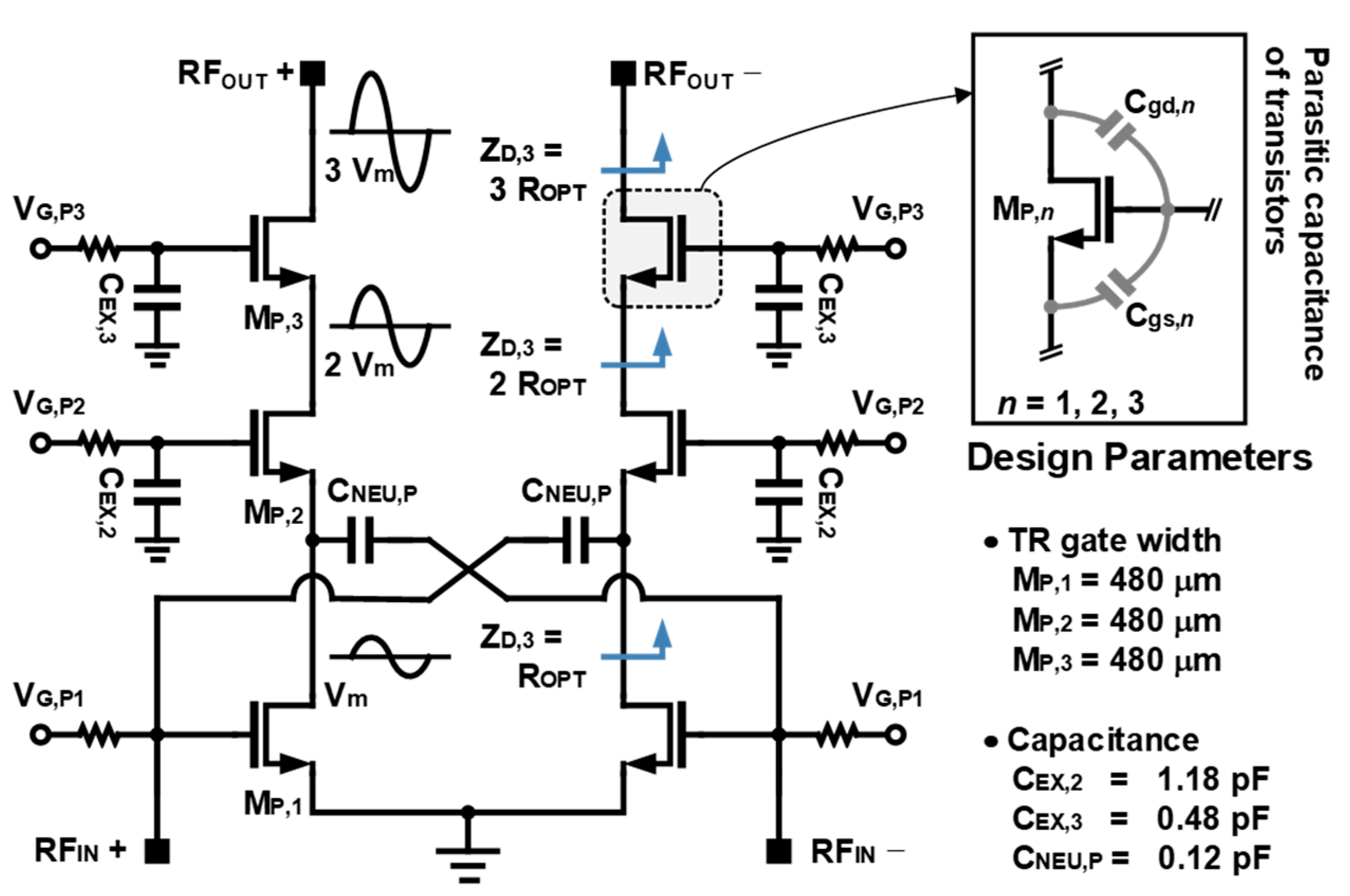

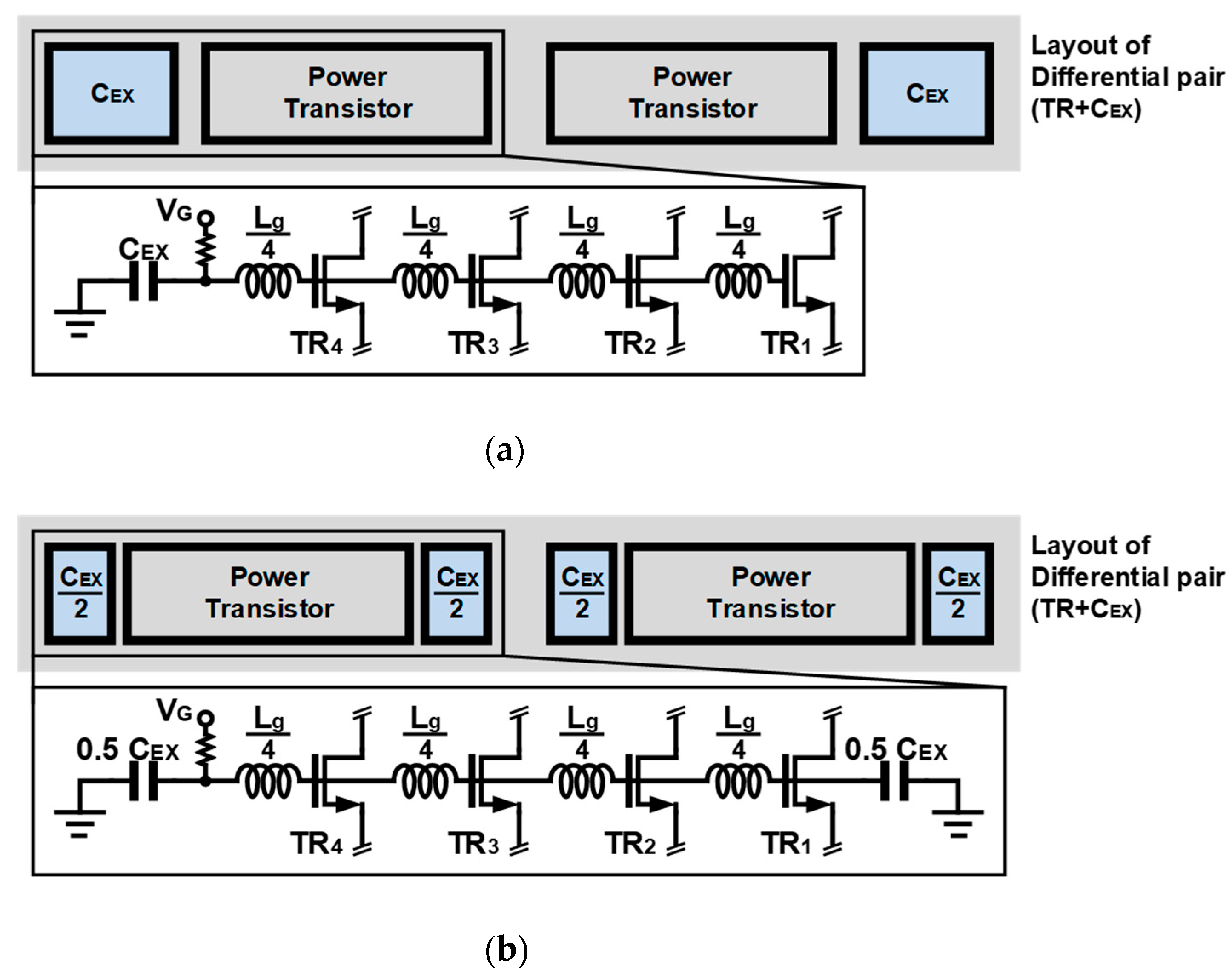

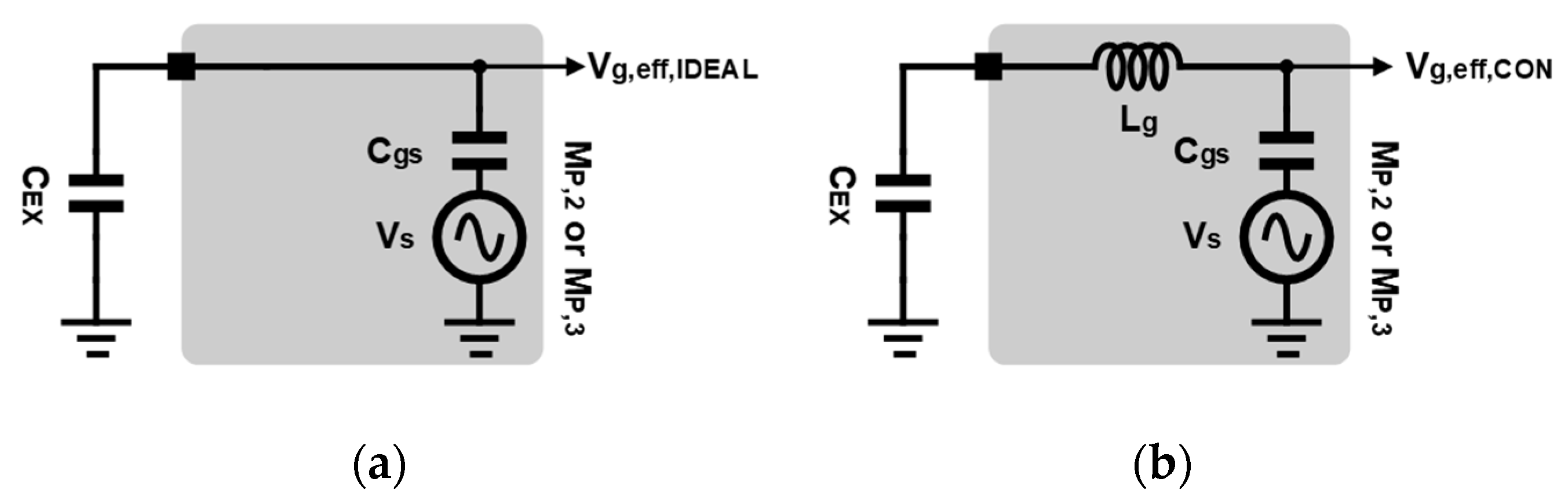

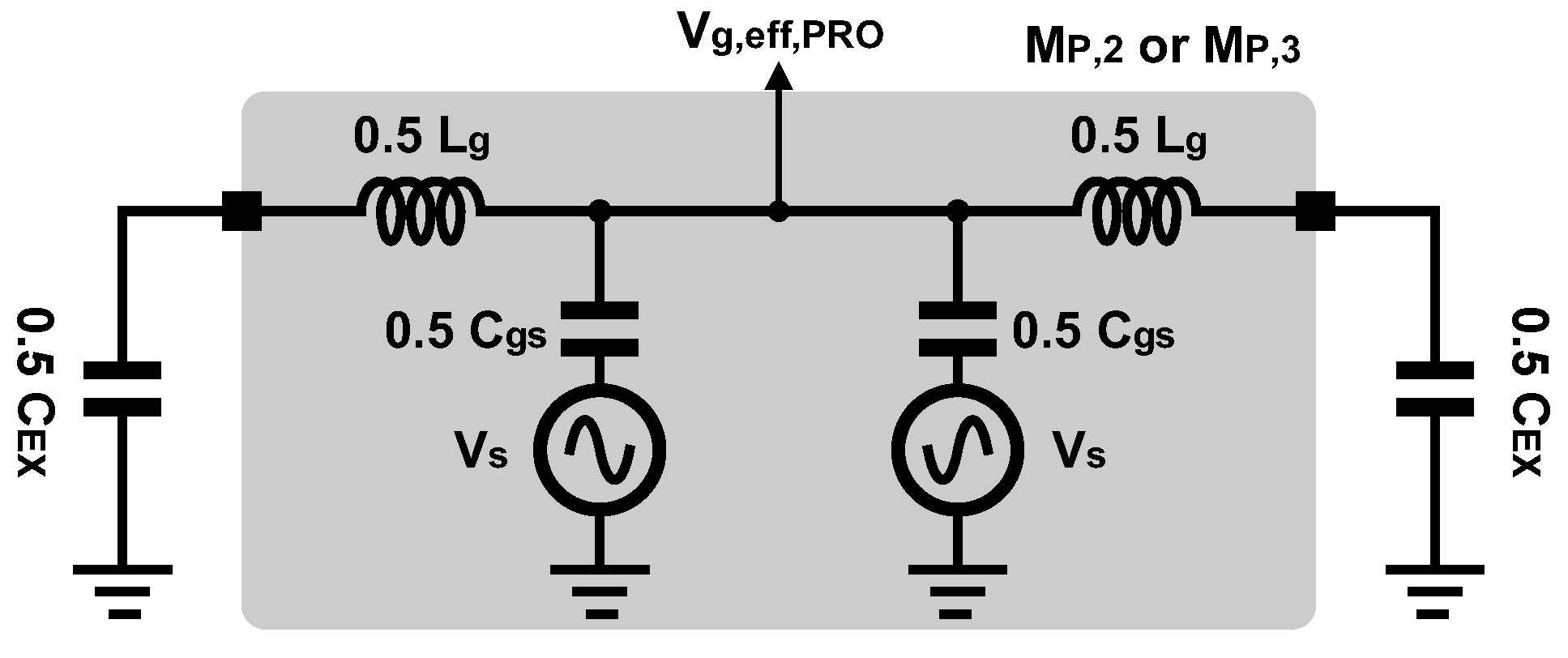

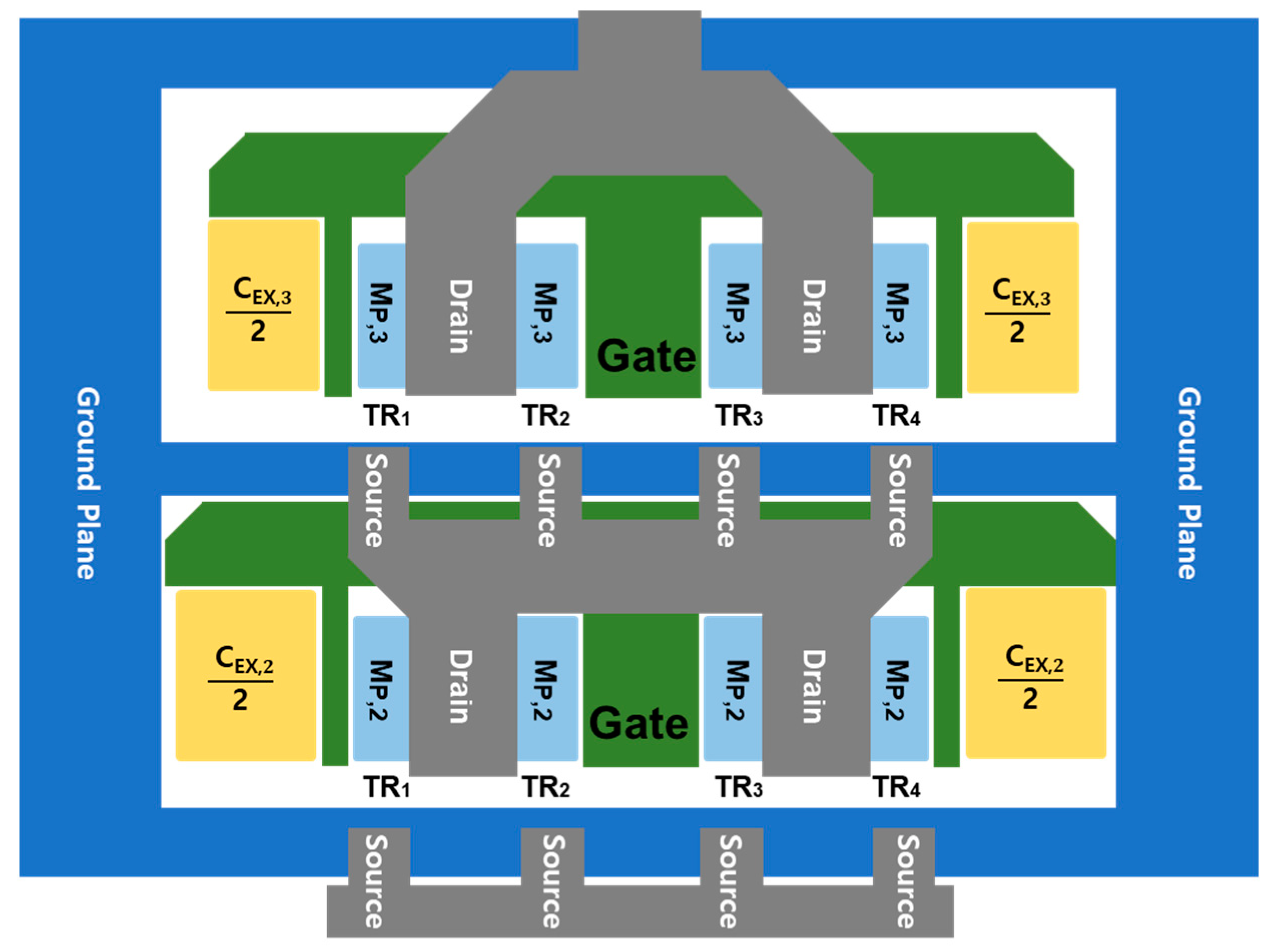

2. Design of External Gate and Neutralization Capacitors

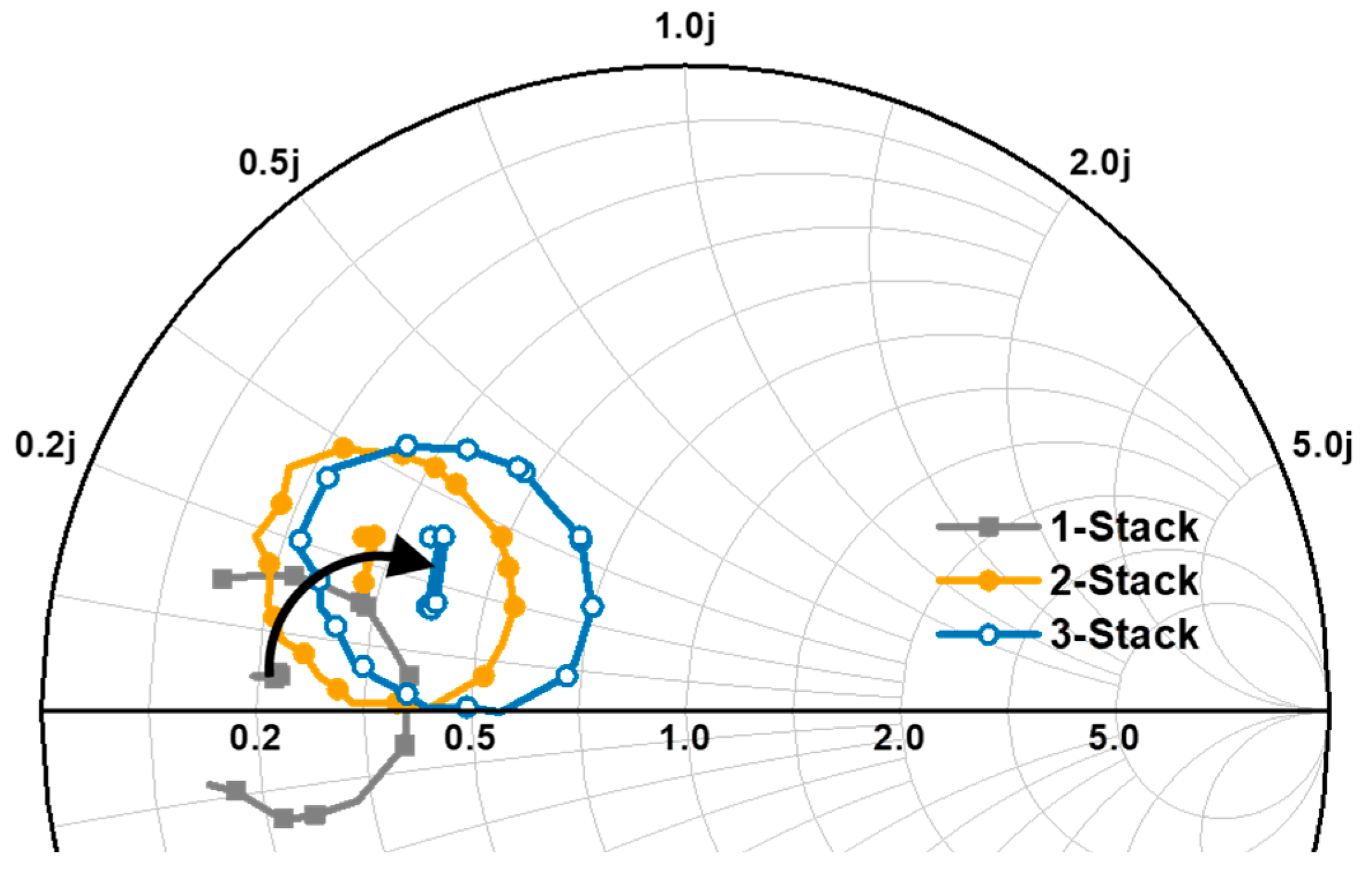

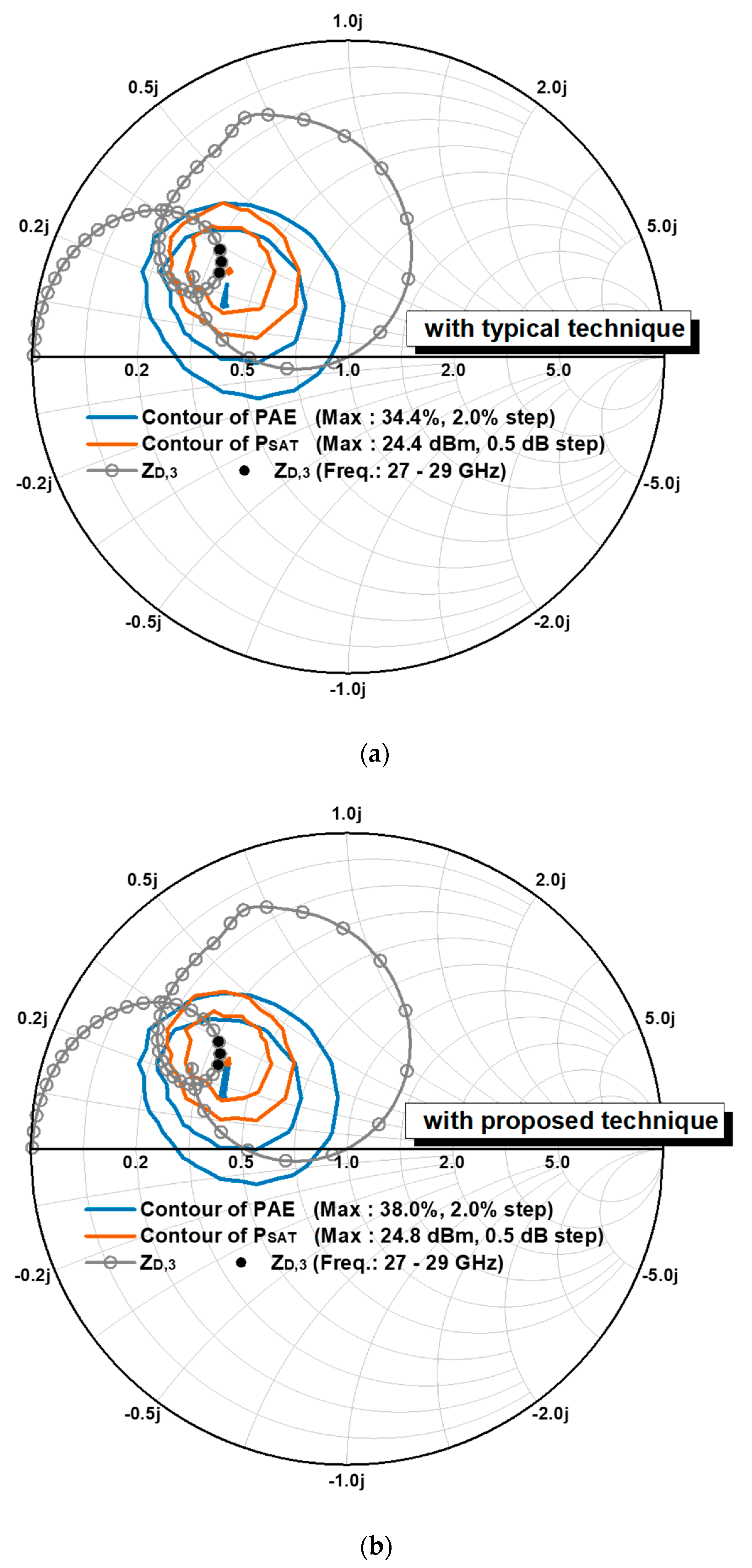

2.1. Determination of External Gate Capacitor Values

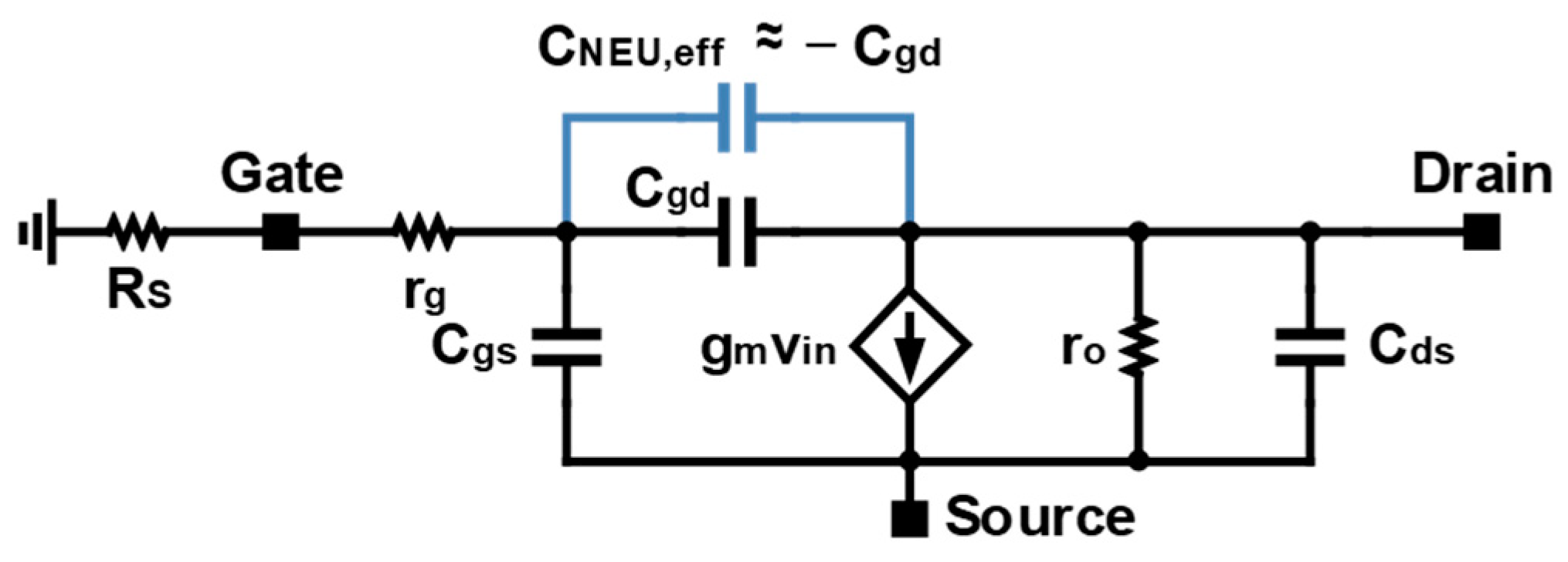

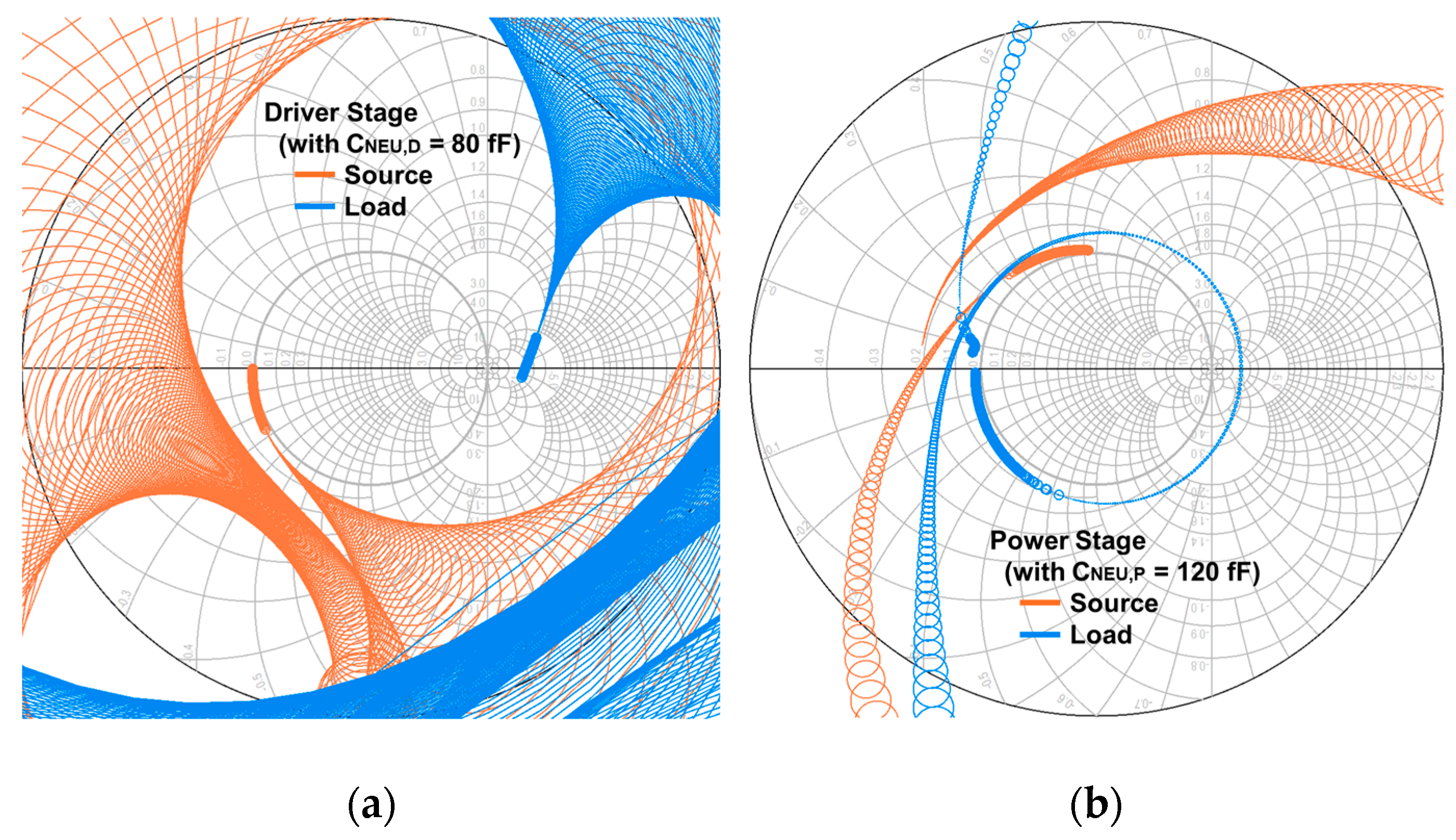

2.2. Determination of Neutralization Capacitor Values

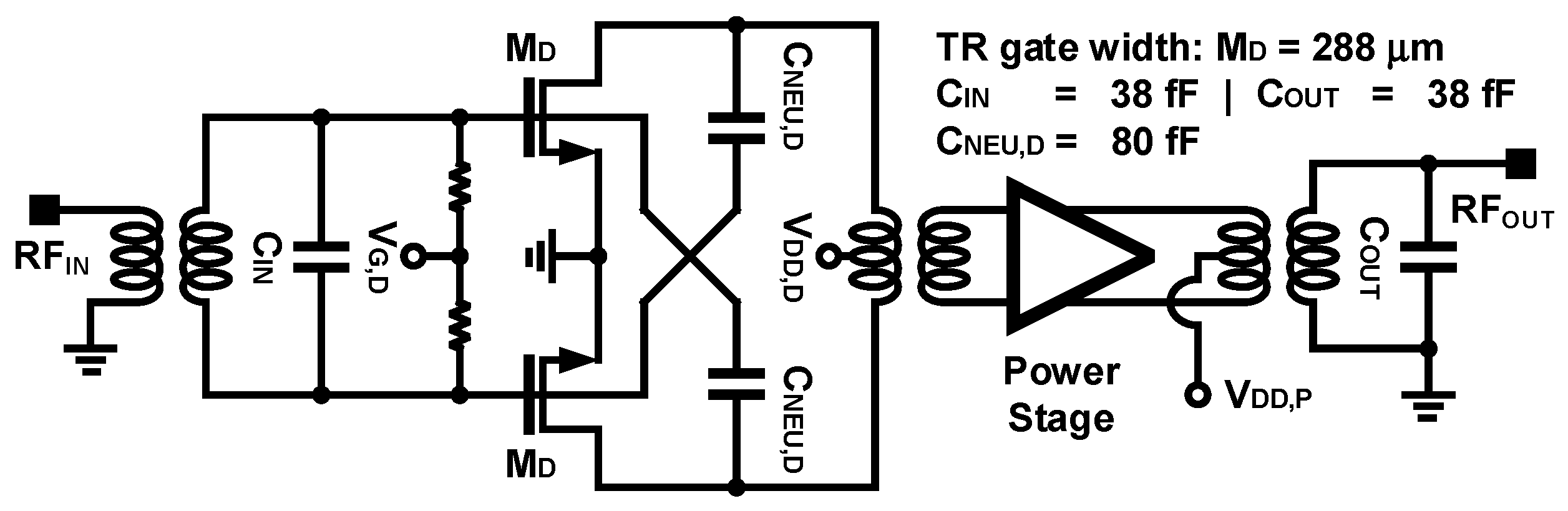

2.3. Design of Driver Stage

3. Design of Proposed Three-Stacked Power Amplifier with Split External Gate Capacitor

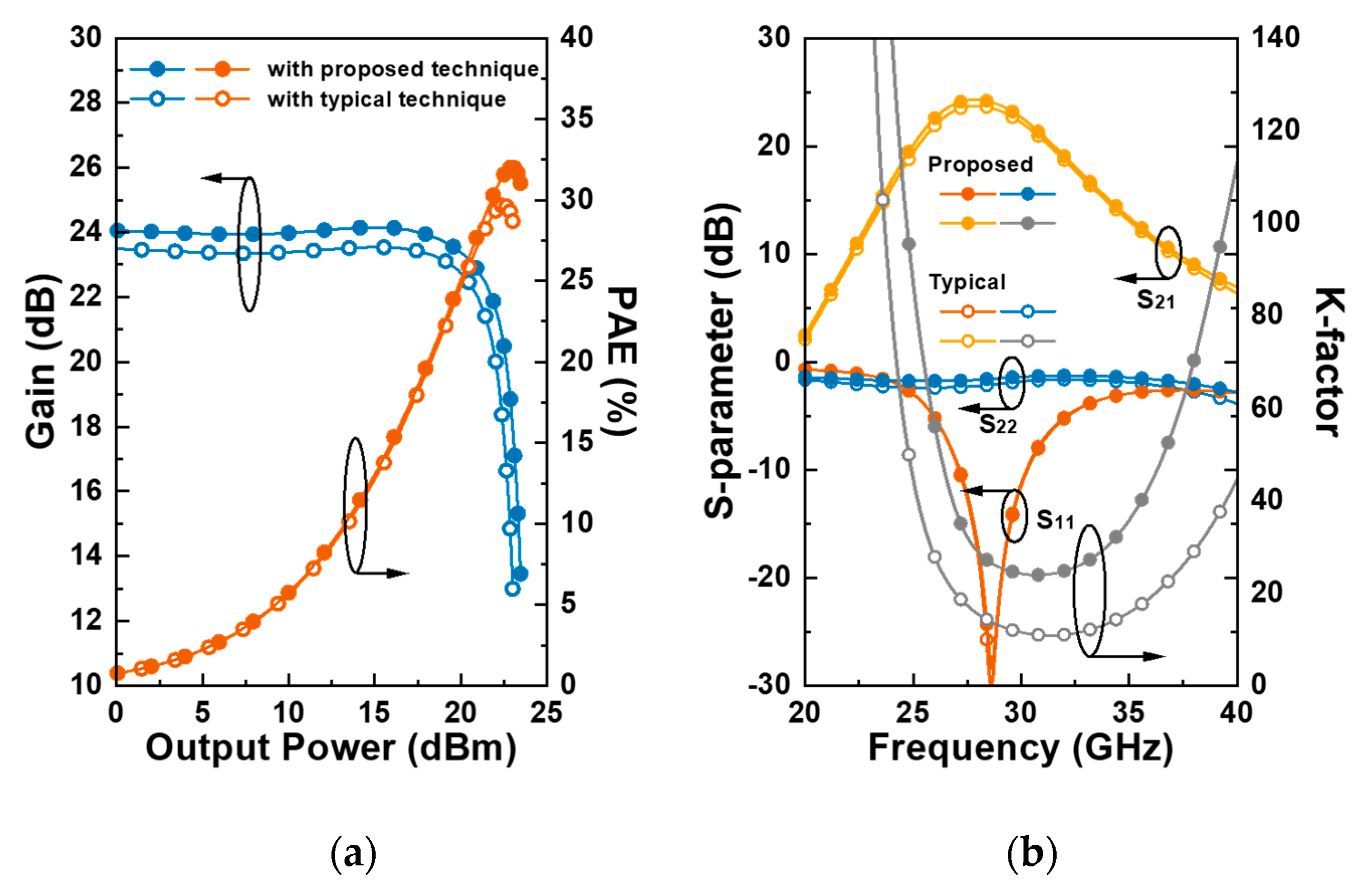

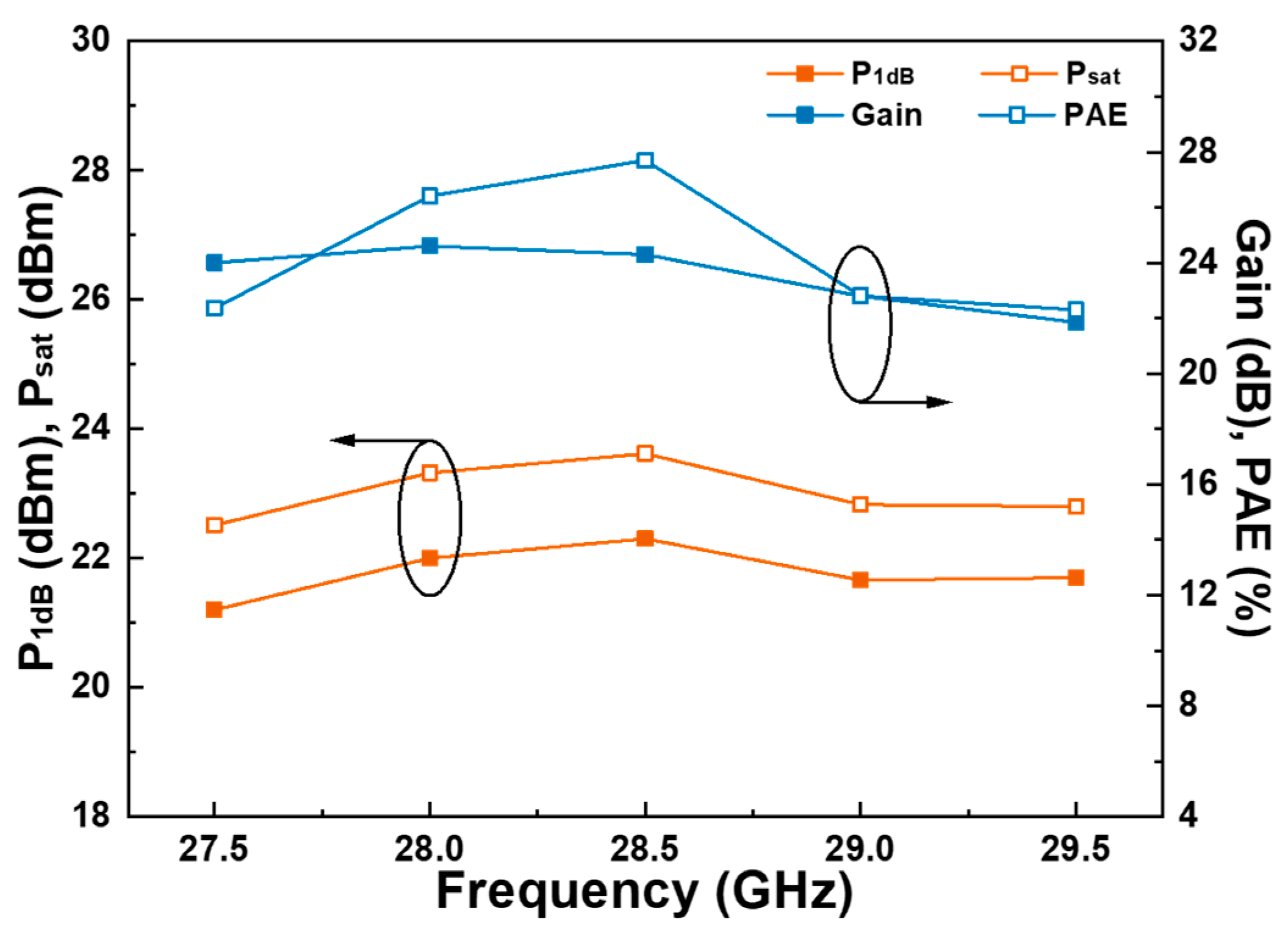

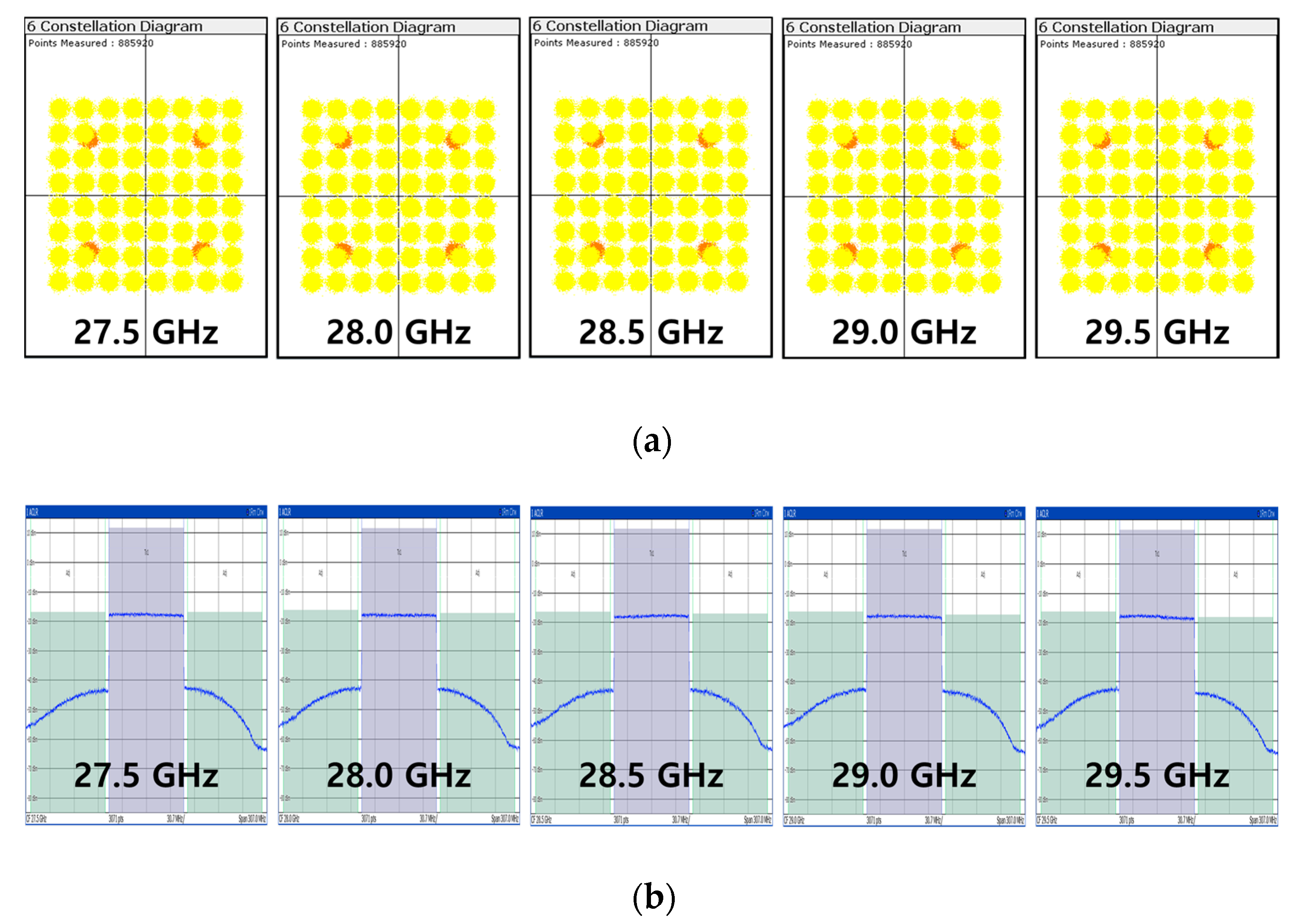

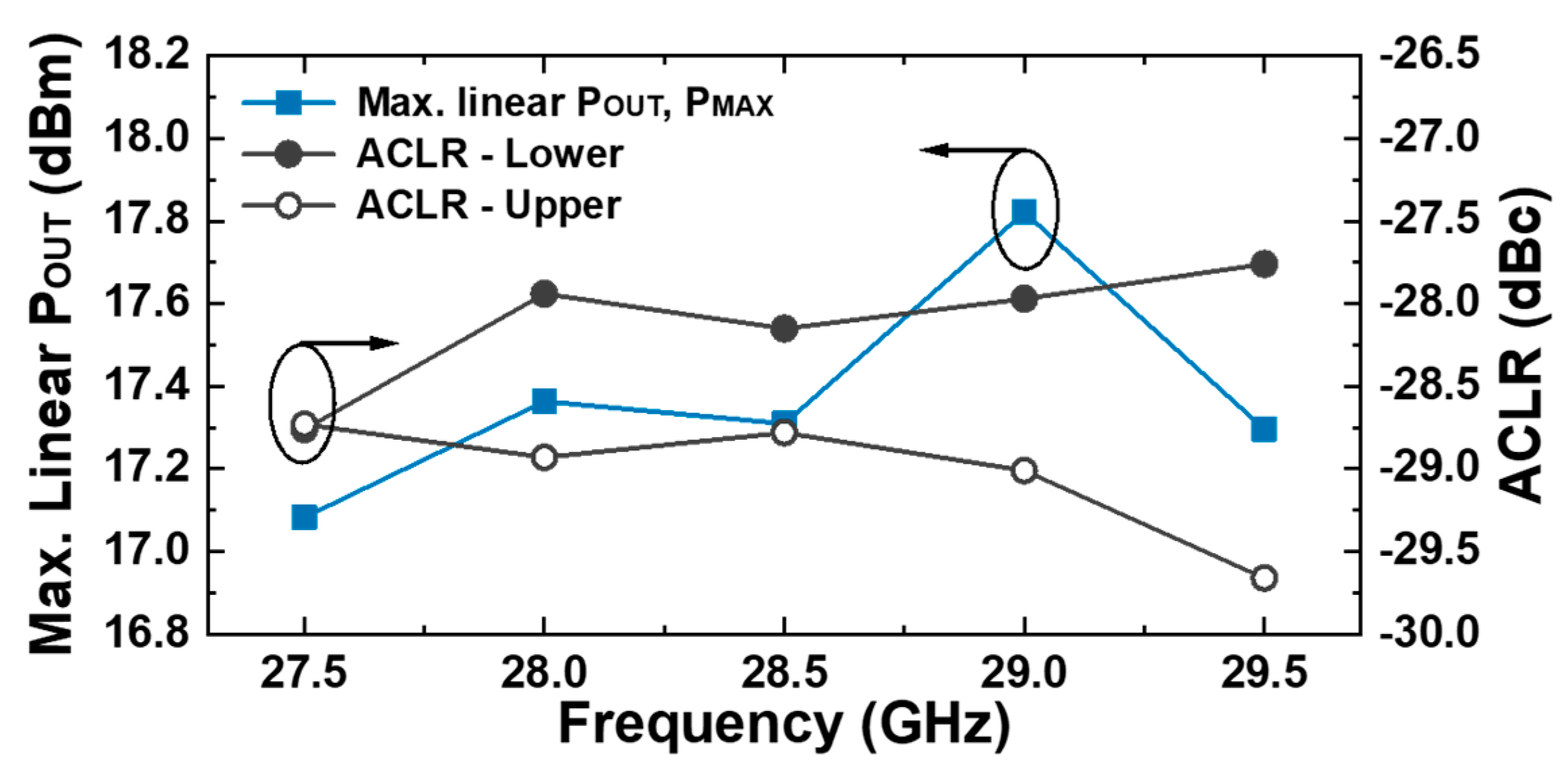

4. Results and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Xiong, Y.; Zeng, X.; Li, J. A Frequency-Reconfigurable CMOS Active Phase Shifter for 5G mm-Wave Applications. IEEE Trans. Circuits Syst. II Express Briefs 2019, 67, 1824–1828. [Google Scholar] [CrossRef]

- Cho, G.; Hong, S. Ka-band CMOS Power Amplifier Based on Transmission Line Transformers with Single-Ended Doherty Network. IEEE Microw. Wirel. Components Lett. 2021, 31, 1. [Google Scholar] [CrossRef]

- Mayeda, J.C.; Lie, D.Y.C.; Lopez, J. A Highly Efficient 18–40 GHz Linear Power Amplifier in 40-nm GaN for mm-Wave 5G. IEEE Microw. Wirel. Components Lett. 2021, 31, 1008–1011. [Google Scholar] [CrossRef]

- Liu, R.-J.; Zhu, X.W.; Xia, J.; Zhao, Z.M.; Dong, Q.; Chen, P.; Zhang, L.; Jiang, X.; Yu, C.; Hong, W.; et al. A 24–28-GHz GaN MMIC Synchronous Doherty Power Amplifier with Enhanced Load Modulation for 5G mm-Wave Applications. IEEE Trans. Microw. Theory Tech. 2022, 70, 3910–3922. [Google Scholar] [CrossRef]

- Kim, T.; Im, H.; Lee, S.-H.; Kim, K.-J.; Park, C. Highly Linear K-/Ka-Band SPDT Switch Based on Traveling-Wave Concept in a 150-nm GaN pHEMT Process. IEEE Microw. Wireless Compon. Lett. 2022, 32, 987–990. [Google Scholar] [CrossRef]

- Qunaj, V.; Reynaert, P. A Ka-Band Doherty-Like LMBA for High-Speed Wireless Communication in 28-nm CMOS. IEEE J. Solid-state Circuits 2021, 56, 3694–3703. [Google Scholar] [CrossRef]

- Yu, C.; Feng, J.; Zhao, D. A 28-GHz Doherty Power Amplifier With a Compact Transformer-Based Quadrature Hybrid in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 2790–2794. [Google Scholar] [CrossRef]

- Zong, Z.; Tang, X.; Khalaf, K.; Yan, D.; Mangraviti, G.; Nguyen, J.; Liu, Y.; Wambacq, P. A 28-GHz SOI-CMOS Doherty Power Amplifier With a Compact Transformer-Based Output Combiner. IEEE Trans. Microw. Theory Tech. 2021, 69, 2795–2808. [Google Scholar] [CrossRef]

- Park, J.; Kang, S.; Hong, S. Design of a Ka-Band Cascode Power Amplifier Linearized With Cold-FET Interstage Matching Network. IEEE Trans. Microw. Theory Tech. 2020, 69, 1429–1438. [Google Scholar] [CrossRef]

- Fan, T.-H.; Wang, Y.; Wang, H. A Broadband Transformer-Based Power Amplifier Achieving 24.5-dBm Output Power Over 24–41 GHz in 65-nm CMOS Process. IEEE Microw. Wirel. Components Lett. 2020, 31, 308–311. [Google Scholar] [CrossRef]

- Aoki, I.; Kee, S.; Rutledge, D.; Hajimiri, A. Distributed active transformer-a new power-combining and impedance-transformation technique. IEEE Trans. Microw. Theory Tech. 2002, 50, 316–331. [Google Scholar] [CrossRef]

- Park, C.; Kim, Y.; Kim, H.; Hong, S. A 1.9-GHz CMOS Power Amplifier Using Three-Port Asymmetric Transmission Line Transformer for a Polar Transmitter. IEEE Trans. Microw. Theory Tech. 2007, 55, 230–238. [Google Scholar] [CrossRef]

- Wang, J.; Zhu, W.; Wang, R.; Wang, Y. A Dual-Mode W-Band Eight-Way Parallel–Series Power-Combining PA with +18-dBm Psat and 15.1% PAE in 65-nm CMOS Technology. IEEE Microw. Wireless Compon. Lett. 2022, 32, 149–152. [Google Scholar] [CrossRef]

- Zhang, L.; Ma, K.; Fu, H. A 60-GHz 32-Way Hybrid Power Combination Power Amplifier in 55-nm Bulk CMOS. IEEE Trans. Microw. Theory Tech. 2022, 2022, 1–15. [Google Scholar] [CrossRef]

- Dabag, H.-T.; Hanafi, B.; Golcuk, F.; Agah, A.; Buckwalter, J.F.; Asbeck, P.M. Analysis and Design of Stacked-FET Millimeter-Wave Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2013, 61, 1543–1556. [Google Scholar] [CrossRef]

- Wu, C.-W.; Lin, Y.-H.; Hsiao, Y.-H.; Chou, C.-F.; Wu, Y.-C.; Wang, H. Design of a 60-GHz High-Output Power Stacked- FET Power Amplifier Using Transformer-Based Voltage-Type Power Combining in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2018, 66, 4595–4607. [Google Scholar] [CrossRef]

- Jeong, H.; Lee, H.D.; Park, B.; Jang, S.; Kong, S.; Park, C. Three-Stacked CMOS Power Amplifier to Increase Output Power With Stability Enhancement for mm-Wave Beamforming Systems. IEEE Trans. Microw. Theory Tech. 2022, 2022, 1–15. [Google Scholar] [CrossRef]

- Chen, Y.-C.; Lin, Y.-H.; Lin, J.-L.; Wang, H. A Ka-Band Transformer-Based Doherty Power Amplifier for Multi-Gb/s Application in 90-nm CMOS. IEEE Microw. Wirel. Components Lett. 2018, 28, 1134–1136. [Google Scholar] [CrossRef]

- Fang, X.; Xia, J.; Boumaiza, S. A 28-GHz Beamforming Doherty Power Amplifier With Enhanced AM-PM Characteristic. IEEE Trans. Microw. Theory Tech. 2020, 68, 3017–3027. [Google Scholar] [CrossRef]

- Jeong, H.; Lee, H.; Park, B.; Jang, S.; Kong, S.; Park, C. Optimization Technique for High-Gain CMOS Power Amplifier for 5G Applications. Appl. Sci. 2021, 11, 11691. [Google Scholar] [CrossRef]

- Chan, W.L.; Long, J.R. A 58–65 GHz Neutralized CMOS Power Amplifier With PAE Above 10% at 1-V Supply. IEEE J. Solid-state Circuits 2010, 45, 554–564. [Google Scholar] [CrossRef]

- Huang, W.-C.; Wang, H. An inductive-neutralized 26-dBm K-/Ka-band power amplifier with 34% PAE in 90-nm CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 4427–4440. [Google Scholar] [CrossRef]

- Lee, J.; Hong, S. A 24–30 GHz 31.7% Fractional Bandwidth Power Amplifier With an Adaptive Capacitance Linearizer. IEEE Trans. Circuits Syst. II Express Briefs 2020, 68, 1163–1167. [Google Scholar] [CrossRef]

- Lee, S.; Kang, S.; Hong, S. A 28-GHz CMOS Linear Power Amplifier With Low Output Phase Variation Over Dual Power Modes. IEEE Microw. Wirel. Components Lett. 2019, 29, 551–553. [Google Scholar] [CrossRef]

| TMTT ’19 [22] | TCAS-II ’21 [23] | MWCL ’19 [24] | Proposed Work | |

|---|---|---|---|---|

| Tech. (nm) | 90 | 28 | 65 | 65 |

| Freq. (GHz) | 28.0 | 30.0 | 28.0 | 28.5 |

| P1dB (dBm) | 23.2 | 17.2 | 16.5 | 22.0 |

| Gain (dB) | 16.3 | 21.2 | 18.0 | 23.3 |

| Peak PAE (%) | 34.1 | 30.3 | 27.3 | 27.7 |

| Modulation /Bandwidth | 64-QAM /100 MHz | 64-QAM /100 MHz | 64-QAM /100 MHz | 64-QAM /100 MHz |

| EVM (dBc) | −25.0 | −25.0 | −25.0 | −25.0 |

| POUT @EVM (dBm) | 19.0 | 10.9 | 7.5 | 17.3 |

| Core size (mm2) | 0.401 | 0.82 | 0.456 | 0.36 |

| Topology | 1-stage Cascode | 2-stage Cascode | 2-stage Cascode | 2-stage 3-stack |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, J.; Lee, J.; Jang, S.; Jeong, H.; Park, C. Ka-Band Three-Stack CMOS Power Amplifier with Split Layout of External Gate Capacitor for 5G Applications. Electronics 2023, 12, 432. https://doi.org/10.3390/electronics12020432

Yang J, Lee J, Jang S, Jeong H, Park C. Ka-Band Three-Stack CMOS Power Amplifier with Split Layout of External Gate Capacitor for 5G Applications. Electronics. 2023; 12(2):432. https://doi.org/10.3390/electronics12020432

Chicago/Turabian StyleYang, Junhyuk, Jaeyong Lee, Seongjin Jang, Hayeon Jeong, and Changkun Park. 2023. "Ka-Band Three-Stack CMOS Power Amplifier with Split Layout of External Gate Capacitor for 5G Applications" Electronics 12, no. 2: 432. https://doi.org/10.3390/electronics12020432

APA StyleYang, J., Lee, J., Jang, S., Jeong, H., & Park, C. (2023). Ka-Band Three-Stack CMOS Power Amplifier with Split Layout of External Gate Capacitor for 5G Applications. Electronics, 12(2), 432. https://doi.org/10.3390/electronics12020432