Design-Aware Parasitic-Aware Simulation Based Automation and Optimization of Highly Linear RF CMOS Power Amplifiers

Abstract

1. Introduction

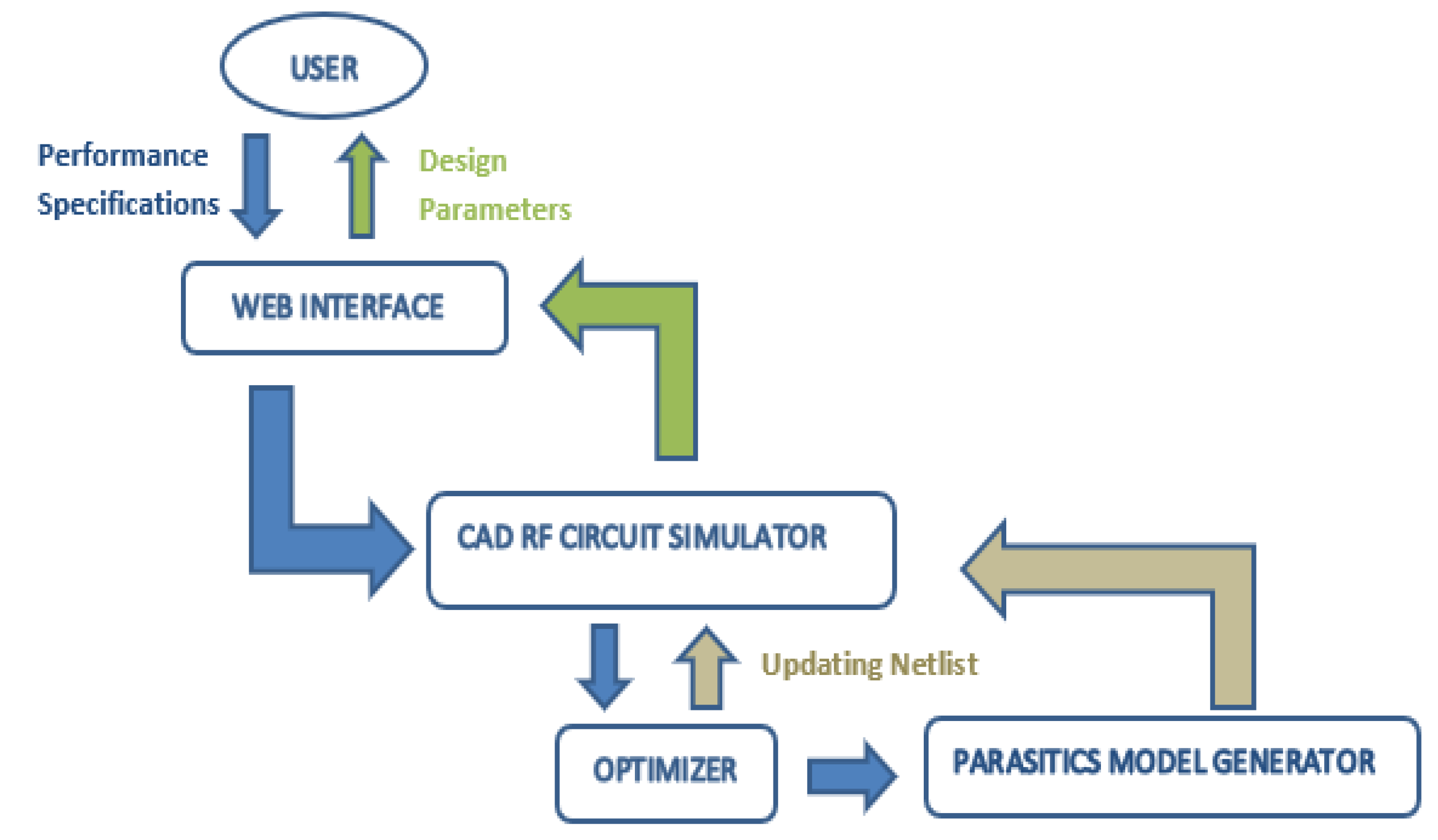

2. The Proposed Design Tool for RF Power Amplifiers

The Adopted Highly Linear PA Architecture

3. Parasitic Modelling

3.1. Parasitic Modelling for Passive Devices

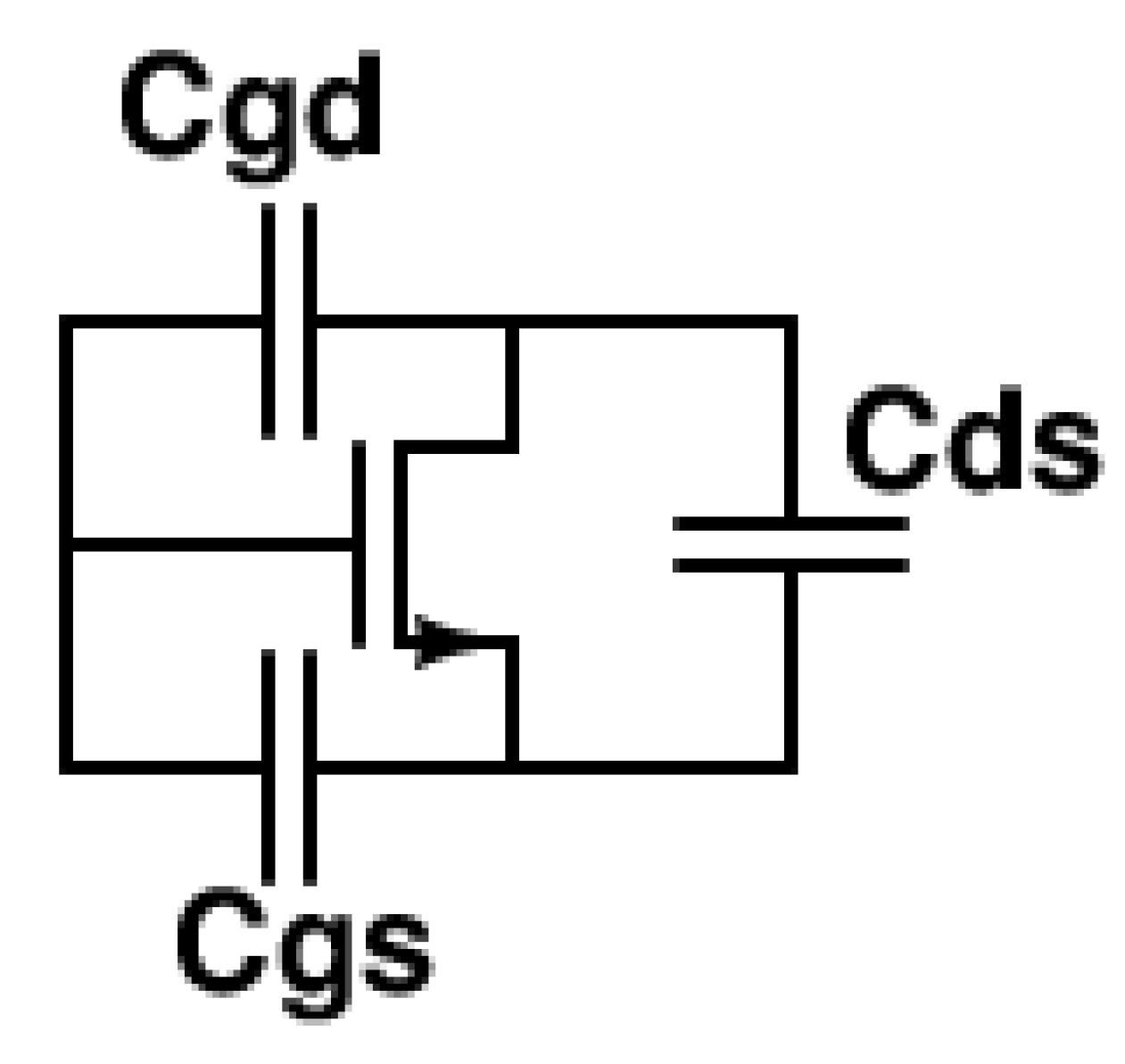

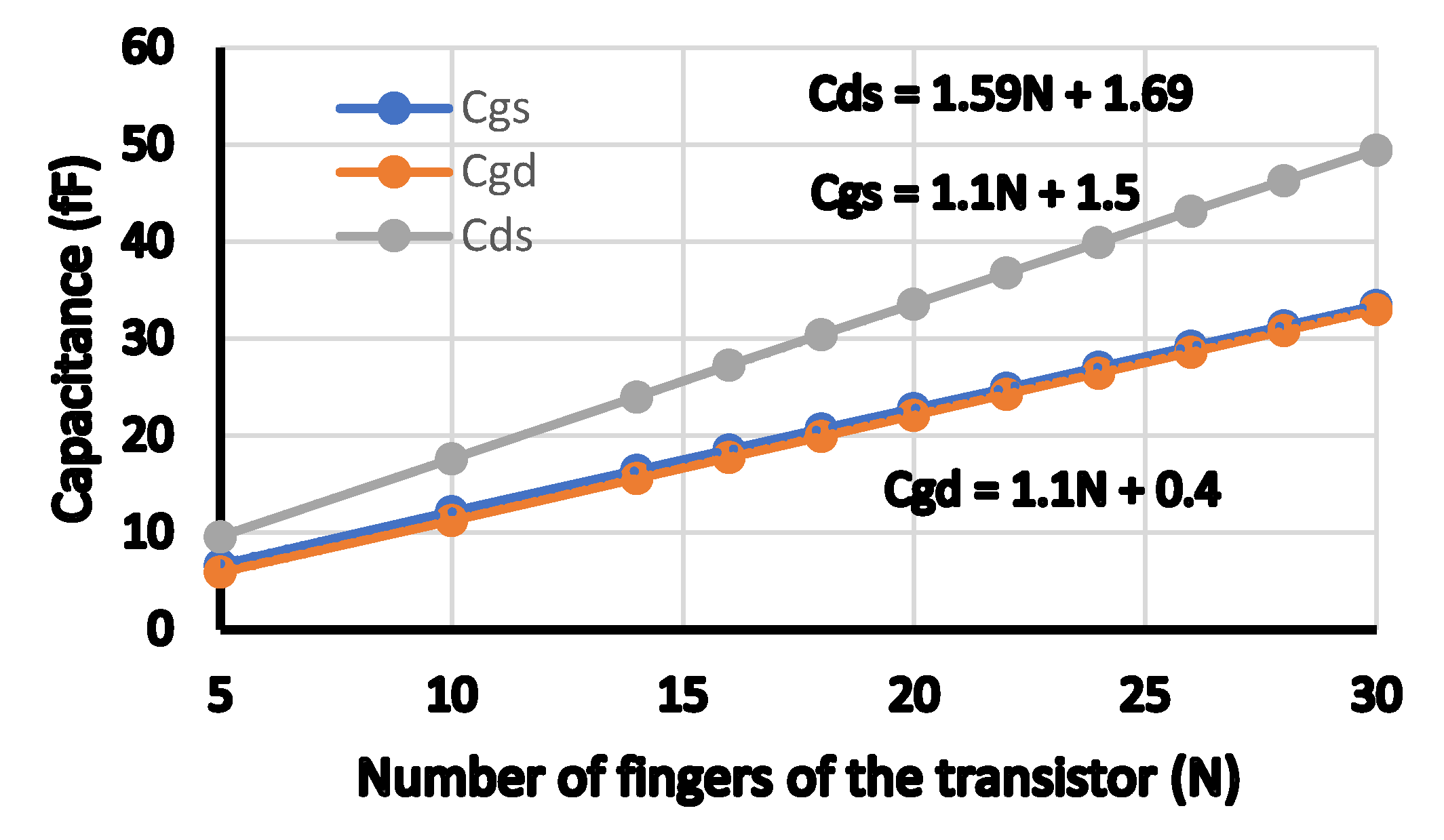

3.2. Parasitic Modelling for Active Devices

4. Design- Aware Optimization and the Proposed Design Flow

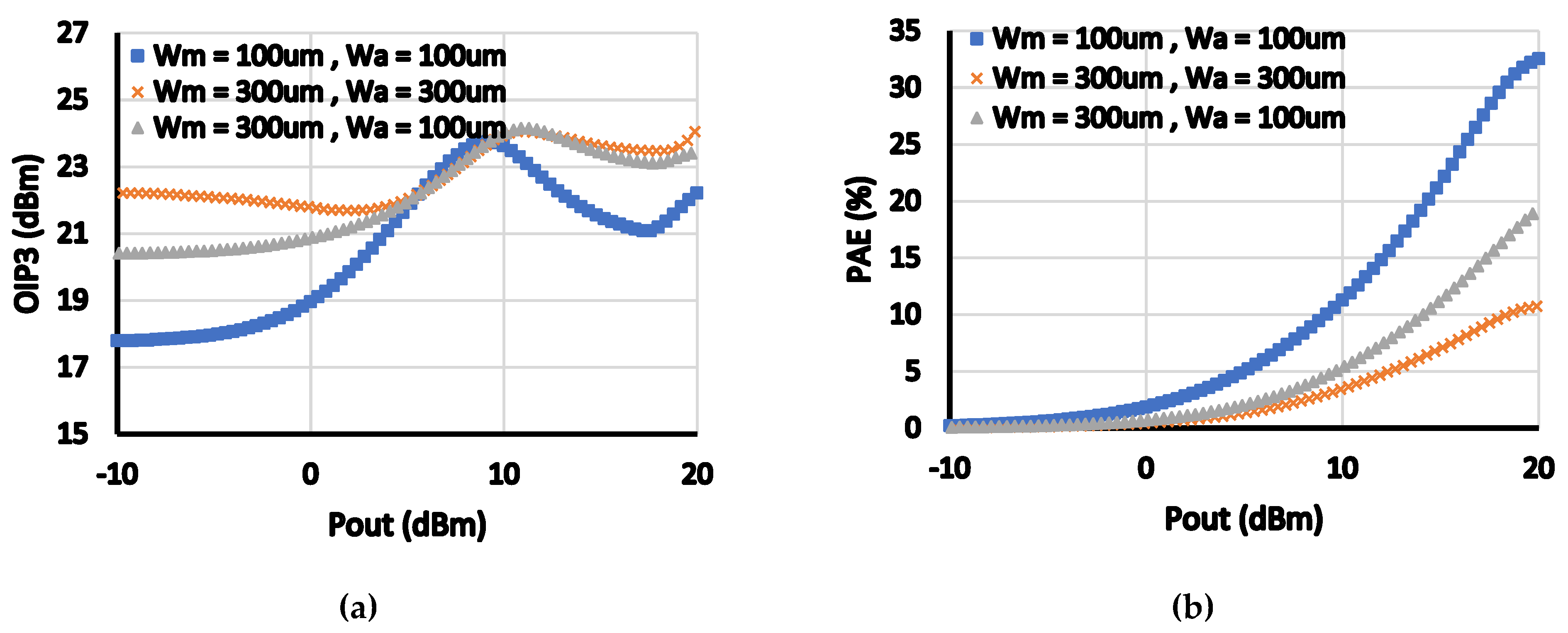

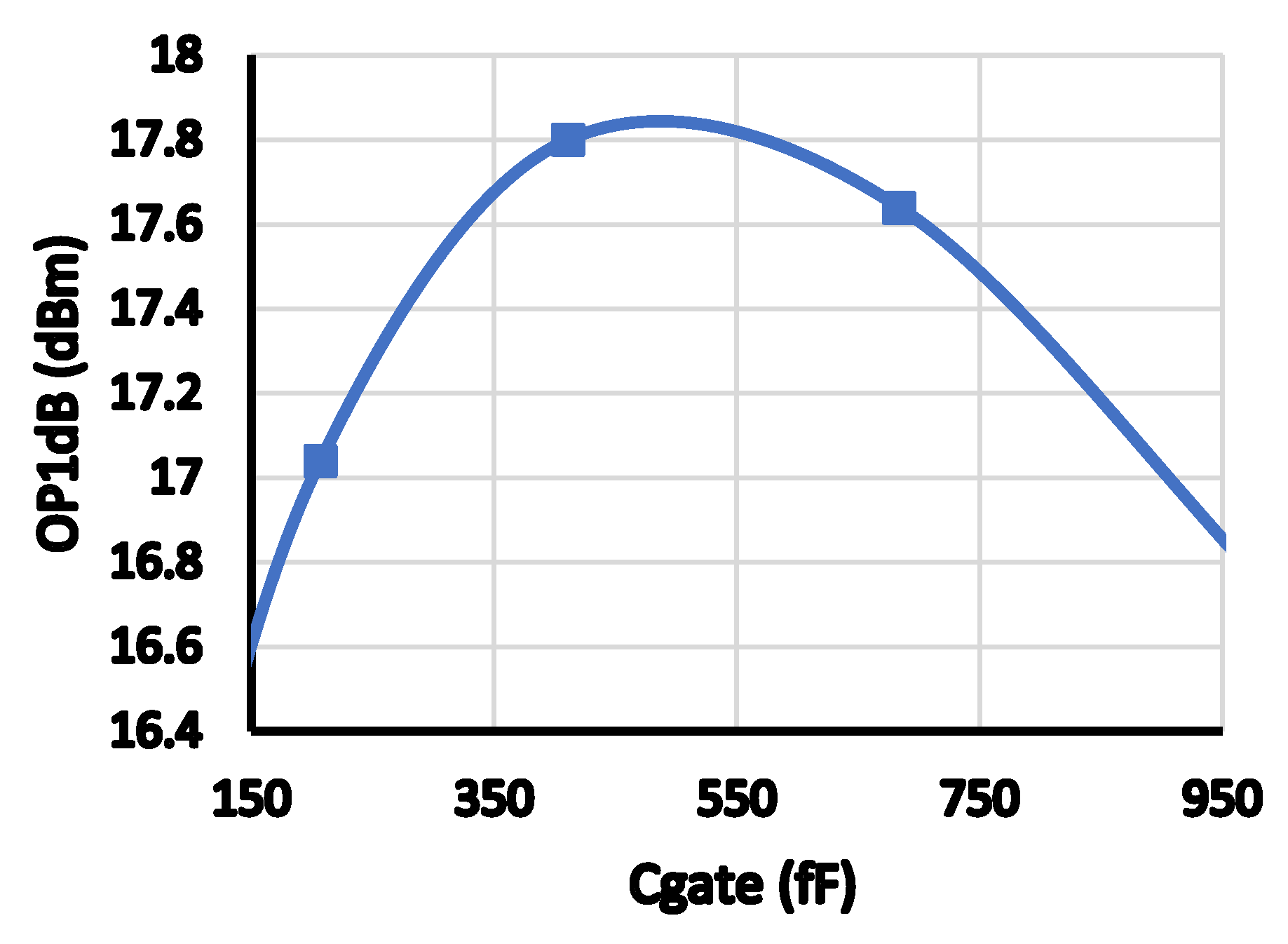

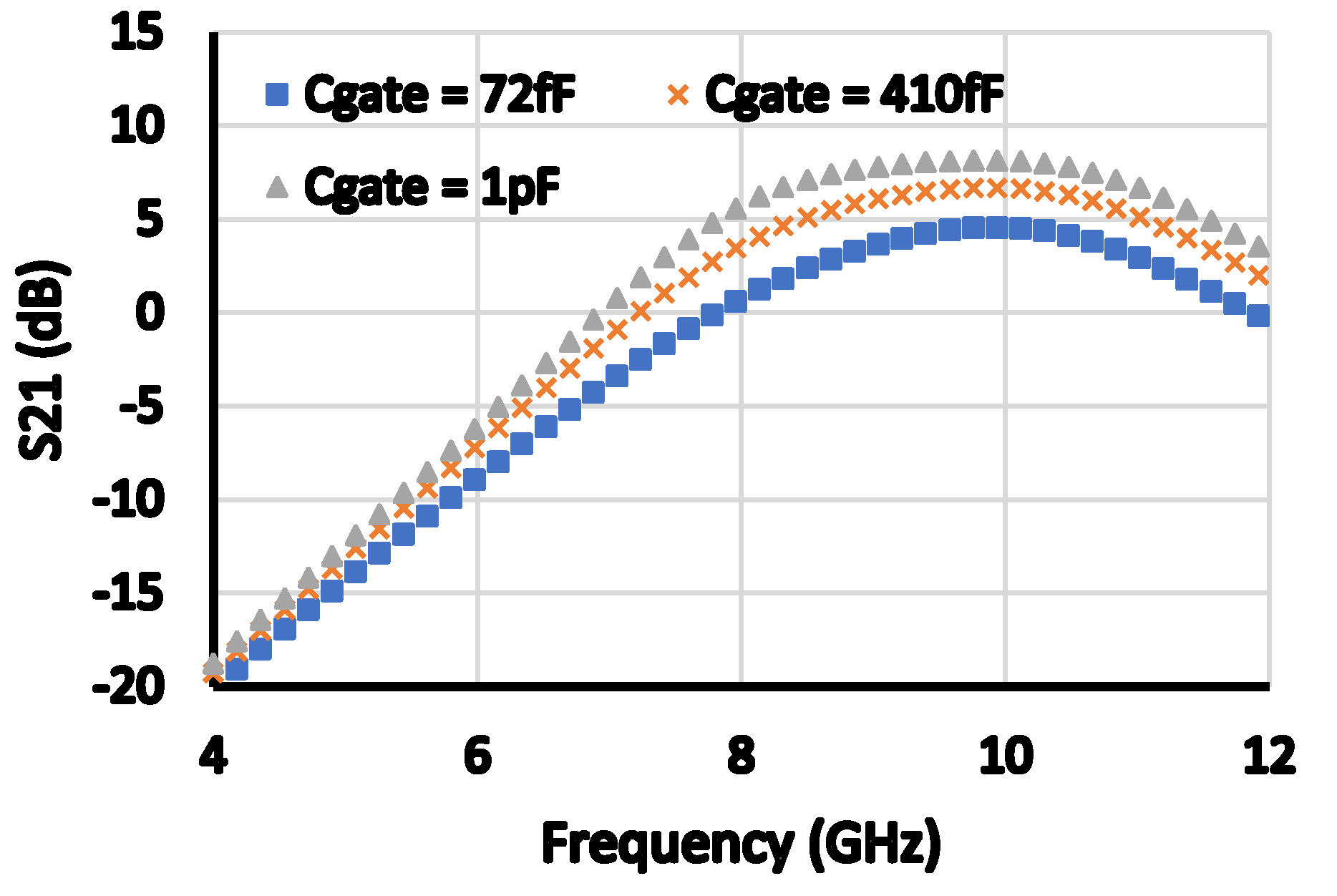

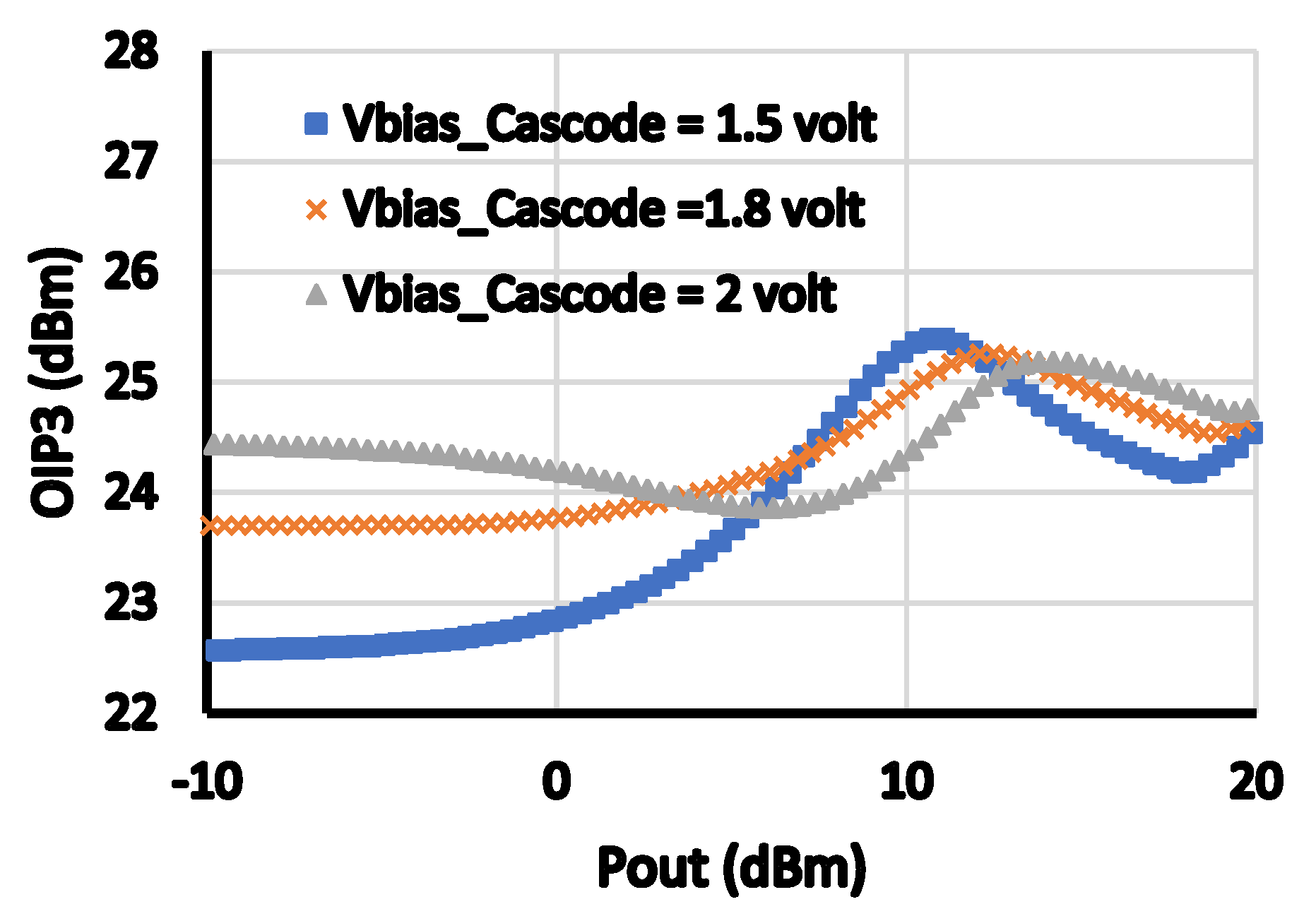

4.1. Design Trade-Offs and Sensitivity Analysis

4.2. The Optimization Flow

- The user enters the frequency of operation and the required specifications (minimum OP1 dB, minimum OIP3 at 6 dB back off power, minimum OIP3 at 10 dB back-off power and minimum gain (S21)) to the tool web interface. The minimum value of OIP3 at 6/10 dB back-off power will determine the efficiency of the power amplifier. In addition, weights for each targeted design specification are defined.

- The stability of the amplifier is considered as a hard constraint that needs to be met regardless of the performance specifications.

- The initial values of the design parameters need to be defined at the beginning of the optimization. Table 1 shows typical values for those parameters.

- Step 1 in Figure 16: the optimization of the input matching network parameters (C1, C2, C3, C4, and Lin) is carried out. The input to this step is the frequency and performance specifications entered by the user. The optimized values are input to steps 2, 3, 4, and 5.

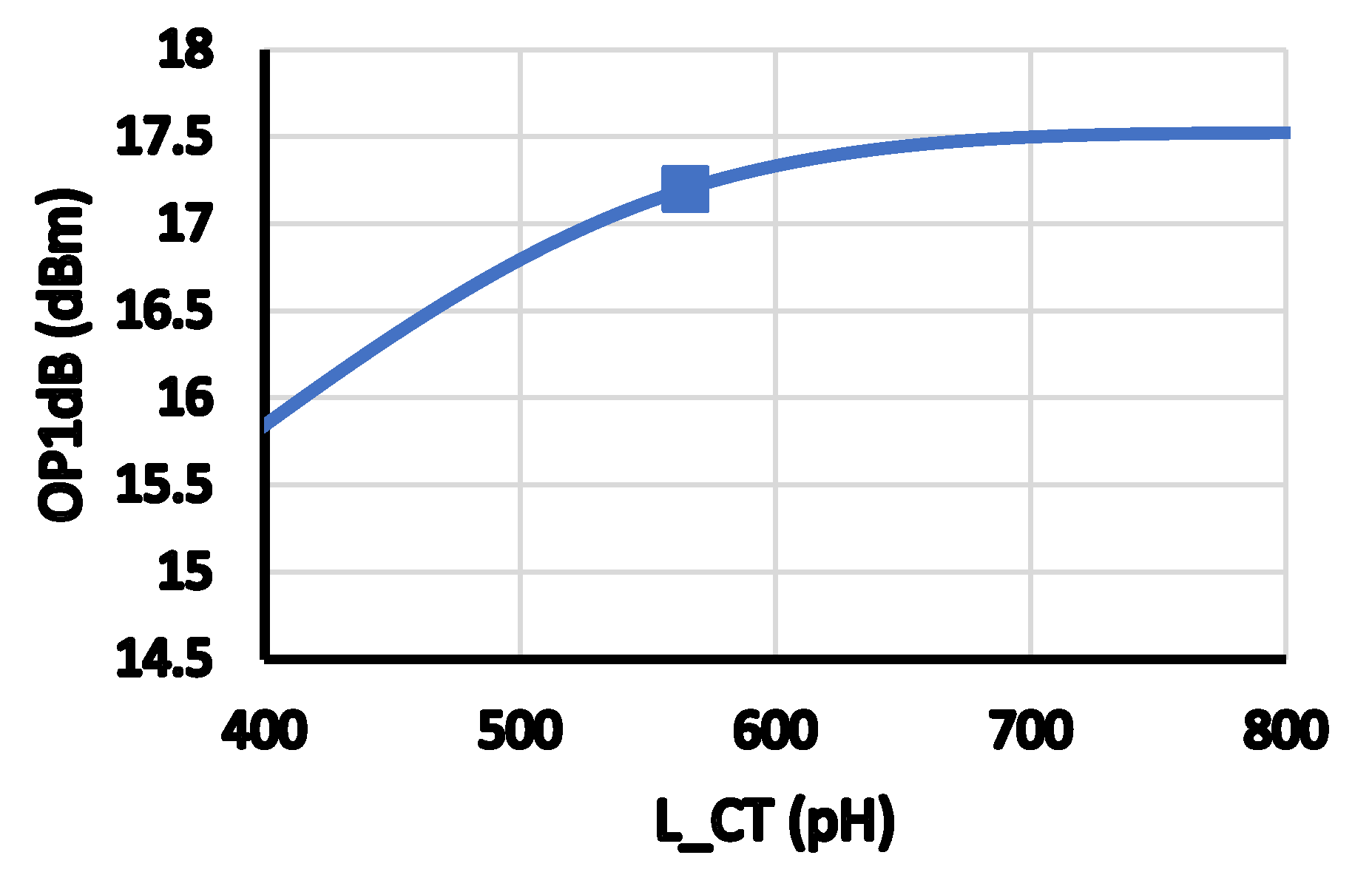

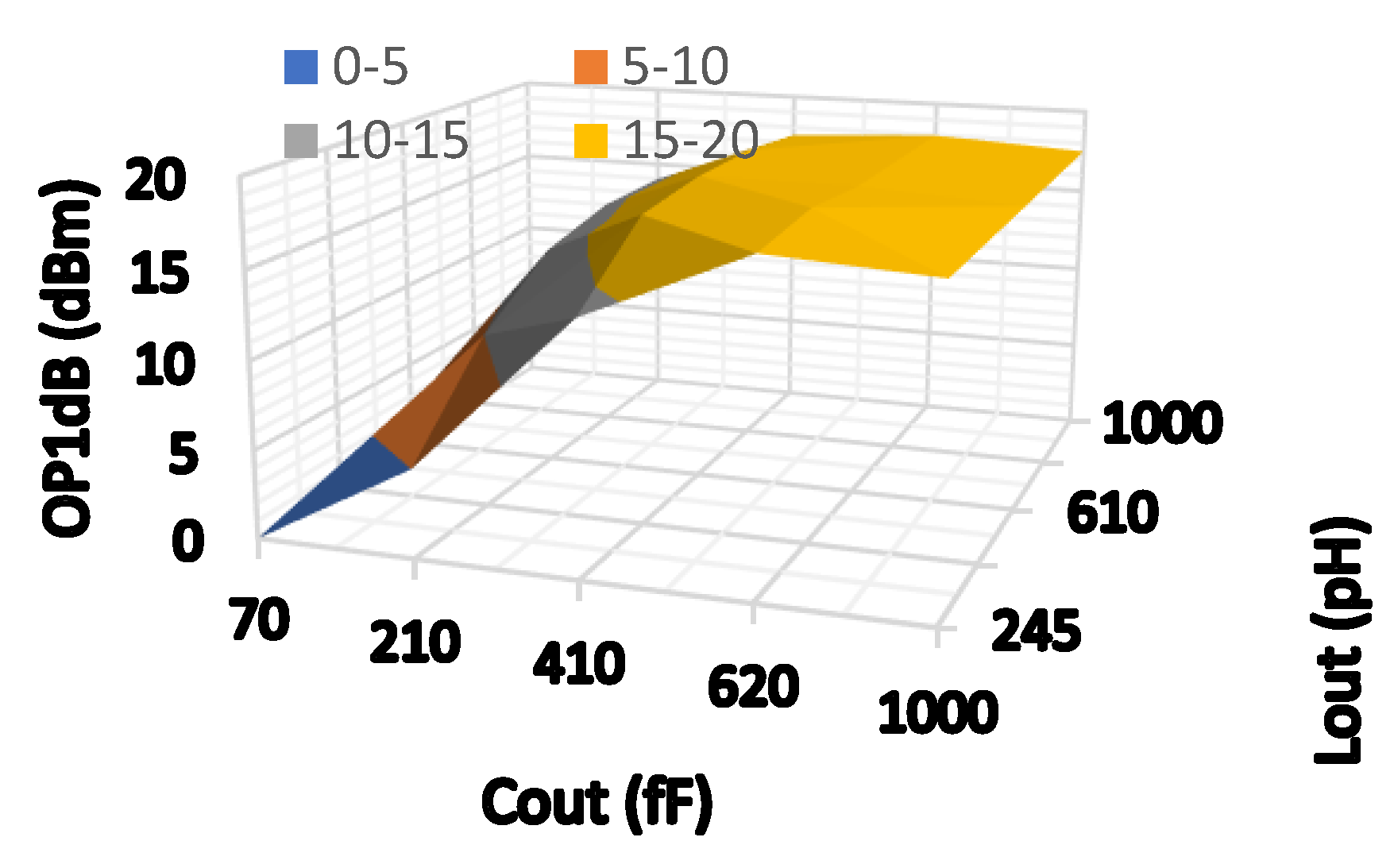

- Step 2 in Figure 16: the optimization of the output matching network parameters (Cout, Lout, and L_CT) is carried out. The input to this step is the frequency, performance specifications entered by the user, and the optimized parameters from step 1. The optimized values are input to steps 3, 4, and 5.

- Step 3 in Figure 16: the optimization of the biasing and sizing of transistors (Vm, Va, Wm, and Wa) is carried out. The input to this step is the frequency, performance specifications entered by the user, and the optimized parameters from steps 1 and 2. At the end of this step, the modelled parasitic capacitances arising from the transistor layout and its interconnects (Cgs, Cgd, and Cds) are updated corresponding to the optimized widths of the transistors (Wm and Wa). The optimized values are input to steps 4 and 5.

- Step 4 in Figure 16: the optimization of the gate capacitance (C7 and C8) and the cascode gate DC biasing voltage (Vcas) are carried out. The input to this step is the frequency, performance specifications entered by the user, and the optimized parameters from steps 1, 2, and 3. The optimized values are input to step 5.

- Step 5 in Figure 16: it is considered an evaluation point, which determines the next step in the optimization flow.

- If all the specifications (OP1 dB, S21, and OIP3) or (OP1 dB and S21) or (OIP3 and S21) or S21 failed, then the optimization flow is directed to step 1, where the values of the input matching network parameters are being optimized again, then all the rest of the steps will follow in succession. It is to be noted that when step 1 is carried out this time, all the other design parameters have new optimized values that differ from their previous values when step 1 was visited for the first time.

- If (OP1 dB and OIP3) or OP1 dB failed, then the optimization flow is directed to step 2, then all the rest of the steps (3, 4, and 5) will follow.

- If OIP3 failed, the optimization flow is directed to step 3, and then steps 4 and 5 will follow.

- The optimization flow stops when the best achieved design point is obtained based on the pre-defined weighting factors.

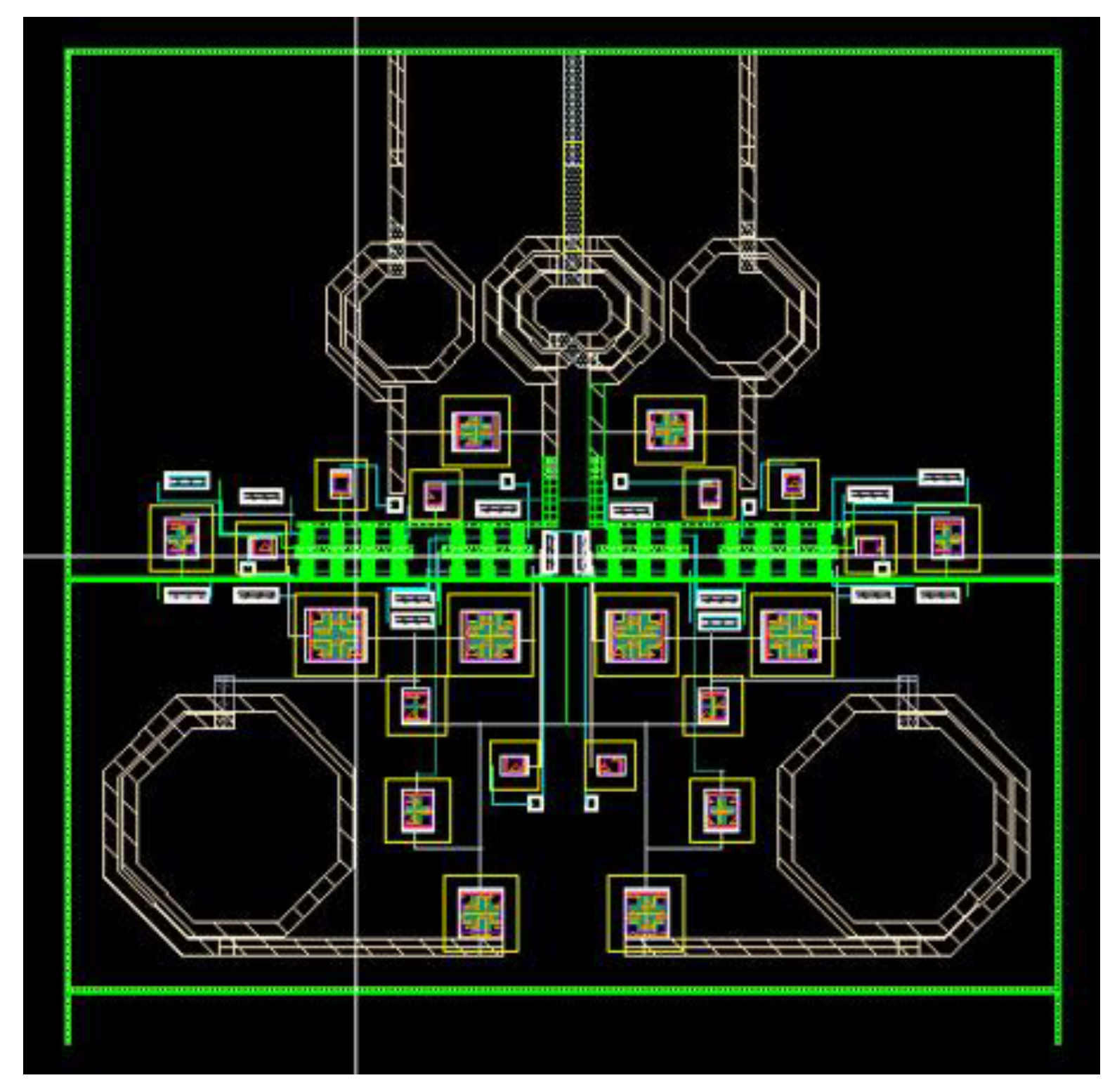

- The tool will return back to the web interface: the achieved values for all the required performance specifications, the consumed DC power, PAE at OP1 dB and at 6 dB back-off power, the values of the optimized design parameters, the circuit schematic, a template of the layout of the circuit, and a GDSII file for further modifications.

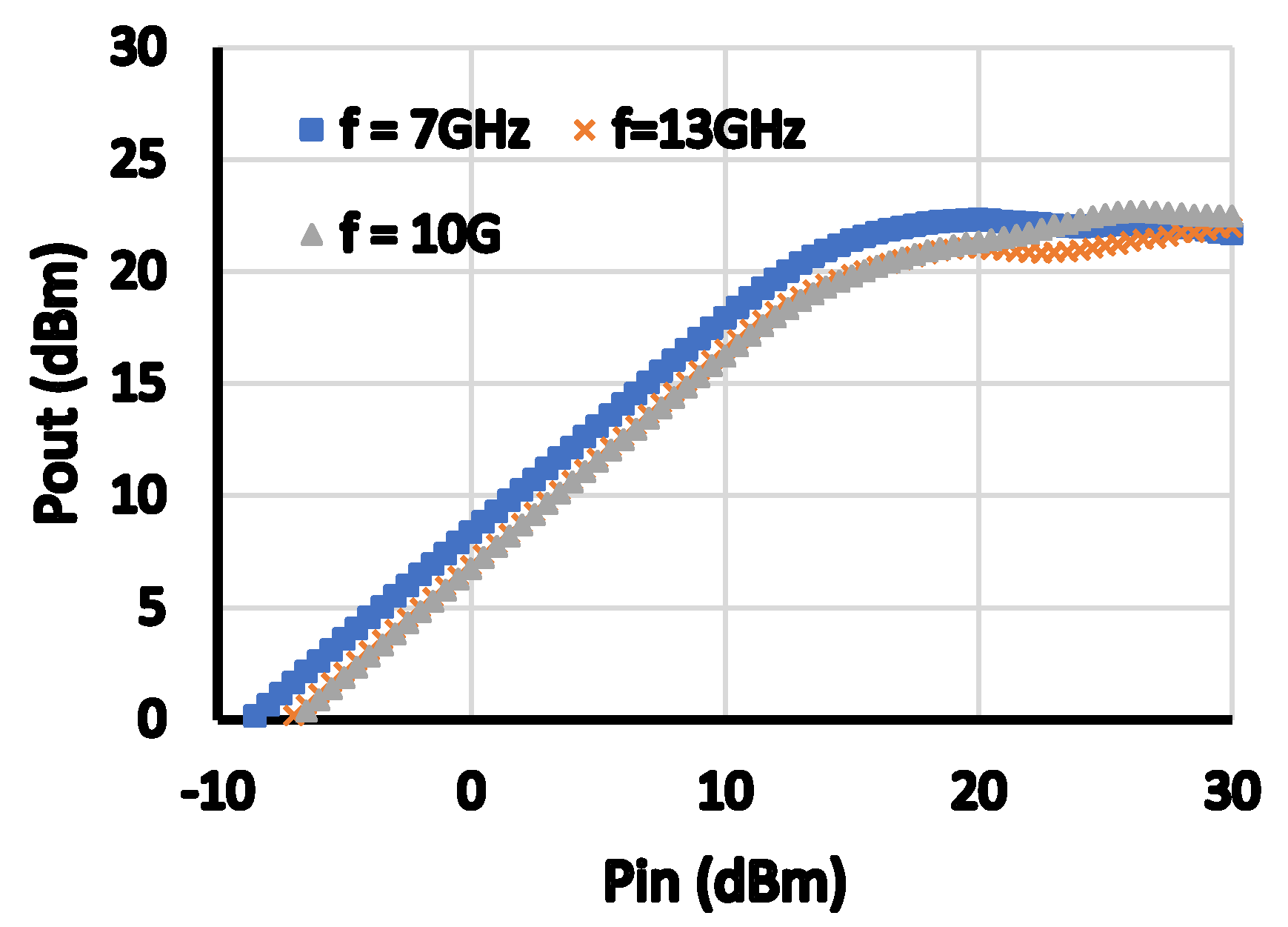

5. Automation and Test Cases Results

6. Discussion

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Sajedin, M.; Elfergani, I.T.E.; Rodriguez, J.; Abd-Alhameed, R.; Barciela, M.F. A Survey on RF and Microwave Doherty Power Amplifier for Mobile Handset Applications. Electronics 2019, 8, 717. [Google Scholar] [CrossRef]

- Kim, J.; Lee, C.; Yoo, J.; Park, C. Antiphase Method of the CMOS Power Amplifier Using PMOS Driver Stage to Enhance Linearity. Electronics 2020, 9, 103. [Google Scholar] [CrossRef]

- Mayeda, J.; Lie, D.Y.C.; Lopez, J. Broadband Millimeter-Wave 5G Power Amplifier Design in 22 nm CMOS FD-SOI and 40 nm GaN HEMT. Electronics 2022, 11, 683. [Google Scholar] [CrossRef]

- Cripps, S.C. RF Power Amplifiers for Wireless Communications, 2nd ed.; Artech: Norwood, MA, USA, 2006. [Google Scholar]

- Borel, A.; Barzdėnas, V.; Vasjanov, A. Linearization as a Solution for Power Amplifier Imperfections: A Review of Methods. Electronics 2021, 10, 1073. [Google Scholar] [CrossRef]

- Yan, W.; Liu, C.; Zhou, S.; Wu, Z.; Zhang, J. Design and measurement analysis of Class AB power amplifier. In Proceedings of the 2016 IEEE International Conference on Microwave and Millimeter Wave Technology (ICMMT), Beijing, China, 5–8 June 2016; pp. 849–851. [Google Scholar]

- Joo, T.; Koo, B.; Hong, S. A WLAN RF CMOS PA with adaptive power cells. In Proceedings of the 2013 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Seattle, WA, USA, 2–4 June 2013; pp. 345–348. [Google Scholar]

- Lu, C.; Pham, A.V.H.; Shaw, M.; Saint, C. Linearization of CMOS Broadband Power Amplifiers Through Combined Multigated Transistors and Capacitance Compensation. IEEE Trans. Microw. Theory Tech. 2007, 55, 2320–2328. [Google Scholar]

- Martins, R.; Lourenco, N.; Passos, F.; Povoa, R.; Canelas, A.; Roca, E.; Castro-Lopez, R.; Sieiro, J.; Fernandez, F.V.; Horta, N. Two-Step RF IC Block Synthesis with Preoptimized Inductors and Full Layout Generation In-the-Loop. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2018, 38, 989–1002. [Google Scholar] [CrossRef]

- Ramos, J.; Francken, K.; Gielen, G.G.E.; Steyaert, M.S.J. An efficient, fully parasitic-aware power amplifier design optimization tool. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1526–1534. [Google Scholar] [CrossRef]

- Gonzalez-Echevarria, R.; Roca, E.; Castro-Lopez, R.; Fernandez, F.V.; Sieiro, J.; Lopez-Villegas, J.M.; Vidal, N. An Automated Design Methodology of RF Circuits by Using Pareto-Optimal Fronts of EM-Simulated Inductors. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2017, 36, 15–26. [Google Scholar] [CrossRef]

- Berkol, G.; Unutulmaz, A.; Afacan, E.; Dündar, G.; Fernandez, F.V.; Pusane, A.E.; Başkaya, F. A two-step layout-in-the-loop design automation tool. In Proceedings of the IEEE 13th International New Circuits and Systems Conference (NEWCAS), Grenoble, France, 7–10 June 2015. [Google Scholar]

- Gupta, R.; Ballweber, B.; Allstot, D. Design and optimization of CMOS RF power amplifiers. IEEE J. Solid-State Circuits 2001, 36, 166–175. [Google Scholar] [CrossRef]

- Liu, B.; Deferm, N.; Zhao, D.; Reynaert, P.; Gielen, G.G.E. An Efficient High-Frequency Linear RF Amplifier Synthesis Method Based on Evolutionary Computation and Machine Learning Techniques. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2012, 31, 981–993. [Google Scholar] [CrossRef]

- Vancorenland, P.; De Ranter, C.; Steyaert, M.; Gielen, G. Optimal RF Design Using Smart Evolutionary Algorithms. In Proceedings of the 37th Annual Design Automation Conference, Los Angeles, CA, USA, 5–9 June 2000; pp. 7–10. [Google Scholar]

- Lberni, A.; Sallem, A.; Marktani, M.A.; Ahaitouf, A.; Masmoudi, N.; Ahaitouf, A. Simulation-Based Optimization for Automated Design of Analog/RF Circuits. In WITS 2020. Lecture Notes in Electrical Engineering; Bennani, S., Lakhrissi, Y., Khaissidi, G., Mansouri, A., Khamlichi, Y., Eds.; Springer: Singapore, 2022; Volume 745. [Google Scholar]

- Liao, T.; Zhang, L. Parasitic-Aware GP-Based Many-Objective Sizing Methodology for Analog and RF Integrated Circuits. In Proceedings of the 2017 22nd Asia and South Pacific Design Automation Conference (ASP-DAC), Chiba, Japan, 16–19 January 2017; pp. 475–480. [Google Scholar]

- Afacan, E.; Dündar, G. A Mixed Domain Sizing Approach for RF Circuit Synthesis. In Proceedings of the 2016 IEEE 19th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), Kosice, Slovakia, 20–22 April 2016; pp. 1–4. [Google Scholar]

- Virtuoso Analog Design Environment GXL. Cadence.com. Available online: www.cadence.com/content/dam/cadence-www/global/en_US/documents/tools/custom-ic-analog-rf-design/virtuoso-analog-design-environment-gxl-ds.pdf (accessed on 20 October 2022).

- Spectre RF Option. Cadence.Com. Available online: www.cadence.com/en_US/home/tools/custom-ic-analog-rf-design/circuit-simulation/spectre-rf-option.html (accessed on 10 November 2022).

- Brownlee, J. A Gentle Introduction to the BFGS Optimization Algorithm. Tutorial on Optimization. Available online: https://machinelearningmastery.com/bfgs-optimization-in-python/ (accessed on 19 May 2021).

- Nocedal, J.; Wright, S. Numerical Optimization (Chapter 6), 2nd ed.; Springer: Berlin/Heidelberg, Germany, 2006. [Google Scholar]

- Kang, S.; Baek, D.; Hong, S. A 5-GHz WLAN RF CMOS Power Amplifier with a Parallel-Cascoded Configuration and an Active Feedback Linearizer. IEEE Trans. Microw. Theory Tech. 2017, 65, 3230–3244. [Google Scholar] [CrossRef]

- De Ranter, C.; Van der Plas, G.; Steyaert, M.; Gielen, G.; Sansen, W. CYCLONE: Automated design and layout of RF LC-oscillators. IEEE Trans. Comput. Des. Integr. Circuits Syst. 2002, 21, 1161–1170. [Google Scholar] [CrossRef]

- Zhang, G.; Dengi, A.; Rohrer, R.A.; Rutenbar, R.A.; Carley, L.R. A Synthesis Flow Toward Fast Parasitic Closure for Radio-Frequency Integrated Circuits. In Proceedings of the 41st Annual Design Automation Conference, San Diego, CA, USA, 7–11 June 2004; pp. 155–158. [Google Scholar]

| Design Parameters | Design Values | |

|---|---|---|

| Length of all transistors | 60 nm | |

| Width of M1 and M3 | 100 µm | |

| Width of M2 and M4 | 300 µm | |

| Biasing | Vm (Main) | 370 mv |

| Va (auxiliary) | 370 mv | |

| Vcas (cascode) | 1.55 v | |

| Input Matching Network | Lin | 430 pH |

| C1 | 700 fF | |

| C2 | 250 fF | |

| C3, C4 | 1 pF | |

| Output Matching Network | Cout | 400 fF |

| Lout | 850 pH | |

| L_CT | 1 nH | |

| Feedback Stability Loops | R | 2 kΩ |

| C | 100 fF | |

| Gate Capacitances | C7 | 365 fF |

| C8 | 365 fF | |

| Performance Specifications | Design Parameters |

|---|---|

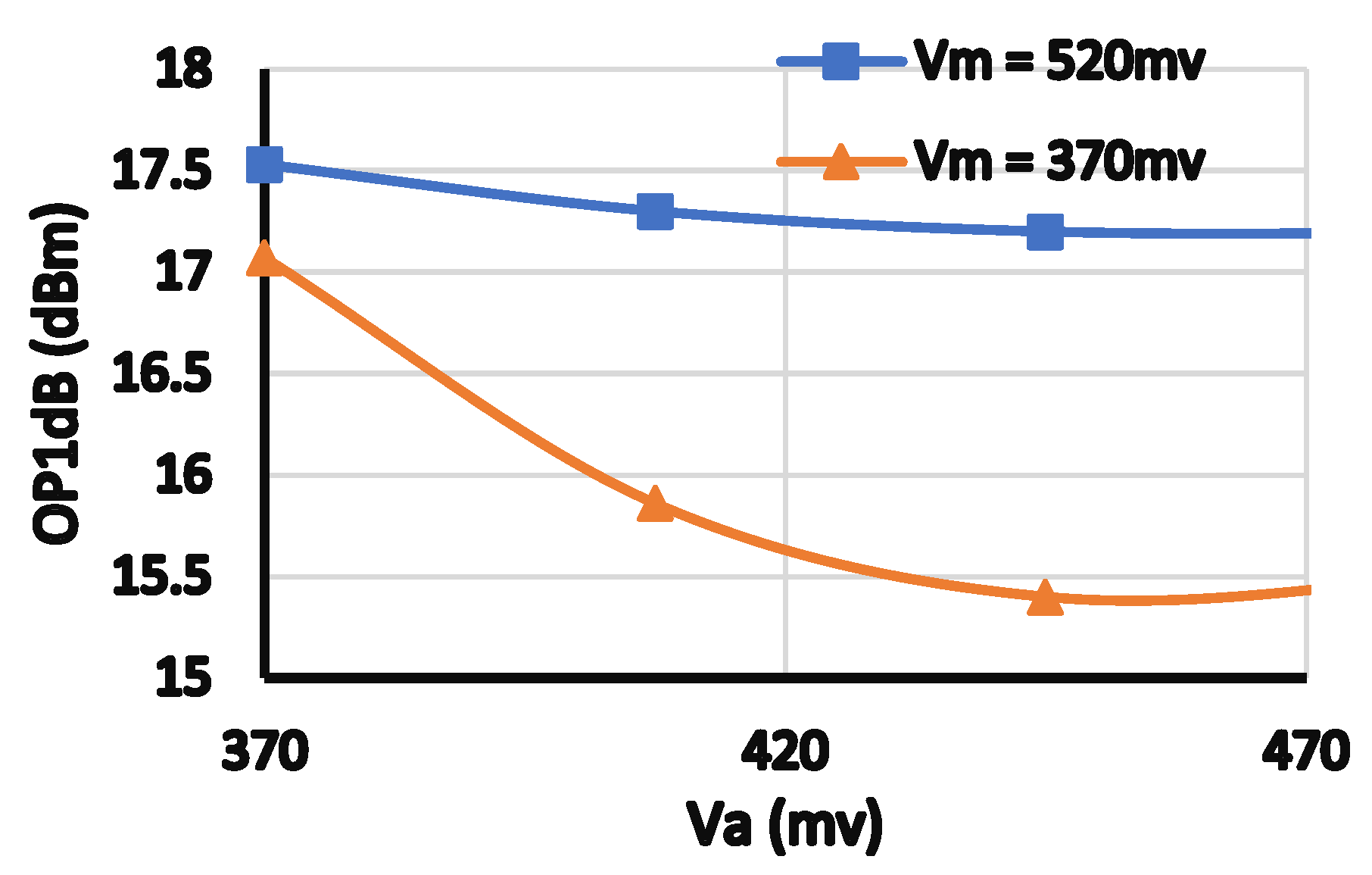

| OP1 dB | Cout, Lout, and L_CT Wm, Wa, Vm, Va, and Cgate |

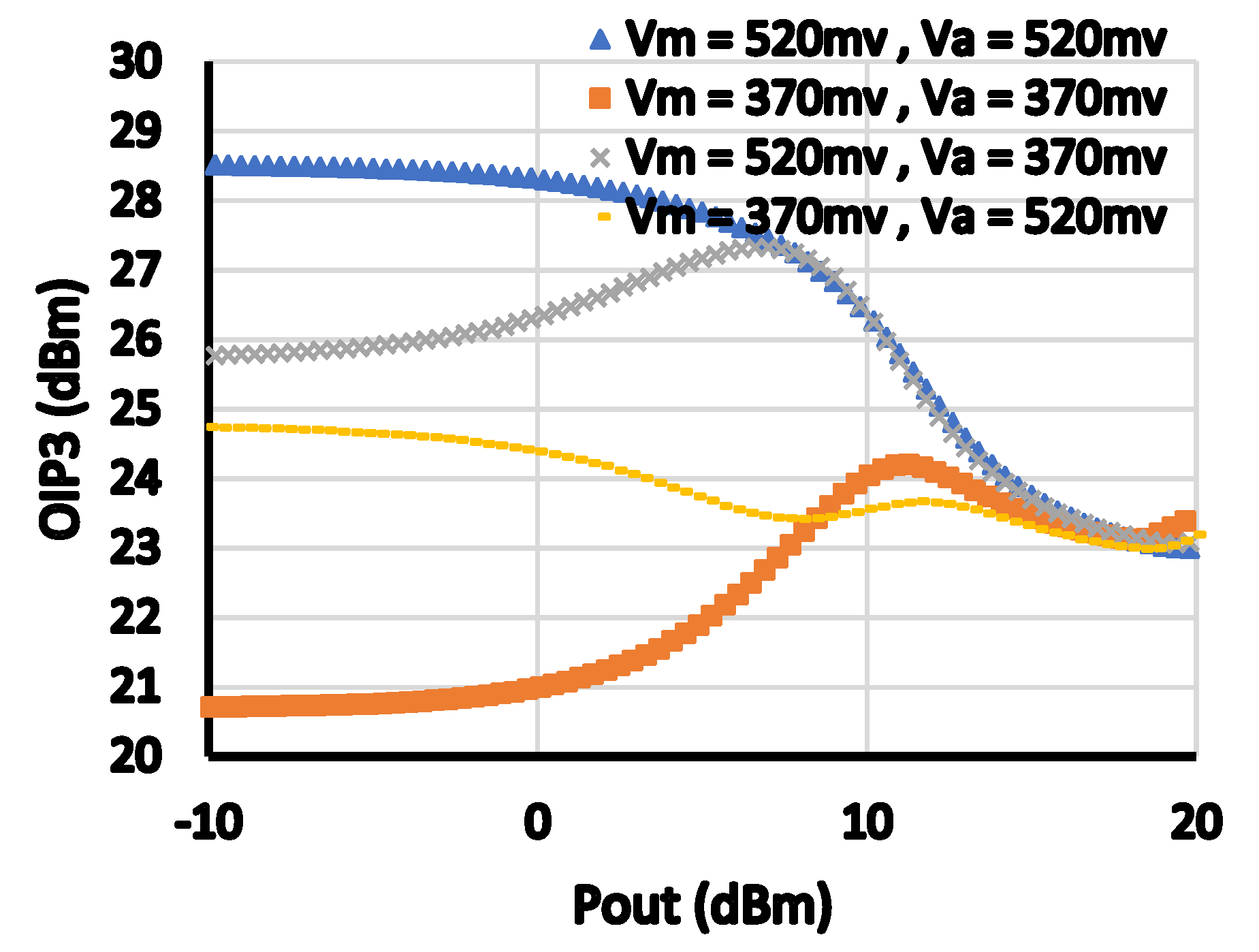

| OIP3 | Vm, Va, Wm, and Wa |

| Gain (S21) | Cout, Lout, and L_CT Lin, C1, C2, C3, and C4 Wm, Wa, Vm, Va, and Cgate |

| PAE | Wm and Wa Vm and Va |

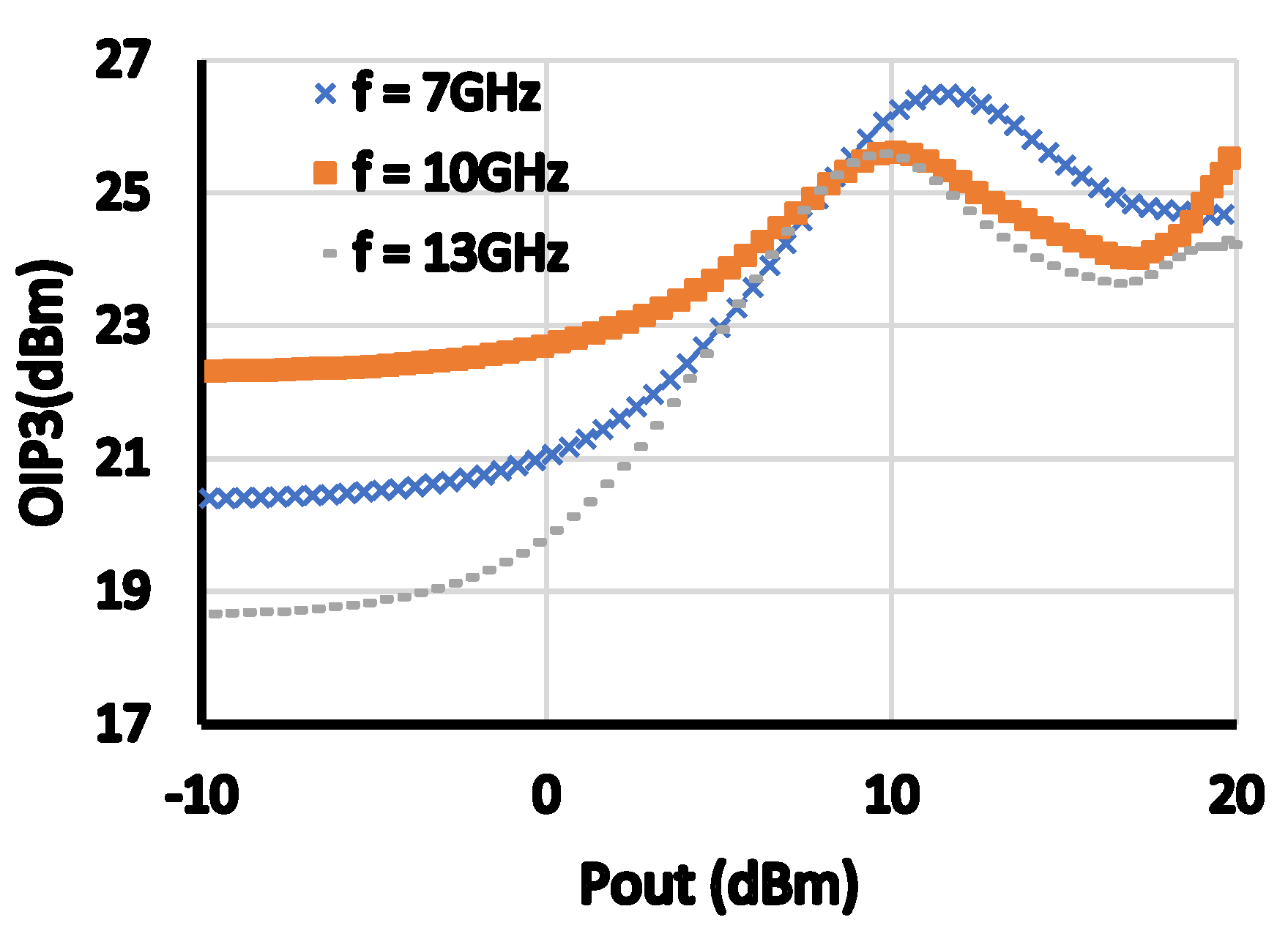

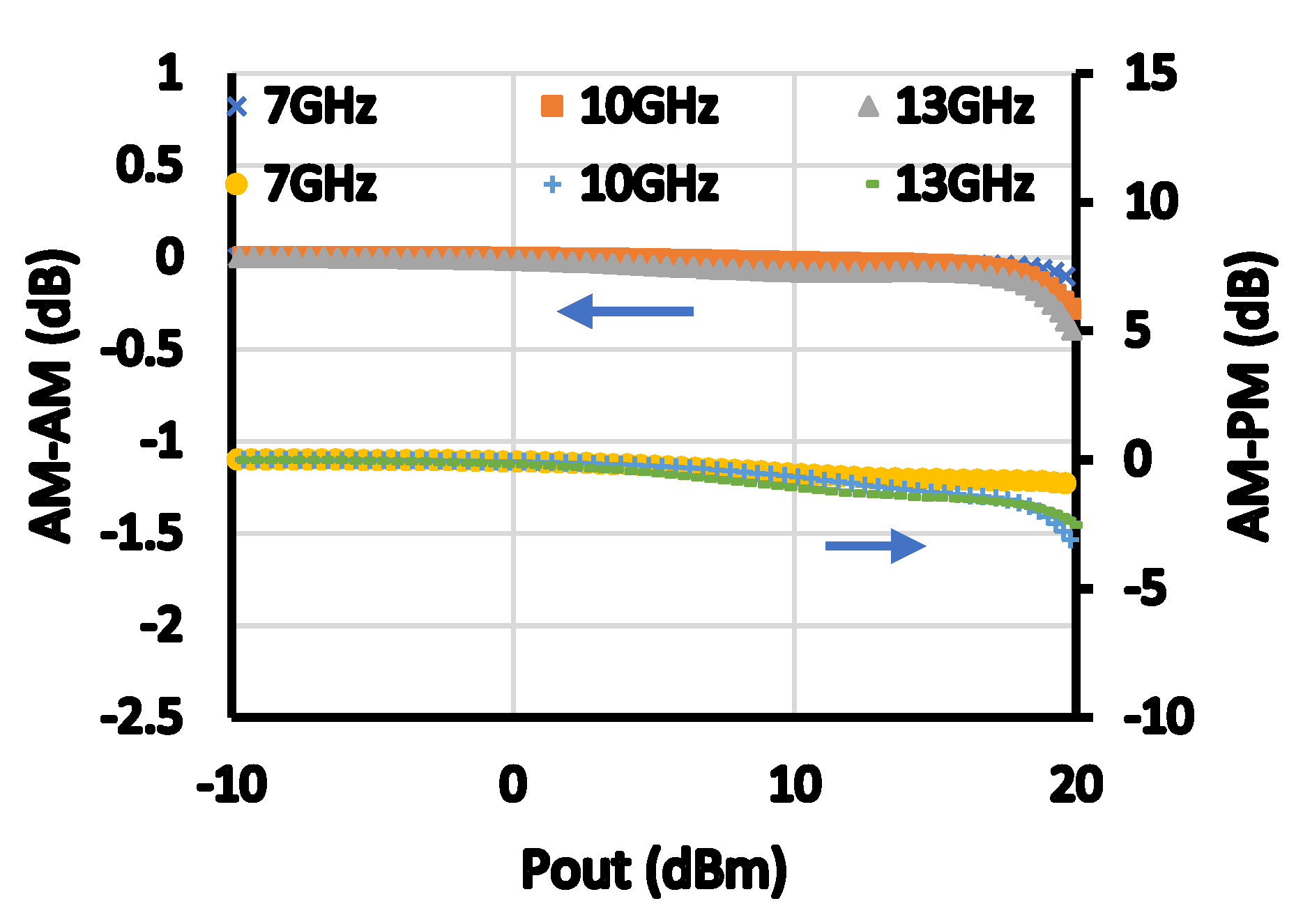

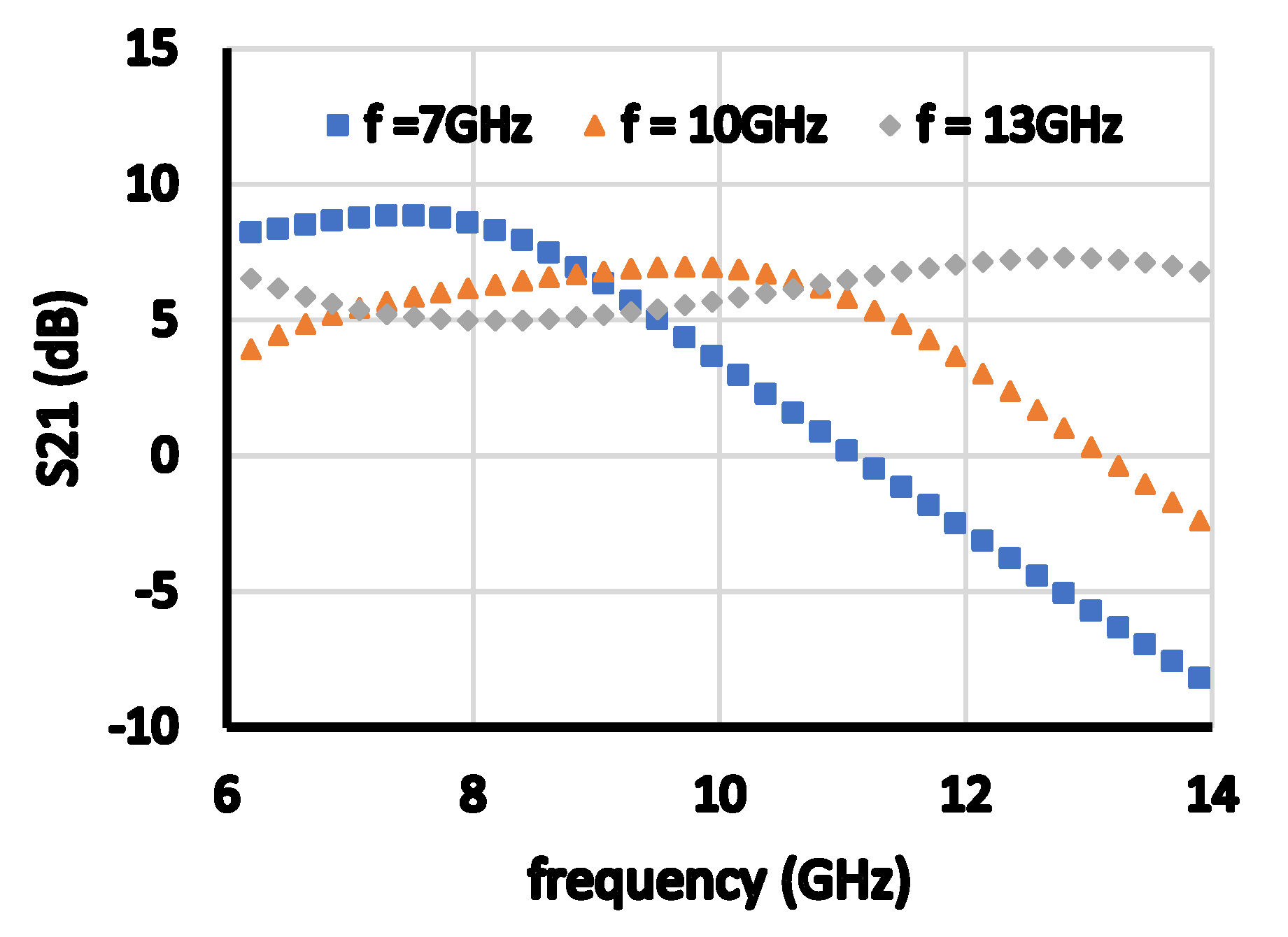

| Performance Specifications | Required | Achieved | ||

|---|---|---|---|---|

| 7 GHz | 10 GHz | 13 GHz | ||

| OP1 dB | >18 dBm | 19 dBm | 18.2 dBm | 18.1 dBm |

| OIP3 at 6 dB back-off power | >24 dBm | 26 dBm | 25.2 dBm | 24.7 dBm |

| S21 | >7 dB | 8.7 dB | 7.1 dB | 7.3 dB |

| DC Consumed Power | - | 89.5 mw | 89.52 mw | 55 mw |

| PAE at OP1 dB | - | 27% | 22 % | 29% |

| PAE at 6 dB back-off | - | 22% | 9% | 15% |

| Work | Performance Evaluator | Inductor Modelling | Layout Included Parasitic Components | Optimizer |

|---|---|---|---|---|

| [15], 2000 | Circuit Simulator and Performance Models | Not Included | Device and interconnect C and CC | Evolutionary Algorithms |

| [13], 2001 | Parametric Equations | Parasitic-included compact model | Not Included | Simulated-Annealing based |

| [24], 2002 | Circuit Simulator | In-the-loop EM simulation | Not Included | Simulated-Annealing based |

| [25], 2004 | Performance Models | Linear behavior into PMs | Not specified | Simulation-based |

| [14], 2012 | Circuit Simulator | EM-based surrogate model built in the loop | Not Included | Evolutionary Algorithms |

| [18], 2016 | Circuit Simulator | 2-п model | Other passive components | Evolutionary Algorithms and simulated-Annealing |

| [11], 2017 | Circuit Simulator | EM-Simulated Pareto-Optimal Front (POF) obtained a priori | Not Included | Particle Swarm Optimization (PSO) |

| [17], 2017 | Performance Models | Linear behavior into PMs | Device and interconnect C, CC, and R | Evolutionary Algorithm based |

| [16], 2022 | Circuit Simulator | 2-п model | Not Included | Meta-heuristics algorithms |

| This Work | Circuit Simulator | Foundry process design kit (PDK) model | Device and interconnect C and CC | BFGS algorithm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Onsy, R.A.; El-Nozahi, M.; Ragai, H. Design-Aware Parasitic-Aware Simulation Based Automation and Optimization of Highly Linear RF CMOS Power Amplifiers. Electronics 2023, 12, 272. https://doi.org/10.3390/electronics12020272

Onsy RA, El-Nozahi M, Ragai H. Design-Aware Parasitic-Aware Simulation Based Automation and Optimization of Highly Linear RF CMOS Power Amplifiers. Electronics. 2023; 12(2):272. https://doi.org/10.3390/electronics12020272

Chicago/Turabian StyleOnsy, Rana Aly, Mohamed El-Nozahi, and Hani Ragai. 2023. "Design-Aware Parasitic-Aware Simulation Based Automation and Optimization of Highly Linear RF CMOS Power Amplifiers" Electronics 12, no. 2: 272. https://doi.org/10.3390/electronics12020272

APA StyleOnsy, R. A., El-Nozahi, M., & Ragai, H. (2023). Design-Aware Parasitic-Aware Simulation Based Automation and Optimization of Highly Linear RF CMOS Power Amplifiers. Electronics, 12(2), 272. https://doi.org/10.3390/electronics12020272