New Multicell Switched-Inductor Quasi-Z-Source Inverter

Abstract

:1. Introduction

- (1)

- (2)

- When combining switched-inductor and switched-capacitors with quasi-Z source inverters, some new qZSI topologies have been obtained one after another [8,9,10,11,12,13,14]. In the literature [8,9], the switched-inductor is combined with the impedance source network to obtain SL-ZSI and SL-qZSI, and the boosting capability is improved. Compared to SL-QZSI, iSL-1ZSI [10], rSL-qZSI [11], and cSL-qZSI [11] improve the boosting capability, voltage stress, and current ripple of the inverter. ASC/SL-qZSI [12], ESL-qZSI [13], SCL-qZSI [14], and ESCL-qZSI [14] also belong to this category of construction methods.

- (3)

- (4)

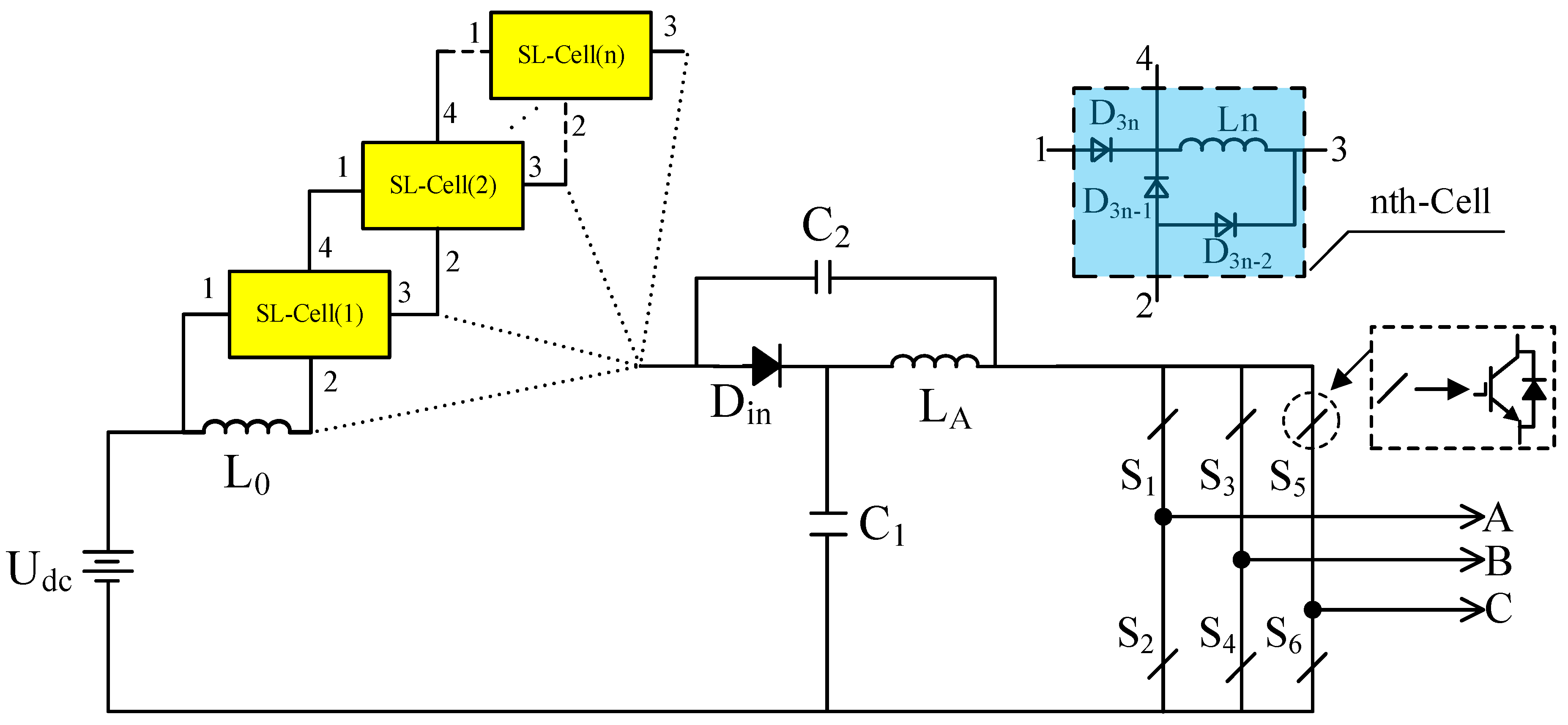

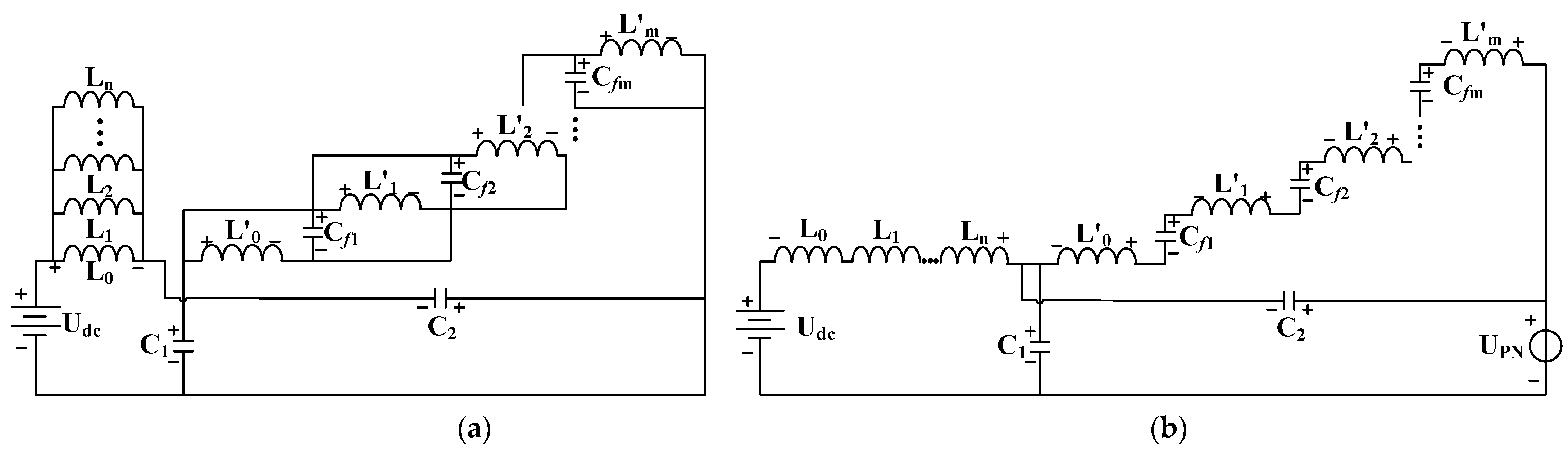

2. Traditional Multicell Switched-Inductor Quasi-Z-Source Inverter

3. New Multicell Switched-Inductor Quasi-Z-Source Inverter

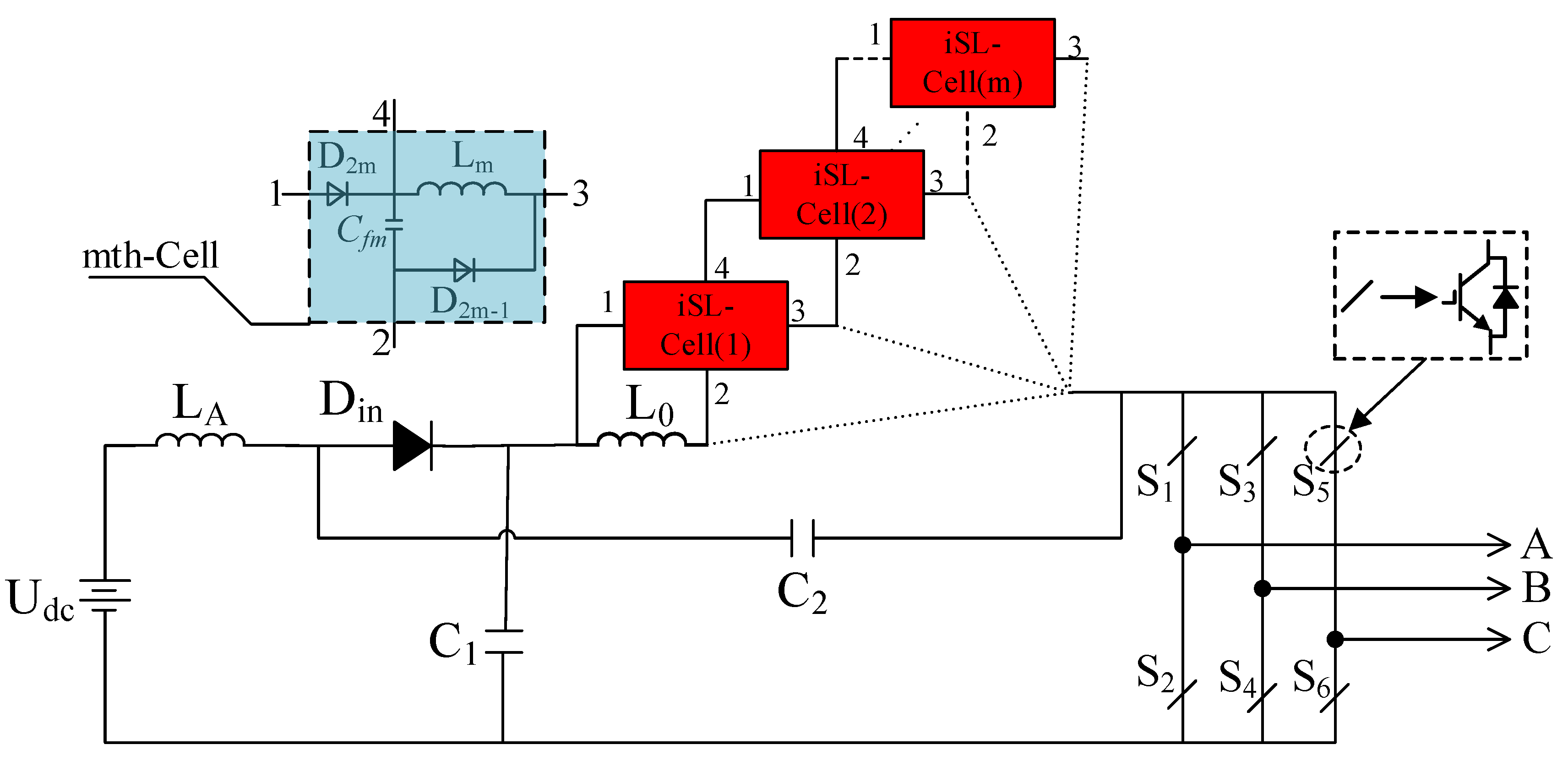

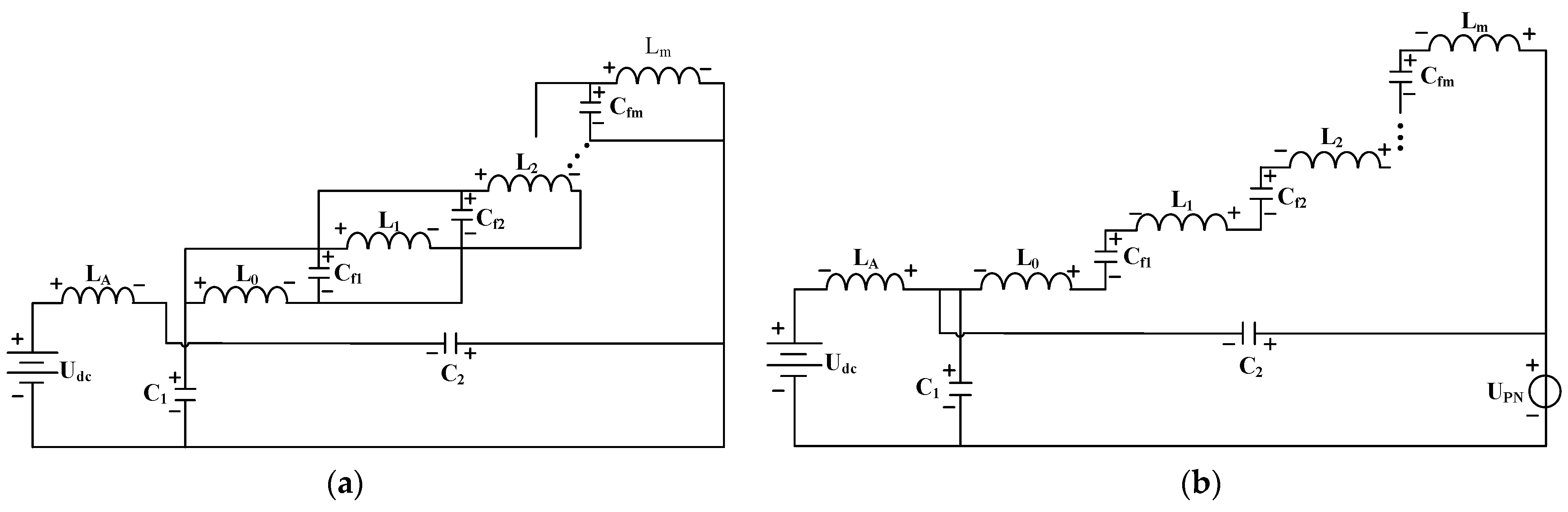

3.1. Multicell Improved-Switched-Inductor Quasi-Z-Source Inverter

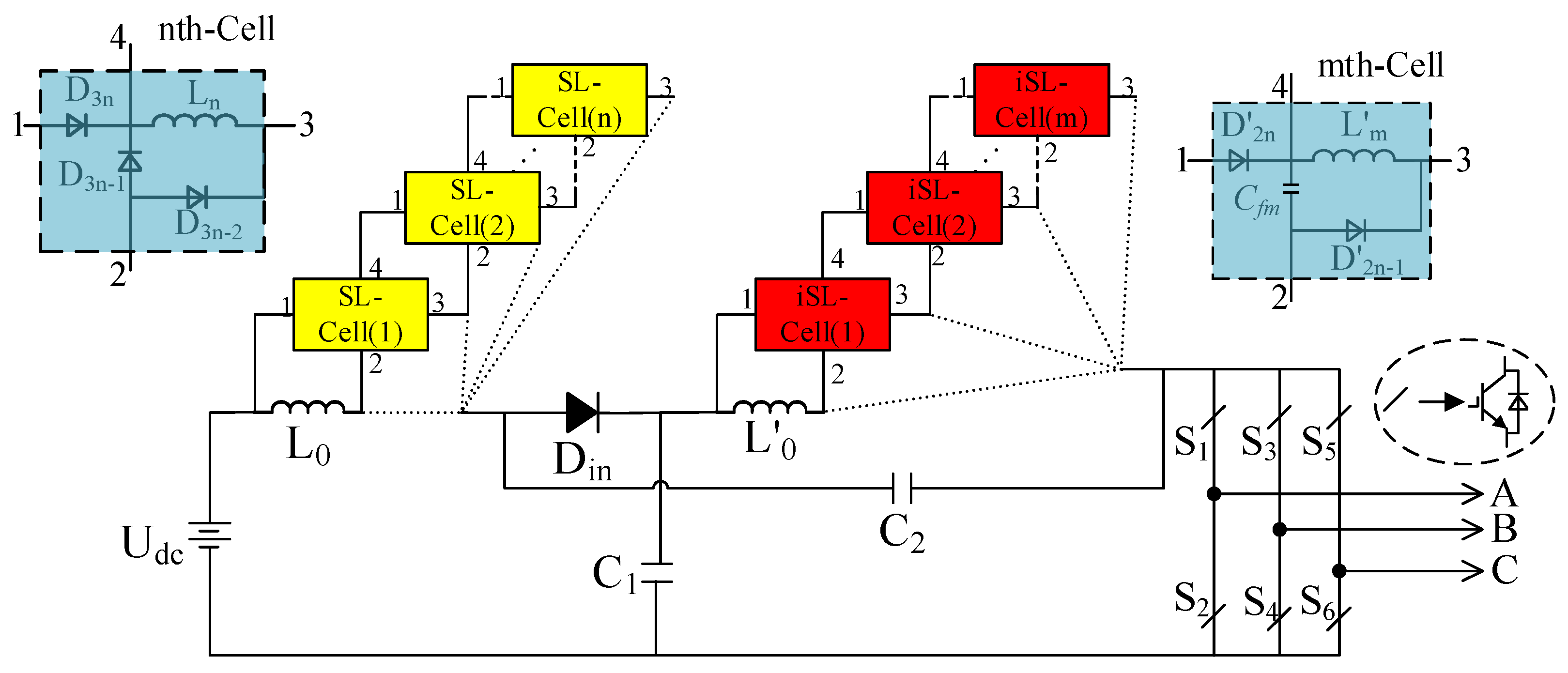

3.2. Hybrid Multicell Switched-Inductor Quasi-Z-Source Inverter

3.3. Comparative Analysis of the Boosting Capacity of Three Types of Inverters

4. Comparative Analysis of the Performance of Inverters of the Same Type

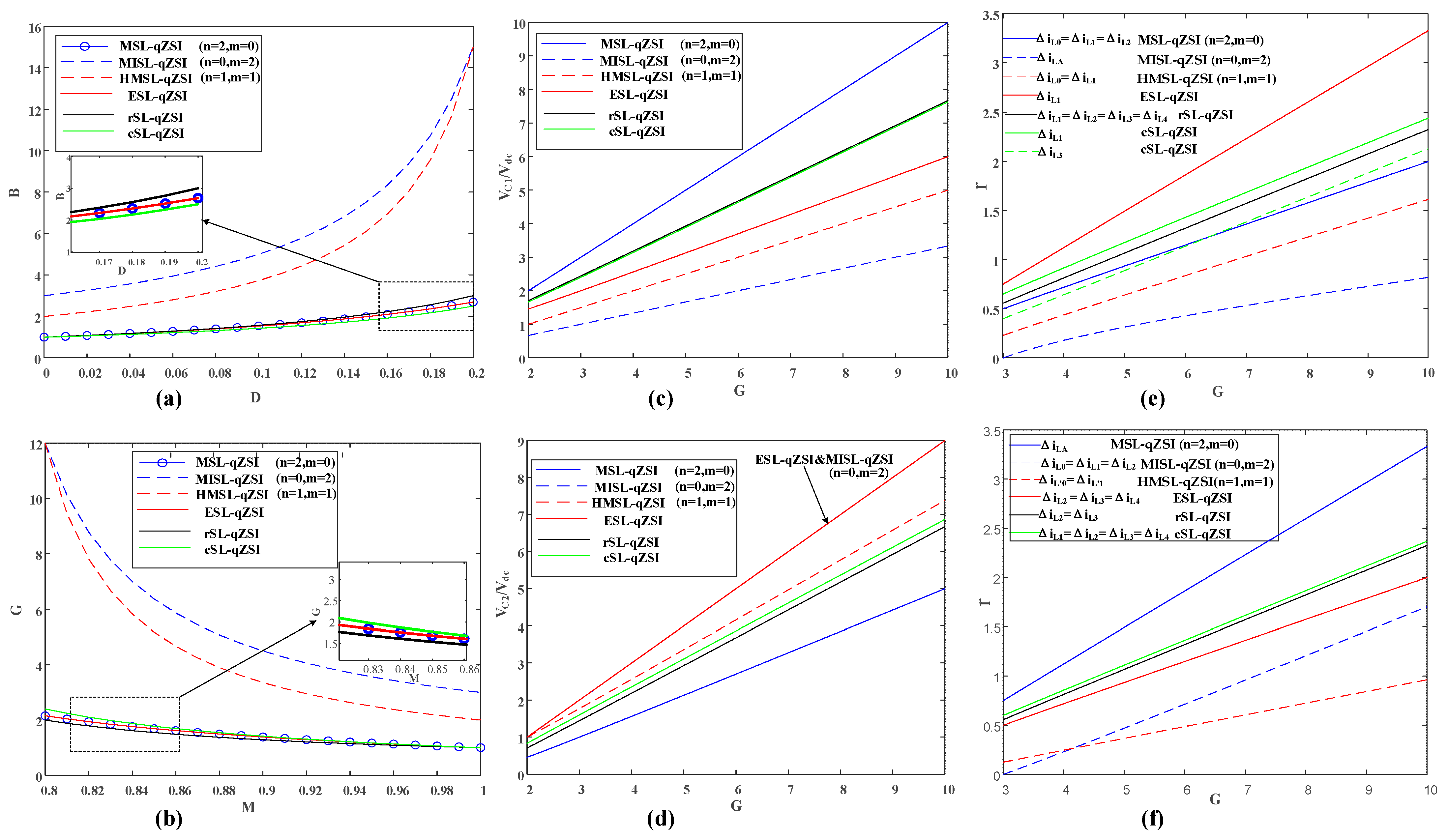

4.1. Boosting Ability

4.2. Voltage Gain

4.3. Capacitor Voltage Stress

4.4. Inductor Current Ripple

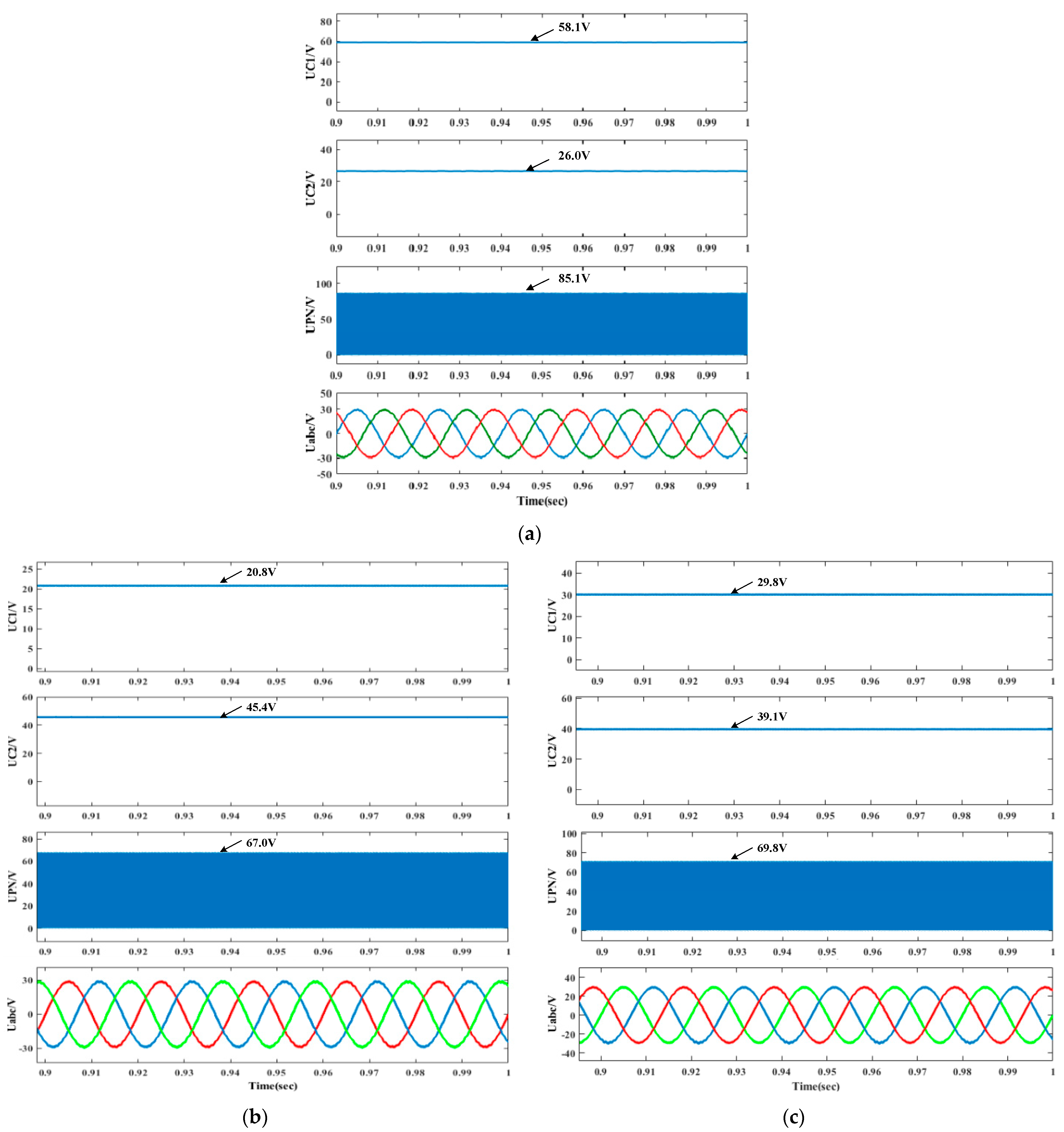

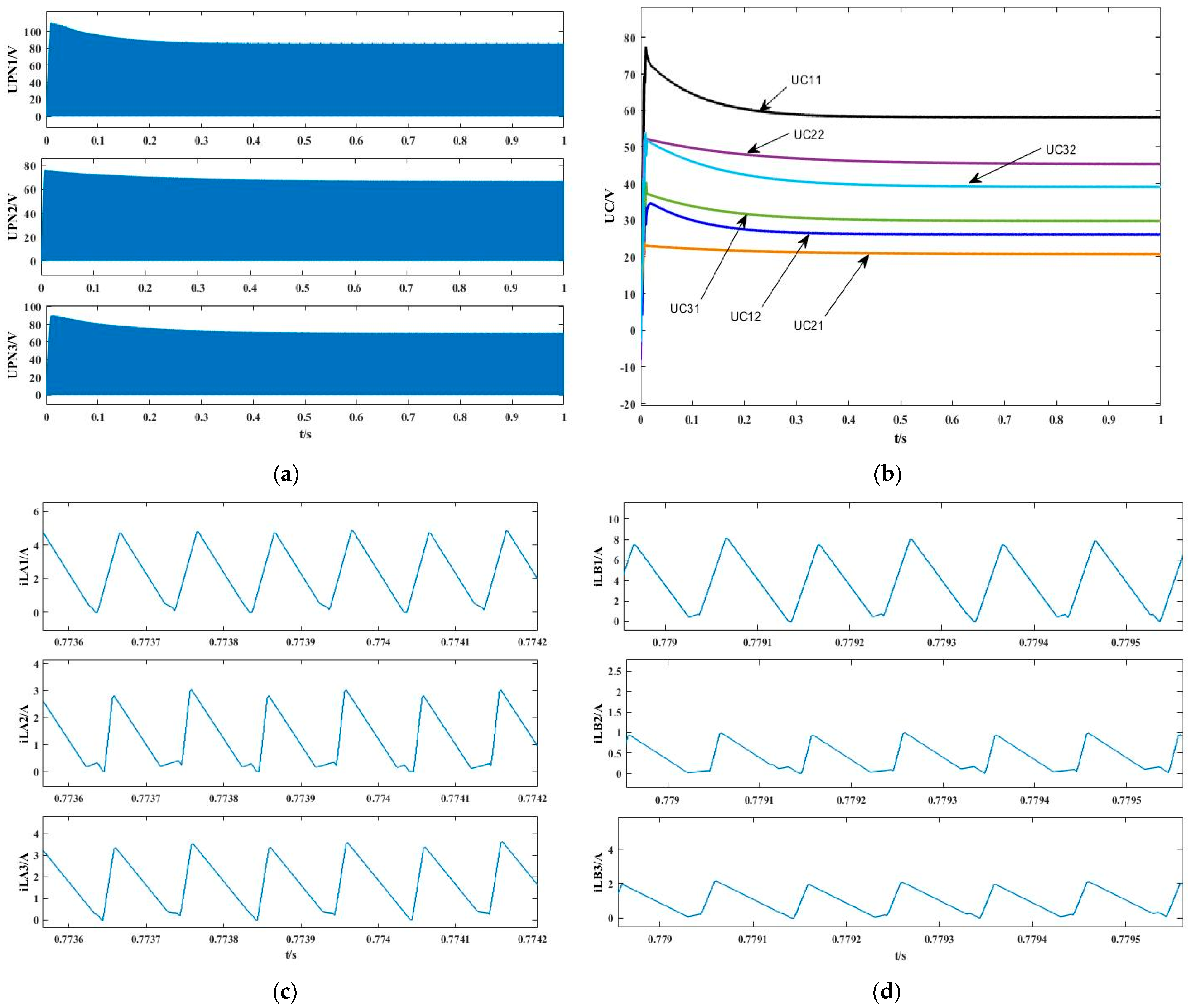

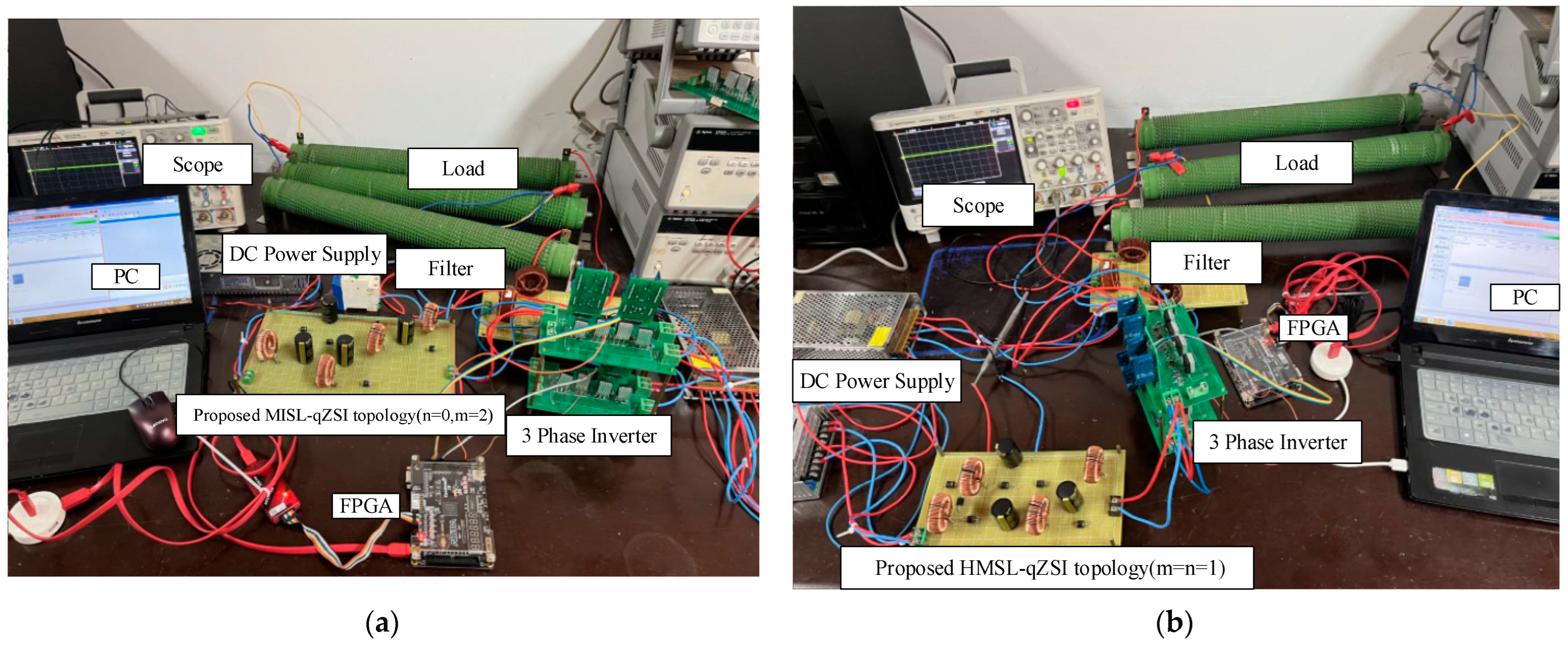

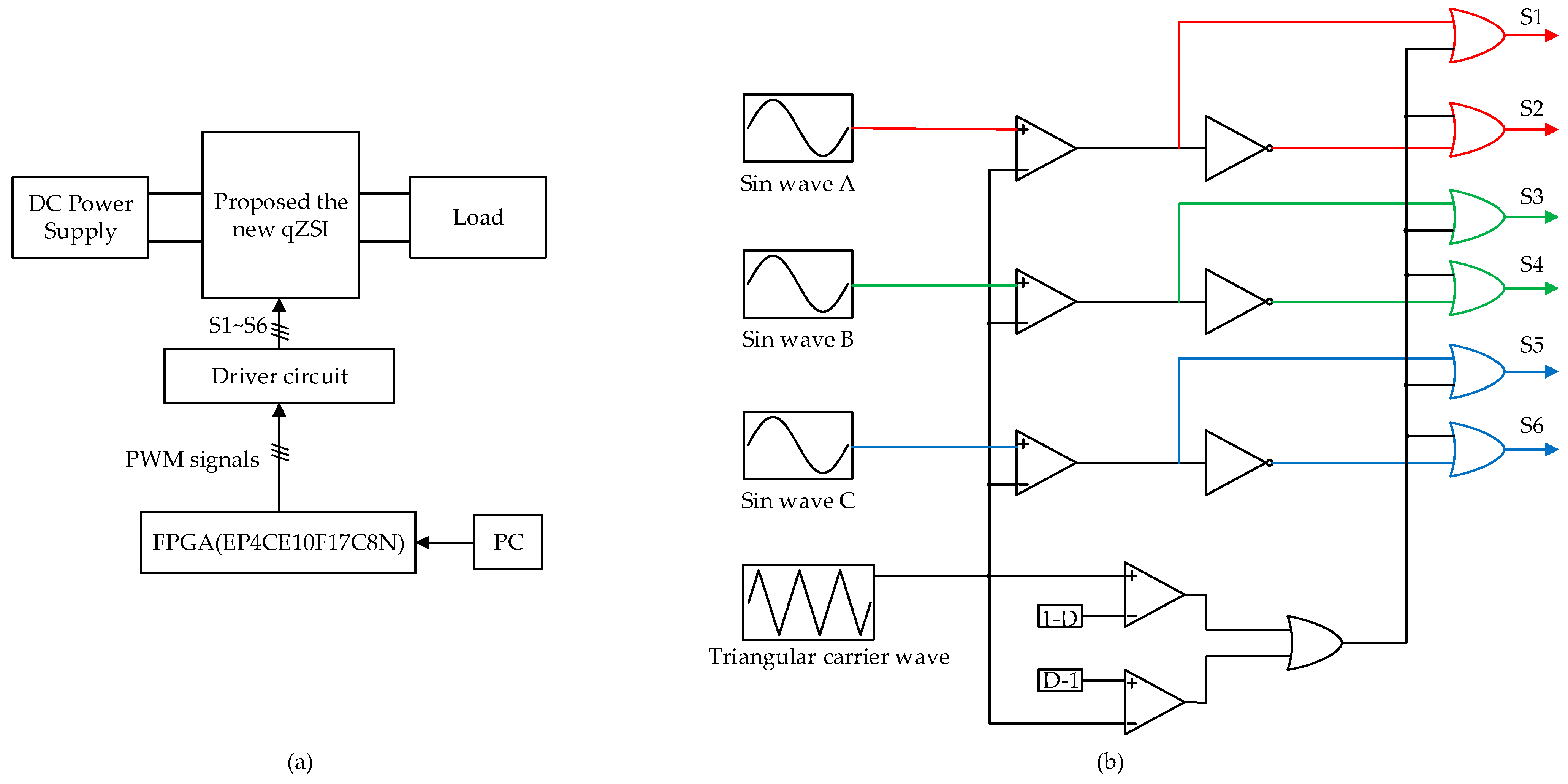

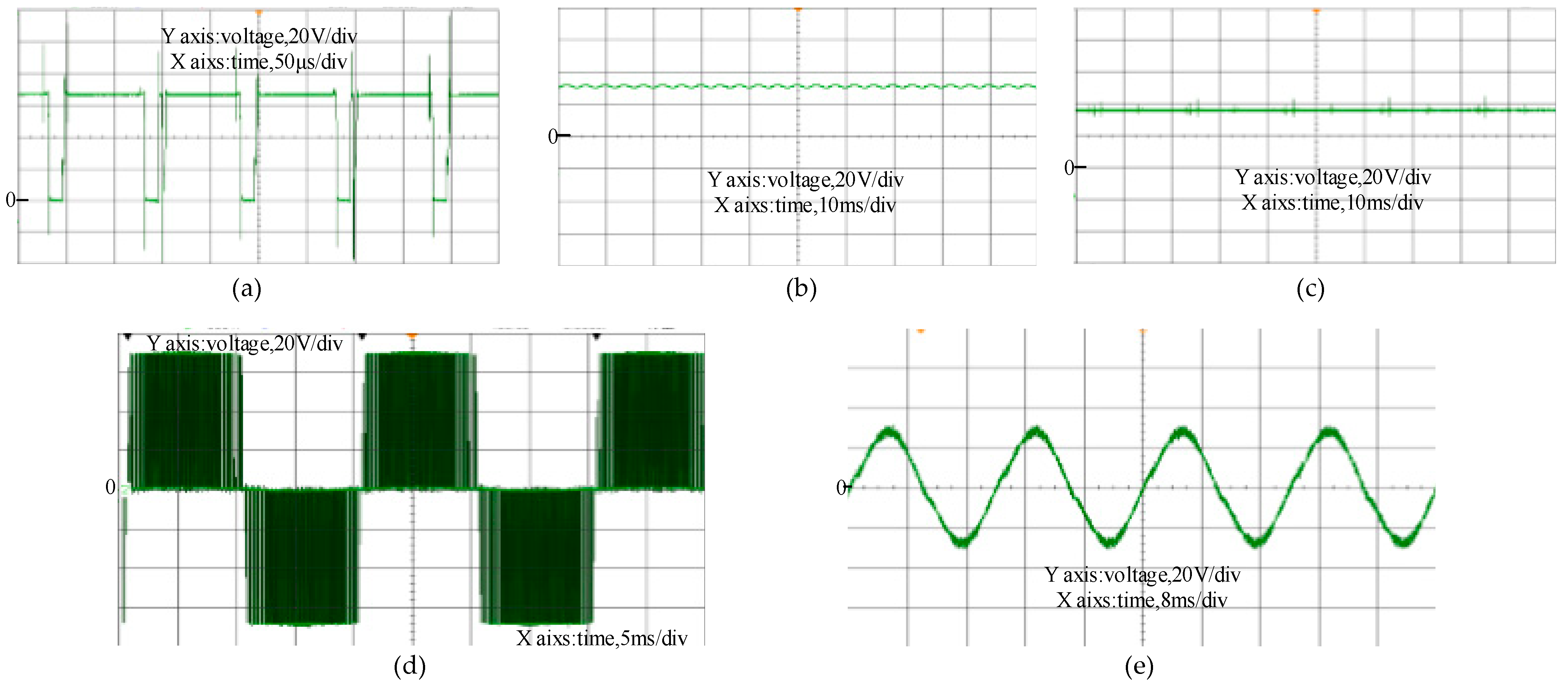

5. Simulation Analysis and Experimental Verification

6. Conclusions

- (1)

- Compared to the conventional quasi-Z-source inverter, the proposed MISL-qZSI and HMSL-qZSI topology have higher boost capability, and its voltage stress across the capacitors and the current ripple through the inductors are effectively reduced.

- (2)

- As the number of cascaded switched-inductor units increases, the boost capability of the new inverter is significantly improved. Therefore, the designers can flexibly select the number of switched-inductor units in the new topologies to meet the requirements of practical applications.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Tripathi, P.R.; Thakura, P.; Keshri, R.K.; Ghosh, S.; Guerrero, J.M. Twenty-Five Years of Single-Stage Buck–Boost Inverters: Development and Challenges. IEEE Ind. Electron. Mag. 2022, 16, 4–10. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, P.C.; Town, G.E. Impedance-Source Networks for Electric Power Conversion Part I: A Topological Review. IEEE Trans. Power Electron. 2015, 30, 699–716. [Google Scholar] [CrossRef]

- Peng, F.Z. Z-Source Inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Anderson, J.; Peng, F.Z. Four Quasi-Z-Source Inverters. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 2743–2749. [Google Scholar]

- Gajanayake, C.J.; Luo, F.L.; Gooi, H.B.; So, P.L.; Siow, L.K. Extended-Boost Z-Source Inverters. IEEE Trans. Power Electron. 2010, 25, 2642–2652. [Google Scholar] [CrossRef]

- Fathi, H.; Madadi, H. Enhanced-Boost Z-Source Inverters with Switched Z-Impedance. IEEE Trans. Ind. Electron. 2016, 63, 691–703. [Google Scholar] [CrossRef]

- Jagan, V.; Kotturu, J.; Das, S. Enhanced-Boost Quasi-Z-Source Inverters with Two-Switched Impedance Networks. IEEE Trans. Ind. Electron. 2017, 64, 6885–6897. [Google Scholar] [CrossRef]

- Zhu, M.; Yu, K.; Luo, F.L. Switched Inductor Z-Source Inverter. IEEE Trans. Power Electron. 2010, 25, 2150–2158. [Google Scholar]

- Nguyen, M.-K.; Lim, Y.-C.; Cho, G.-B. Switched-Inductor Quasi-Z-Source Inverter. IEEE Trans. Power Electron. 2011, 26, 3183–3191. [Google Scholar] [CrossRef]

- Deng, K.; Zheng, J.; Mei, J. Novel Switched-Inductor Quasi-Z-Source Inverter. J. Power Electron. 2014, 14, 11–21. [Google Scholar] [CrossRef]

- Lim, Y.-C.; Nguyen, M.-K.; Choi, J.-H. Two Switched-Inductor Quasi-Z-Source Inverters. IET Power Electron. 2012, 5, 1017–1025. [Google Scholar]

- Ho, A.-V.; Chun, T.-W.; Kim, H.-G. Extended Boost Active-Switched-Capacitor/Switched-Inductor Quasi-Z-Source Inverters. IEEE Trans. Power Electron. 2015, 30, 5681–5690. [Google Scholar] [CrossRef]

- Masoud, G.; Seyed Masoud, B.; Bin, W. Extended Switched-Inductor Quasi-Z-Source Inverter: Modeling and Prototype Realization. Int. Trans. Electr. Energy Syst. 2019, 29, e2744. [Google Scholar]

- Abbasi Bolaghi, J.; Taheri, A.; Babaei, M.H.; Gholami, M. Quasi Z-Source Inverter with Switched-Capacitor-Inductor for Enhancing Boost Factor. IET Power Electron. 2021, 14, 2545–2562. [Google Scholar] [CrossRef]

- Qian, W.; Peng, F.Z.; Cha, H. Trans-Z-Source Inverters. IEEE Trans. Power Electron. 2011, 26, 3453–3463. [Google Scholar] [CrossRef]

- Loh, P.C.; Li, D.; Blaabjerg, F. Γ-Z-Source Inverters. IEEE Trans. Power Electron. 2013, 28, 4880–4884. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Loh, P.C.; Blaabjerg, F.; Town, G.E. Y-Source Impedance Network. IEEE Trans. Power Electron. 2014, 29, 3250–3254. [Google Scholar] [CrossRef]

- Tang, Y.; Sun, H.; Wang, S. A Family of High Step-Up Quasi Z-Source Inverters with Coupled Inductor. Energies 2020, 13, 5667. [Google Scholar] [CrossRef]

- Sharifi, S.; Chulaee, Y.; Zarchi, H.A.; Monfared, M. Generalized Three-Winding Switched-Coupled-Inductor Impedance Networks with Highly Flexible Gain. IEEE Trans. Ind. Electron. 2021, 68, 2130–2141. [Google Scholar] [CrossRef]

- Ji, Y.; Geng, L.; Li, F.; Liu, H.; Wheeler, P. An Enhanced-Boost Coupled-Inductor Impedance Network Inverter Without Limitation of Inductor Parameters. IEEE Trans. Transp. Electrif. 2022, 8, 699–709. [Google Scholar] [CrossRef]

- Tang, Y.; Wang, T.; Fu, D. Multicell Switched-Inductor/Switched-Capacitor Combined Active-Network Converters. IEEE Trans. Power Electron. 2015, 30, 2063–2072. [Google Scholar] [CrossRef]

- Li, D.; Loh, P.C.; Zhu, M.; Gao, F.; Blaabjerg, F. Generalized Multicell Switched-Inductor and Switched-Capacitor Z-Source Inverters. IEEE Trans. Power Electron. 2013, 28, 837–848. [Google Scholar] [CrossRef]

- Majeed, R.; Chughtai, A.H. Multicell Schemes for Active-Switched-Capacitor and Active-Switched-Capacitor/Switched- Inductor Quasi-Z-Source Inverters. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 1739–1754. [Google Scholar] [CrossRef]

- Cheng, Z.; Cheng, J.; Yu, H.; Ye, S.; Zhang, Z. Switched-inductor quasi-Z -source inverter based on multi-cascaded. J. Anhui Univ. Nat. Sci. 2013, 37, 48–56. [Google Scholar]

- Barath, J.N.; Soundarrajan, A.; Stepenko, S.; Husev, O.; Vinnikov, D.; Nguyen, M.-K. Topological Review of Quasi-Switched Boost Inverters. Electronics 2021, 10, 1485. [Google Scholar] [CrossRef]

| Topology Type | MSL-qZSI (m = 0) | MISL-qZSI (n = 0) | HMSL-qZSI (m, n ≠ 0) | |

|---|---|---|---|---|

| Num of SL Units | ||||

| 1 | / | |||

| 2 | ||||

| 3 | (m = 2, n = 1) (m = 1, n = 2) | |||

| 4 | (m = 2, n = 2) | |||

| Parameters | MSL-qZSI (n = 2, m = 0) | MISL-qZSI (n = 0, m = 2) | HMSL-qZSI (n = 1, m = 1) | ESL-qZSI [10] | rSL-qZSI [11] | cSL-qZSI [11] |

|---|---|---|---|---|---|---|

| Number of L | 4 | 4 | 4 | 4 | 4 | 4 |

| Number of C | 2 | 4 | 3 | 2 | 2 | 2 |

| Number of D | 7 | 5 | 6 | 7 | 7 | 7 |

| Total | 13 | 13 | 13 | 13 | 13 | 13 |

| Parameters | B | G | D | VC | ΔI |

| MSL-qZSI (n = 2, m = 0) | |||||

| MISL-qZSI (n = 0, m = 2) | |||||

| HMSL-qZSI (n = 1, m = 1) | |||||

| Esl-qZSI [7] | |||||

| rsl-qZSI [11] | |||||

| csl-qZSI [11] |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| DC voltage sources Udc/V | 12 | Modulation index M0 | 0.70127 |

| Carrier frequency fc/kHZ | 5 | Shoot-through duty ratio D0 | 0.29873 |

| Output frequency f0/HZ | 50 | Modulation index M1 | 0.88235 |

| Inductors L/μH | 220 | Shoot-through duty ratio D1 | 0.11765 |

| Capacitors C/μF | 1000 | Modulation index M2 | 0.85323 |

| Filter inductors Lf/mH | 1 | Shoot-through duty ratio D2 | 0.14677 |

| Filter capacitors Cf/μF | 20 | Overall voltage gain G = M × B | 5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gong, R.; Tang, J.; Wan, X.; Wu, H. New Multicell Switched-Inductor Quasi-Z-Source Inverter. Electronics 2023, 12, 3814. https://doi.org/10.3390/electronics12183814

Gong R, Tang J, Wan X, Wu H. New Multicell Switched-Inductor Quasi-Z-Source Inverter. Electronics. 2023; 12(18):3814. https://doi.org/10.3390/electronics12183814

Chicago/Turabian StyleGong, Renxi, Jing Tang, Xingyuan Wan, and Hao Wu. 2023. "New Multicell Switched-Inductor Quasi-Z-Source Inverter" Electronics 12, no. 18: 3814. https://doi.org/10.3390/electronics12183814

APA StyleGong, R., Tang, J., Wan, X., & Wu, H. (2023). New Multicell Switched-Inductor Quasi-Z-Source Inverter. Electronics, 12(18), 3814. https://doi.org/10.3390/electronics12183814