Research on High-Dose-Rate Transient Ionizing Radiation Effect in Nano-Scale FDSOI Flip-Flops

Abstract

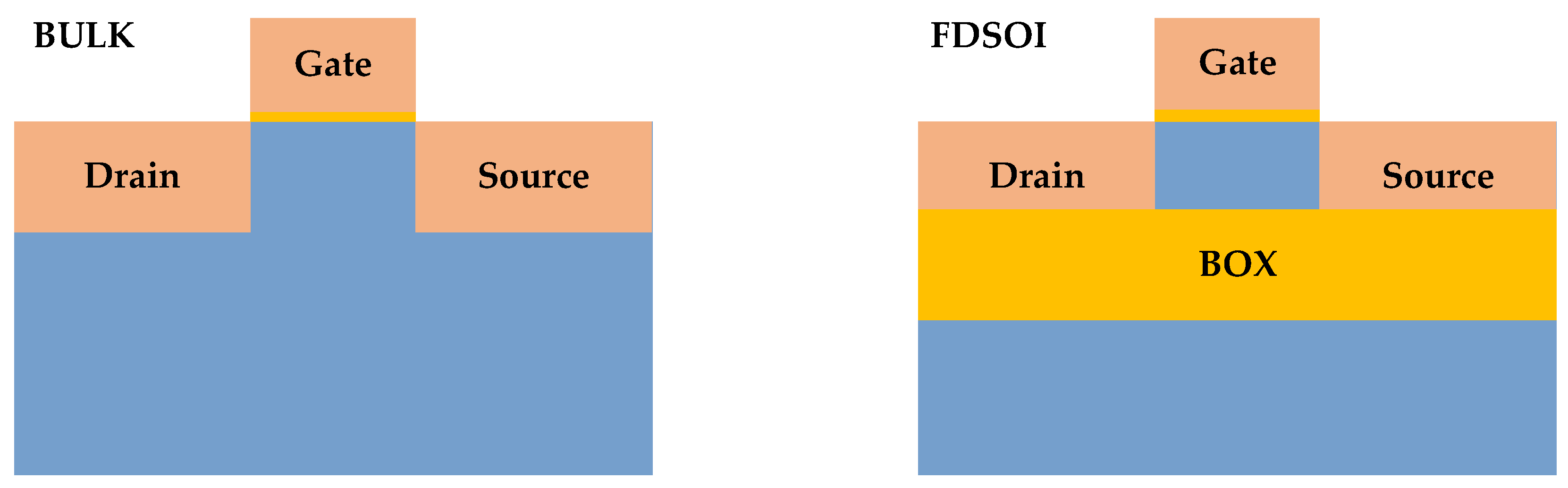

1. Introduction

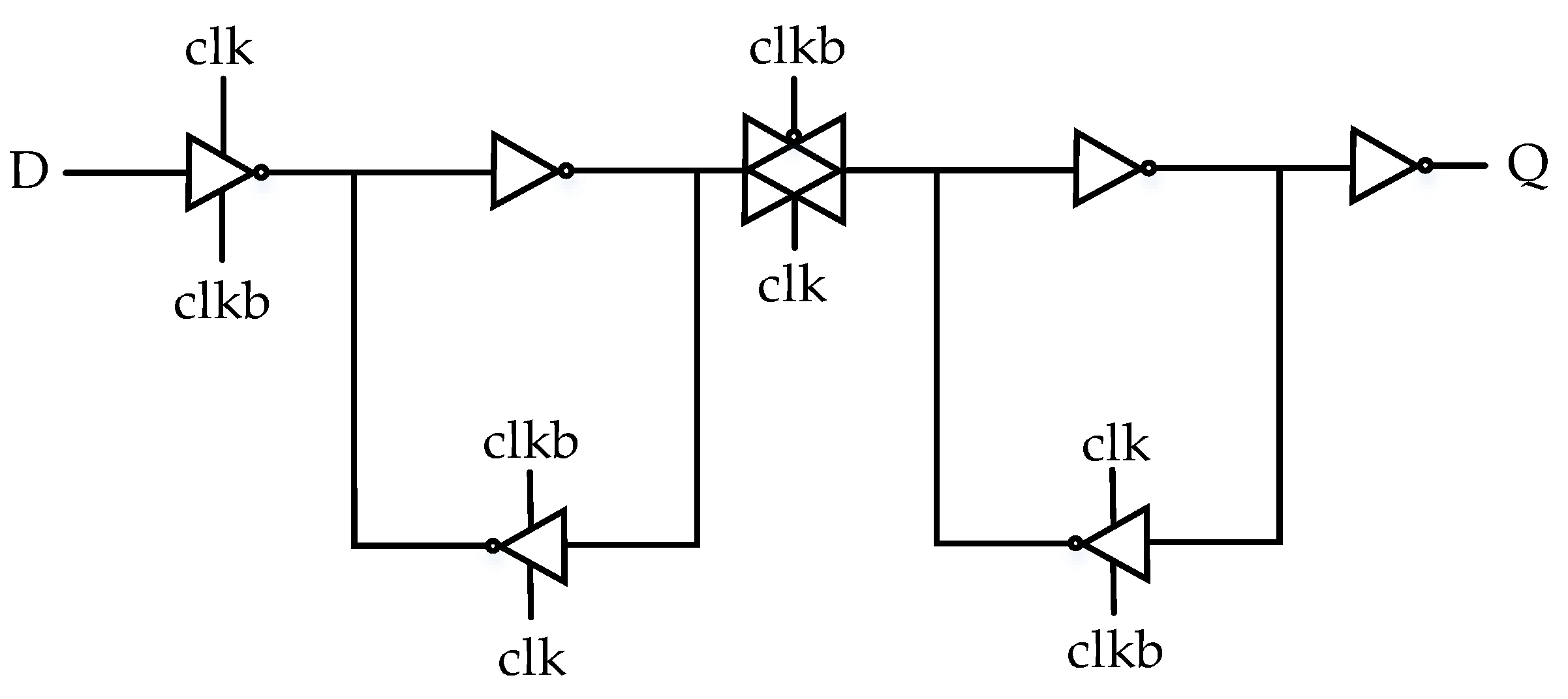

2. Circuit Samples

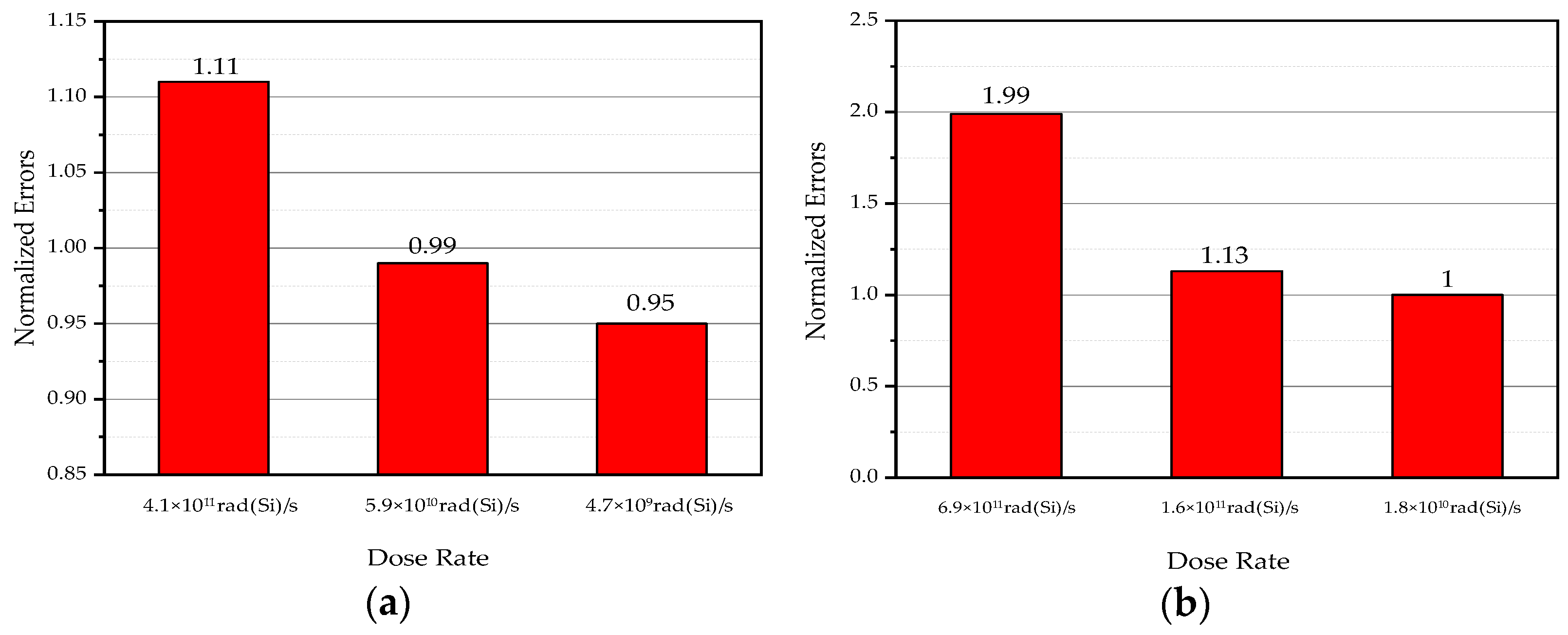

3. Radiation Experiments

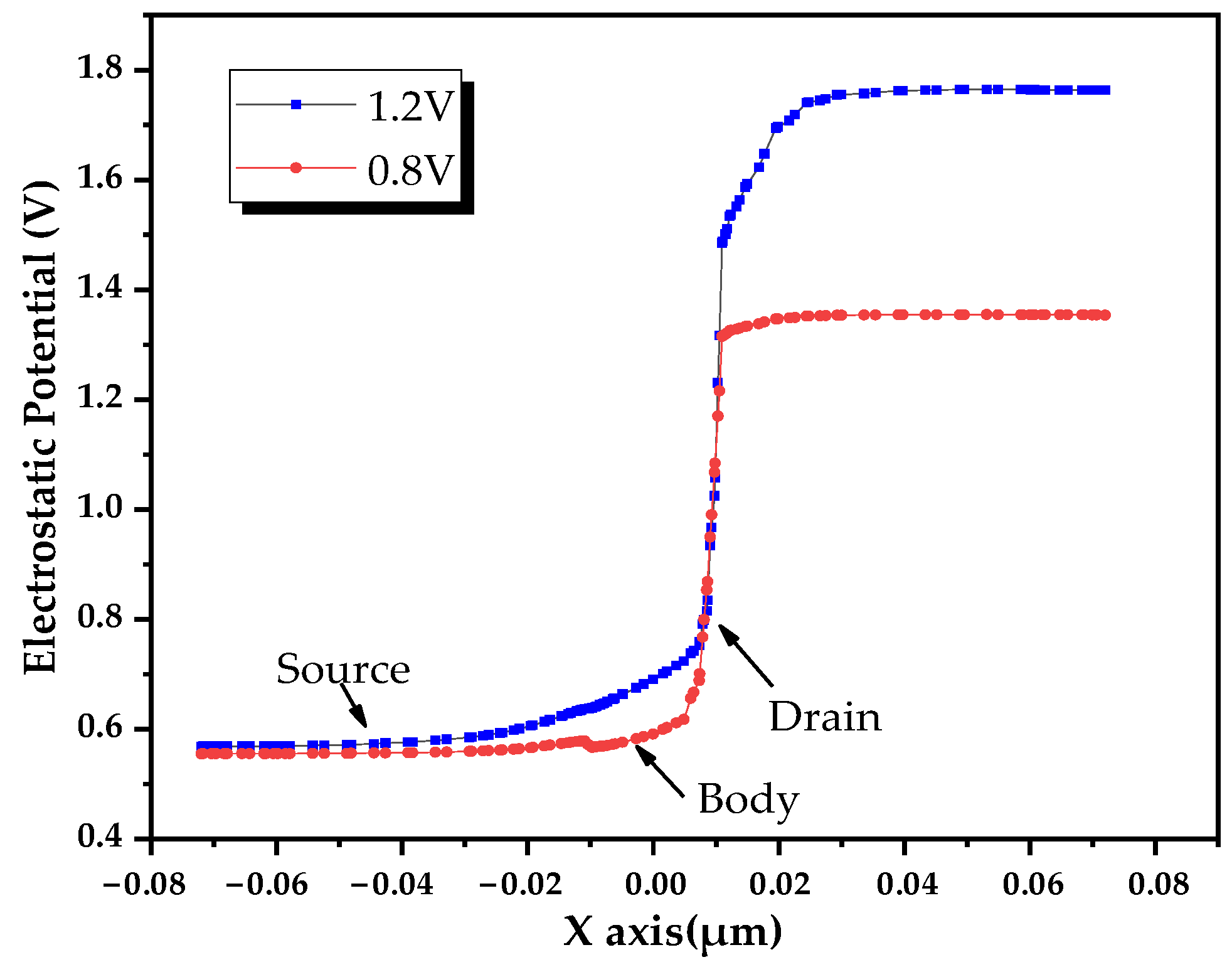

4. Experimental Analysis and Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Hu, C.; He, C. Numerical Simulation of Neutron Irradiation in Ultra-Deep Submicron SOI NMOSFETs. At. Energy Sci. Technol. 2011, 45, 456–460. [Google Scholar]

- Xue, H.; Zhang, M. Numerical Simulation of Transient Dose Rate Effects in NMOS Devices with Deep Submicron SOI process. Appl. Electron. Technol. 2019, 45, 59–61. [Google Scholar]

- Niu, Z.; Tu, Y. Research on Neutron Irradiation Effect of Computer Based on DSP. In Proceedings of the 10th Annual National Conference on Radiation Resistant Electronics and Electromagnetic Pulse, Shenyang, China, 1 July 2009; pp. 97–102. [Google Scholar]

- Liu, W. Radiation Effects of Silicon Semiconductor Devices and Reinforcement Techniques, 1st ed.; Beijing Science Press: Beijing, China, 2013; pp. 132–136. [Google Scholar]

- Ellis, T.D.; Kim, Y.D. Use of a Pulsed Laser as an Aid to Transient Upset Testing of 12L LSI Microcircuits. IEEE Trans. Nucl. Sci. 1978, 25, 1489–1493. [Google Scholar] [CrossRef]

- Weber, O. FDSOI vs FinFET: Differentiating Device Features for Ultra Low Power & IoT applications. In Proceedings of the 2017 IEEE International Conference on IC Design and Technology (ICICDT), Austin, TX, USA, 23–25 May 2017; pp. 1–3. [Google Scholar]

- Luo, H. SOI Devices and Applications. Electron. Packag. 2007, 7, 41–45. [Google Scholar]

- Perin, L.; Pereira, A. SOI Stacked Transistors Tolerance to Single-Event Effects. IEEE Trans. Device Mater. Reliab. 2019, 19, 393–401. [Google Scholar] [CrossRef]

- Heidel, A. Single-Event Upsets and Multiple-Bit Upsets on a 45 nm SOI SRAM. IEEE Trans. Nucl. Sci. 2009, 56, 3499–3504. [Google Scholar] [CrossRef]

- Elesin, V.; Nazarova, G. Investigation of the Possibility to Develop Radiation-Hardness LSIs for Navigational Purposes According to the 0.35-μm Domestic CMOS SOI Technology. Russ. Microelectron. 2012, 41, 266–277. [Google Scholar] [CrossRef]

- Zhang, Z.; Liu, J. Investigation of Threshold Ion Range for Accurate Single Event Upset Measurements in Both SOI and Bulk Technologies. IEEE Trans. Nucl. Sci. 2014, 61, 1459–1467. [Google Scholar] [CrossRef]

- Raine, M.; Gaillardin, M. Experimental Evidence of Large Dispersion of Deposited Energy in Thin Active Layer Devices. IEEE Trans. Nucl. Sci. 2011, 58, 2664–2672. [Google Scholar] [CrossRef]

- Wirth, J.; Rogers, S. The Transient Response of Transistors and Diodes to Ionizing Radiation. IEEE Trans. Nucl. Sci. 1964, 11, 24–38. [Google Scholar] [CrossRef]

- Palkuti, L.; Alles, M. The Role of Radiation Effects in SOI Technology Development. In Proceedings of the 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Millbrae, CA, USA, 6–9 October 2014; pp. 1–2. [Google Scholar]

- Schwank, J.; Ferlet, V. Radiation Effects in SOI Technologies. IEEE Trans. Nucl. Sci. 2003, 50, 522–538. [Google Scholar] [CrossRef]

- Zhang, Z.; Zou, S. Radiation Hardening Technology of SOI Materials and Devices. Chin. Sci. Bull. 2017, 62, 1004–1017. [Google Scholar] [CrossRef]

- Ferlet, V.; Gasiot, G. Insights on the Transient Response of Fully and Partially Depleted SOI Technologies Under Heavy-ion and Dose-Rate Irradiations. IEEE Trans. Nucl. Sci. 2002, 49, 2948–2956. [Google Scholar] [CrossRef]

- Nazarova, G.; Elesin, V. Long-Term Transient Radiation Effects in SOI CMOS RF ICs. In Proceedings of the 2015 15th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Moscow, Russia, 14–18 September 2015; pp. 1–4. [Google Scholar]

- Wu, L.; Han, X. Radiation-hardened SOI Process Design and FPGA. Inf. Electron. Eng. 2012, 10, 627–632. [Google Scholar]

- Zhao, K.; Liu, Z. Resist Radiation 128 KB PDSO1 Static Random Access Memory. J. Semicond. 2007, 7, 1139–1143. [Google Scholar]

- Ball, D.; Alles, M. The Impact of Charge Collection Volume and Parasitic Capacitance on SEUs in SOI- and Bulk-FinFET D Flip-Flops. IEEE Trans. Nucl. Sci. 2018, 65, 326–330. [Google Scholar] [CrossRef]

- Liu, H.; Golke, K. A New Dose Rate Model for SOI MOSFETs and Its Implementation in SPICE. In Proceedings of the 2005 IEEE International SOI Conference Proceedings, Honolulu, HI, USA, 3–6 October 2005; pp. 112–113. [Google Scholar]

- Kauppila, J.; Kay, W. Single-Event Upset Characterization Across Temperature and Supply Voltage for a 20-nm Bulk Planar CMOS Technology. IEEE Trans. Nucl. Sci. 2015, 62, 2613–2619. [Google Scholar] [CrossRef]

- Li, T.; Zhao, Y. Investigation on Transient Ionizing Radiation Effects in a 4-Mb SRAM with Dual Supply Voltages. IEEE Trans. Nucl. Sci. 2022, 69, 340–348. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, T.; Yuan, J.; Bai, Y.; Yu, C.; Gou, C.; Shu, L.; Wang, L.; Zhao, Y. Research on High-Dose-Rate Transient Ionizing Radiation Effect in Nano-Scale FDSOI Flip-Flops. Electronics 2023, 12, 3149. https://doi.org/10.3390/electronics12143149

Li T, Yuan J, Bai Y, Yu C, Gou C, Shu L, Wang L, Zhao Y. Research on High-Dose-Rate Transient Ionizing Radiation Effect in Nano-Scale FDSOI Flip-Flops. Electronics. 2023; 12(14):3149. https://doi.org/10.3390/electronics12143149

Chicago/Turabian StyleLi, Tongde, Jingshuang Yuan, Yang Bai, Chunqing Yu, Chunliang Gou, Lei Shu, Liang Wang, and Yuanfu Zhao. 2023. "Research on High-Dose-Rate Transient Ionizing Radiation Effect in Nano-Scale FDSOI Flip-Flops" Electronics 12, no. 14: 3149. https://doi.org/10.3390/electronics12143149

APA StyleLi, T., Yuan, J., Bai, Y., Yu, C., Gou, C., Shu, L., Wang, L., & Zhao, Y. (2023). Research on High-Dose-Rate Transient Ionizing Radiation Effect in Nano-Scale FDSOI Flip-Flops. Electronics, 12(14), 3149. https://doi.org/10.3390/electronics12143149