Leakage Current Stability Analysis for Subthreshold SRAM

Abstract

:1. Introduction

2. Methods

2.1. Impact of Leakage Current on SRAM

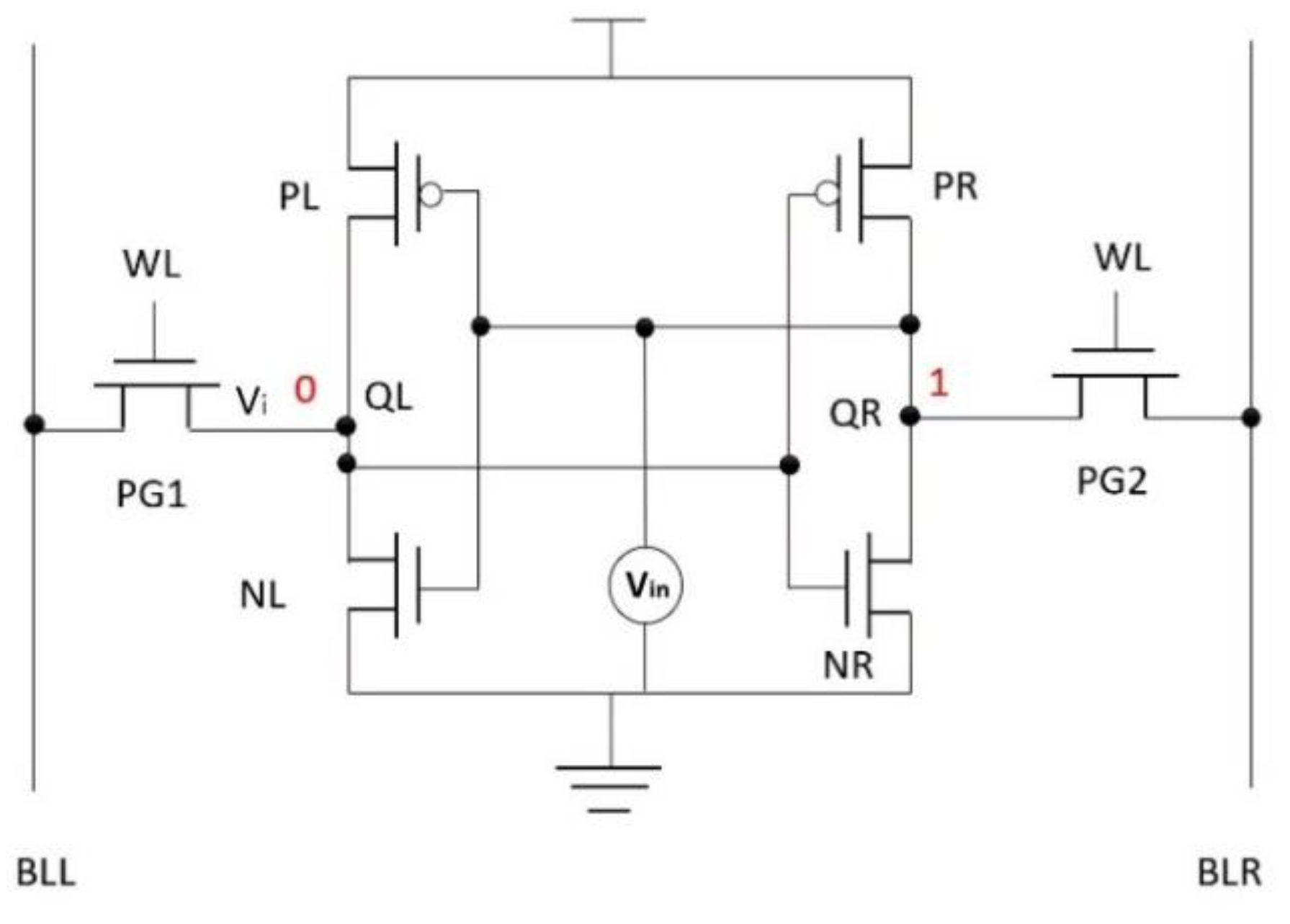

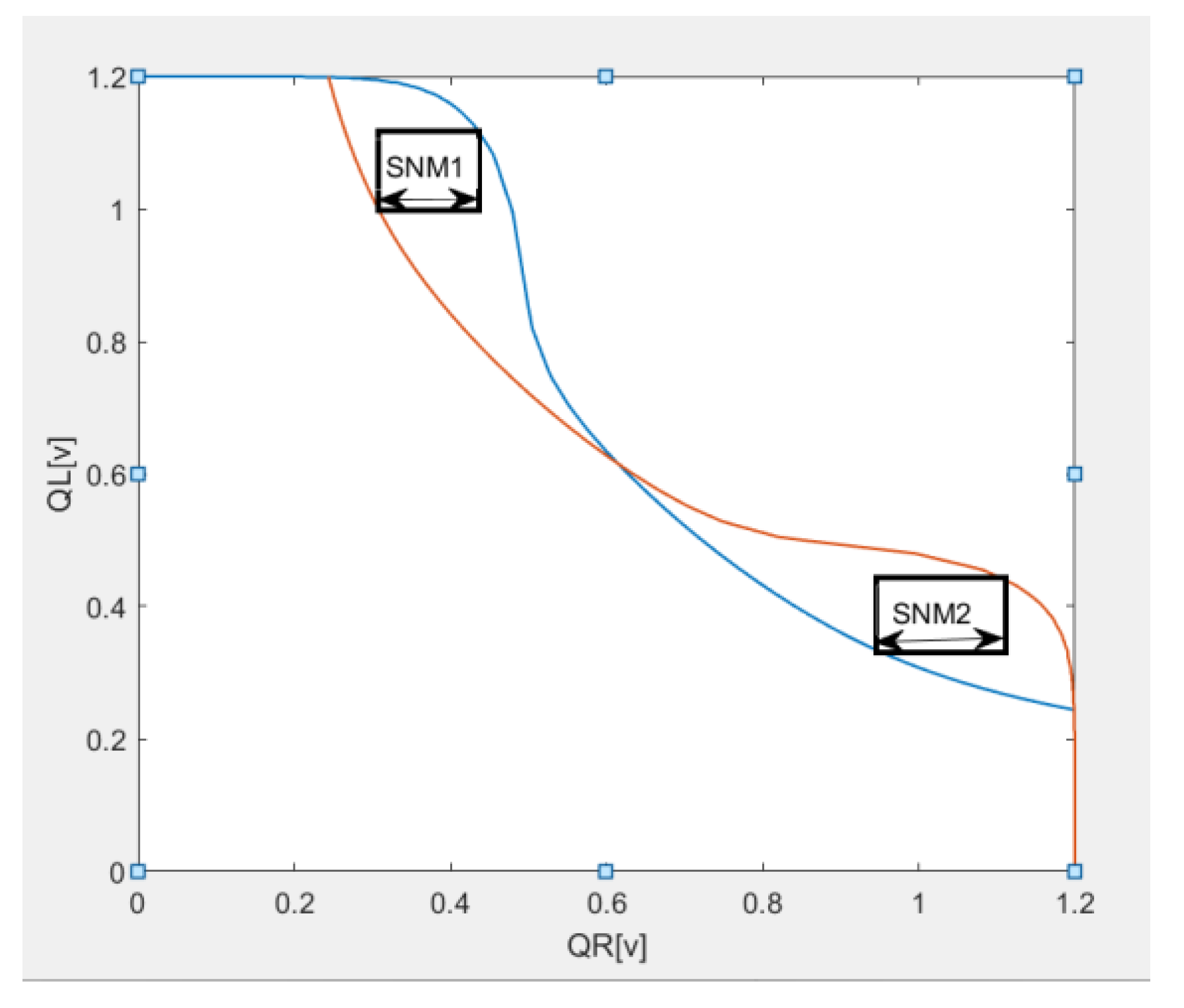

2.2. Conventional Static Stability Analysis Methods

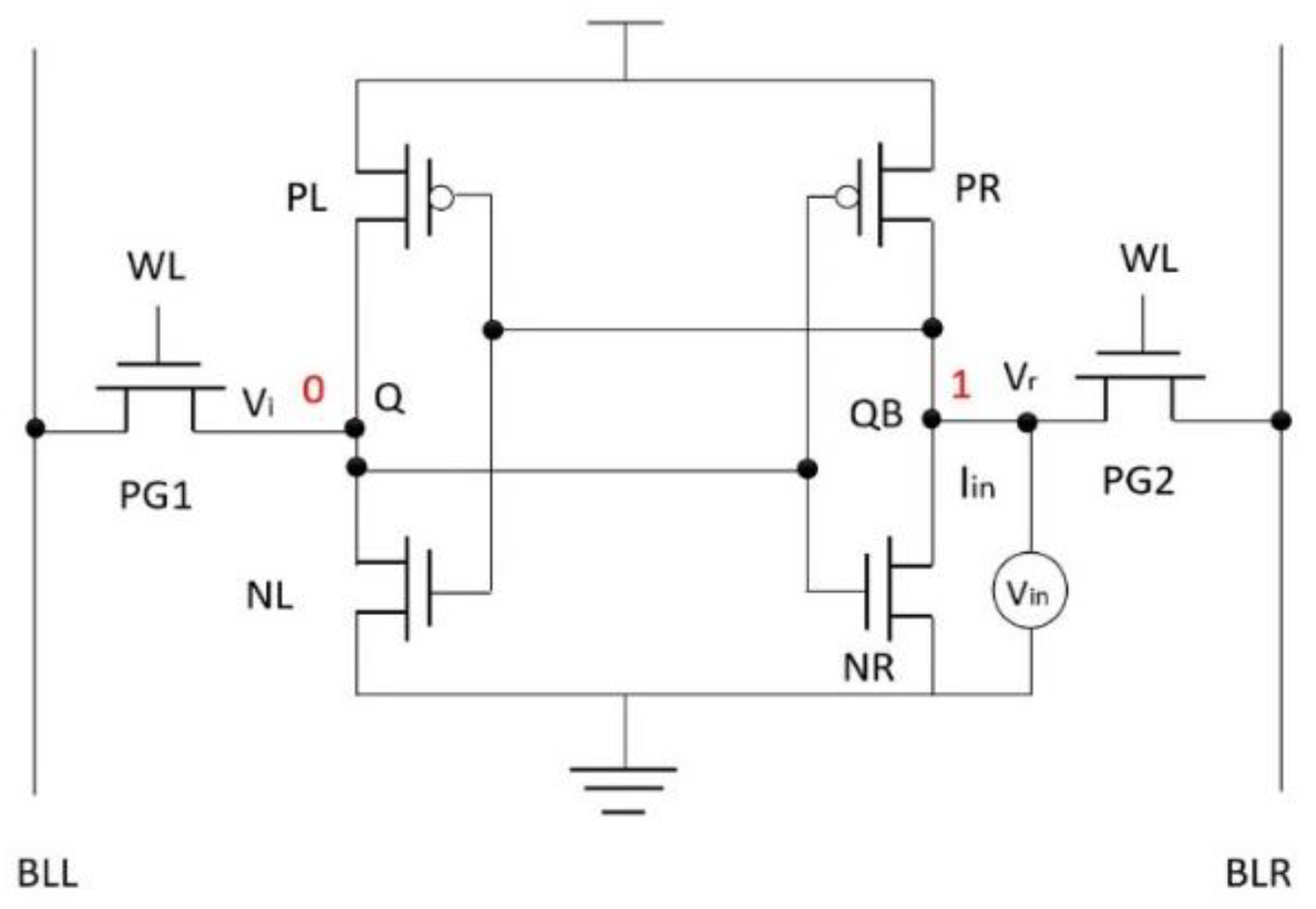

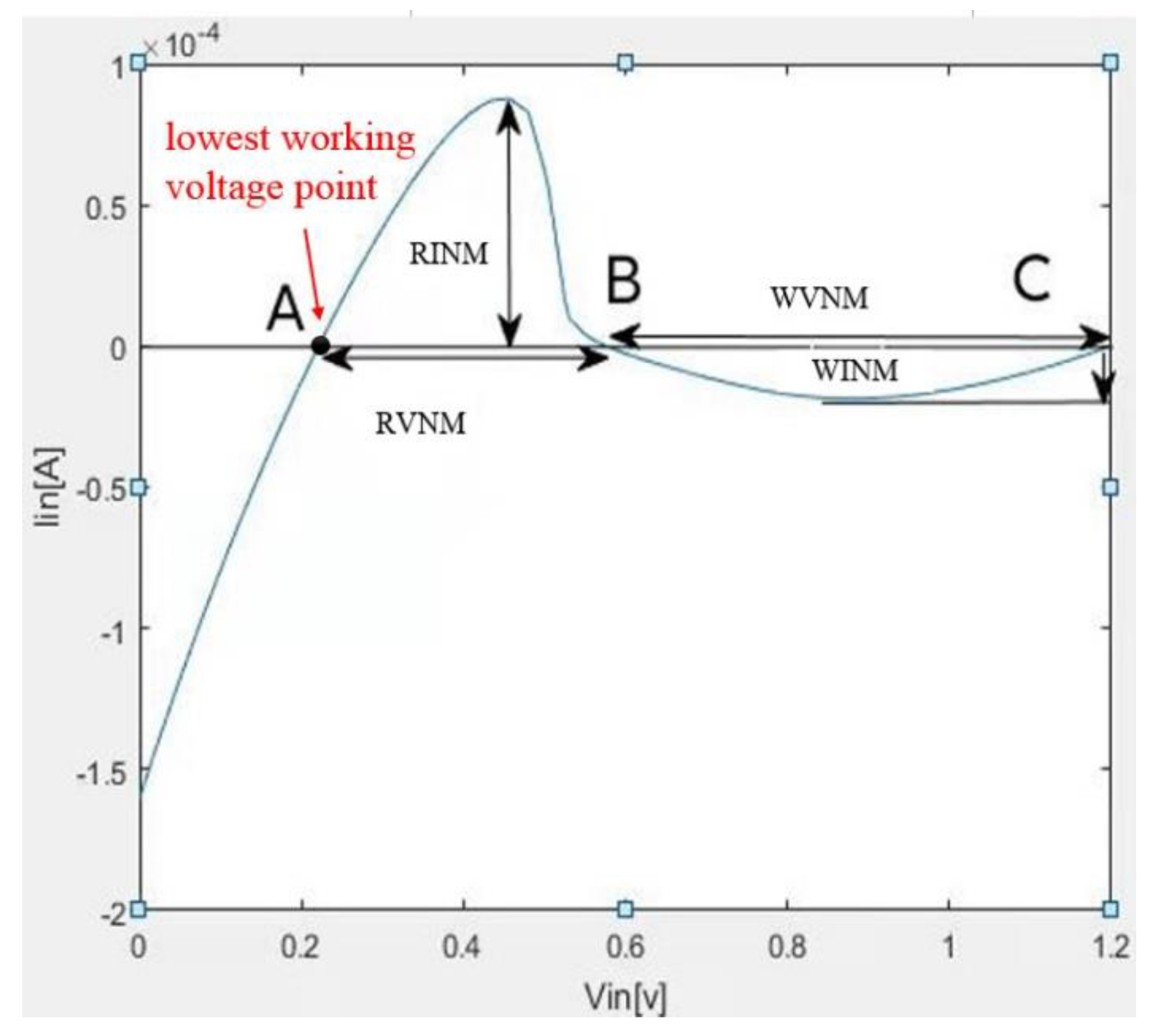

2.3. Leakage-Current-Based Stability Analysis Methods

2.4. Advantages of Leakage-Current-Based Stability

3. Results and Discussion

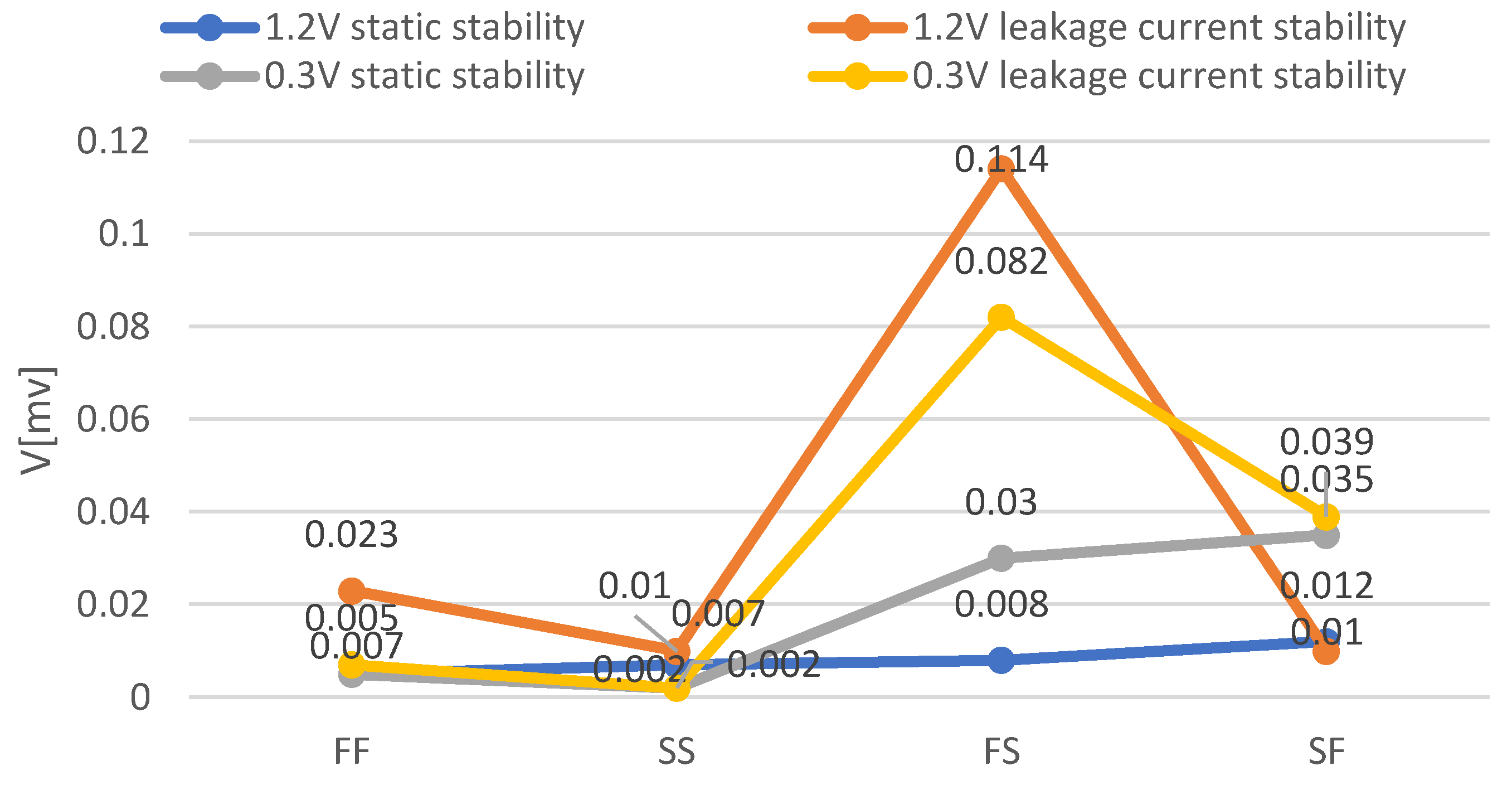

3.1. Different Process Corners in Same Design

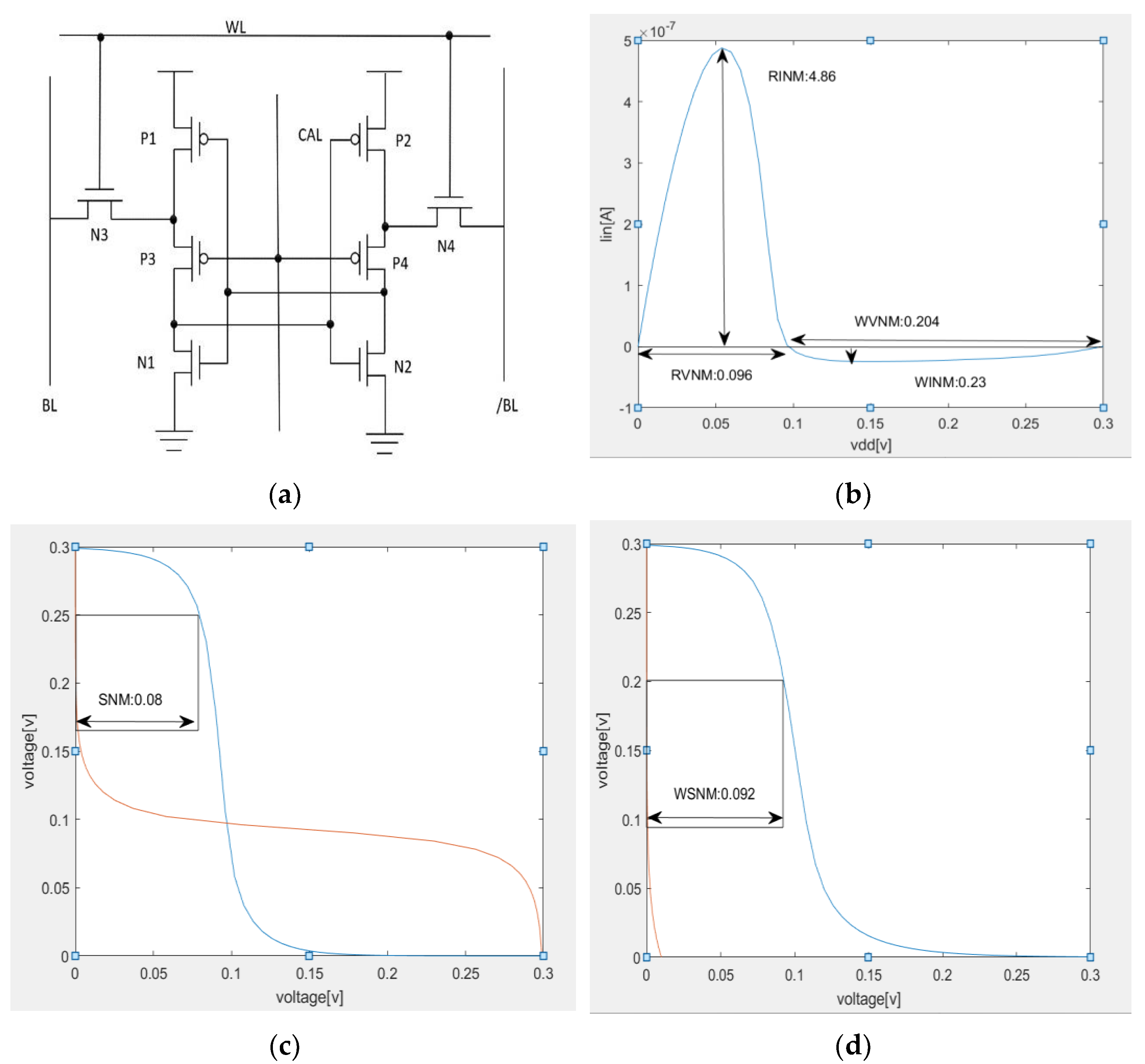

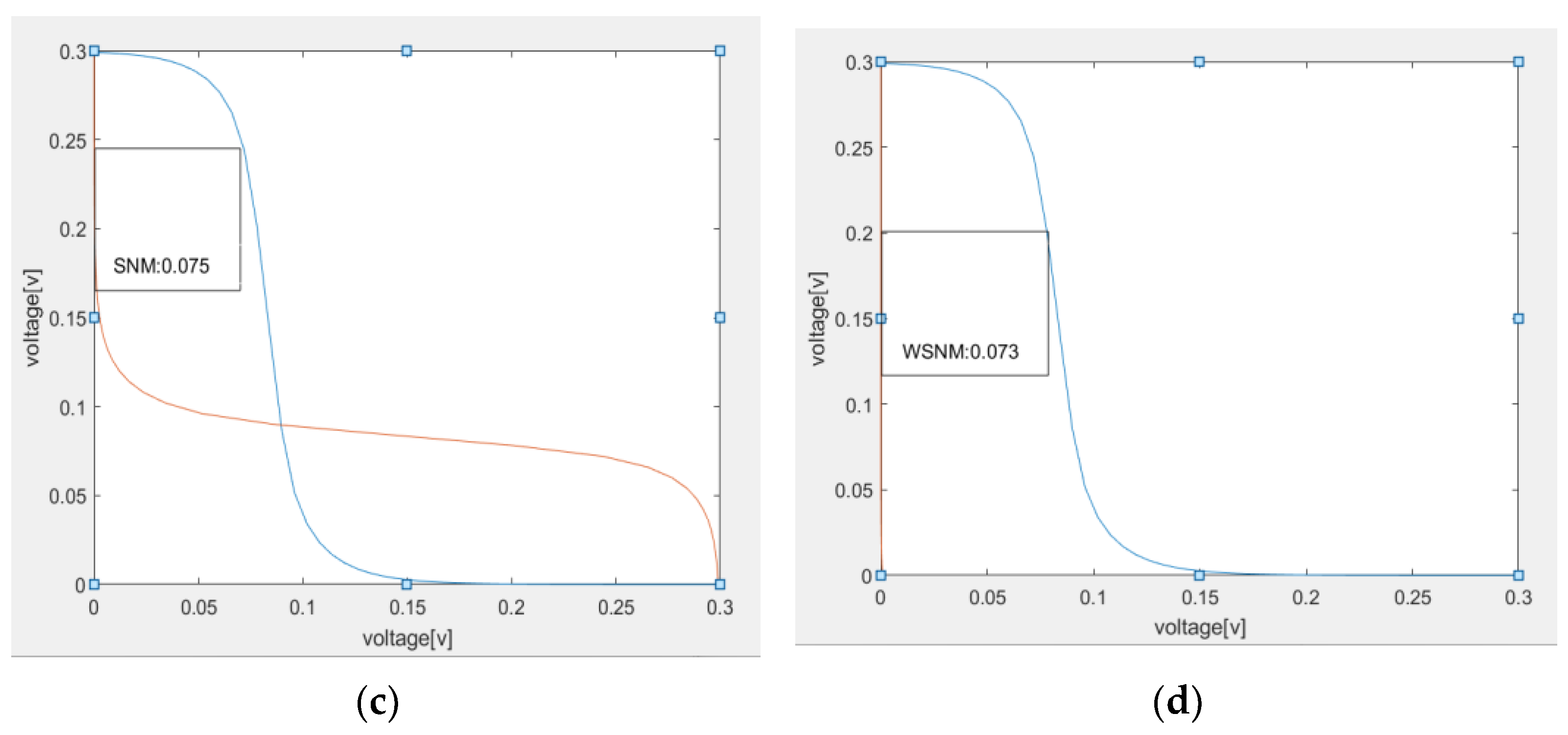

3.2. Different Design in Same Process

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Gaadhe, A.; Shirode, U.; Kanphade, R. The Stability Performance Analysis of SRAM Cell Topologies in 90nm and 130nm CMOS technology. In Proceedings of the 2021 International Conference on Emerging Smart Computing and Informatics (ESCI), Pune, India, 5–7 March 2021; pp. 733–736. [Google Scholar] [CrossRef]

- Karamimanesh, M.; Abiri, E.; Hassanli, K.; Salehi, M.R.; Darabi, A. A Write Bit-Line Free Sub-threshold SRAM Cell with Fully Half-Select Free Feature and High Reliability for Ultra-Low Power Applications. AEU-Int. J. Electron. Commun. 2021, 145, 154075. [Google Scholar] [CrossRef]

- Gopinath, A.; Ytterdal, T.; Miled, Z.B.; Meagher, R.; Rizkalla, M. Leakage Current and Static Power Analysis of TFET 8T-SRAM Cell—ScienceDirect. Mater. Today Proc. 2019, 7, 878–887. [Google Scholar] [CrossRef]

- Nanda, U.; Nayak, D.; Saw, S.K.; KK, A.M.; Jena, B. Analysis of Static Noise Margin of 10T SRAM Using Sleepy Stack Transistor Approach. In Proceedings of the 2021 Devices for Integrated Circuit (DevIC), Kalyani, India, 24–25 March 2021. [Google Scholar]

- Rawat, R.M.; Kumar, V. A Comparative Study of 6T and 8T SRAM Cell with Improved Read and Write Margins in 130 nm CMOS Technology. WSEAS Trans. Circuits Syst. 2020, 19, 13–18. [Google Scholar] [CrossRef]

- Saun, S.; Kumar, H. Design and performance analysis of 6T SRAM cell on different CMOS technologies with stability characterization. IOP Conf. Ser. Mater. Sci. Eng. 2019, 561, 012093. [Google Scholar] [CrossRef] [Green Version]

- Sachdeva, A.; Tomar, V. Statistical Stability Characterization of Schmitt Trigger Based 10-T SRAM Cell Design. In Proceedings of the 7th International Conference on Signal Processing and Integrated Networks (SPIN 2020), Noida, India, 27–28 February 2020. [Google Scholar]

- Yadav, S.; Sharma, D. Assessment of read and write stability for 6T SRAM cell based on charge plasma DLTFET. Superlattices Microstruct. 2018, 115, 67–77. [Google Scholar]

- Kim, T.; Manisankar, S.; Chung, Y. A Novel 8T Cell-Based Subthreshold Static RAM for Ultra-Low Power Platform Applications. Electronics 2020, 9, 928. [Google Scholar] [CrossRef]

- Zheng, Z.A.; Hu, P.H. Improved Read Stability and Writability of Negative Capacitance FinFET SRAM Cell for Subthreshold Operation. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Hokkaido, Japan, 26–29 May 2019; IEEE: Piscataway, NJ, USA, 2019. [Google Scholar]

- Huang, X.; Yao, Y.; Peng, S.; Zhang, D.; Shi, J.; Jin, Z. Effects of Charge Trapping at the MoS2–SiO2 Interface on the Stability of Subthreshold Swing of MoS2 Field Effect Transistors. Materials 2020, 13, 2896. [Google Scholar] [CrossRef] [PubMed]

- Raychowdhury, A.; Mukhopadhyay, S.; Roy, K. A Feasibility Study of Subthreshold SRAM Across Technology Generations. In Proceedings of the IEEE International Conference on Computer Design: Vlsi in Computers & Processors IEEE, San Jose, CA, USA, 2–5 October 2005. [Google Scholar]

- Zamani, M.; Hassanzadeh, S.; Hajsadeghi, K.; Saeidi, R. A 32 kb 90 nm 9T-cell sub-threshold SRAM with improved read and write SNM. In Proceedings of the 2013 8th International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Abu Dhabi, United Arab Emirates, 26–28 March 2013; pp. 104–107. [Google Scholar] [CrossRef]

- Birla, S.; Singh, R.K.; Pattanaik, M. Stability and Leakage Analysis of a Novel PP Based 9T SRAM Cell Using N Curve at Deep Submicron Technology for Multimedia Applications. Circuits Syst. 2011, 2, 274–280. [Google Scholar] [CrossRef] [Green Version]

- Samson, M.; Srinivas, M.B. Analyzing N-Curve Metrics for Sub-Threshold 65nm CMOS SRAM. In Proceedings of the Nanotechnology, NANO ’08, 8th IEEE Conference, Arlington, TX, USA, 18–21 August 2008; IEEE: Piscataway, NJ, USA, 2008. [Google Scholar]

- Kingra, S.K.; Majumdar, S.; Suri, M. Stability analysis of hybrid CMOS-RRAM based 4T-2R NVSRAM. In Proceedings of the New Circuits & Systems Conference, Strasbourg, France, 25–28 June 2017; IEEE: Piscataway, NJ, USA, 2017. [Google Scholar]

- Kim, H.; Kim, T.; Manisankar, S.; Chung, Y. Read disturb-free SRAM bit-cell for subthreshold memory applications. In Proceedings of the 2017 International Conference on Electron Devices and Solid-State Circuits (EDSSC), Hsinchu, Taiwan, 18–20 October 2017. [Google Scholar]

- Gupta, M.; Gupta, K.; Pandey, N. A 32-nm Sub-Threshold 9T SRAM Bitcell with Improved Read and Write performance. In Proceedings of the 2018 International Conference on Advances in Computing, Communication Control and Networking (ICACCCN), Greater Noida, India, 12–13 October 2018; pp. 781–787. [Google Scholar] [CrossRef]

- Eslami, N.; Ebrahimi, B.; Shakouri, E.; Najafi, D. A single-ended low leakage and low voltage 10T SRAM cell with high yield. Analog Integr. Circuits Signal Process. 2020, 105, 263–274. [Google Scholar] [CrossRef]

| Static Stability Analysis | Stability Analysis Based on Leakage Current |

|---|---|

| Read stability indicators: read voltage noise tolerance (RVNM), read current noise tolerance (RINM) | Read stability indicators: read static voltage noise tolerance (RSNM) |

| Write stability indicators: write voltage noise tolerance (WVNM), write current noise tolerance (WINM) | Write stability indicators: write static voltage noise tolerance (WSNM) |

| The maximum noise tolerance that can be measured:0.5 Vdd [16] | The maximum noise tolerance that can be measured: no limit |

| Additional calculation tools required (MATLAB) | No additional calculation tools required |

| Read and write information are separated | Read and write information are in one curve |

| Data contain only voltage information | Data contain both current and voltage information |

| SNM (mV) | WSNM (mV) | RINM (nA) | RVNM (mV) | WVNM (mV) | WINM (nA) | |

|---|---|---|---|---|---|---|

| 8T | 80 | 92 | 486 | 96 | 204 | 23 |

| 9T | 80 | 79 | 521 | 107 | 193 | 81.4 |

| 10T | 75 | 73 | 449 | 82 | 218 | 42 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bai, N.; Hu, Z.; Wang, Y.; Xu, Y. Leakage Current Stability Analysis for Subthreshold SRAM. Electronics 2022, 11, 1196. https://doi.org/10.3390/electronics11081196

Bai N, Hu Z, Wang Y, Xu Y. Leakage Current Stability Analysis for Subthreshold SRAM. Electronics. 2022; 11(8):1196. https://doi.org/10.3390/electronics11081196

Chicago/Turabian StyleBai, Na, Zhiqiang Hu, Yi Wang, and Yaohua Xu. 2022. "Leakage Current Stability Analysis for Subthreshold SRAM" Electronics 11, no. 8: 1196. https://doi.org/10.3390/electronics11081196

APA StyleBai, N., Hu, Z., Wang, Y., & Xu, Y. (2022). Leakage Current Stability Analysis for Subthreshold SRAM. Electronics, 11(8), 1196. https://doi.org/10.3390/electronics11081196