A Simple Virtual-Vector-Based PWM Formulation for Multilevel Three-Phase Neutral-Point-Clamped DC–AC Converters including the Overmodulation Region

Abstract

:1. Introduction

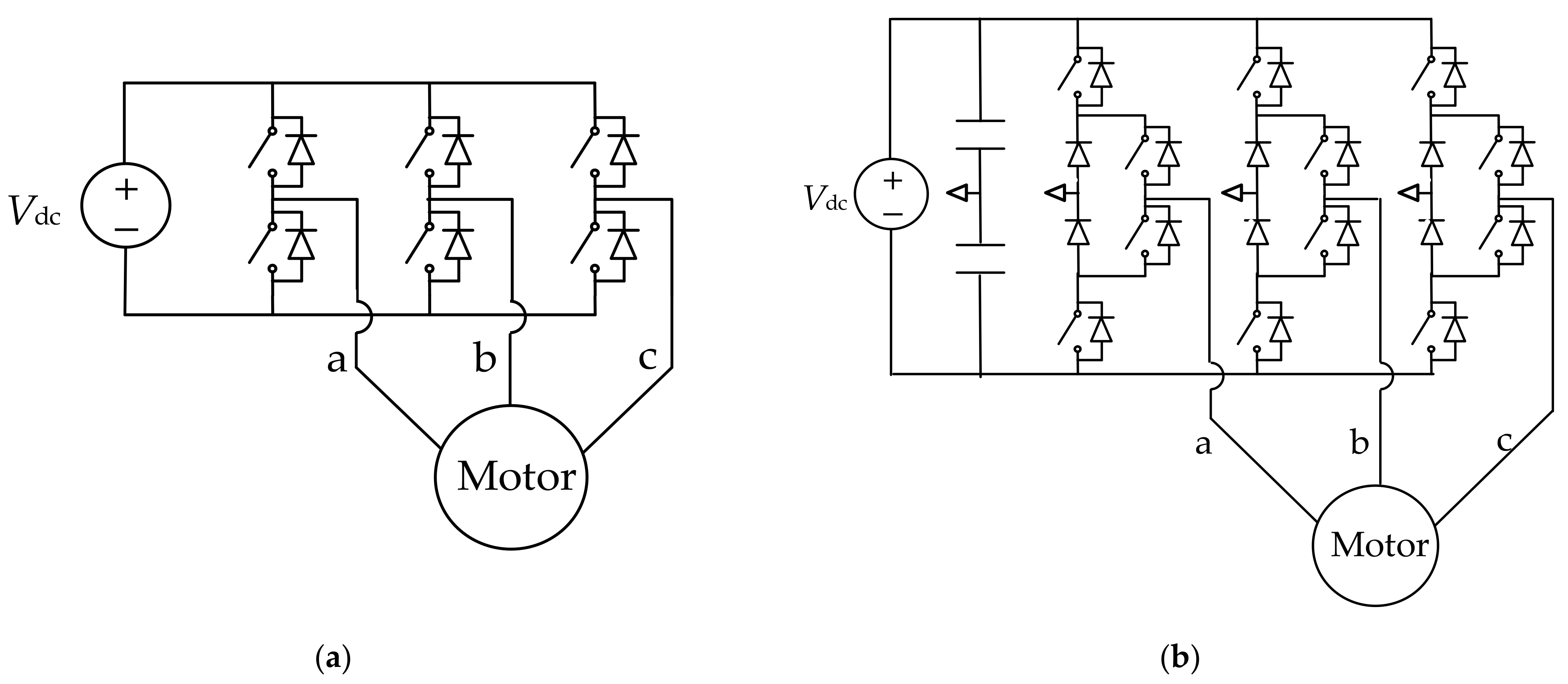

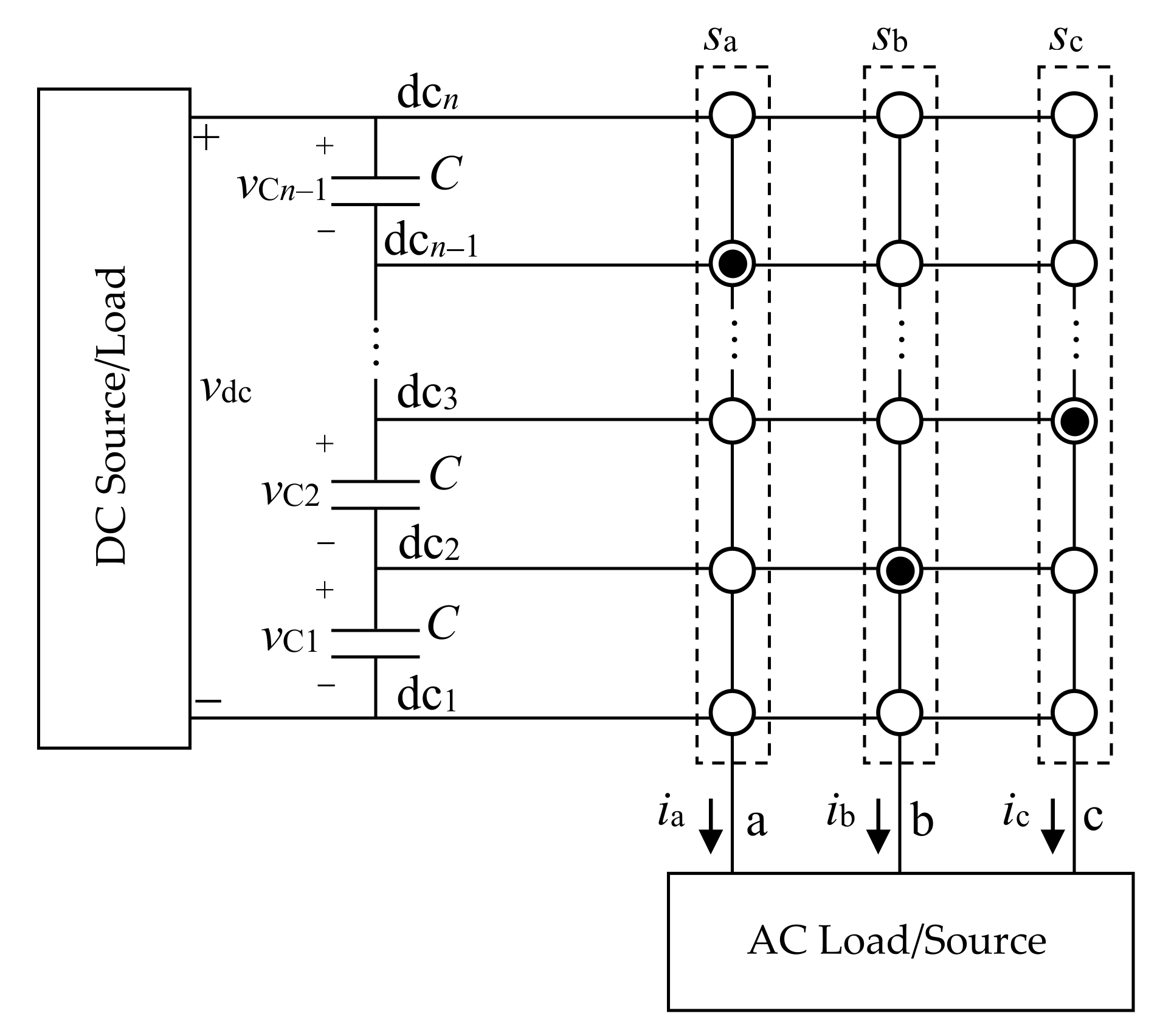

2. Review of NPC Topologies and Their Operating Principle

3. Simplified Virtual-Vector-Based PWM Formulation

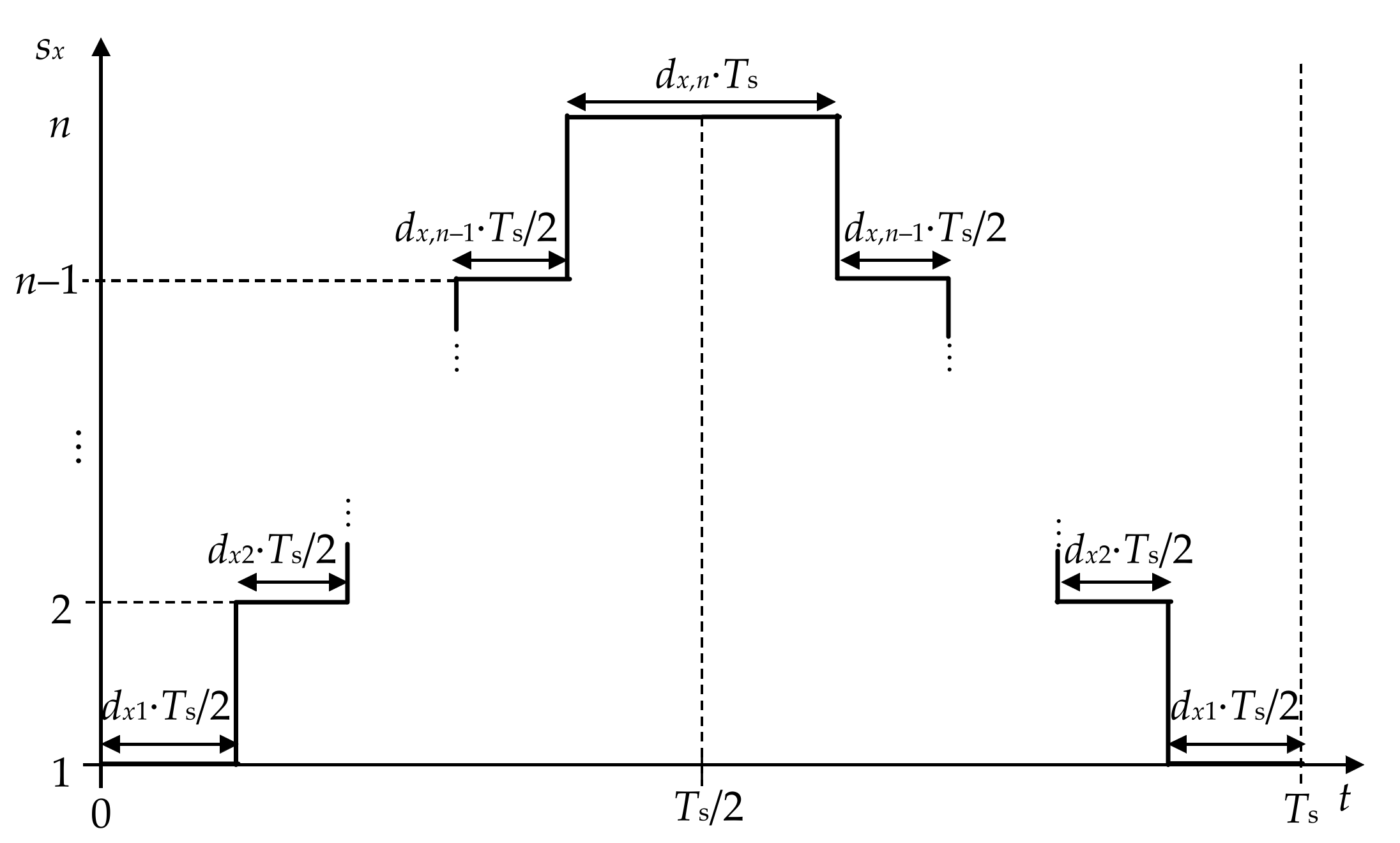

3.1. Undermodulation Range

3.2. Full Modulation Range

| Algorithm 1 |

| 1: if m ≤ hbc 2: mode = 1 3: m’ = m 4: elseif hbc < m ≤ hbc·mmaxI 5: mode = 1 6: 7: 8: elseif hbc·mmaxI < m ≤ hbc·mmaxII 9: mode = 2 10: 11: 12: end |

| Algorithm 2 |

| 1: 2: 3: 4: 5: 6: 7: 8: if dpp ≤ hbc 9: if mode = 1 10: 11: 12: elseif mode = 2 13: if dmed ≤ 0 14: 15: 16: elseif dmed > 0 17: 18: 19: end 20: end 21: elseif dpp > hbc 22: 23: 24: end 25: |

| Algorithm 3 |

| 1: if m ≤ hbc 2: mode = 1 3: m’ = m 4: elseif hbc < m ≤ hbc·mmaxI 5: mode = 1 6: 7: elseif hbc·mmaxI < m ≤ hbc·mmaxII 8: mode = 2 9: 10: end |

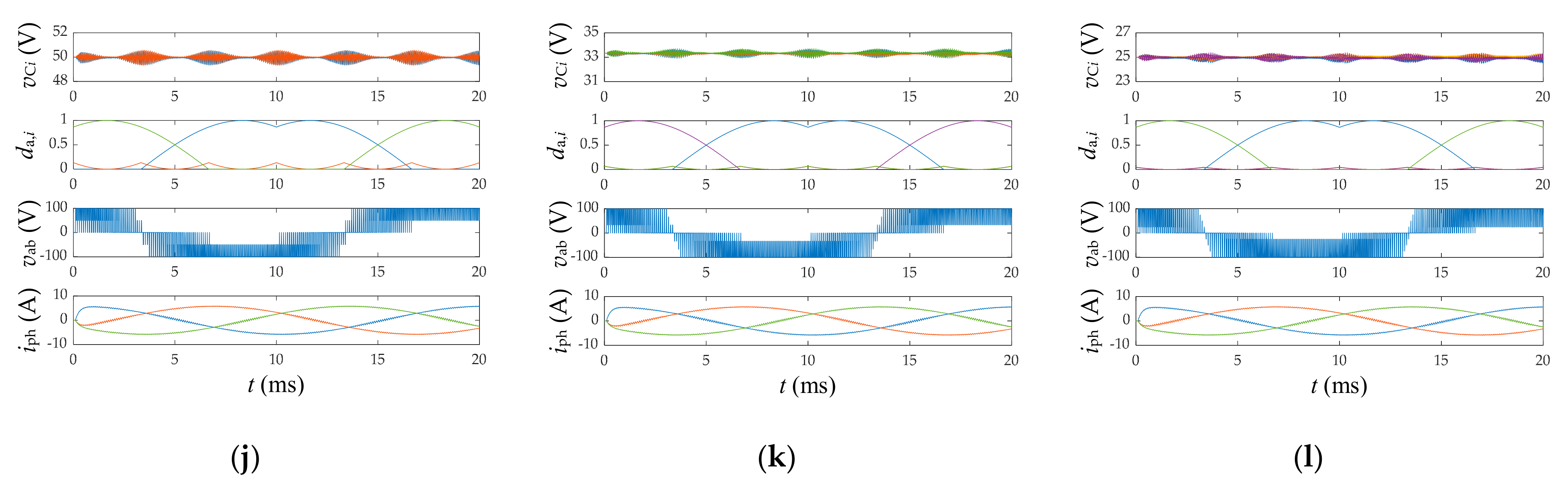

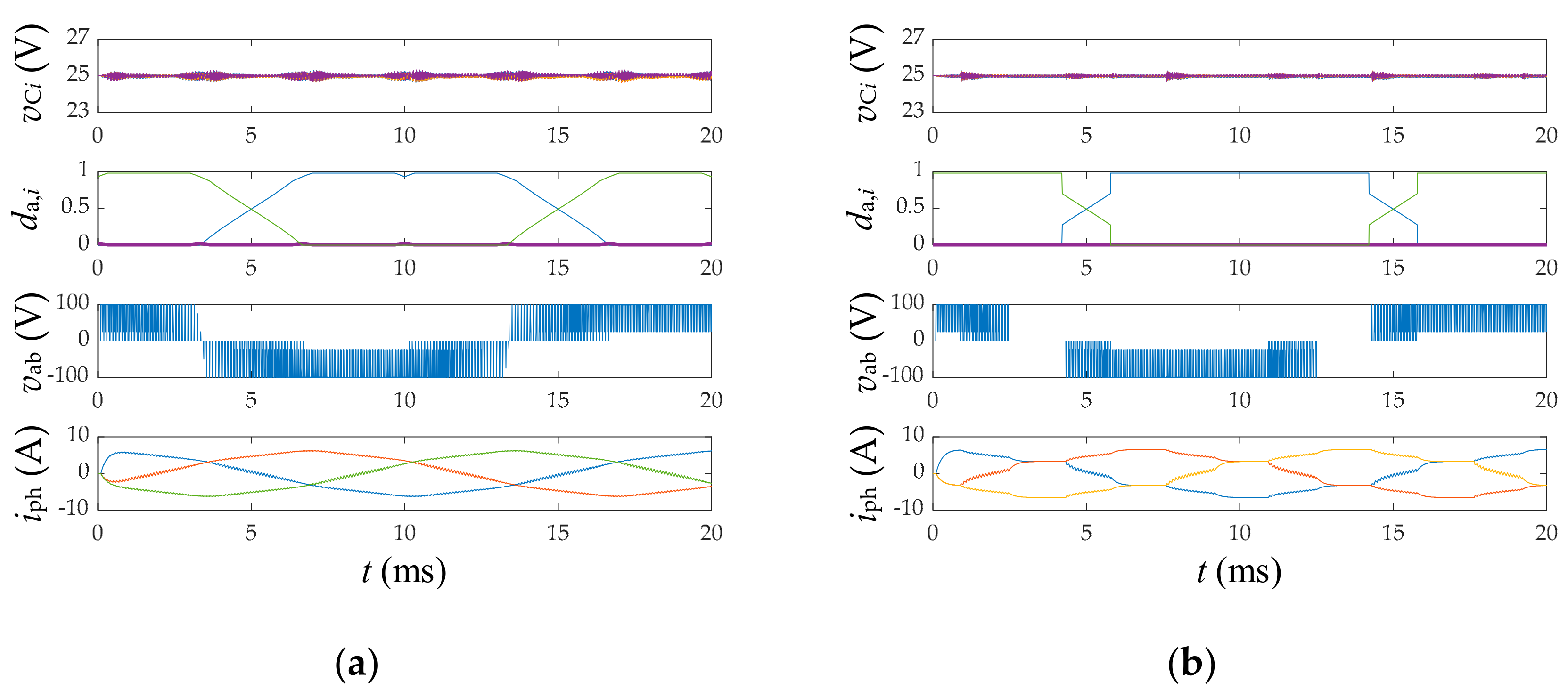

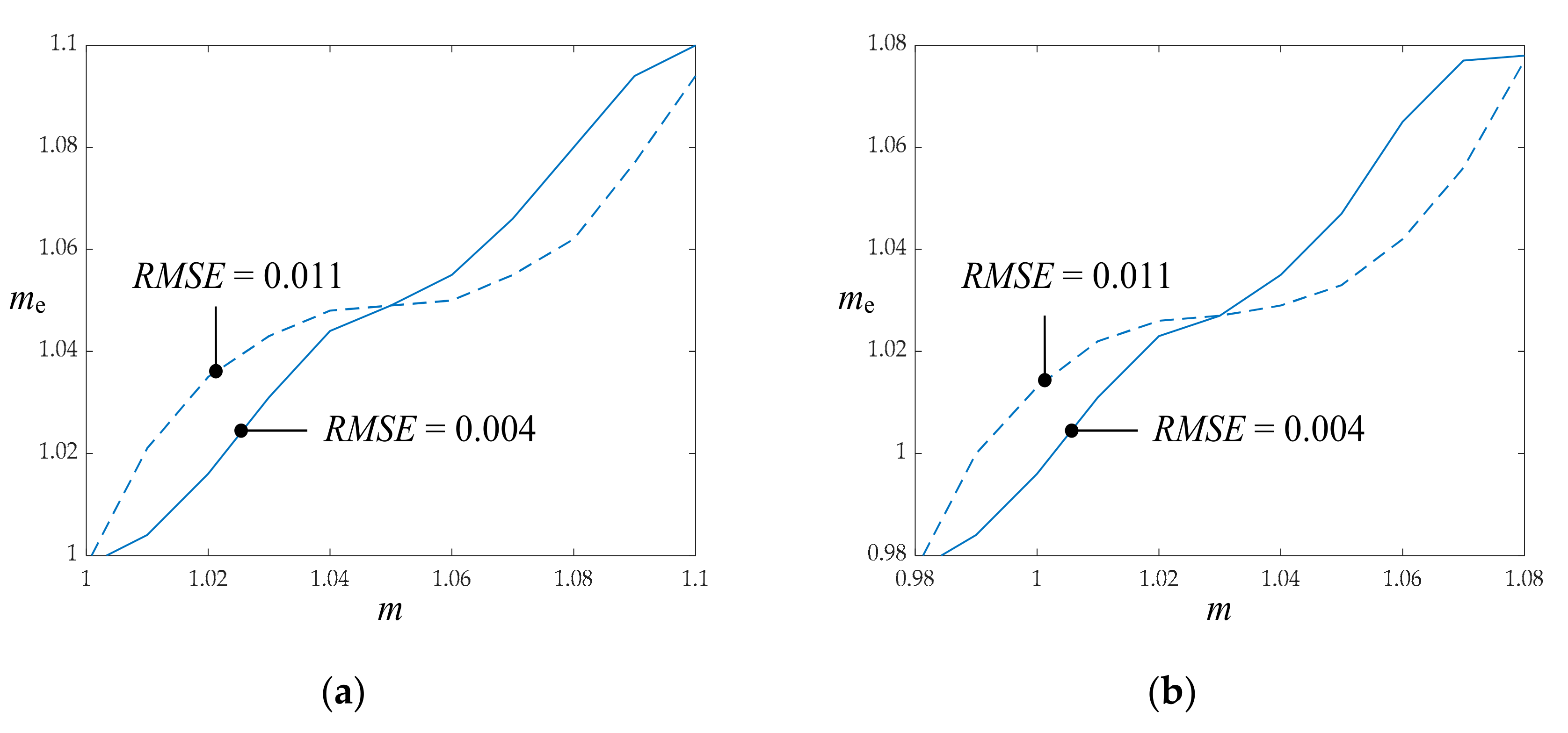

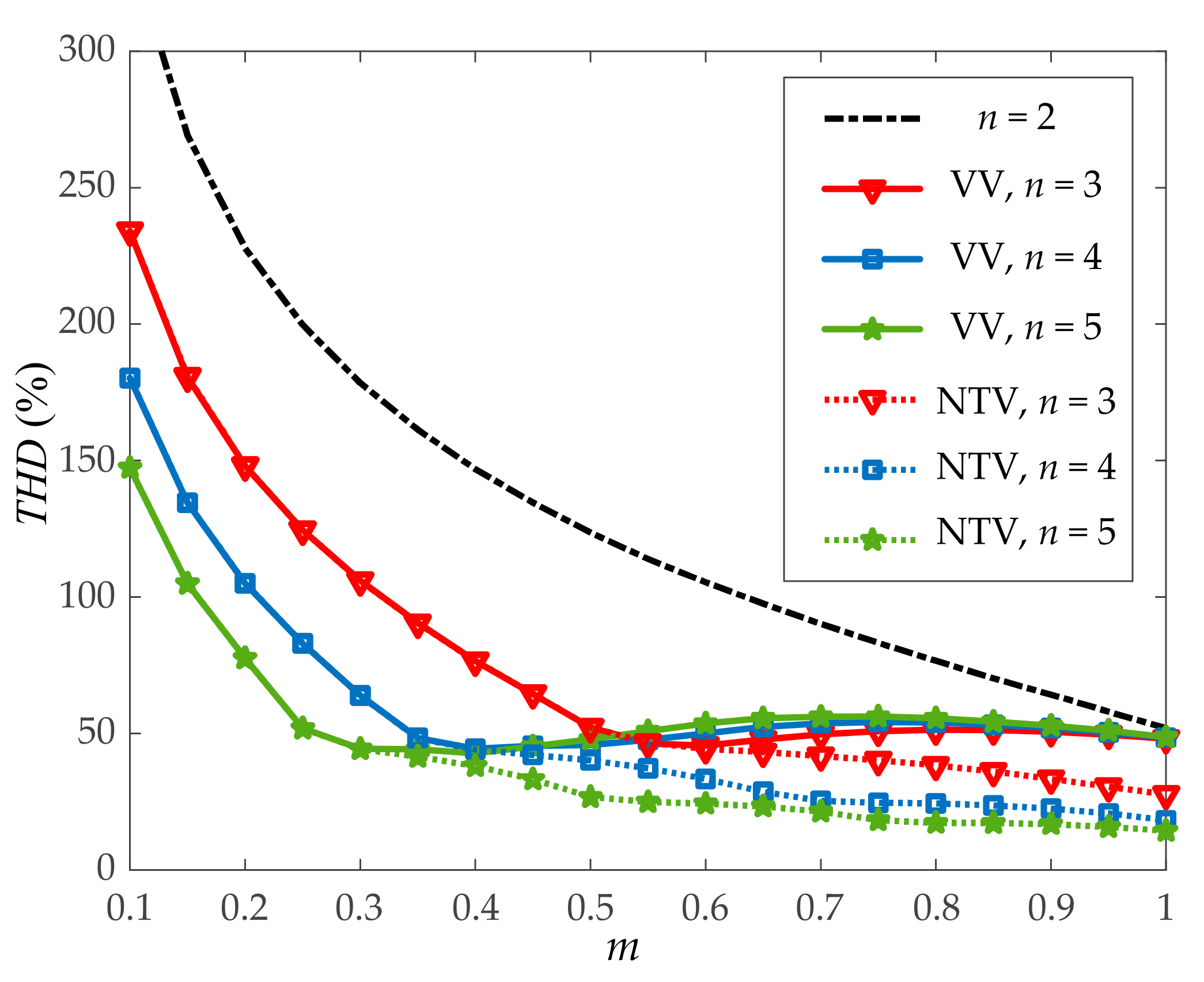

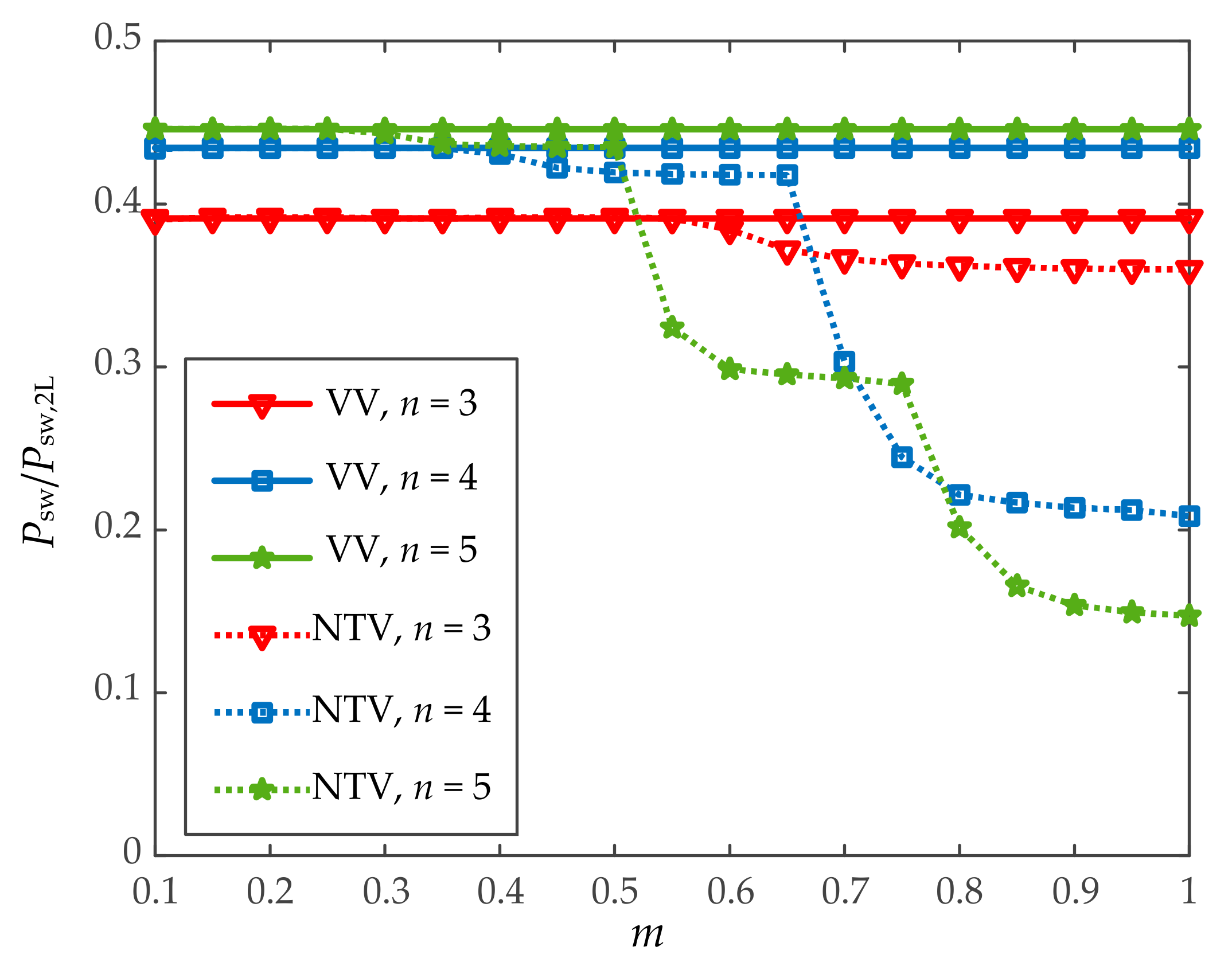

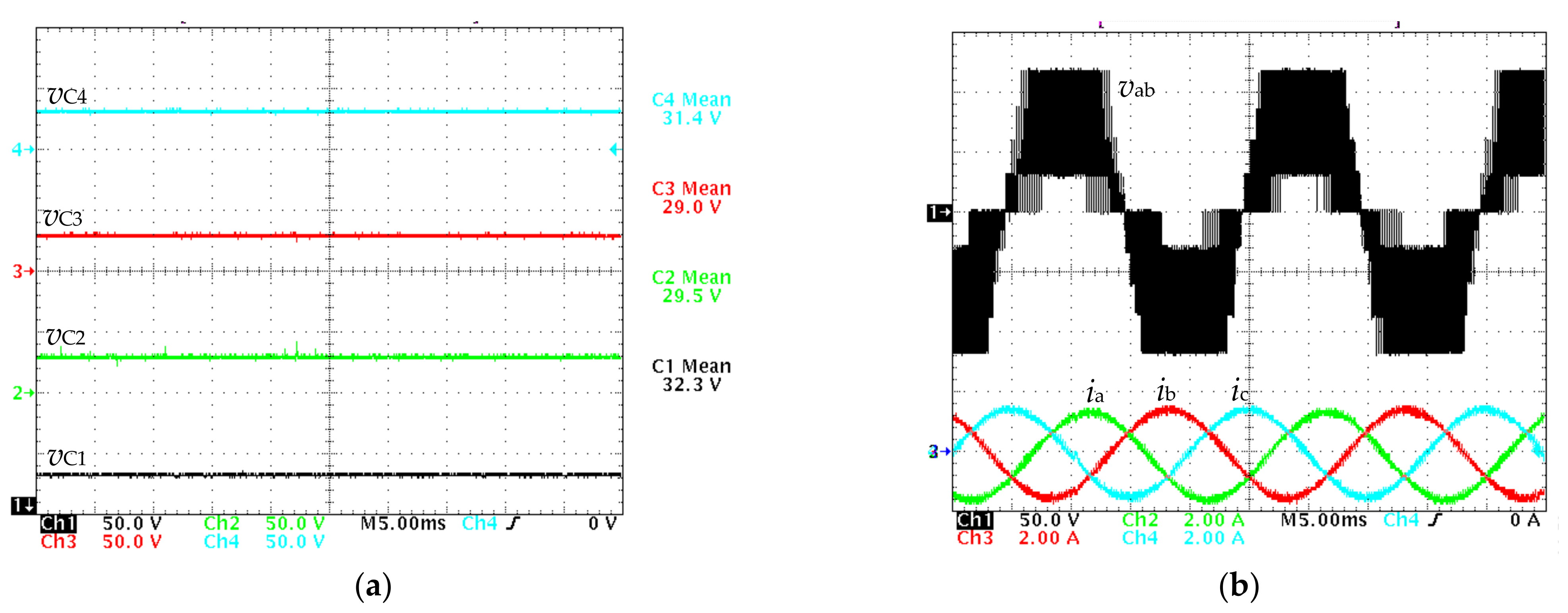

4. Simulation Results

5. Conclusions

Funding

Conflicts of Interest

References

- Levi, E. Multiphase Electric Machines for Variable-Speed Applications. IEEE Trans. Ind. Electron. 2008, 55, 1893–1909. [Google Scholar] [CrossRef]

- Zhu, Z.Q.; Howe, D. Electrical Machines and Drives for Electric, Hybrid, and Fuel Cell Vehicles. Proc. IEEE 2007, 95, 746–765. [Google Scholar] [CrossRef]

- Kouro, S.; Malinowski, M.; Gopakumar, K.; Pou, J.; Franquelo, L.G.; Wu, B.; Rodriguez, J.; Perez, M.A.; Leon, J.I. Recent Advances and Industrial Applications of Multilevel Converters. IEEE Trans. Ind. Electron. 2010, 57, 2553–2580. [Google Scholar] [CrossRef]

- Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [Google Scholar] [CrossRef]

- Sunddararaj, S.P.; Rangarajan, S.S.; N, S. An Extensive Review of Multilevel Inverters Based on Their Multifaceted Structural Configuration, Triggering Methods and Applications. Electronics 2020, 9, 433. [Google Scholar] [CrossRef] [Green Version]

- Hassan, A.; Yang, X.; Chen, W.; Houran, M.A. A State of the Art of the Multilevel Inverters with Reduced Count Components. Electronics 2020, 9, 1924. [Google Scholar] [CrossRef]

- Rana, R.A.; Patel, S.A.; Muthusamy, A.; Lee, C.W.; Kim, H.-J. Review of Multilevel Voltage Source Inverter Topologies and Analysis of Harmonics Distortions in FC-MLI. Electronics 2019, 8, 1329. [Google Scholar] [CrossRef] [Green Version]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Busquets-Monge, S. Neutral-point-clamped dc-ac power converters. In Wiley Encyclopedia of Electrical and Electronics Engineering; Webster, J.G., Ed.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2018; pp. 1–20. [Google Scholar]

- Kang, K.-P.; Cho, Y.; Kim, H.-S.; Baek, J.-W. DC-Link Capacitor Voltage Imbalance Compensation Method Based Injecting Harmonic Voltage for Cascaded Multi-Module Neutral Point Clamped Inverter. Electronics 2019, 8, 155. [Google Scholar] [CrossRef] [Green Version]

- Li, P.; Zhang, L.; Ouyang, B.; Liu, Y. Nonlinear Effects of Three-Level Neutral-Point Clamped Inverter on Speed Sensorless Control of Induction Motor. Electronics 2019, 8, 402. [Google Scholar] [CrossRef] [Green Version]

- Kim, S.-H.; Kim, S.-M.; Park, S.; Lee, K.-B. Switch Open-Fault Detection for a Three-Phase Hybrid Active Neutral-Point-Clamped Rectifier. Electronics 2020, 9, 1437. [Google Scholar] [CrossRef]

- Halabi, L.M.; Alsofyani, I.M.; Lee, K.-B. Open-Circuit Fault Tolerance Method for Three-Level Hybrid Active Neutral Point Clamped Converters. Electronics 2020, 9, 1535. [Google Scholar] [CrossRef]

- Madasamy, P.; Verma, R.; Rameshbabu, A.; Murugesan, A.; Umamageswari, R.; Munda, J.; Bharatiraja, C.; Mihet-Popa, L. Neutral Point Clamped Transformer-Less Multilevel Converter for Grid-Connected Photovoltaic System. Electronics 2021, 10, 977. [Google Scholar] [CrossRef]

- Barros, J.; Rocha, L.; Silva, J. Backstepping Predictive Control of Hybrid Microgrids Interconnected by Neutral Point Clamped Converters. Electronics 2021, 10, 1210. [Google Scholar] [CrossRef]

- Alepuz, S.; Busquets-Monge, S.; Nicolás-Apruzzese, J.; Filbà-Martínez, À.; Bordonau, J.; Yuan, X.; Kouro, S. A Survey on Capacitor Voltage Control in Neutral-Point-Clamped Multilevel Converters. Electronics 2022, 11, 527. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Alepuz, S.; Rocabert, J.; Bordonau, J. Pulsewidth Modulations for the Comprehensive Capacitor Voltage Balance of n-Level Three-Leg Diode-Clamped Converters. IEEE Trans. Power Electron. 2009, 24, 1364–1375. [Google Scholar] [CrossRef] [Green Version]

- Busquets-Monge, S.; Maheshwari, R.; Munk-Nielsen, S. Overmodulation of n-Level Three-Leg DC–AC Diode-Clamped Converters with Comprehensive Capacitor Voltage Balance. IEEE Trans. Ind. Electron. 2012, 60, 1872–1883. [Google Scholar] [CrossRef]

- Busquets-Monge, S.; Ruderman, A. Carrier-based PWM strategies for the comprehensive capacitor voltage balance of mul-tilevel multileg diode-clamped converters. In Proceedings of the 2010 IEEE International Symposium on Industrial Electronics, Bari, Italy, 4–7 July 2010. [Google Scholar]

- Maheshwari, R.; Munk-Nielsen, S.; Busquets-Monge, S. A carrier-based approach for overmodulation of three-level neutral-point-clamped inverter with zero neutral-point current. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 1767–1773. [Google Scholar]

- Gui, S.W.; Lin, Z.J.; Huang, S.H. A Varied VSVM Strategy for Balancing the Neutral-Point Voltage of DC-Link Capacitors in Three-Level NPC Converters. Energies 2015, 8, 2032–2047. [Google Scholar] [CrossRef] [Green Version]

- Hu, C.; Yu, X.; Holmes, D.G.; Shen, W.; Wang, Q.; Luo, F.; Liu, N. An Improved Virtual Space Vector Modulation Scheme for Three-Level Active Neutral-Point-Clamped Inverter. IEEE Trans. Power Electron. 2016, 32, 7419–7434. [Google Scholar] [CrossRef]

- Wang, J.; Gao, Y.; Jiang, W.; Weidong, J. A Carrier-Based Implementation of Virtual Space Vector Modulation for Neutral-Point-Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2017, 64, 9580–9586. [Google Scholar] [CrossRef]

- Wu, X.; Tan, G.; Ye, Z.; Yao, G.; Liu, Z.; Liu, G. Virtual-Space-Vector PWM for a Three-Level Neutral-Point-Clamped Inverter with Unbalanced DC-Links. IEEE Trans. Power Electron. 2017, 33, 2630–2642. [Google Scholar] [CrossRef]

- Xiang, C.-Q.; Shu, C.; Han, D.; Mao, B.-K.; Wu, X.; Yu, T.-J. Improved Virtual Space Vector Modulation for Three-Level Neutral-Point-Clamped Converter with Feedback of Neutral-Point Voltage. IEEE Trans. Power Electron. 2018, 33, 5452–5464. [Google Scholar] [CrossRef]

- Liu, G.; Wang, D.; Wang, M.; Zhu, C.; Wang, M. Neutral-Point Voltage Balancing in Three-Level Inverters Using an Optimized Virtual Space Vector PWM with Reduced Commutations. IEEE Trans. Ind. Electron. 2018, 65, 6959–6969. [Google Scholar] [CrossRef]

- Weidong, J.; Wang, L.; Wang, J.; Zhang, X.; Wang, P. A Carrier-Based Virtual Space Vector Modulation With Active Neutral-Point Voltage Control for a Neutral-Point-Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2018, 65, 8687–8696. [Google Scholar] [CrossRef]

- Giri, S.K.; Mukherjee, S.; Kundu, S.; Banerjee, S.; Chakraborty, C. An Improved PWM Scheme for Three-Level Inverter Extending Operation into Overmodulation Region with Neutral-Point Voltage Balancing for Full Power-Factor Range. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1527–1539. [Google Scholar] [CrossRef]

- Jiang, W.; Wang, P.; Ma, M.; Wang, J.; Li, J.; Li, L.; Chen, K.; Weidong, J. A Novel Virtual Space Vector Modulation with Reduced Common-Mode Voltage and Eliminated Neutral Point Voltage Oscillation for Neutral Point Clamped Three-Level Inverter. IEEE Trans. Ind. Electron. 2019, 67, 884–894. [Google Scholar] [CrossRef]

- Qamar, M.A.; Wang, K.; Zheng, Z.; Wang, S.; Li, Y. A Simplified Virtual Vector PWM Algorithm to Balance the Capacitor Voltages of Four-Level Diode-Clamped Converter. IEEE Access 2020, 8, 180896–180908. [Google Scholar] [CrossRef]

- Guo, F.; Yang, T.; Diab, A.M.; Yeoh, S.S.; Bozhko, S.; Wheeler, P. An Enhanced Virtual Space Vector Modulation Scheme of Three-Level NPC Converters for More-Electric-Aircraft Applications. IEEE Trans. Ind. Appl. 2021, 57, 5239–5251. [Google Scholar] [CrossRef]

- Xia, S.; Wu, X.; Zheng, J.; Li, X.; Wang, K. A Virtual Space Vector PWM With Active Neutral Point Voltage Control and Common Mode Voltage Suppression for Three-Level NPC Converters. IEEE Trans. Ind. Electron. 2021, 68, 11761–11771. [Google Scholar] [CrossRef]

- Wang, K.; Zheng, Z.; Li, Y. A Novel Carrier-Overlapped PWM Method for Four-Level Neutral-Point Clamped Converters. IEEE Trans. Power Electron. 2019, 34, 7–12. [Google Scholar] [CrossRef]

- Wang, J.; Wang, J.; Xiao, B.; Gui, Z.; Jiang, W. Full Range Capacitor Voltage Balance PWM Strategy for Diode-Clamped Multilevel Inverter. Electronics 2020, 9, 1263. [Google Scholar] [CrossRef]

- Maheshwari, R.; Munk-Nielsen, S.; Busquets-Monge, S. EMI performance comparison of two-level and three-level inverters in small dc-link capacitors based motor drives. In Proceedings of the 2012 IEEE International Symposium on Industrial Electronics, Hangzhou, China, 28–31 May 2012; pp. 652–657. [Google Scholar]

| sac | Connection of AC Terminal to | s1 | s2 | s3 | … | sk−1 | sk | … | sn−3 | sn−2 | sn−1 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | dc1 | 0 | 0 | 0 | … | 0 | 0 | … | 0 | 0 | 0 |

| 2 | dc2 | 1 | 0 | 0 | … | 0 | 0 | … | 0 | 0 | 0 |

| 3 | dc3 | 1 | 1 | 0 | … | 0 | 0 | … | 0 | 0 | 0 |

| … | … | … | … | … | … | … | … | … | … | … | … |

| k | dck | 1 | 1 | 1 | … | 1 | 0 | … | 0 | 0 | 0 |

| … | … | … | … | … | … | … | … | … | … | … | … |

| n − 2 | dcn−2 | 1 | 1 | 1 | … | 1 | 1 | … | 1 | 0 | 0 |

| n − 1 | dcn−1 | 1 | 1 | 1 | … | 1 | 1 | … | 1 | 1 | 0 |

| n | dcn | 1 | 1 | 1 | … | 1 | 1 | … | 1 | 1 | 1 |

| Parameter | Description | Value |

|---|---|---|

| Vdc | Total DC-link voltage | 100 V |

| C | Capacitance of each DC-link capacitor | 100 µF |

| fo | Line-cycle fundamental frequency | 50 Hz |

| fs | Switching frequency | 10 kHz |

| RL | Per-phase load resistance | 10 Ω |

| LL | Per-phase load inductance | 2 mH |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Busquets-Monge, S. A Simple Virtual-Vector-Based PWM Formulation for Multilevel Three-Phase Neutral-Point-Clamped DC–AC Converters including the Overmodulation Region. Electronics 2022, 11, 641. https://doi.org/10.3390/electronics11040641

Busquets-Monge S. A Simple Virtual-Vector-Based PWM Formulation for Multilevel Three-Phase Neutral-Point-Clamped DC–AC Converters including the Overmodulation Region. Electronics. 2022; 11(4):641. https://doi.org/10.3390/electronics11040641

Chicago/Turabian StyleBusquets-Monge, Sergio. 2022. "A Simple Virtual-Vector-Based PWM Formulation for Multilevel Three-Phase Neutral-Point-Clamped DC–AC Converters including the Overmodulation Region" Electronics 11, no. 4: 641. https://doi.org/10.3390/electronics11040641

APA StyleBusquets-Monge, S. (2022). A Simple Virtual-Vector-Based PWM Formulation for Multilevel Three-Phase Neutral-Point-Clamped DC–AC Converters including the Overmodulation Region. Electronics, 11(4), 641. https://doi.org/10.3390/electronics11040641