Exploiting a Deep Learning Toolbox for Human-Machine Feedback towards Analog Integrated Circuit Placement Automation

Abstract

1. Introduction

2. Related Work and Contributions

- The proposed toolbox breaks with recent ML-based analog IC placement approaches [15,20,21,22] by focusing on explainable AI, where the expert designer is involved in the synthesis flow. This is accomplished through its GUI, offering filtering and editing options over the several proposed floorplan solutions. During floorplan design there are several conflicting constraints and objectives, and by providing a tool is in a constant state of human-machine feedback, the impact of each device’s position change and the inherent tradeoffs is instantly presented to the IC designer. Additionally, subsequent moves are also suggested by the tool;

- The toolbox’s underlying DL model relies on pairwise device interactions, which can encode any of several topological constraints. This feature results in an enhanced generalization, turning it capable of dealing with newer circuit topologies (i.e., circuit topologies not used for its training), unlike approaches based on retargeting from a legacy layout or template or synthesis by knowledge mining that make use of existing target examples in the form of previously designed placement solutions, encoding the knowledge and intuition of the design expert. In those, the legacy examples serve as a surrogate for the explicit definition of the constraints to be met, and the problem is ultimately dealt with in a fully deterministic fashion, where a given circuit is matched to a previously seen design without any innovation or case-specific optimization. Deep Placer’s enhanced generalization simultaneously allows to handle different technology nodes without additional effort;

- Similar to the approaches based on generation from topological constraints, the toolbox automatically produces placement solutions from scratch. Those works have already explored the possibility of explicitly defining the constraints to be considered within the synthesis process. However, they rely on time-consuming optimization cycles to design each solution. Deep Placer increases designers’ productivity by proposing tens of valid floorplan solutions for a singular block-level analog structure at push-button speed (i.e., bypassing the time required for optimization);

- Experimental results show that the toolbox produces competitive floorplans compared to human-designed ones while complementing industry automation solutions.

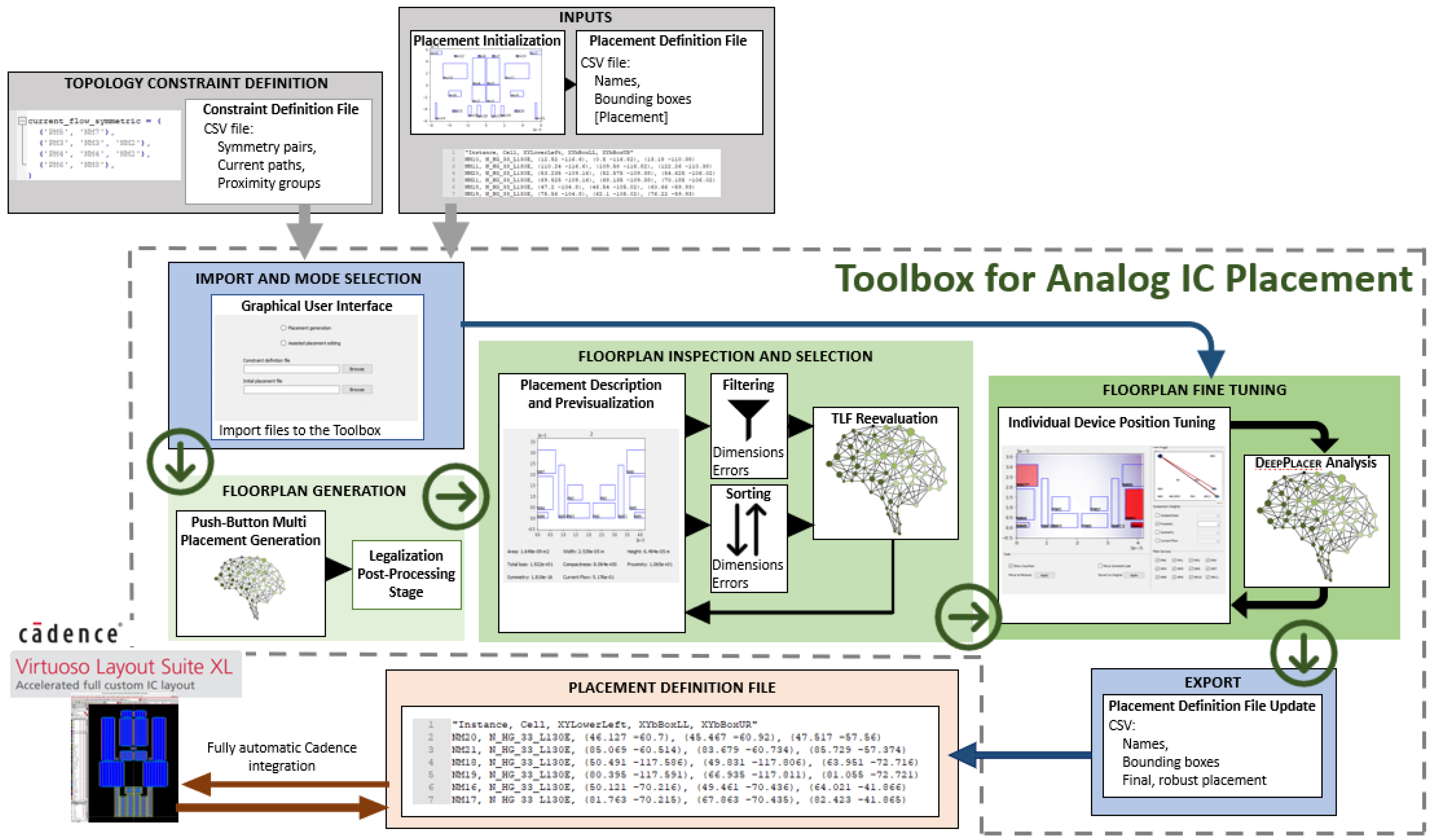

3. Toolbox

3.1. Underlying DL Model

3.2. Context for a Human-Machine Feedback Approach

3.3. Fully Automatic and User-Assisted Functionalities

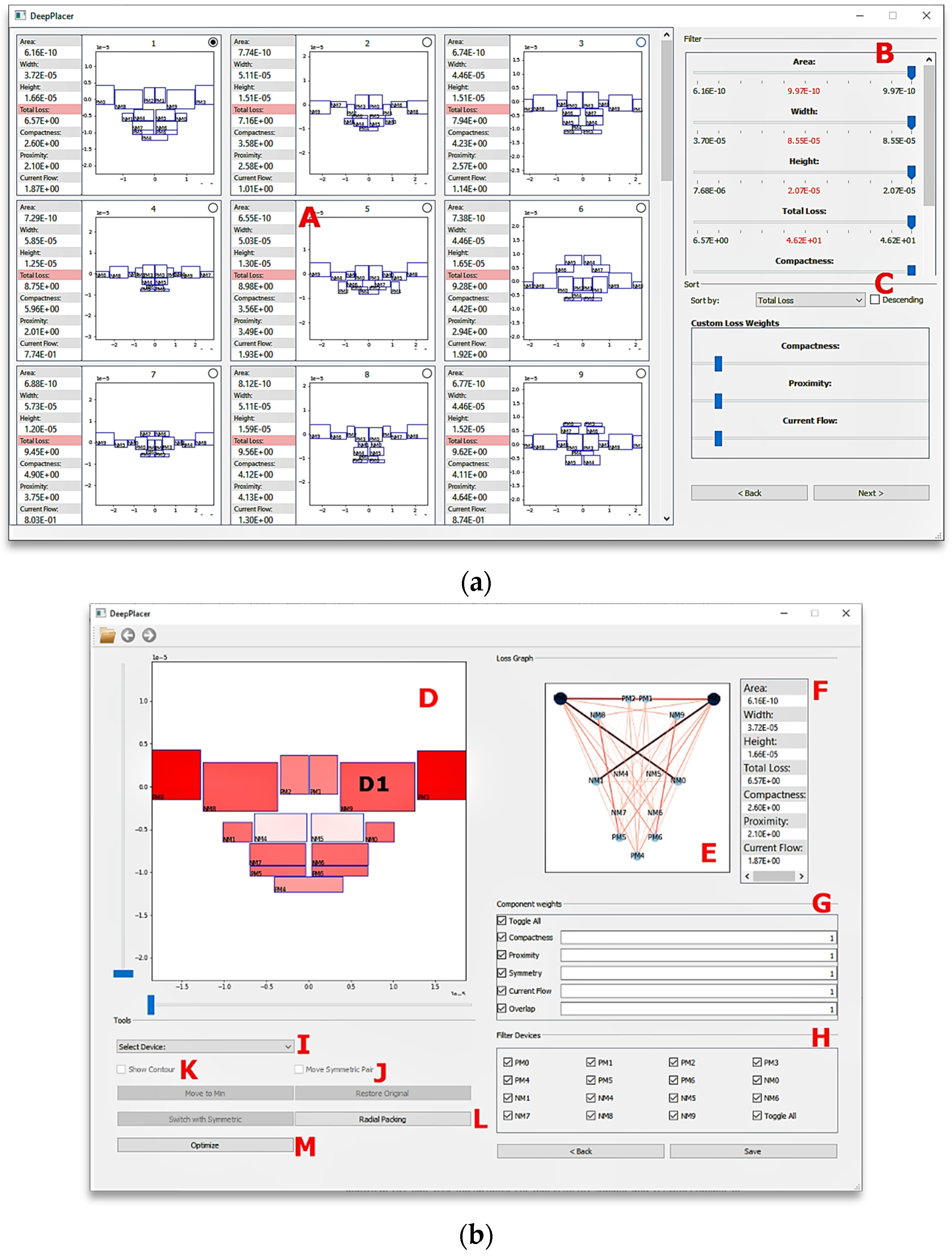

3.4. Graphical User Interface

3.5. Applicability

4. Results

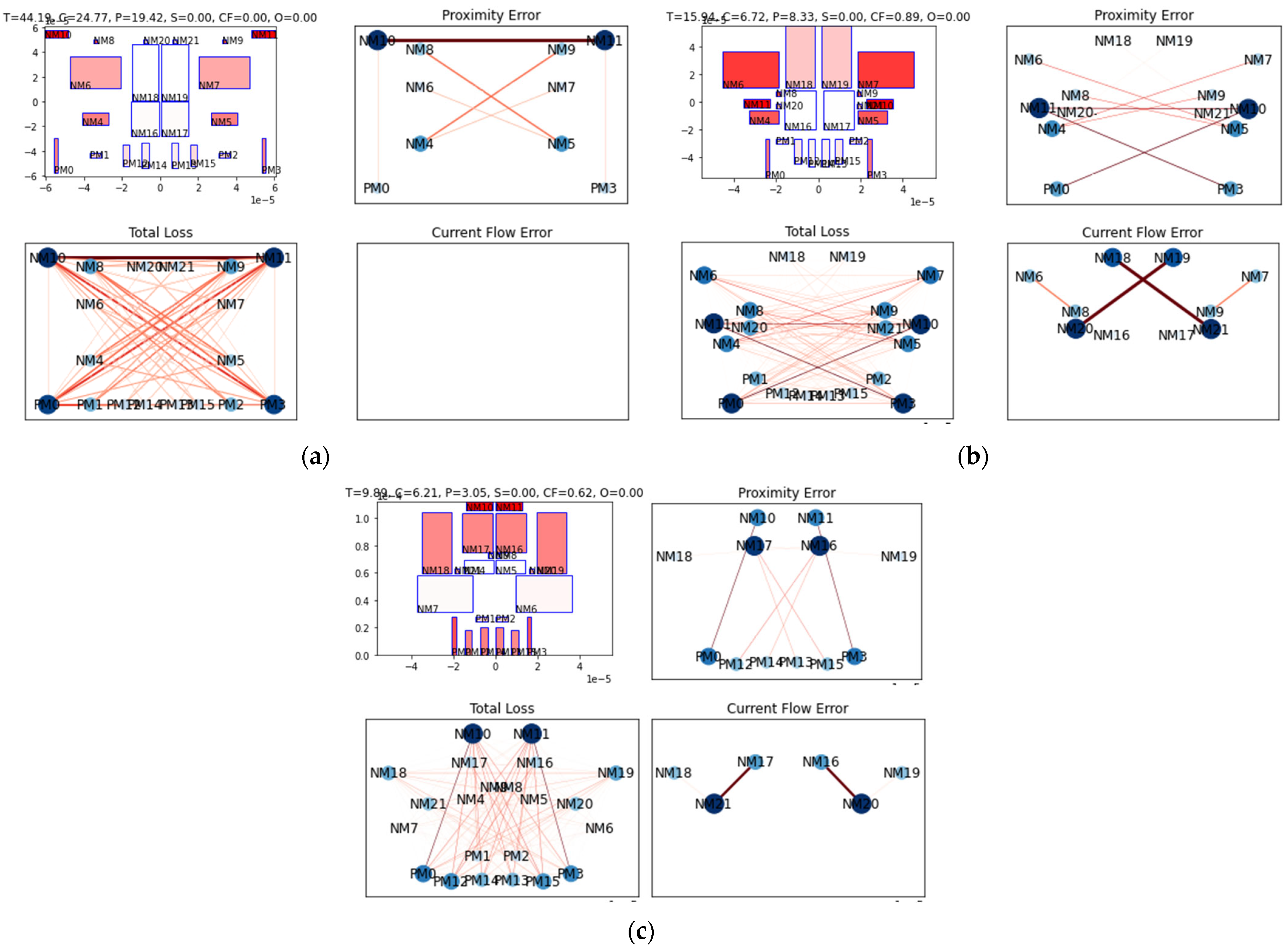

4.1. Current Starving Single-Stage Amplifier biased by Voltage-Combiners

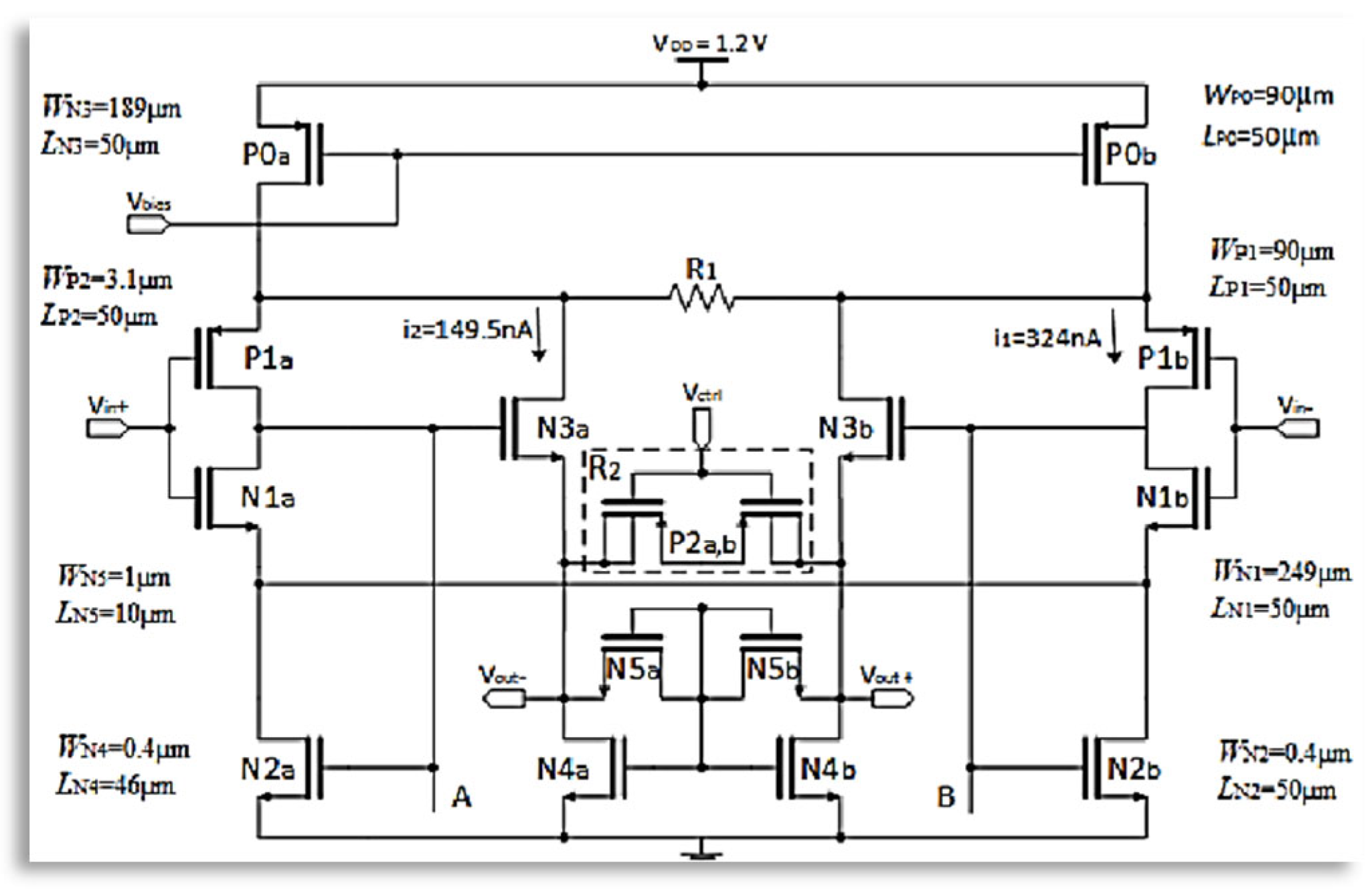

4.2. Low-Power Low-Noise Amplifier

5. Discussion

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Graeb, H.E. Analog Layout Synthesis: A Survey of Topological Approaches, 1st ed.; Springer: New York, NY, USA, 2011. [Google Scholar] [CrossRef]

- Lin, P.-H.; Chang, Y.-W.; Hung, C.-M. Recent Research Development and New Challenges in Analog Layout Synthesis. In Proceedings of the Asia and South Pacific Design Automation Conference, Macao, China, 25–28 January 2016. [Google Scholar]

- Patyal, A.; Pan, P.-C.; Asha, K.A.; Chen, H.-M.; Chi, H.-Y.; Liu, C.-N. Analog Placement with Current Flow and Symmetry Constraints Using PCP-SP. In Proceedings of the ACM/ESDA/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 24–28 June 2018. [Google Scholar]

- Zhang, L.; Raut, R.; Jiang, Y.; Kleine, U. Placement Algorithm in Analog-Layout Designs. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2006, 25, 1889–1903. [Google Scholar] [CrossRef]

- Jangkrajarng, N.; Bhattacharya, S.; Hartono, R.; Shi, R. IPRAIL—Intellectual property reuse-based analog IC layout automation. Integr. VSLI 2003, 36, 237–262. [Google Scholar] [CrossRef]

- Valencia-Ponce, M.A.; Tlelo-Cuautle, E.; de la Fraga, L.G. On the Sizing of CMOS Operational Amplifiers by Applying Many-Objective Optimization Algorithms. Electronics 2021, 10, 3148. [Google Scholar] [CrossRef]

- Sanabria-Borbón, A.C.; Soto-Aguilar, S.; Estrada-López, J.J.; Allaire, D.; Sánchez-Sinencio, E. Gaussian-Process-Based Surrogate for Optimization-Aided and Process-Variations-Aware Analog Circuit Design. Electronics 2020, 9, 685. [Google Scholar] [CrossRef]

- Wu, P.; Lin, M.; Chen, T.; Yeh, C.; Li, X.; Ho, T. A novel analog physical synthesis methodology integrating existent design expertise. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2015, 34, 199–212. [Google Scholar] [CrossRef]

- Cadence’s Virtuoso Layout L/XL/GXL. Available online: http://www.cadence.com (accessed on 5 July 2022).

- Fayazi, M.; Colter, Z.; Afshari, E.; Dreslinski, R. Applications of Artificial Intelligence on the Modeling and Optimization for Analog and Mixed-Signal Circuits: A Review. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2418–2431. [Google Scholar] [CrossRef]

- Mina, R.; Jabbour, C.; Sakr, G.E. A Review of Machine Learning Techniques in Analog Integrated Circuit Design Automation. Electronics 2022, 11, 435. [Google Scholar] [CrossRef]

- Takai, N.; Fukuda, M. Prediction of Element Values of OPAmp for Required Specifications Utilizing Deep Learning. In Proceedings of the International Symposium on Electronics and Smart Devices (ISESD), Yogyakarta, Indonesia, 17–19 October 2017. [Google Scholar]

- Islamoǧlu, G.; Çakici, T.; Afacan, E.; Dündar, G. Artificial Neural Network Assisted Analog IC Sizing Tool. In Proceedings of the 16th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design, Lausanne, Switzerland, 15–18 July 2019. [Google Scholar]

- Kunal, K.; Dhar, T.; Madhusudan, M.; Poojary, J.; Sharma, A.; Xu, W.; Burns, S.M.; Hu, J.; Harjani, R.; Sapatnekar, S.S. GANA: Graph Convolutional Network Based Automated Netlist Annotation for Analog Circuits. In Proceedings of the Design, Automation and Test in Europe Conference and Exhibition, Grenoble, France, 9–13 March 2020. [Google Scholar]

- Guerra, D.; Canelas, A.; Póvoa, R.; Horta, N.; Lourenço, N.; Martins, R. Artificial Neural Networks as an Alternative for Automatic Analog IC Placement. In Proceedings of the 16th International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design, Lausanne, Switzerland, 15–18 July 2019. [Google Scholar]

- Zhu, K.; Liu, M.; Lin, Y.; Xu, B.; Li, S.; Tang, X.; Sun, N.; Pan, D.Z. Genius Route: A New Analog Routing Paradigm Using Generative Neural Network Guidance. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, Westminster, CO, USA, 4–7 November 2019. [Google Scholar]

- Kunal, K.; Poojary, J.; Dhar, T.; Madhusudan, M.; Harjani, R.; Sapatnekar, S.S. A General Approach for Identifying Hierarchical Symmetry Constraints for Analog Circuit Layout. In Proceedings of the 39th International Conference on Computer-Aided Design, New York, NY, USA, 2–5 November 2020. [Google Scholar]

- Liu, M.; Wu, L.; Zhu, K.; Xu, B.; Lin, Y.; Shen, L.; Tang, X.; Sun, N.; Pan, D.Z. S3DET: Detecting System Symmetry Constraints for Analog Circuits with Graph Similarity. In Proceedings of the 25th Asia and South Pacific Design Automation Conference, Beijing, China, 13–16 January 2020. [Google Scholar]

- Xu, B.; Lin, Y.; Tang, X.; Li, S.; Shen, L.; Sun, N.; Pan, D.Z. Well GAN: Generative-Adversarial-Network-Guided Well Generation for Analog/Mixed-Signal Circuit Layout. In Proceedings of the 56th ACM/IEEE Design Automation Conference, Las Vegas, NV, USA, 2–6 June 2019. [Google Scholar]

- He, R.; Zhang, L. Artificial Neural Network Application in Analog Layout Placement Design. In Proceedings of the Canadian Conference on Electrical and Computer Engineering, St. John’s, NL, Canada, 3–6 May 2009. [Google Scholar]

- Gusmão, A.; Passos, F.; Póvoa, R.; Horta, N.; Lourenço, N.; Martins, R. Semi-Supervised Artificial Neural Networks towards Analog IC Placement Recommender. In Proceedings of the IEEE International Symposium on Circuits and Systems, Seville, Spain, 12–14 October 2020. [Google Scholar]

- Gusmão, A.; Horta, N.; Lourenço, N.; Martins, R. Scalable and Order Invariant Analog Integrated Circuit Placement with Attention-Based Graph-to-Sequence Deep Models. Expert Syst. Appl. 2022, 207, 117954. [Google Scholar] [CrossRef]

- Póvoa, R.; Lourenço, N.; Martins, R.; Canelas, A.; Horta, N.; Goes, J. Single-Stage OTA Biased by Voltage-Combiners with Enhanced Performance Using Current Starving. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1599–1603. [Google Scholar] [CrossRef]

- Eick, M.; Strasser, M.; Lu, K.; Schlichtmann, U.; Graeb, H. Comprehensive Generation of Hierachical Placement Rules for Analog Integrated Circuits. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2011, 30, 180–193. [Google Scholar] [CrossRef]

- Eick, M.; Graeb, H. MARS: Matching-Driven Analog Sizing. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2013, 31, 1145–1158. [Google Scholar] [CrossRef]

- Vieira, R.; Martins, R.; Horta, N.; Lourenço, N.; Póvoa, R. A Sub-1muA Low-Power Low-Noise Amplifier with Tunable Gain and Bandwidth for EMG and EOG Biopotential Signals. In Proceedings of the International Conference on Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design, Erfurt, Germany, 19–22 July 2021. [Google Scholar]

| Placement | Compactness | Comp. | Proximity | Comp. | Current-Flow | Total Error | Comp. |

|---|---|---|---|---|---|---|---|

| Virtuoso XL | 24.77 | 3.99× | 19.42 | 6.37× | 0.00 | 44.19 | 4.47× |

| Human [23] | 6.72 | 1.08× | 8.33 | 2.73× | 0.89 | 15.94 | 1.61× |

| This Work | 6.21 | - | 3.05 | - | 0.62 | 9.89 | - |

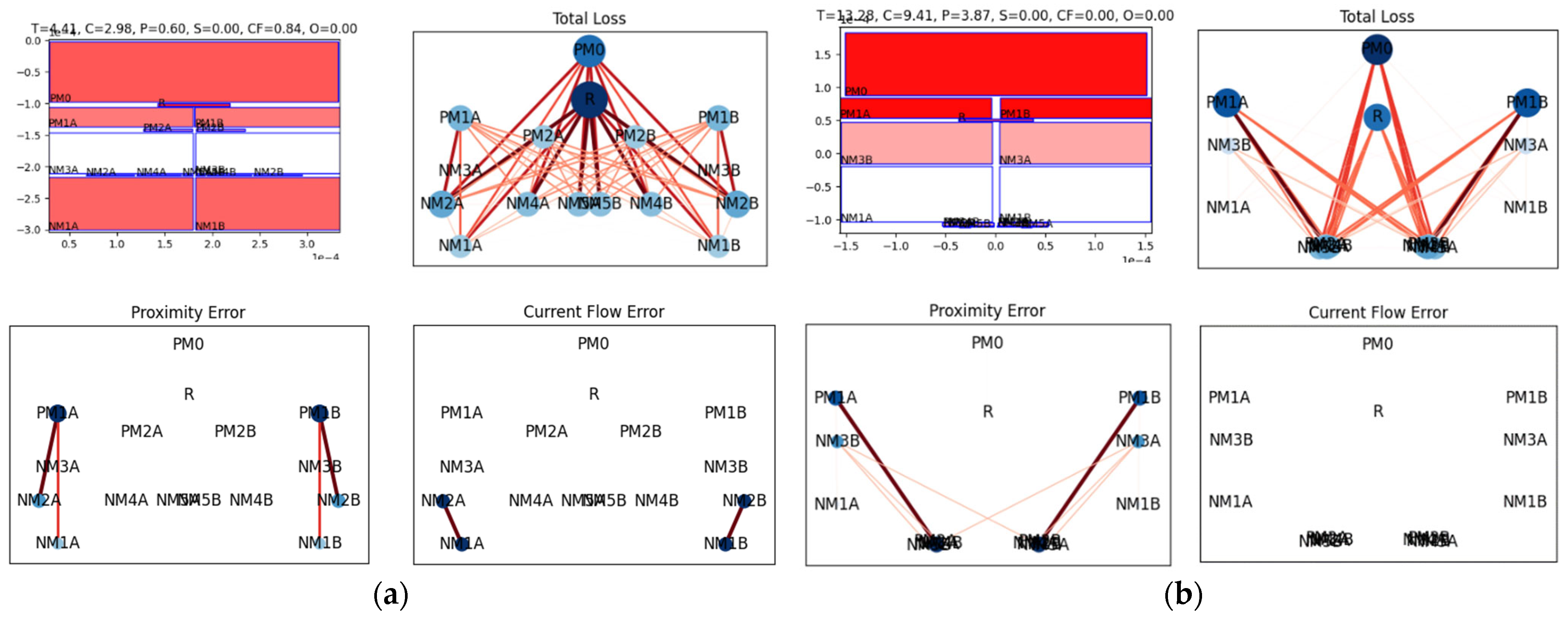

| Placement | Compactness | Comp. | Proximity | Comp. | Current-Flow | Total Error | Comp. |

|---|---|---|---|---|---|---|---|

| Human [26] | 2.98 | - | 0.6 | - | 0.84 | 4.41 | |

| This Work | 9.41 | 3.16× | 3.87 | 6.45× | 0.00 | 13.28 | 3.01× |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gusmão, A.; Vieira, R.; Horta, N.; Lourenço, N.; Martins, R. Exploiting a Deep Learning Toolbox for Human-Machine Feedback towards Analog Integrated Circuit Placement Automation. Electronics 2022, 11, 3964. https://doi.org/10.3390/electronics11233964

Gusmão A, Vieira R, Horta N, Lourenço N, Martins R. Exploiting a Deep Learning Toolbox for Human-Machine Feedback towards Analog Integrated Circuit Placement Automation. Electronics. 2022; 11(23):3964. https://doi.org/10.3390/electronics11233964

Chicago/Turabian StyleGusmão, António, Rafael Vieira, Nuno Horta, Nuno Lourenço, and Ricardo Martins. 2022. "Exploiting a Deep Learning Toolbox for Human-Machine Feedback towards Analog Integrated Circuit Placement Automation" Electronics 11, no. 23: 3964. https://doi.org/10.3390/electronics11233964

APA StyleGusmão, A., Vieira, R., Horta, N., Lourenço, N., & Martins, R. (2022). Exploiting a Deep Learning Toolbox for Human-Machine Feedback towards Analog Integrated Circuit Placement Automation. Electronics, 11(23), 3964. https://doi.org/10.3390/electronics11233964