A Single-Event Burnout Hardened Super-Junction Trench SOI LDMOS with Additional Hole Leakage Paths

Abstract

1. Introduction

2. Device Structure and Simulation Setup

3. Simulation Results and Discussion

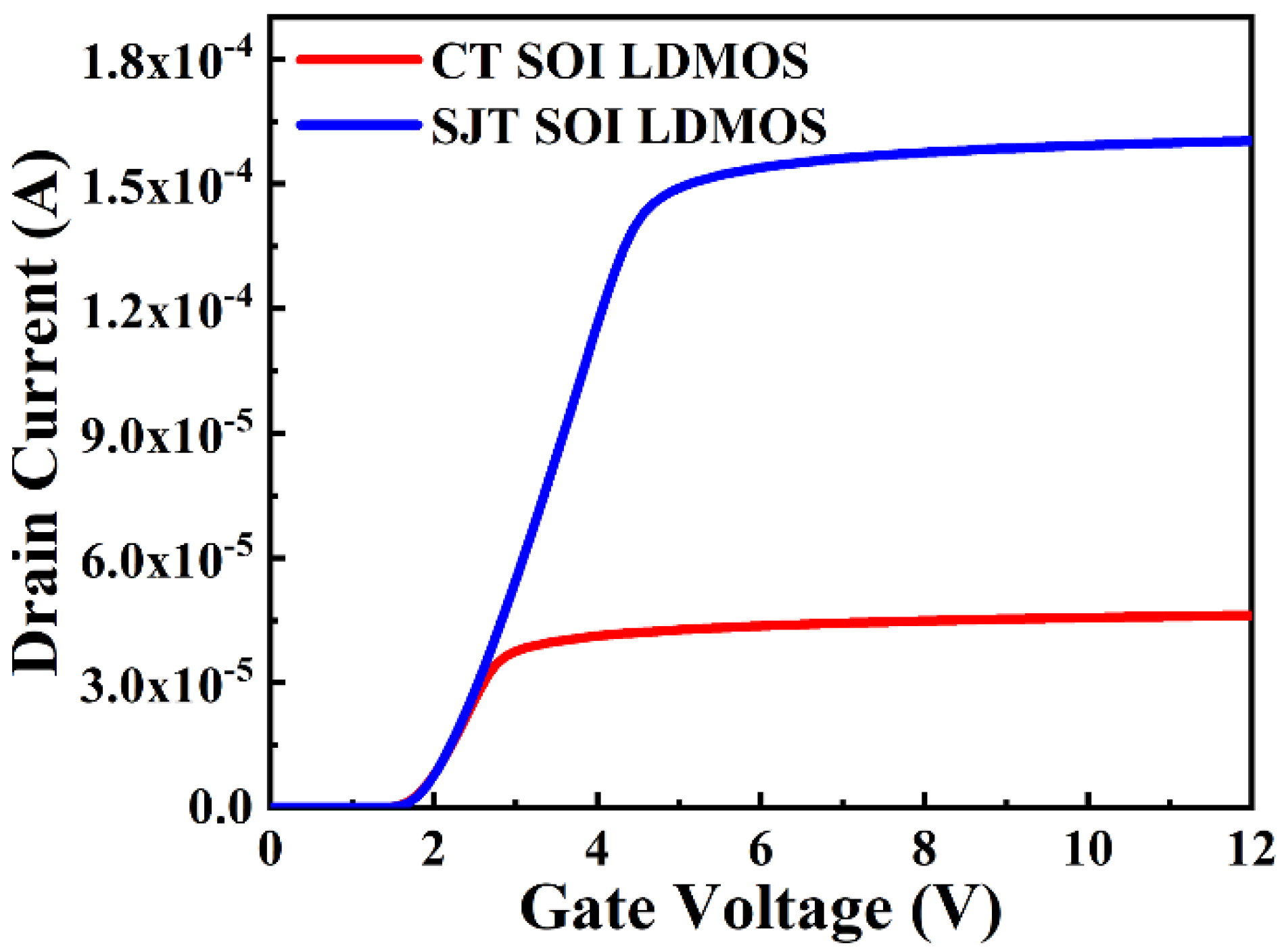

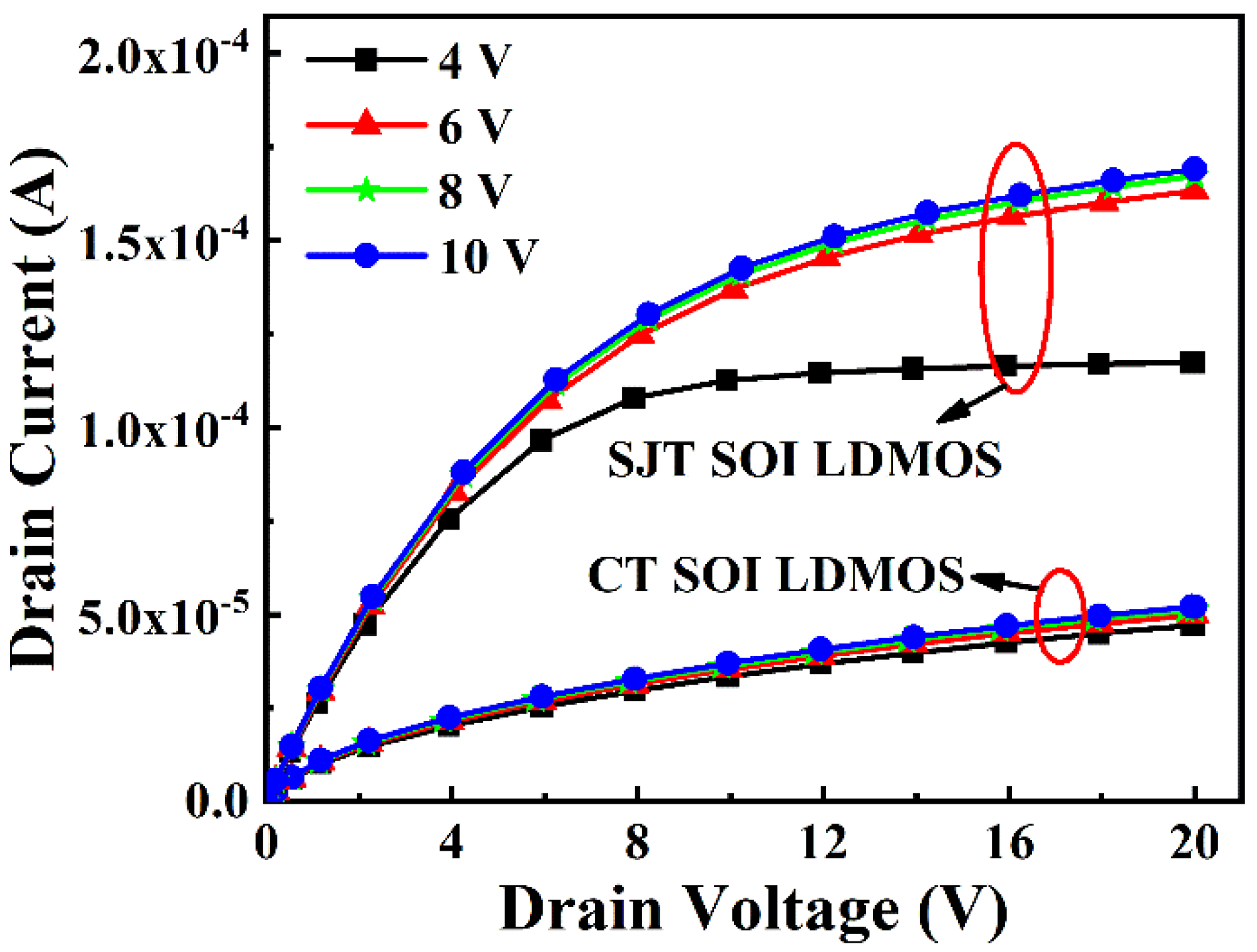

3.1. Basic Electrical Characteristics

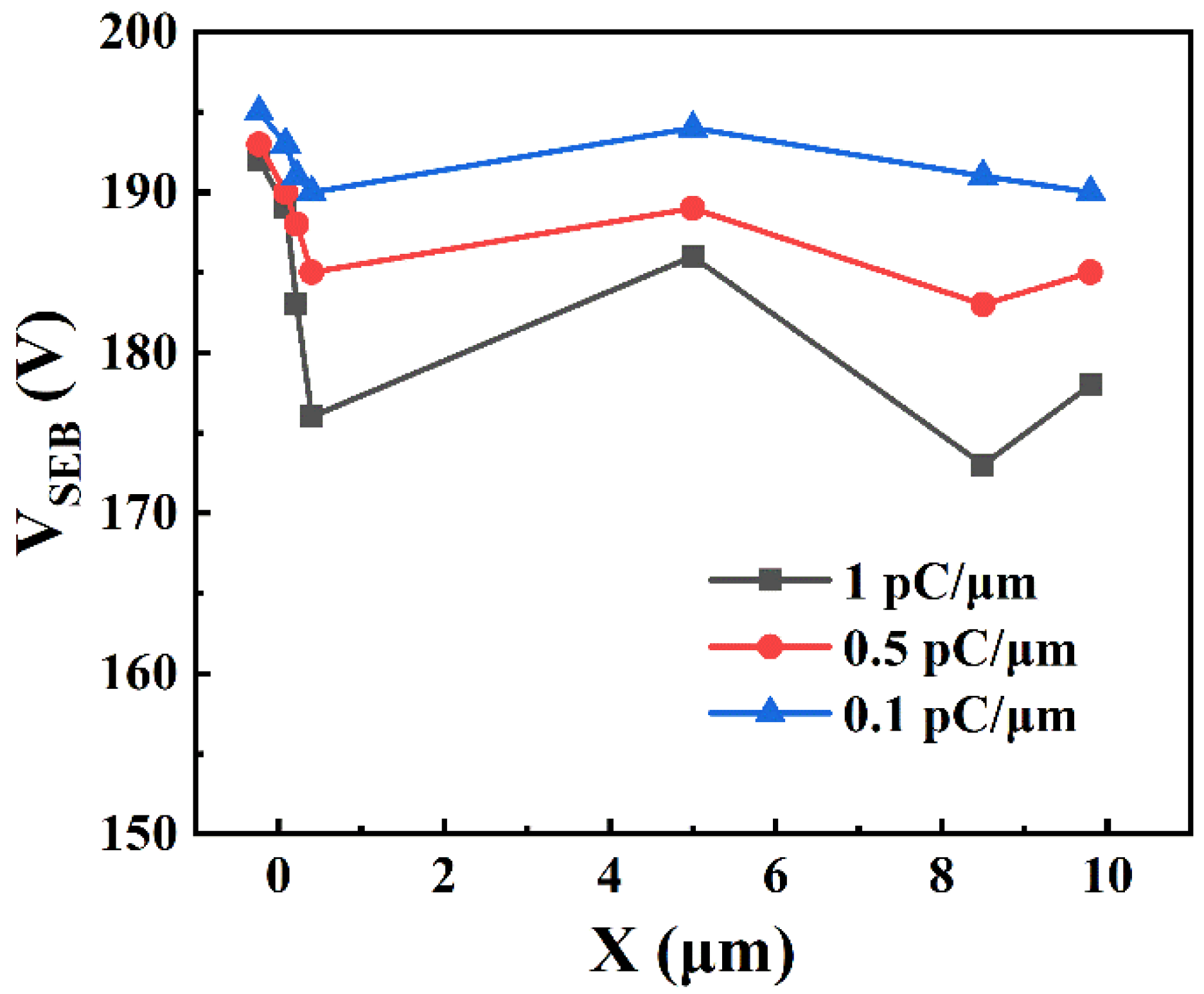

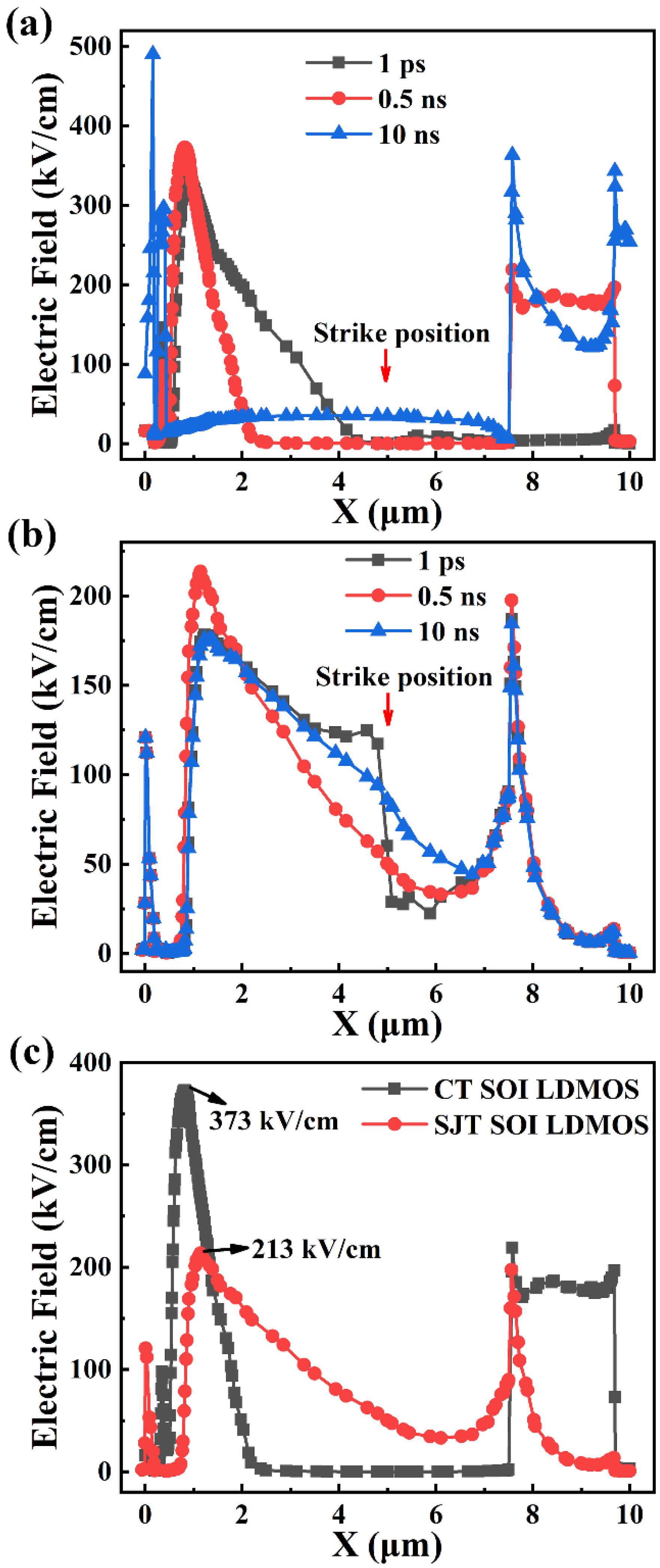

3.2. Single-Event Burnout Performance

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Barth, J.L.; Dyer, C.S.; Stassinopoulos, E.G. Space, atmospheric, and terrestrial radiation environments. IEEE Trans. Nucl. Sci. 2003, 50, 466–482. [Google Scholar] [CrossRef]

- Stassinopoulos, E.G.; Raymond, J.P. The space radiation environment for electronics. Proc. IEEE 1988, 76, 1423–1442. [Google Scholar] [CrossRef]

- Wang, Y.; Zhang, Y.; Wang, L.G.; Yu, C. Single-event burnout hardening of power UMOSFETs with optimized structure. IEEE Trans. Electron Devices 2013, 60, 2001–2007. [Google Scholar] [CrossRef]

- Sexton, F.W. Destructive single-event effects in semiconductor devices and ICs. IEEE Trans. Nucl. Sci. 2003, 50, 603–621. [Google Scholar] [CrossRef]

- Dodd, P.E.; Shaneyfelt, M.R.; Draper, B.L.; Young, R.W.; Savignon, D.; Witcher, J.B.; Vizkelethy, G.; Schwank, J.R.; Shen, Z.J.; Shea, P.; et al. Development of a radiation-hardened lateral power MOSFET for POL applications. IEEE Trans. Nucl. Sci. 2009, 56, 3456–3462. [Google Scholar] [CrossRef]

- Titus, J.L.; Johnson, G.H.; Schrimpf, R.D.; Galloway, K.F. Single-event burnout of power bipolar junction transistors. IEEE Trans. Nucl. Sci. 1991, 38, 1315–1322. [Google Scholar] [CrossRef]

- Waskiewicz, A.E.; Groninger, J.W.; Strahan, V.H.; Long, D.M. Burnout of power MOS transistors with heavy-ions of californium-252. IEEE Trans. Nucl. Sci. 1986, 33, 1710–1713. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, L.; Guo, M.; Chen, R.; Wang, S.; Jiang, Y. Research of single event burnout in a high-performance radiation-hardened SOI lateral power MOSFET. Microelectron. Reliab. 2022, 129, 114475. [Google Scholar] [CrossRef]

- Liu, S.; Titus, J.L.; Boden, M. Effect of buffer layer on single-event burnout of power DMOSFETs. IEEE Trans. Nucl. Sci. 2007, 54, 2554–2560. [Google Scholar] [CrossRef]

- Dachs, C.; Roubaud, F.; Palau, J.M.; Bruguier, G.; Gasiot, J.; Tastet, P.; Calvett, M.C.; Calvel, P. Simulation aided hardening of N-channel power MOSFETs to prevent single event burnout. IEEE Trans. Nucl. Sci. 1995, 42, 1935–1939. [Google Scholar] [CrossRef]

- Yu, C.H.; Wang, Y.; Cao, F.; Huang, L.L.; Wang, Y.Y. Research of single-event burnout in power planar VDMOSFETs by localized carrier lifetime control. IEEE Trans. Electron Devices 2015, 62, 143–148. [Google Scholar]

- Wang, Y.; Zhang, Y.; Cao, F.; Shan, M.G. Single-event burnout hardened structure of power UMOSFETs with Schottky source. IEEE Trans. Power Electron. 2014, 29, 3733–3737. [Google Scholar] [CrossRef]

- Wan, X.; Zhou, W.S.; Ren, S.; Liu, D.G.; Xu, J.; Bo, H.L.; Zhang, E.X.; Schrimpf, R.D.; Fleetwood, D.M.; Ma, T.P. SEB hardened power MOSFETs with high-K dielectrics. IEEE Trans. Nucl. Sci. 2015, 62, 2830–2836. [Google Scholar] [CrossRef]

- Stork, J.M.C.; Hosey, G.P. SOI technology for power management in automotive and industrial applications. Solid-State Electron. 2017, 128, 3–9. [Google Scholar] [CrossRef]

- Shea, P.M.; Shen, Z.J. Numerical and experimental investigation of single event effects in SOI lateral power MOSFETs. IEEE Trans. Nucl. Sci. 2011, 58, 2739–2747. [Google Scholar] [CrossRef]

- Shu, L.; Qi, C.H.; Galloway, K.F.; Zhao, Y.F.; Cao, W.Y.; Li, X.J.; Wang, L.; Zhang, E.X.; Wang, X.S.; Shi, R.X.; et al. Observation of single event burnout (SEB) in an SOI NLDMOSFET using a pulsed laser. Microelectron. Reliab. 2021, 116, 113997. [Google Scholar] [CrossRef]

- Wang, Y.; Meng, X.F.; Tang, P.P.; Cui, S.F. Analytical model and optimization for variable drift region width SOI LDMOS device. IEEE Trans. Electron Devices 2016, 63, 4352–4358. [Google Scholar] [CrossRef]

- Luo, X.; Lei, T.F.; Wang, Y.G.; Yao, G.L.; Jiang, Y.H.; Zhou, K.; Wang, P.; Zhang, Z.Y.; Fan, J.; Wang, Q.; et al. Low on-resistance SOI dual-trench-gate MOSFET. IEEE Trans. Electron Devices 2012, 59, 504–509. [Google Scholar] [CrossRef]

- Disney, D.; Chan, W.; Lam, R.; Blattner, R.; Ma, S.; Seng, W.; Chen, J.W.; Cornell, M.; Williams, R. 60V lateral trench MOSFET in 0.35 μm technology. In Proceedings of the 2008 20th International Symposium on Power Semiconductor Devices and IC’s, Orlando, FL, USA, 18–22 May 2008. [Google Scholar]

- Fujishima, N.; Sugi, A.; Kajiwara, S.; Matsubara, K.; Nagayasu, Y.; Salama, C.A.T. A high-density low on-resistance trench lateral power MOSFET with a trench bottom source contact. IEEE Trans. Electron Devices 2002, 49, 1462–1468. [Google Scholar] [CrossRef]

- Park, I.Y.; Salama, C.A.T. New-superjunction LDMOST with N-buffer layer. IEEE Trans. Electron Devices 2006, 53, 1909–1913. [Google Scholar] [CrossRef]

- Zhang, B.; Wang, W.; Chen, W.; Li, Z.; Li, Z. High-voltage LDMOS with charge-balanced surface low on-resistance path layer. IEEE Electron Device Lett. 2009, 30, 849–851. [Google Scholar] [CrossRef]

- Wang, Y.; Wang, Z.; Bai, T.; Kuo, J.B. Modeling of breakdown voltage for SOI trench LDMOS device based on conformal mapping. IEEE Trans. Electron Devices 2018, 65, 1056–1062. [Google Scholar] [CrossRef]

- Huang, S.; Amaratunga, G.A.J.; Udrea, F. Analysis of SEB and SEGR in super-junction MOSFETs. IEEE Trans. Nucl. Sci. 2000, 47, 2640–2647. [Google Scholar] [CrossRef]

- TCAD. Available online: https://www.synopsys.com/ (accessed on 6 August 2022).

- Luu, A.; Austin, P.; Miller, F.; Buard, N.; Carrière, T.; Poirot, P.; Gaillard, R.; Bafleur, M.; Sarrabayrouse, G. Sensitive volume and triggering criteria of SEB in classic planar VDMOS. IEEE Trans. Nucl. Sci. 2010, 57, 1900–1907. [Google Scholar] [CrossRef]

- Haynes, R.H.; Dolphin, G.W. The calculation of linear energy transfer, with special reference to a 14 MeV electron beam and 10 MeV per nucleon ion beams. Phys. Med. Biol. 1959, 4, 148–158. [Google Scholar] [CrossRef] [PubMed]

- Luo, X.; Wang, Y.; Hao, Y.; Li, X.; Liu, C.M.; Fei, X.X.; Yu, C.H.; Cao, F. Research of single-event burnout and hardening of AlGaN/GaN-based MISFET. IEEE Trans. Electron Devices 2019, 66, 1118–1122. [Google Scholar] [CrossRef]

- Dachs, C.; Roubaud, F.; Palau, J.M.; Bruguier, G.; Gasiot, J.; Tastet, P. Evidence of the ion’s impact position effect on SEB in N-channel power MOSFETs. IEEE Trans. Nucl. Sci. 1994, 41, 2167–2171. [Google Scholar] [CrossRef]

- Zhou, X.; Tang, Y.; Jia, Y.; Hu, D.; Wu, Y.; Xia, T.; Gong, H.; Pang, H. Single-event effects in SiC double-trench MOSFETs. IEEE Trans. Nucl. Sci. 2019, 66, 2312–2318. [Google Scholar] [CrossRef]

- Roubaud, F.; Dachs, C.; Palau, J.M.; Gasiot, J.; Tastet, P. Experimental and 2D simulation study of the single-event burnout in N-channel power MOSFETs. IEEE Trans. Nucl. Sci. 1993, 40, 1952–1958. [Google Scholar] [CrossRef]

- Miller, F.; Luu, A.; Prud’homme, F.; Poirot, P.; Gaillard, R.; Buard, N.; Carriere, T. Characterization of single-event burnout in power MOSFET using backside laser testing. IEEE Trans. Nucl. Sci. 2006, 53, 3145–3152. [Google Scholar] [CrossRef]

- Wrobel, T.F.; Beutler, D.E. Solutions to heavy ion induced avalanche burnout in power devices. IEEE Trans. Nucl. Sci. 1992, 39, 1636–1641. [Google Scholar] [CrossRef]

- Zhou, X.; Jia, Y.; Hu, D.; Wu, Y. A simulation-based comparison between Si and SiC MOSFETs on single-event burnout susceptibility. IEEE Trans. Electron Devices 2019, 66, 2551–2556. [Google Scholar] [CrossRef]

- Oberg, D.L.; Wert, J.L.; Normand, E.; Majewski, P.P.; Wender, S.A. First observations of power MOSFET burnout with high energy neutrons. IEEE Trans. Nucl. Sci. 1996, 43, 2913–2920. [Google Scholar] [CrossRef]

- Pendharkar, S.; Efland, T.; Tsai, C.Y. Analysis of high current breakdown and UIS behavior of Resurf LDMOS (RLDMOS) devices. In Proceedings of the 10th International Symposium on Power Semiconductor Devices and ICs. ISPSD’98 (IEEE Cat. No.98CH36212), Kyoto, Japan, 3–6 June 1998. [Google Scholar]

| Device Parameter | CT SOI LDMOS | SJT SOI LDMOS |

|---|---|---|

| Cell pitch | 10 μm | 10.4 μm |

| Trench width | 0.15 μm | 0.15 μm |

| Trench depth | 0.48 μm | 0.48 μm |

| Gate oxide wall thickness | 30 nm | 30 nm |

| Gate oxide bottom thickness | 0.1 μm | 0.1 μm |

| P pillar thickness | - | 0.42 μm |

| N pillar thickness | - | 0.46 μm |

| Buried oxide (BOX) layer thickness | 1.26 μm | 1.26 μm |

| P pillar doping | - | 6 × 1016 cm−3 |

| N pillar doping | - | 7 × 1016 cm−3 |

| N drift region doping | 1.7 × 1016 cm−3 | - |

| P+ region doping | - | 4 × 1017 cm−3 |

| P+ region width | - | 0.3 μm |

| P+ region depth | - | 0.4 μm |

| P+ region trench source depth | - | 0.13 μm |

| P buried region doping | - | 4 × 1017 cm−3 |

| P buried region depth | - | 0.88 μm |

| P buried region width | - | 0.43 μm |

| P buried region trench source depth | - | 0.7 μm |

| N+ source doping | 1.8 × 1018 cm−3 | 1.8 × 1018 cm−3 |

| P well region doping | 2 × 1017 cm−3 | 2 × 1017 cm−3 |

| N+ drain doping | 6 × 1017 cm−3 | 6 × 1017 cm−3 |

| Substrate doping | 5 × 1018 cm−3 | 5 × 1018 cm−3 |

| Parameter | Value |

|---|---|

| Track radius ω0 | 0.05 μm |

| Temporal Gaussian function width Tc | 2 ps |

| Initial charge generation time T0 | 0.1 ps |

| Track length l0 | 2.14 μm |

| Linear energy transfer (LET) | 1 pC/μm (96 MeV·cm2/mg) |

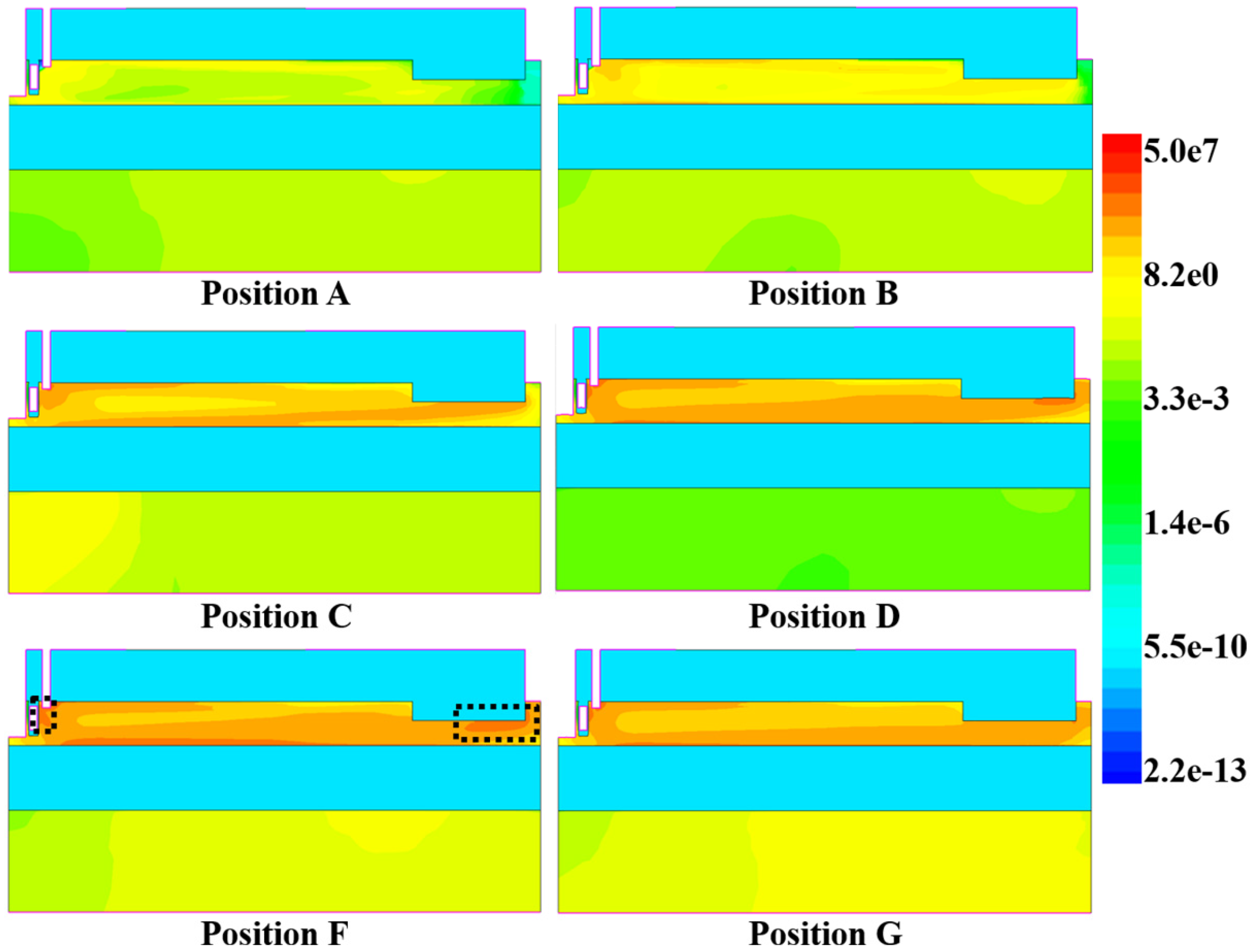

| Strike Positions | CT SOI LDMOS (V) | SJT SOI LDMOS (V) |

|---|---|---|

| Position A | - | 192 |

| Position B | 132 | 189 |

| Position C | 129 | 183 |

| Position D | 142 | 176 |

| Position E | 58 | 186 |

| Position F | 129 | 173 |

| Position G | 129 | 178 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.; Wang, L.; Li, Y.; Cui, M.; Zheng, Z. A Single-Event Burnout Hardened Super-Junction Trench SOI LDMOS with Additional Hole Leakage Paths. Electronics 2022, 11, 3764. https://doi.org/10.3390/electronics11223764

Wang Y, Wang L, Li Y, Cui M, Zheng Z. A Single-Event Burnout Hardened Super-Junction Trench SOI LDMOS with Additional Hole Leakage Paths. Electronics. 2022; 11(22):3764. https://doi.org/10.3390/electronics11223764

Chicago/Turabian StyleWang, Yue, Lixin Wang, Yuanzhe Li, Mengyao Cui, and Zhuoxuan Zheng. 2022. "A Single-Event Burnout Hardened Super-Junction Trench SOI LDMOS with Additional Hole Leakage Paths" Electronics 11, no. 22: 3764. https://doi.org/10.3390/electronics11223764

APA StyleWang, Y., Wang, L., Li, Y., Cui, M., & Zheng, Z. (2022). A Single-Event Burnout Hardened Super-Junction Trench SOI LDMOS with Additional Hole Leakage Paths. Electronics, 11(22), 3764. https://doi.org/10.3390/electronics11223764