Lg = 50 nm Gate-All-Around In0.53Ga0.47As Nanosheet MOSFETs with Regrown In0.53Ga0.47As Contacts

Abstract

:1. Introduction

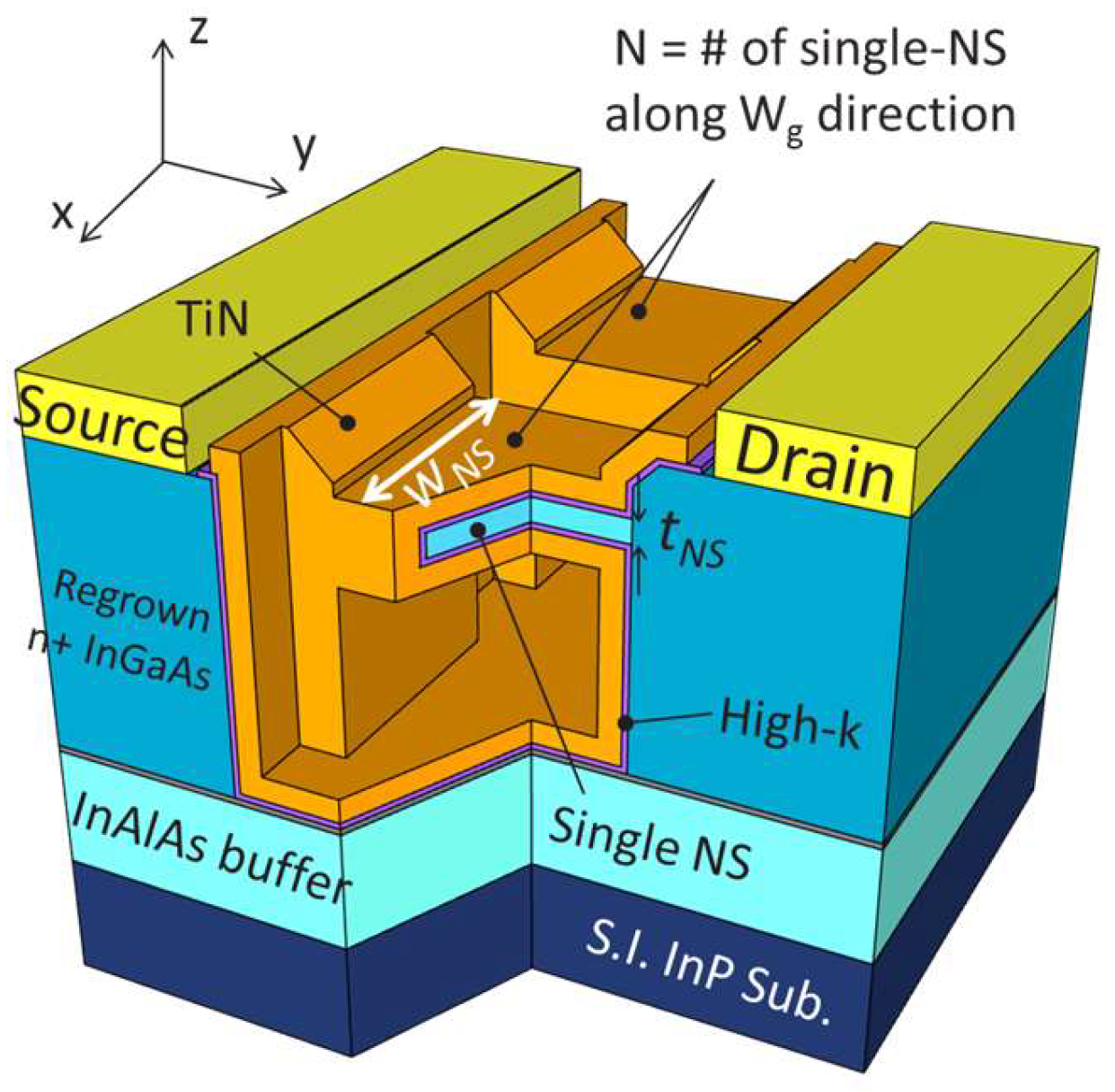

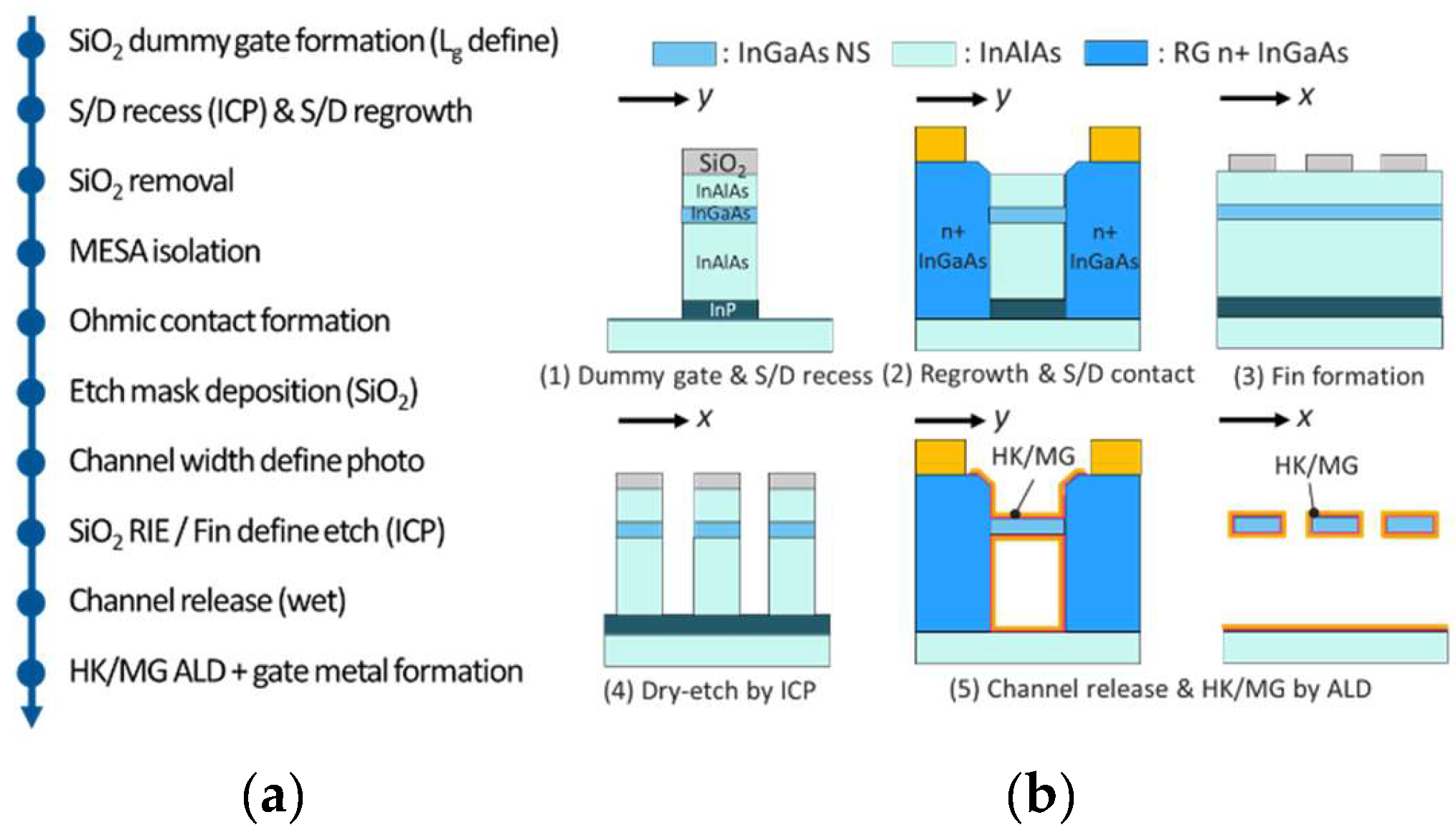

2. Experimental Procedure

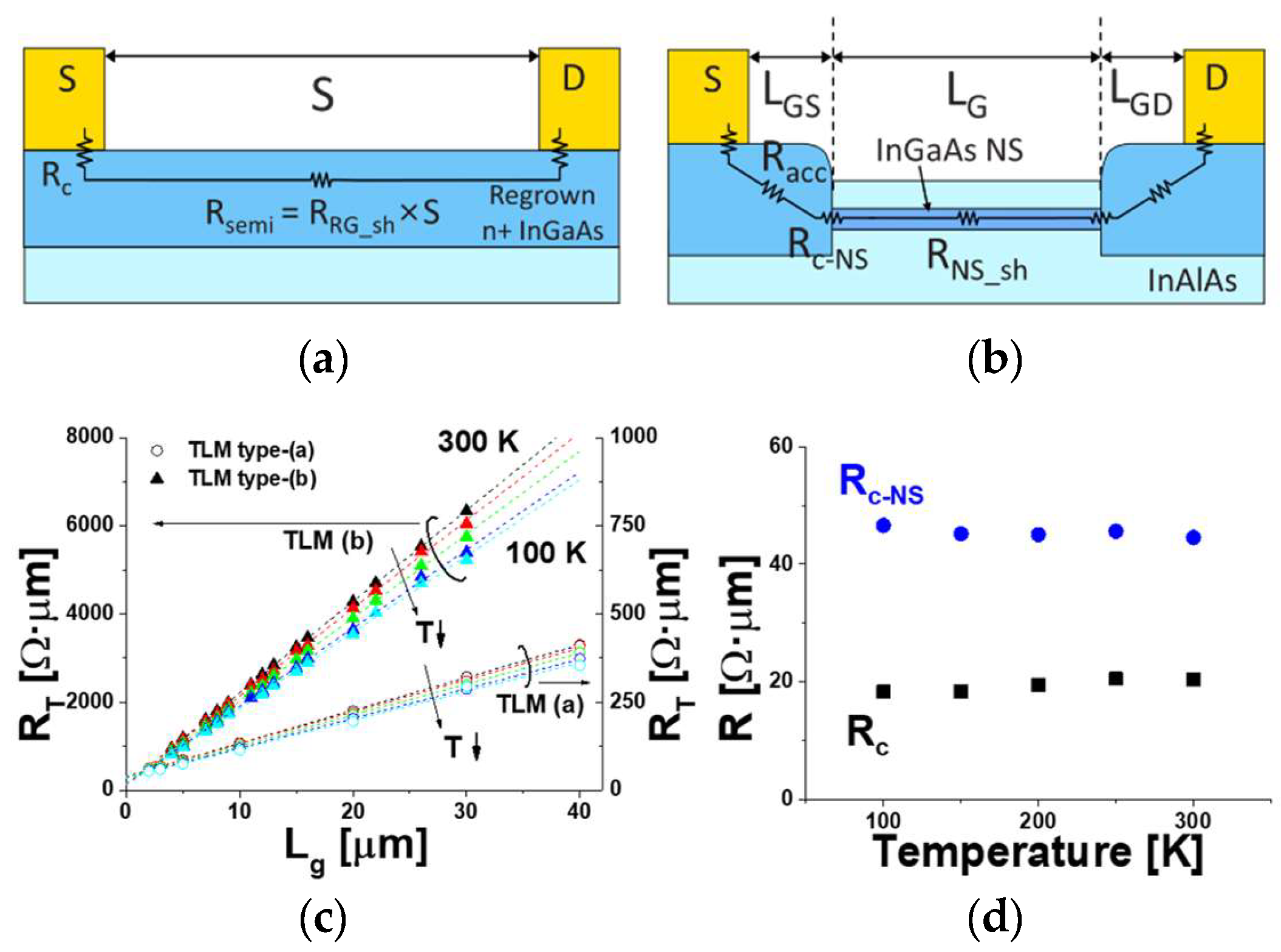

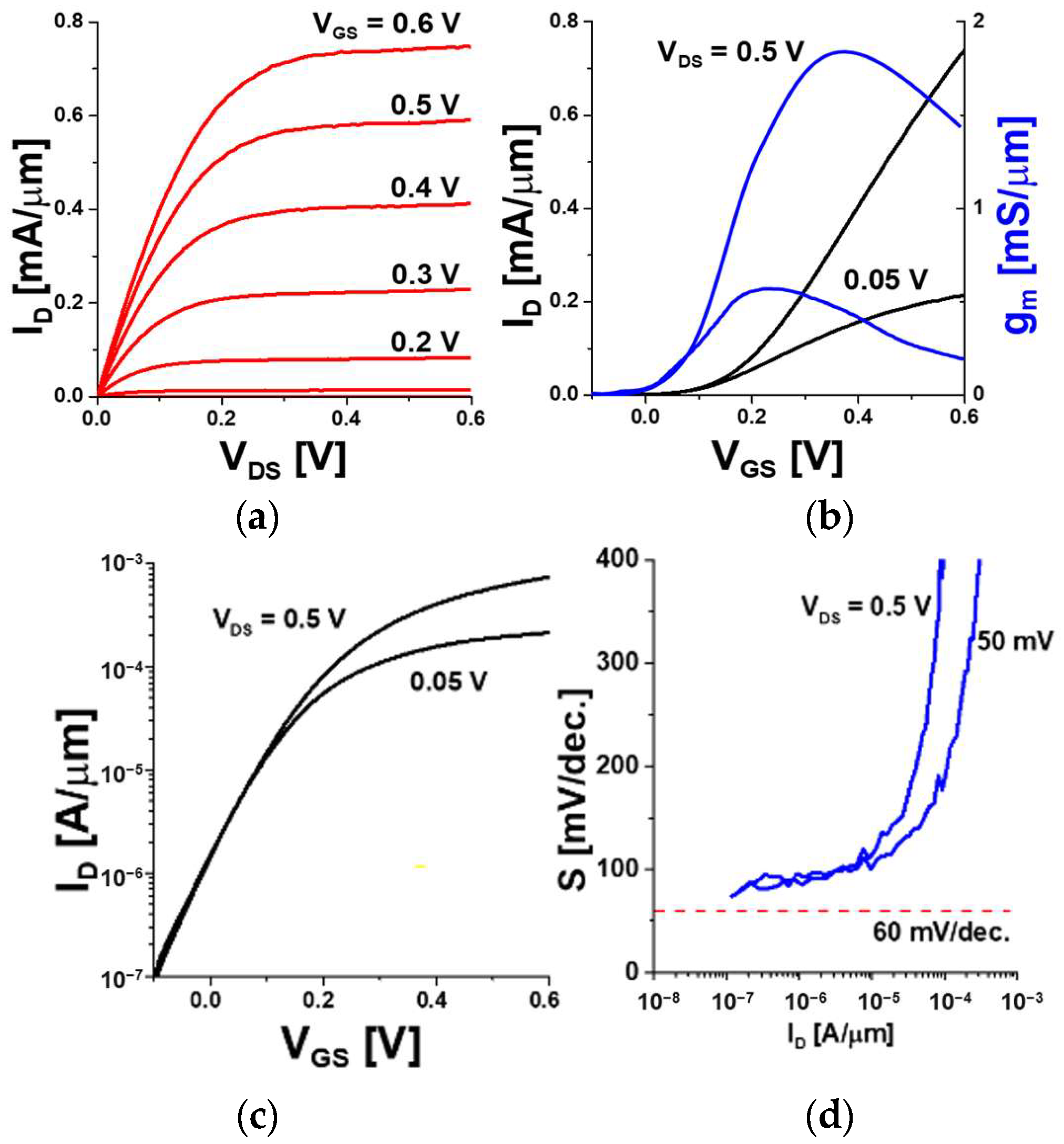

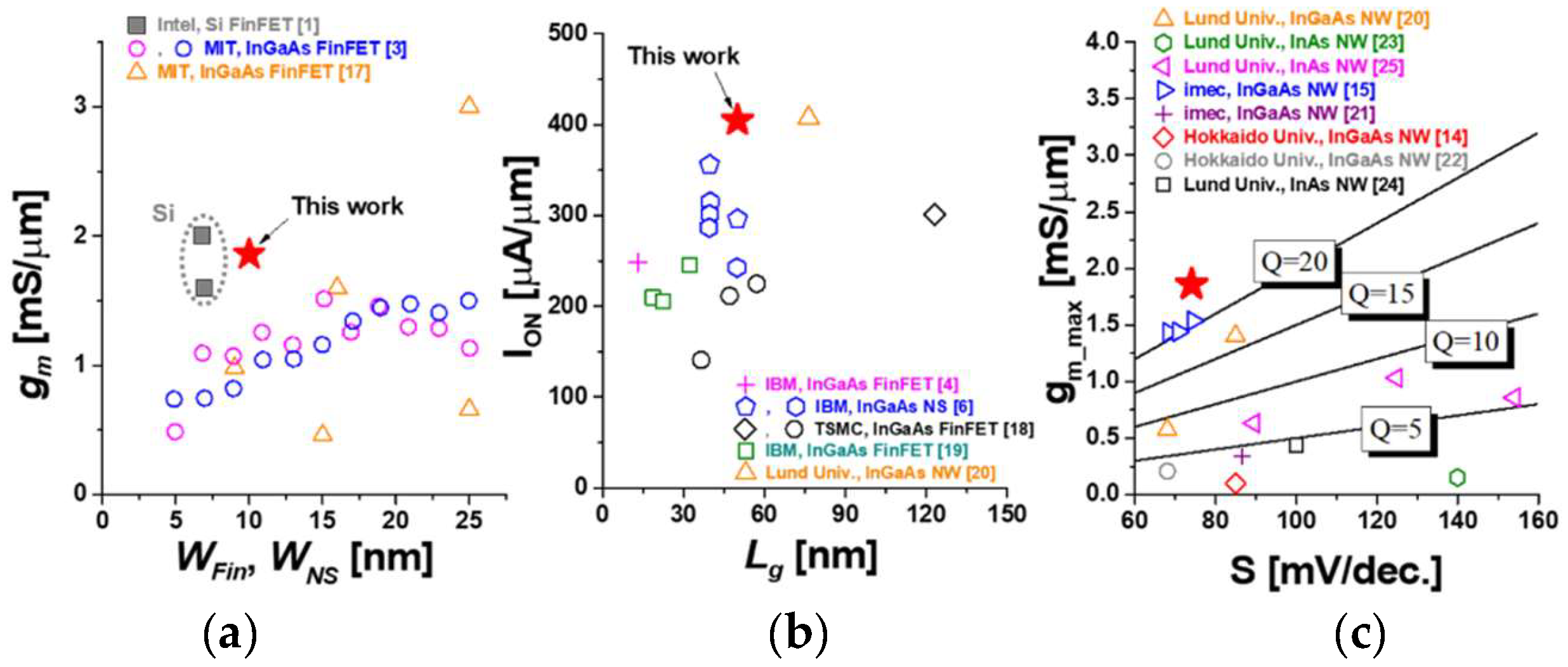

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Auth, C.; Aliyarukunju, A.; Asoro, M.; Bergstrom, D.; Bhagwat, V.; Birdsall, J.; Bisnik, N.; Buehler, M.; Chikarmane, V.; Ding, G.; et al. A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 29.1.1–29.1.4. [Google Scholar]

- Hashemi, P.; Ando, T.; Balakrishnan, K.; Cartier, E.; Lofaro, M.; Ott, J.A.; Bruley, J.; Lee, K.-L.; Koswatta, S.; Dawes, S.; et al. Replacement High-K/Metal-Gate High-Ge-Content Strained SiGe FinFETs with High Hole Mobility and Excellent SS and Reliability at Aggressive EOT ∼7Å and Scaled Dimensions down to Sub-4nm Fin Widths. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Vardi, A.; Kong, L.; Lu, W.; Cai, X.; Zhao, X.; Grajal, J.; del Alamo, J.A. Self-Aligned InGaAs FinFETs with 5-nm Fin-Width and 5-nm Gate-Contact Separation. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 17.6.1–17.6.4. [Google Scholar]

- Hahn, H.; Deshpande, V.; Caruso, E.; Sant, S.; O’Connor, E.; Baumgartner, Y.; Sousa, M.; Caimi, D.; Olziersky, A.; Palestri, P.; et al. A Scaled Replacement Metal Gate InGaAs-on-Insulator n-FinFET on Si with Record Performance. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 17.5.1–17.5.4. [Google Scholar]

- Lu, W.; Roh, I.P.; Geum, D.-M.; Kim, S.-H.; Song, J.D.; Kong, L.; del Alamo, J.A. 10-nm Fin-Width InGaSb p-Channel Self-Aligned FinFETs Using Antimonide-Compatible Digital Etch. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 17.7.1–17.7.4. [Google Scholar]

- Lee, S.; Cheng, C.-W.; Sun, X.; D’Emic, C.; Miyazoe, H.; Frank, M.M.; Lofaro, M.; Bruley, J.; Hashemi, P.; Ott, J.A.; et al. High Performance InGaAs Gate-All-Around Nanosheet FET on Si Using Template Assisted Selective Epitaxy. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 39.5.1–39.5.4. [Google Scholar]

- Kanazawa, T.; Ohsawa, K.; Amemiya, T.; Kise, N.; Aonuma, R.; Miyamoto, Y. Fabrication of InGaAs Nanosheet Transistors with Regrown Source. In Proceedings of the Compound Semiconductor Week (CSW), Cambridge, MA, USA, 29 May–1 June 2018; p. We3C3.2. [Google Scholar]

- Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked Nanosheet Gate-All-Around Transistor to Enable Scaling beyond FinFET. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T230–T231. [Google Scholar]

- Tsai, C.-E.; Liu, Y.-C.; Tu, C.-T.; Huang, B.-W.; Jan, S.-R.; Chen, Y.-R.; Chen, J.-Y.; Chueh, S.-J.; Cheng, C.-Y.; Tsen, C.-J.; et al. Highly Stacked 8 Ge0.9Sn0.1 Nanosheet PFETs with Ultrathin Bodies (~3nm) and Thick Bodies (~30nm) Featuring the Respective Record ION/IOFF of 1.4 × 107 and Record ION of 92 μA/ at VOV=VDS=-0.5V by CVD Epitaxy and Dry Etching. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 26.4.1–26.4.4. [Google Scholar]

- Agrawal, A.; Chouksey, S.; Rachmady, W.; Vishwanath, S.; Ghose, S.; Mehta, M.; Torres, J.; Oni, A.A.; Weng, X.; Li, H.; et al. Gate-All-Around Strained Si0.4Ge0.6 Nanosheet PMOS on Strain Relaxed Buffer for High Performance Low Power Logic Application. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 2.2.1–2.2.4. [Google Scholar]

- Del Alamo, J.A. Nanometre-Scale Electronics with III–V Compound Semiconductors. Nature 2011, 479, 317. [Google Scholar] [CrossRef] [PubMed]

- Lin, J.; Zhao, X.; Yu, T.; Antoniadis, D.A.; del Alamo, J.A. A New Self-Aligned Quantum-Well MOSFET Architecture Fabricated by a Scalable Tight-Pitch Process. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 16.2.1–16.2.4. [Google Scholar]

- Xuan, Y.; Wu, Y.Q.; Ye, P.D. High-Performance Inversion-Type Enhancement-Mode InGaAs MOSFET With Maximum Drain Current Exceeding 1 A/mm. IEEE Electron. Device Lett. 2008, 29, 294–296. [Google Scholar] [CrossRef]

- Tomioka, K.; Yoshimura, M.; Fukui, T. A III–V Nanowire Channel on Silicon for High-Performance Vertical Transistors. Nature 2012, 488, 189–192. [Google Scholar] [CrossRef] [PubMed]

- Ramesh, S.; Ivanov, T.; Putcha, V.; Alian, A.; Sibaja-Hernandez, A.; Rooyackers, R.; Camerotto, E.; Milenin, A.; Pinna, N.; Kazzi, S.E.; et al. Record Performance Top-down In0.53Ga0.47As Vertical Nanowire FETs and Vertical Nanosheets. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 17.1.1–17.1.4. [Google Scholar]

- Solomon, P.M.; Palevski, A.; Kuech, T.F.; Tischler, M.A. Low Resistance Ohmic Contacts to Two-Dimensional Electron-Gas Structures by Selective MOVPE. In Proceedings of the International Technical Digest on Electron Devices Meeting, Washington, DC, USA, 3–6 December 1989; pp. 405–408. [Google Scholar]

- Lu, W.; Lee, Y.; Murdzek, J.; Gertsch, J.; Vardi, A.; Kong, L.; George, S.M.; del Alamo, J.A. First Transistor Demonstration of Thermal Atomic Layer Etching: InGaAs FinFETs with Sub-5 nm Fin-Width Featuring in Situ ALE-ALD. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 39.1.1–39.1.4. [Google Scholar]

- Huang, M.L.; Chang, S.W.; Chen, M.K.; Oniki, Y.; Chen, H.C.; Lin, C.H.; Lee, W.C.; Lin, C.H.; Khaderbad, M.A.; Lee, K.Y.; et al. High Performance In0.53Ga0.47As FinFETs Fabricated on 300 mm Si Substrate. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Sun, X.; D’Emic, C.; Cheng, C.-W.; Majumdar, A.; Sun, Y.; Cartier, E.; Bruce, R.L.; Frank, M.; Miyazoe, H.; Shiu, K.-T.; et al. High Performance and Low Leakage Current InGaAs-on-Silicon FinFETs with 20 nm Gate Length. In Proceedings of the 2017 Symposium on VLSI Technology, Kyoto, Japan, 5–8 June 2017; pp. T40–T41. [Google Scholar]

- Kilpi, O.; Svensson, J.; Wernersson, L. Sub-100-nm Gate-Length Scaling of Vertical InAs/InGaAs Nanowire MOSFETs on Si. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 17.3.1–17.3.4. [Google Scholar]

- Ramesh, S.; Ivanov, T.; Camerotto, E.; Sun, N.; Franco, J.; Sibaja-Hernandez, A.; Rooyackers, R.; Alian, A.; Loo, J.; Veloso, A.; et al. Top-down InGaAs Nanowire and Fin Vertical FETs with Record Performance. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Tomioka, K.; Motohisa, J.; Fukui, T. III-V Nanowire Channel on Si: From High-Performance Vertical FET to Steep-Slope Devices. In Proceedings of the 2015 International Symposium on VLSI Technology, Systems and Applications, Hsinchu, Taiwan, 27–29 April 2015; pp. 1–2. [Google Scholar]

- Persson, K.-M.; Berg, M.; Borg, M.B.; Wu, J.; Johansson, S.; Svensson, J.; Jansson, K.; Lind, E.; Wernersson, L.-E. Extrinsic and Intrinsic Performance of Vertical InAs Nanowire MOSFETs on Si Substrates. IEEE Trans. Electron. Devices 2013, 60, 2761–2767. [Google Scholar] [CrossRef]

- Thelander, C.; Fröberg, L.E.; Rehnstedt, C.; Samuelson, L.; Wernersson, L.-E. Vertical Enhancement-Mode InAs Nanowire Field-Effect Transistor With 50-nm Wrap Gate. IEEE Electron. Device Lett. 2008, 29, 206–208. [Google Scholar] [CrossRef]

- Berg, M.; Persson, K.; Kilpi, O.; Svensson, J.; Lind, E.; Wernersson, L. Self-Aligned, Gate-Last Process for Vertical InAs Nanowire MOSFETs on Si. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 31.2.1–31.2.4. [Google Scholar]

- Doornbos, G.; Passlack, M. Benchmarking of III–V n-MOSFET Maturity and Feasibility for Future CMOS. IEEE Electron. Device Lett. 2010, 31, 1110–1112. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, I.-G.; Jo, H.-B.; Baek, J.-M.; Lee, S.-T.; Choi, S.-M.; Kim, H.-J.; Park, W.-S.; Yoo, J.-H.; Ko, D.-H.; Kim, T.-W.; et al. Lg = 50 nm Gate-All-Around In0.53Ga0.47As Nanosheet MOSFETs with Regrown In0.53Ga0.47As Contacts. Electronics 2022, 11, 2744. https://doi.org/10.3390/electronics11172744

Lee I-G, Jo H-B, Baek J-M, Lee S-T, Choi S-M, Kim H-J, Park W-S, Yoo J-H, Ko D-H, Kim T-W, et al. Lg = 50 nm Gate-All-Around In0.53Ga0.47As Nanosheet MOSFETs with Regrown In0.53Ga0.47As Contacts. Electronics. 2022; 11(17):2744. https://doi.org/10.3390/electronics11172744

Chicago/Turabian StyleLee, In-Geun, Hyeon-Bhin Jo, Ji-Min Baek, Sang-Tae Lee, Su-Min Choi, Hyo-Jin Kim, Wan-Soo Park, Ji-Hoon Yoo, Dae-Hong Ko, Tae-Woo Kim, and et al. 2022. "Lg = 50 nm Gate-All-Around In0.53Ga0.47As Nanosheet MOSFETs with Regrown In0.53Ga0.47As Contacts" Electronics 11, no. 17: 2744. https://doi.org/10.3390/electronics11172744

APA StyleLee, I.-G., Jo, H.-B., Baek, J.-M., Lee, S.-T., Choi, S.-M., Kim, H.-J., Park, W.-S., Yoo, J.-H., Ko, D.-H., Kim, T.-W., Kim, S.-K., Kim, J.-G., Yun, J., Kim, T., Lee, J.-H., Shin, C.-S., Lee, J.-H., Seo, K.-S., & Kim, D.-H. (2022). Lg = 50 nm Gate-All-Around In0.53Ga0.47As Nanosheet MOSFETs with Regrown In0.53Ga0.47As Contacts. Electronics, 11(17), 2744. https://doi.org/10.3390/electronics11172744