Fault Diagnosis and Tolerant Control for Three-Level T-Type Inverters

Abstract

:1. Introduction

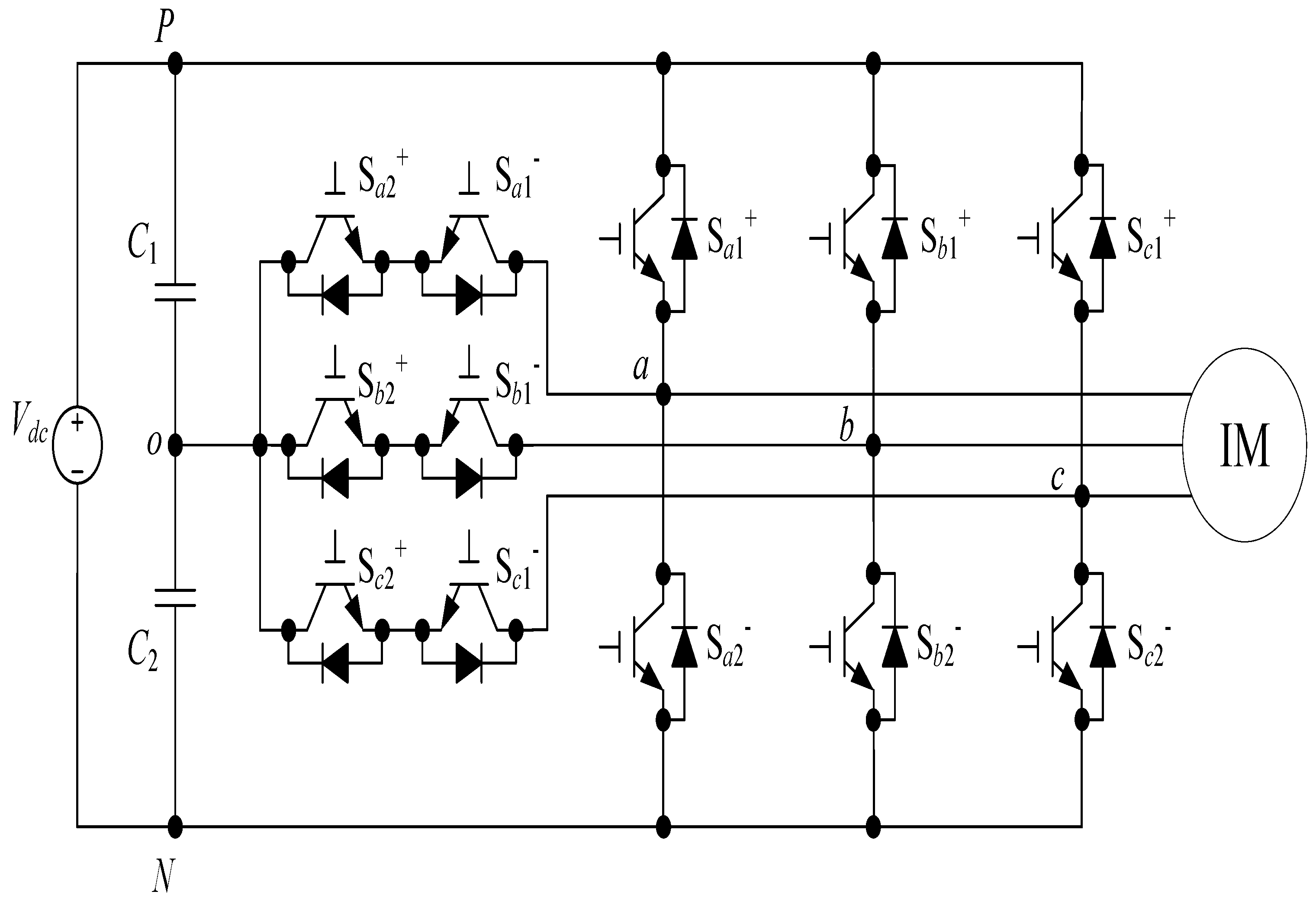

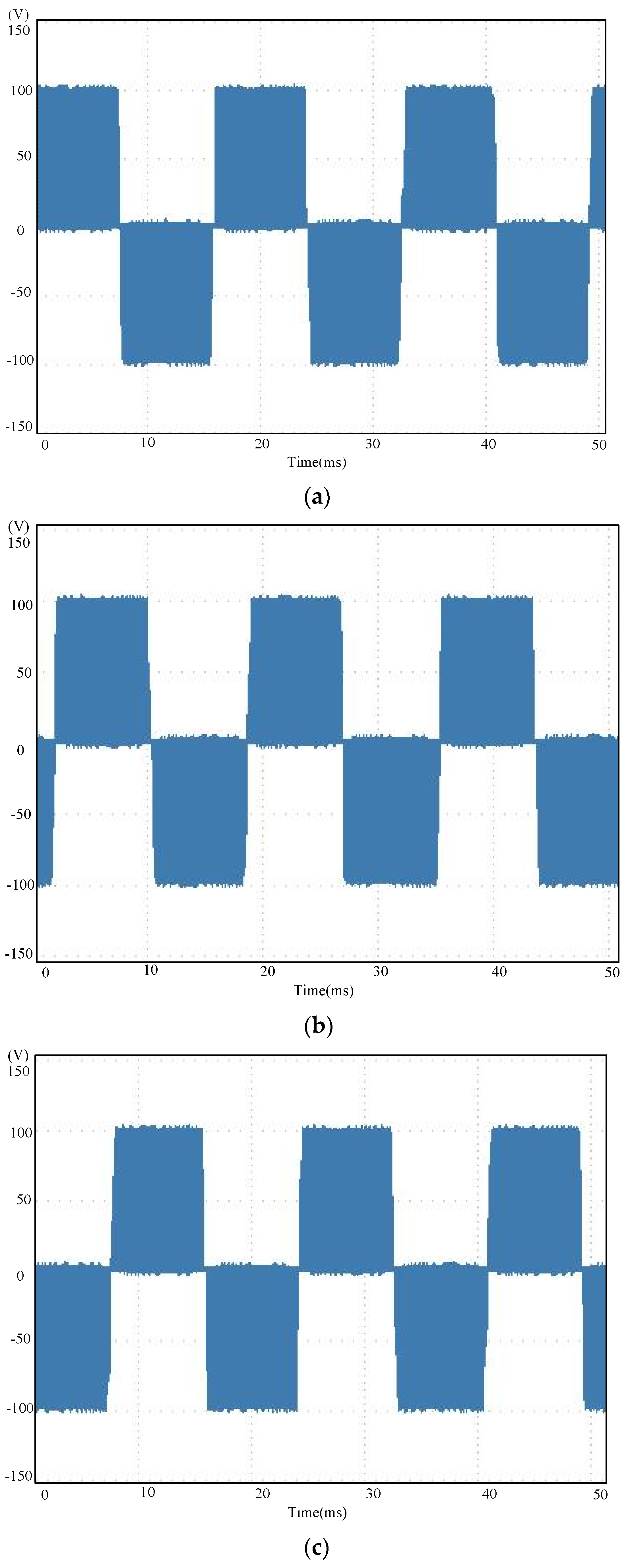

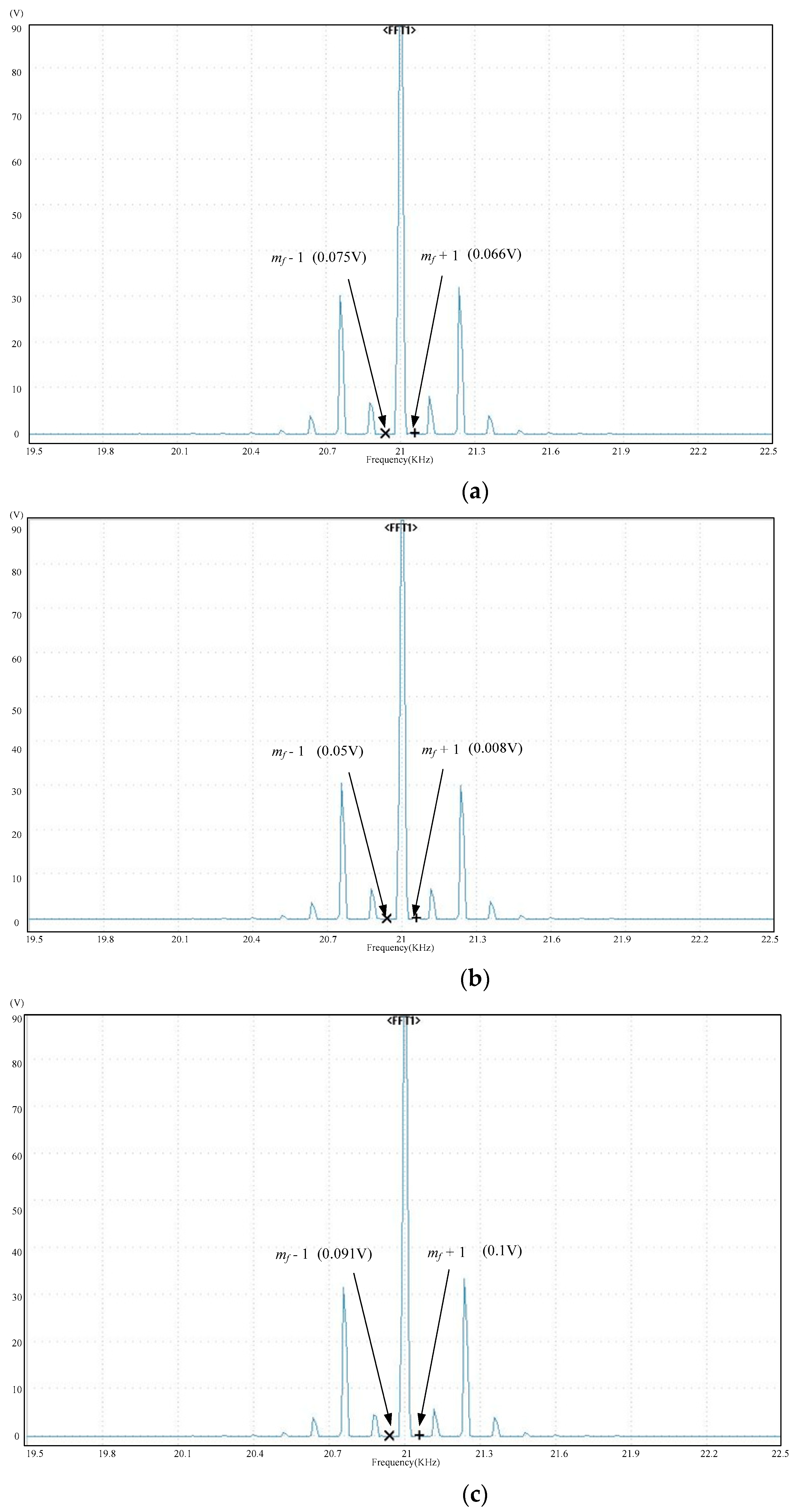

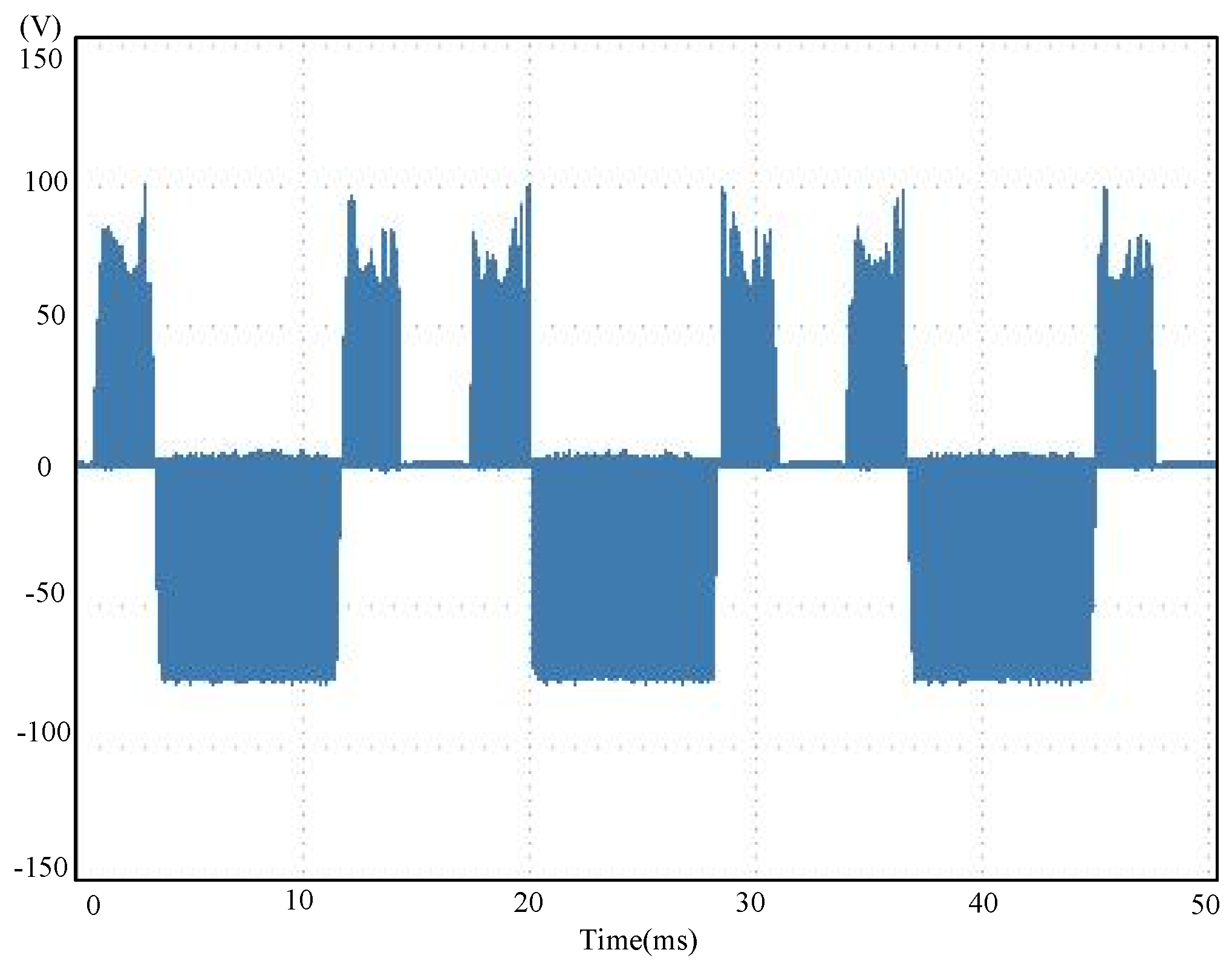

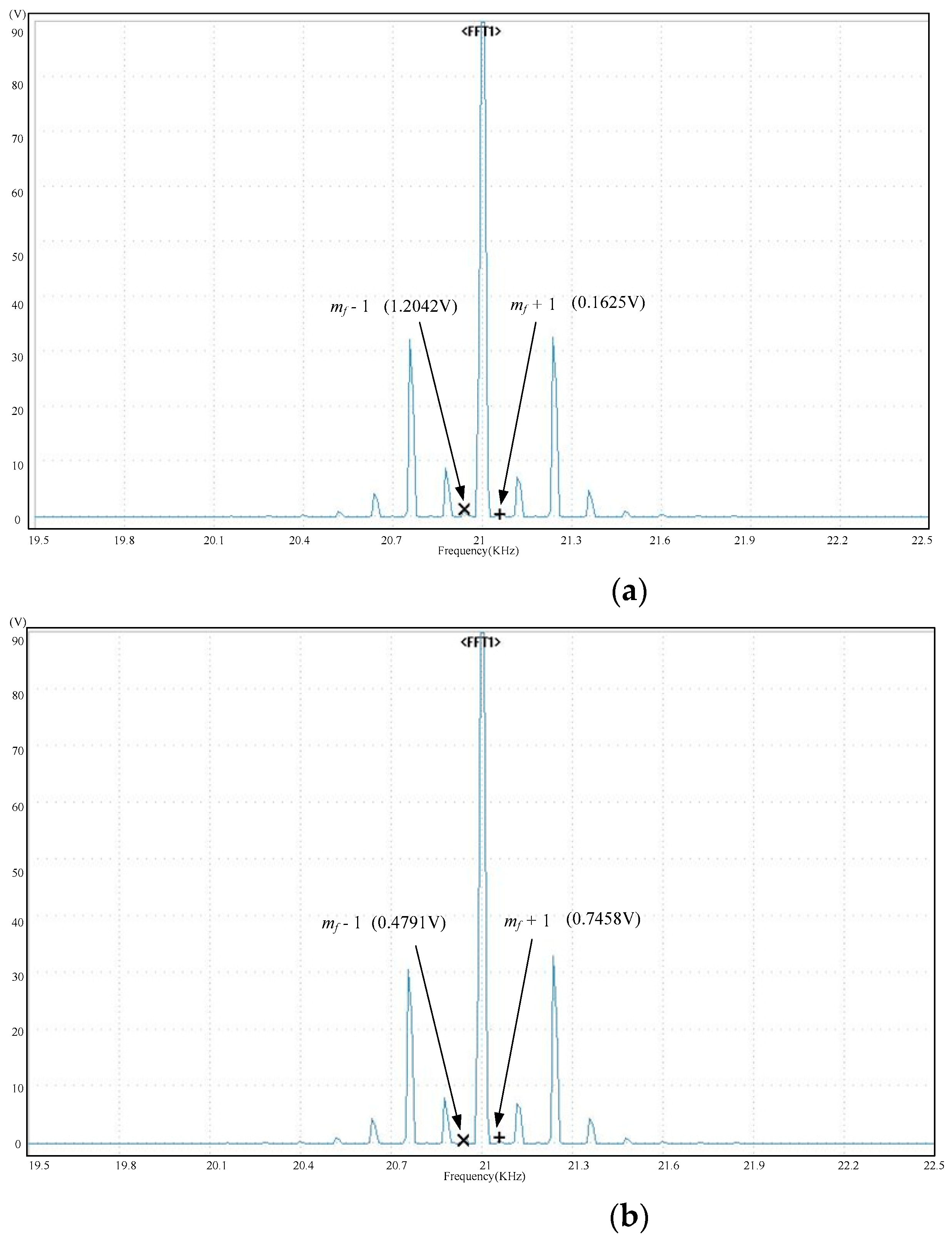

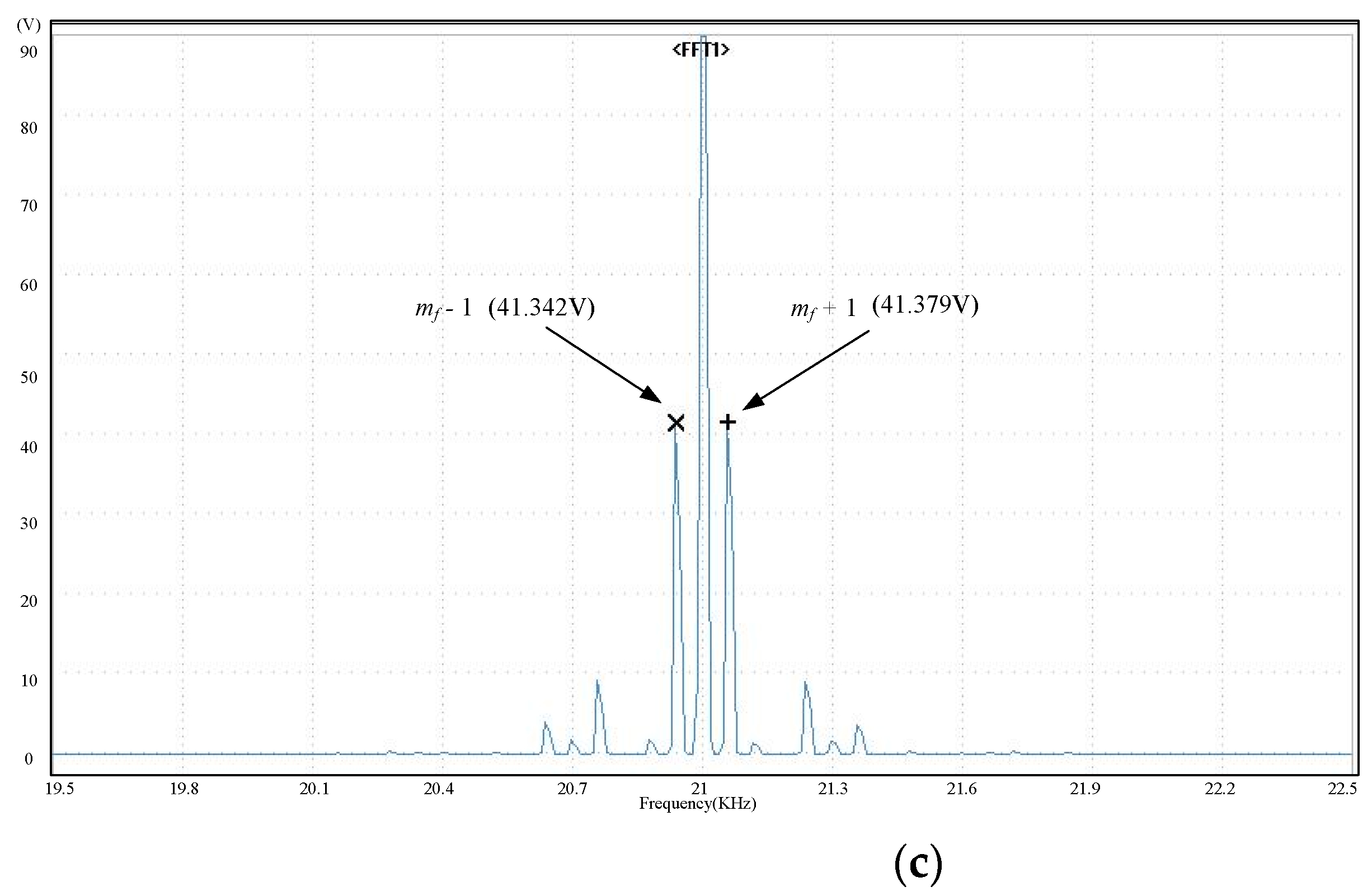

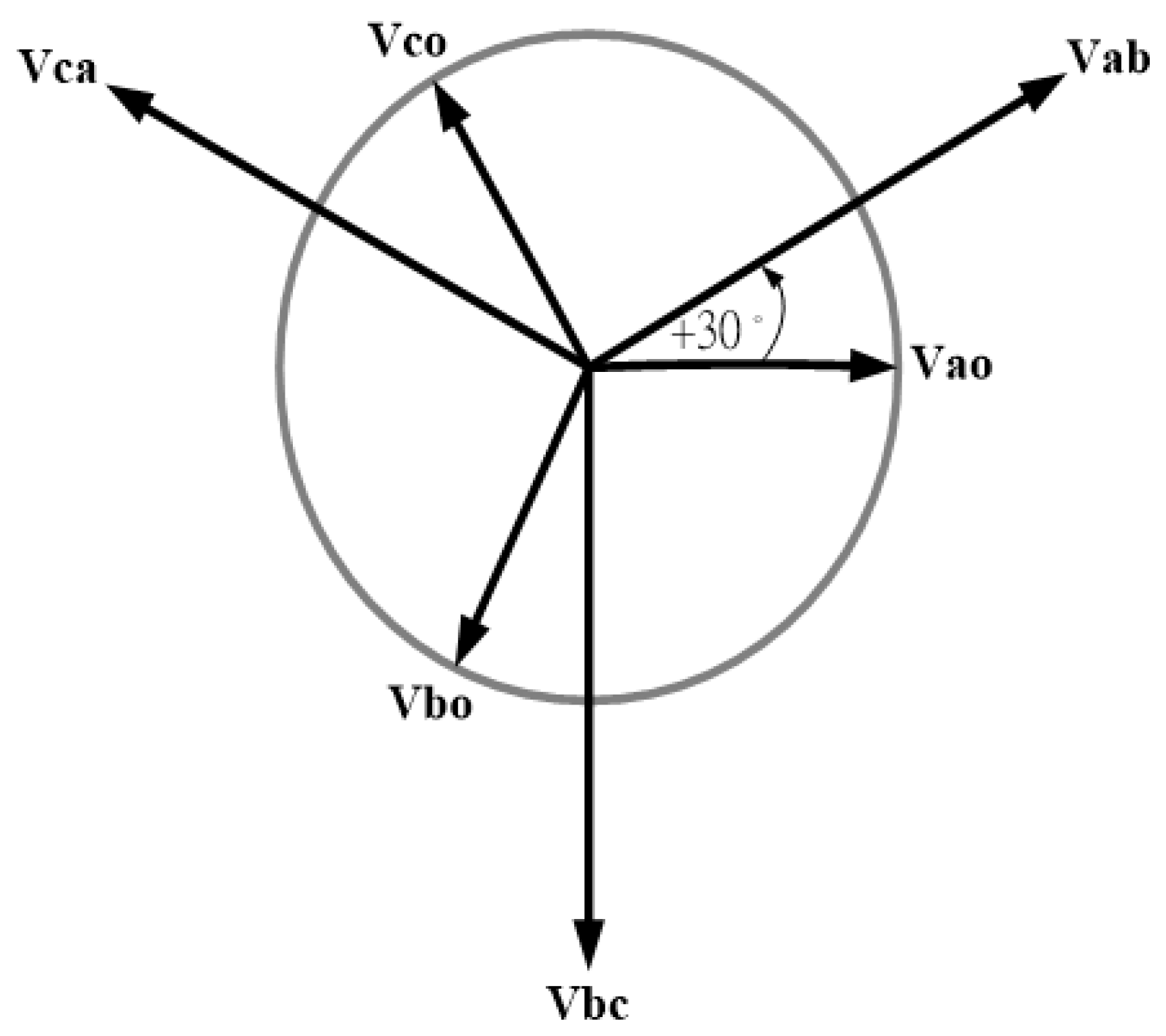

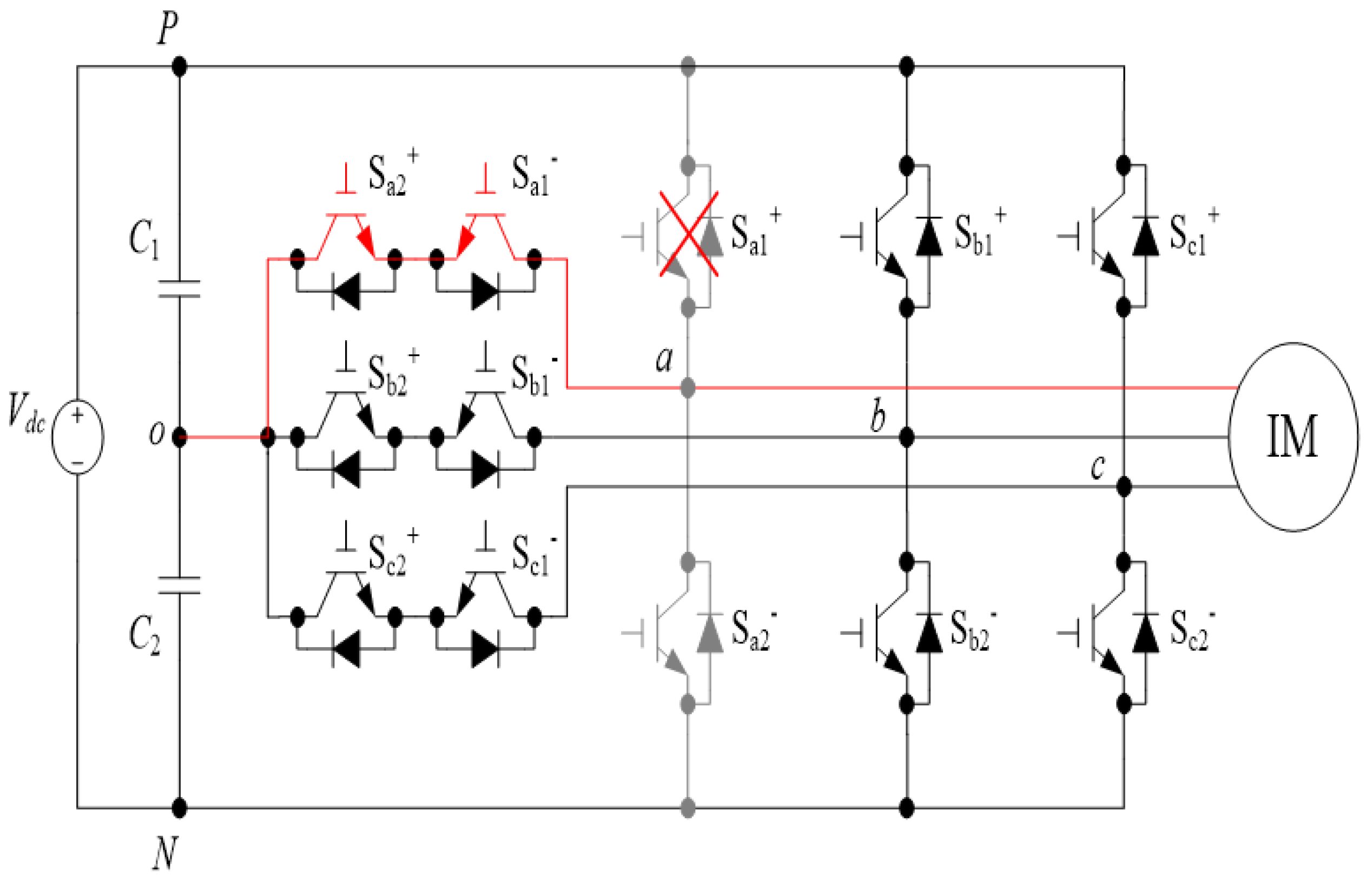

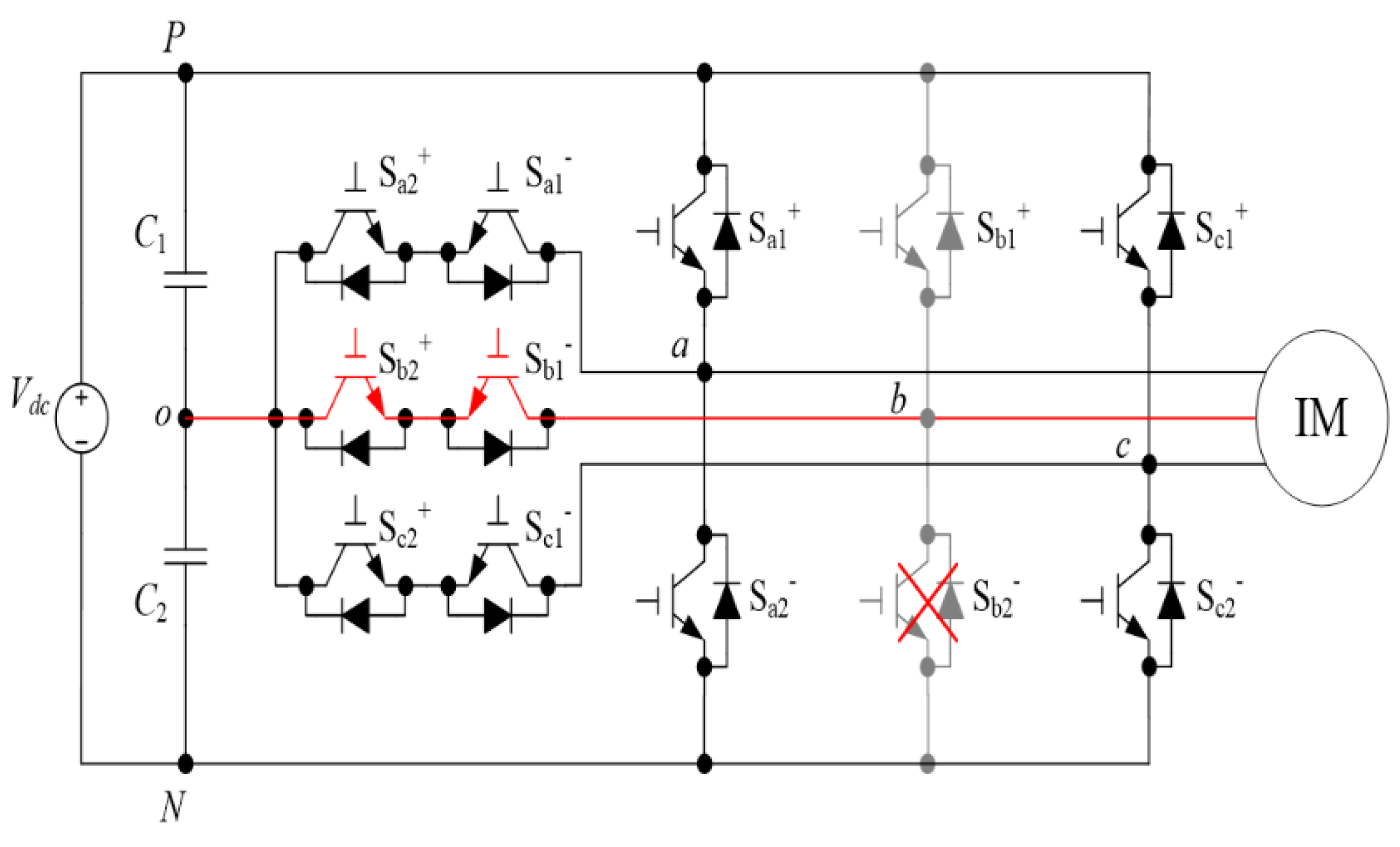

2. Fault Characteristics of Three-Level Inverters

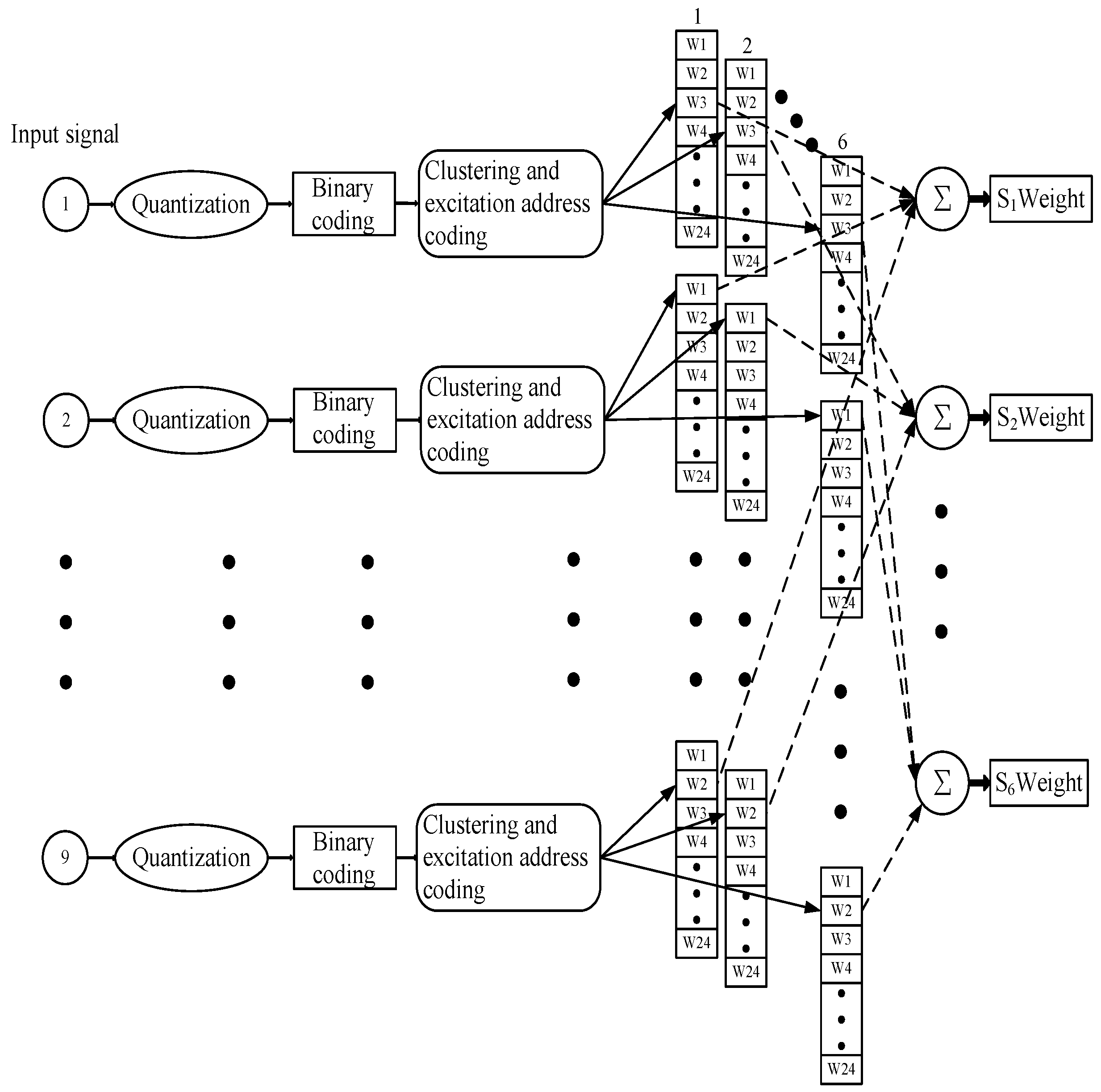

3. The Cerebellar Model Articulation Controller

3.1. Quantization

3.2. Excitation Address Coding and CMAC Output Calculation

3.3. Memory Weight Tuning

3.4. Fault Tolerance

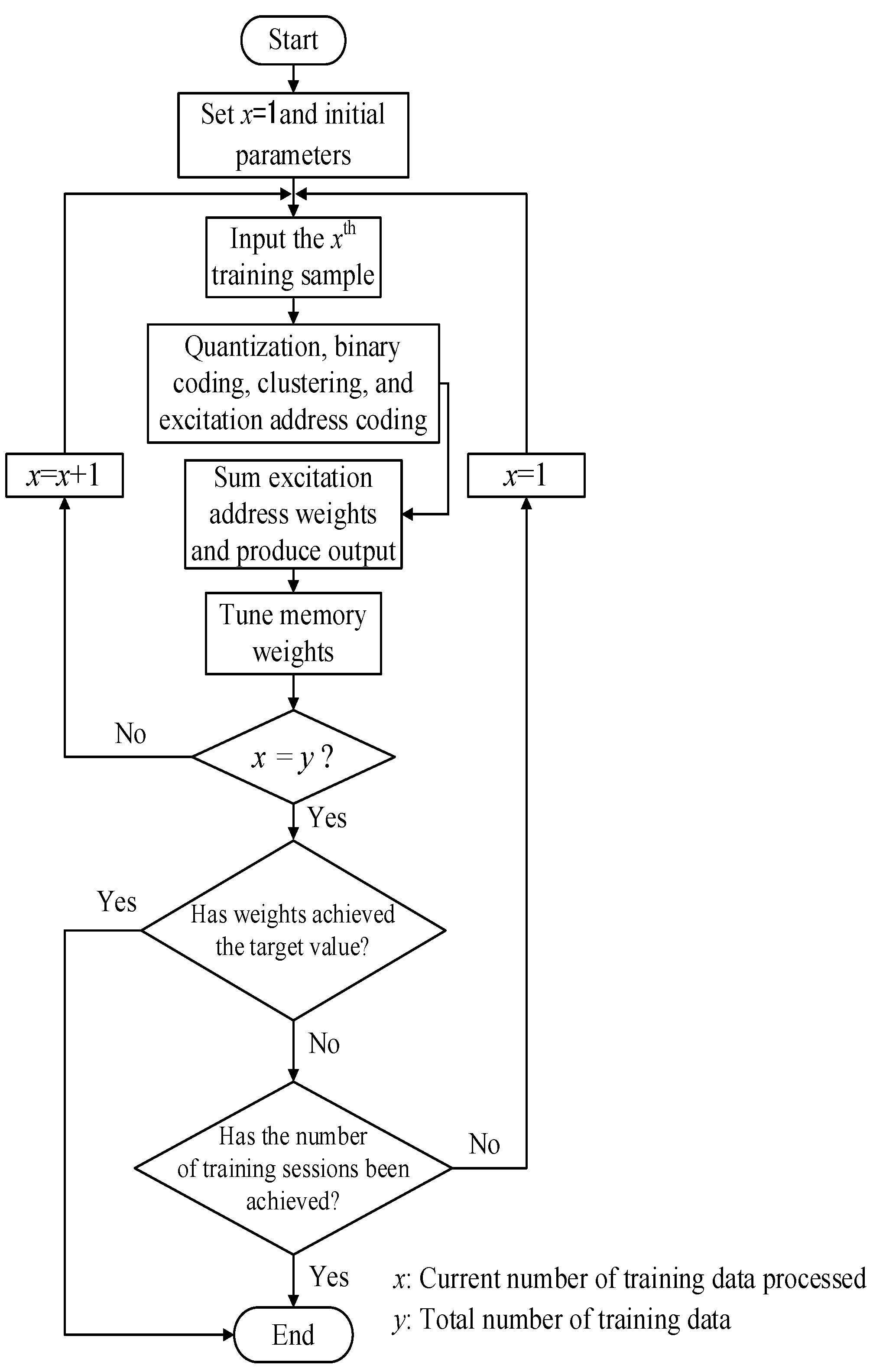

3.5. CMAC Training

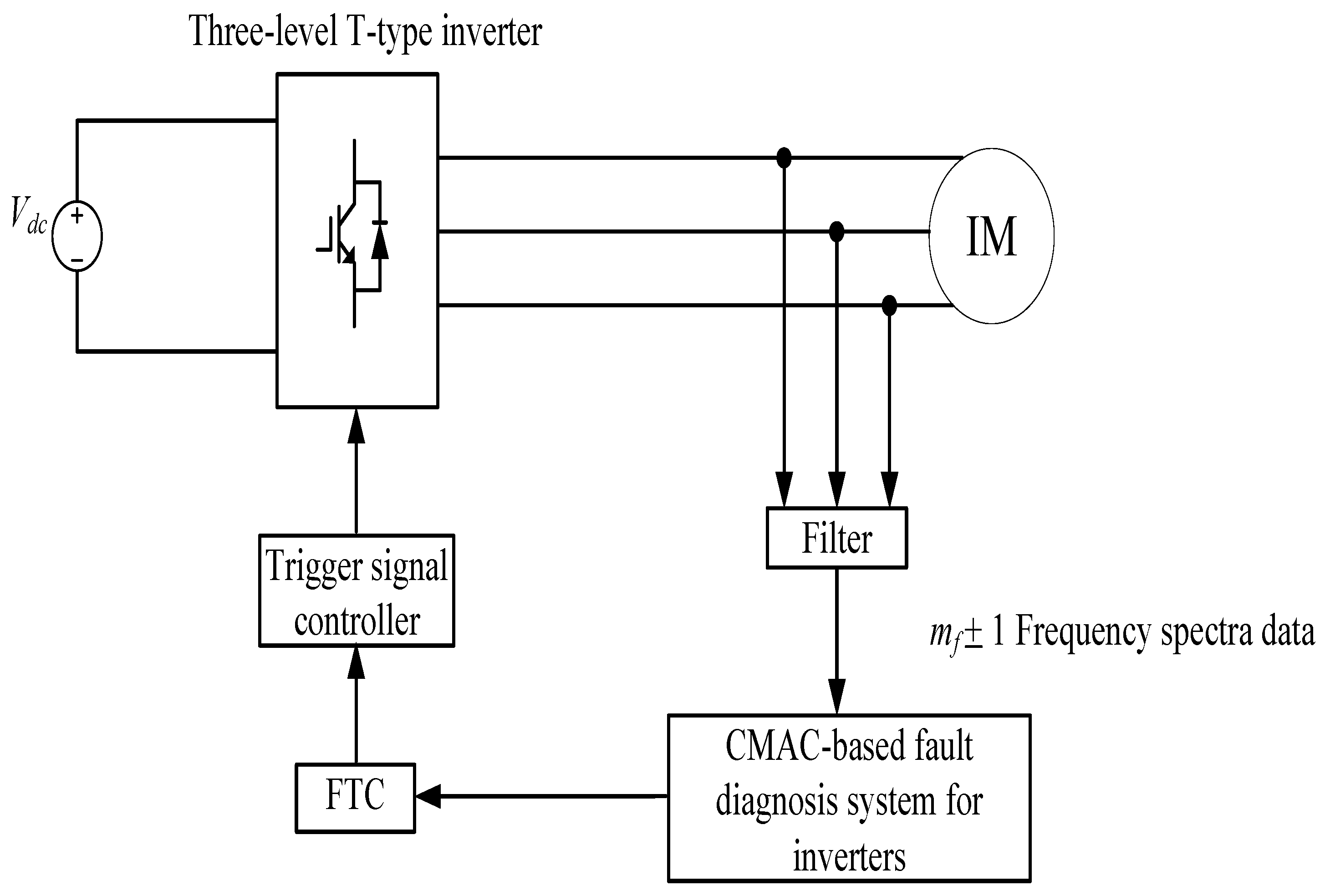

4. CMAC-Based Fault Diagnosis for Inverters

- Step 1. Access the weights of the trained CMAC.

- Step 2. Access the test data samples.

- Step 3. Proceed in the quantization, combined coding, clustering, and excitation address coding of the data.

- Step 4. Sum the weights of the excitation addresses to produce an output.

- Step 5. Determine the weight of the output (weight value closer to 1 denotes an increased likeliness of fault).

- Step 6. Generate fault diagnostic results.

5. Test Results

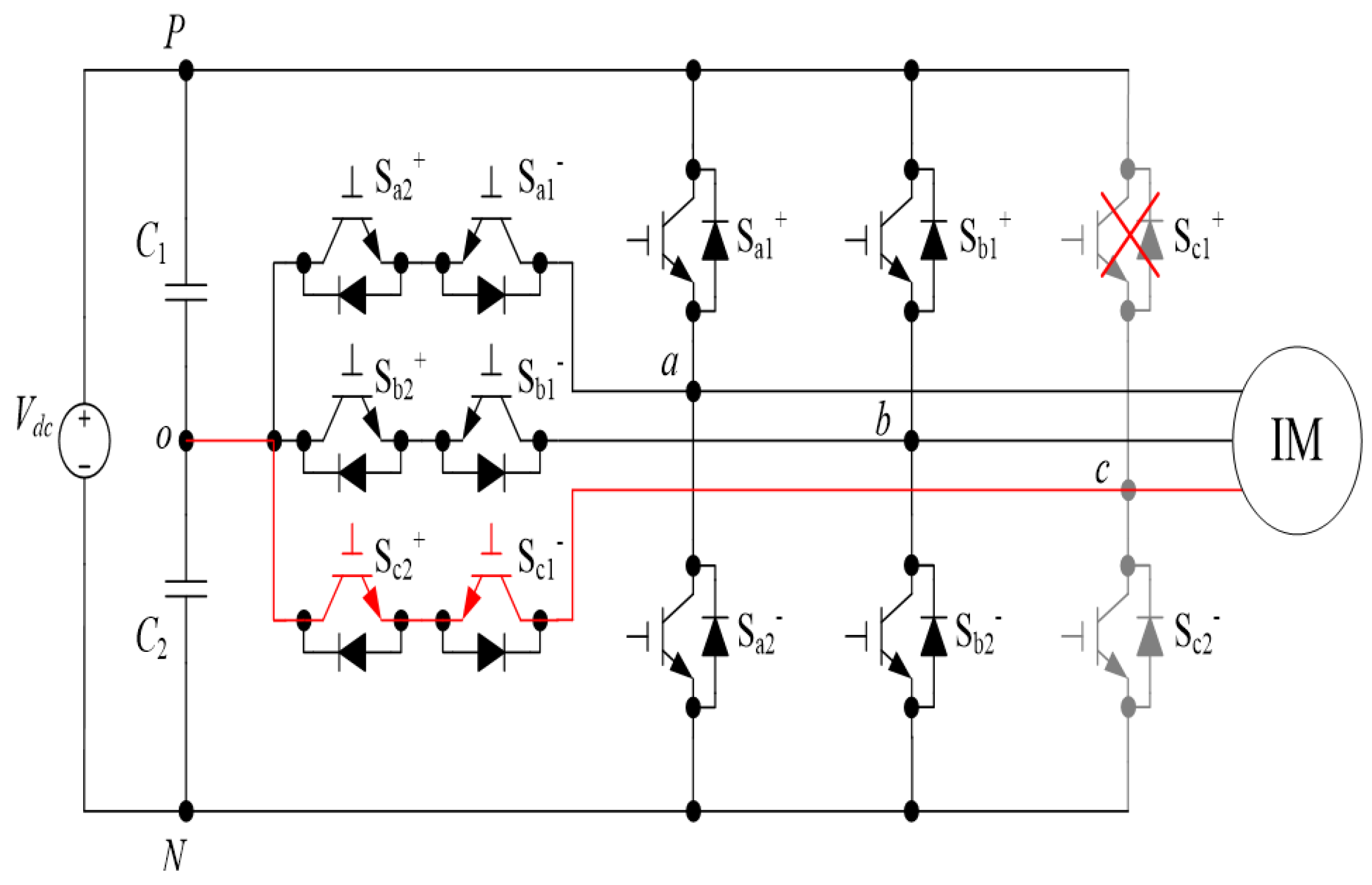

6. Fault Tolerance of Three-Level T-Type Inverter

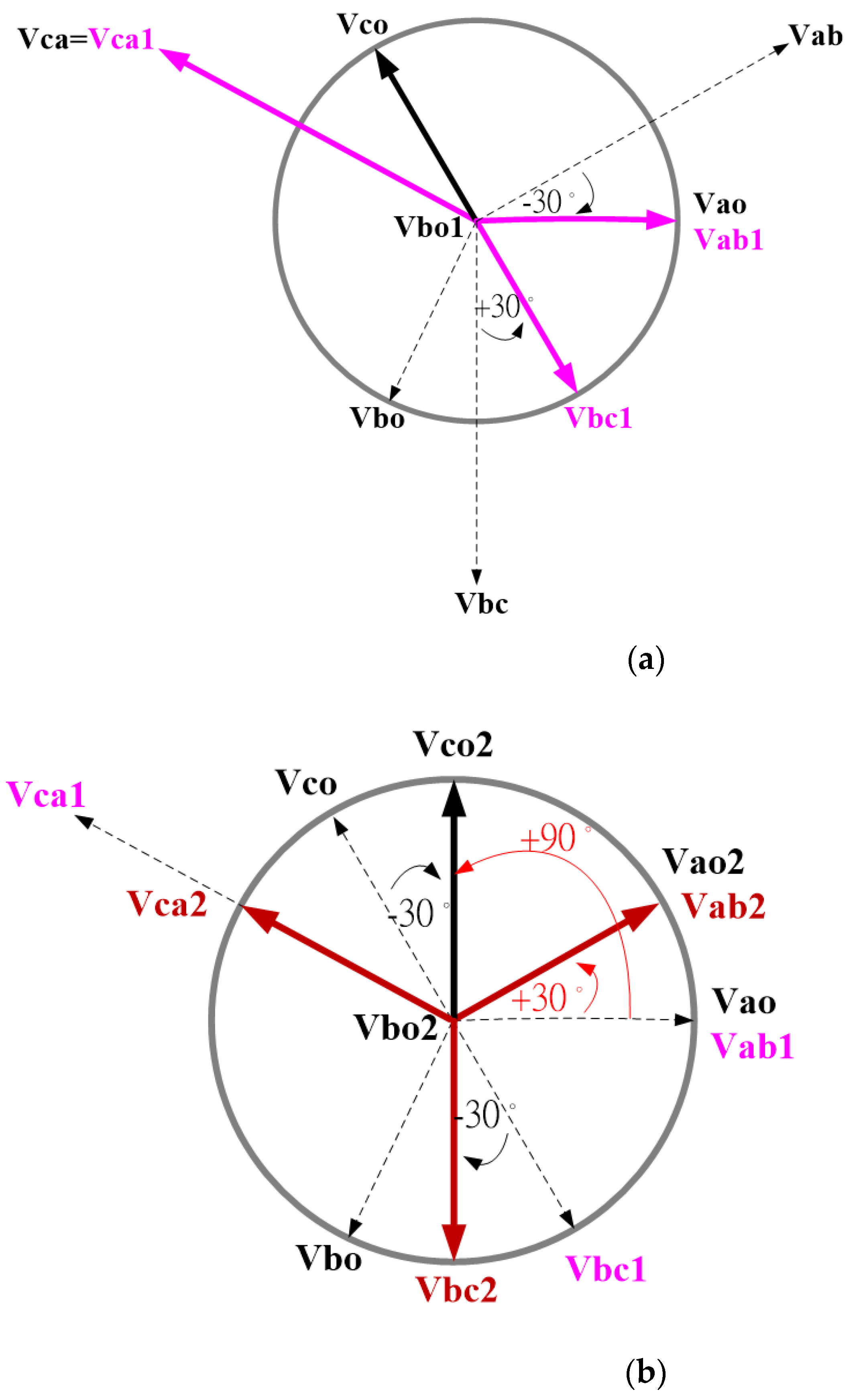

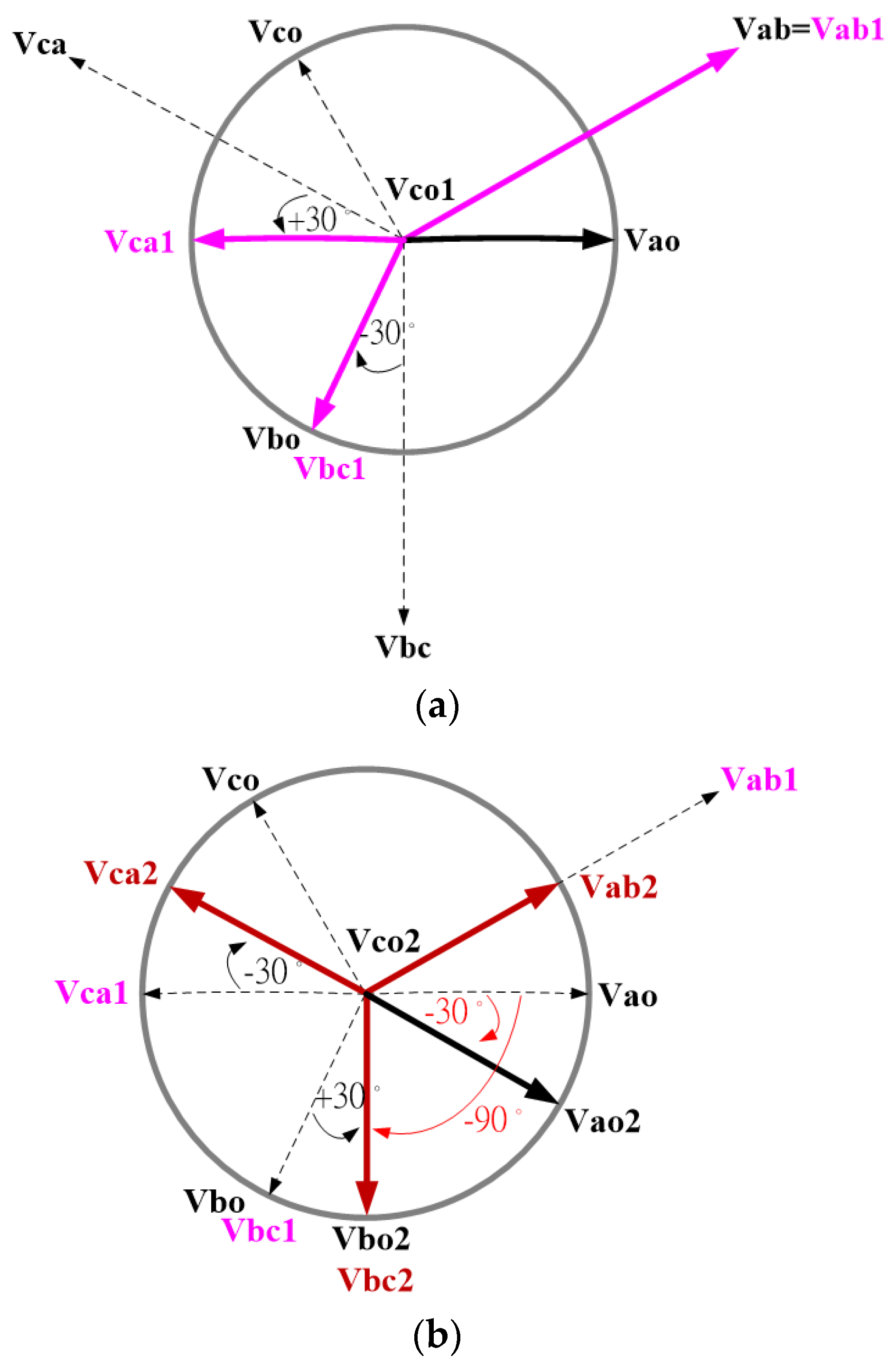

6.1. Fault-Tolerant Control Analysis

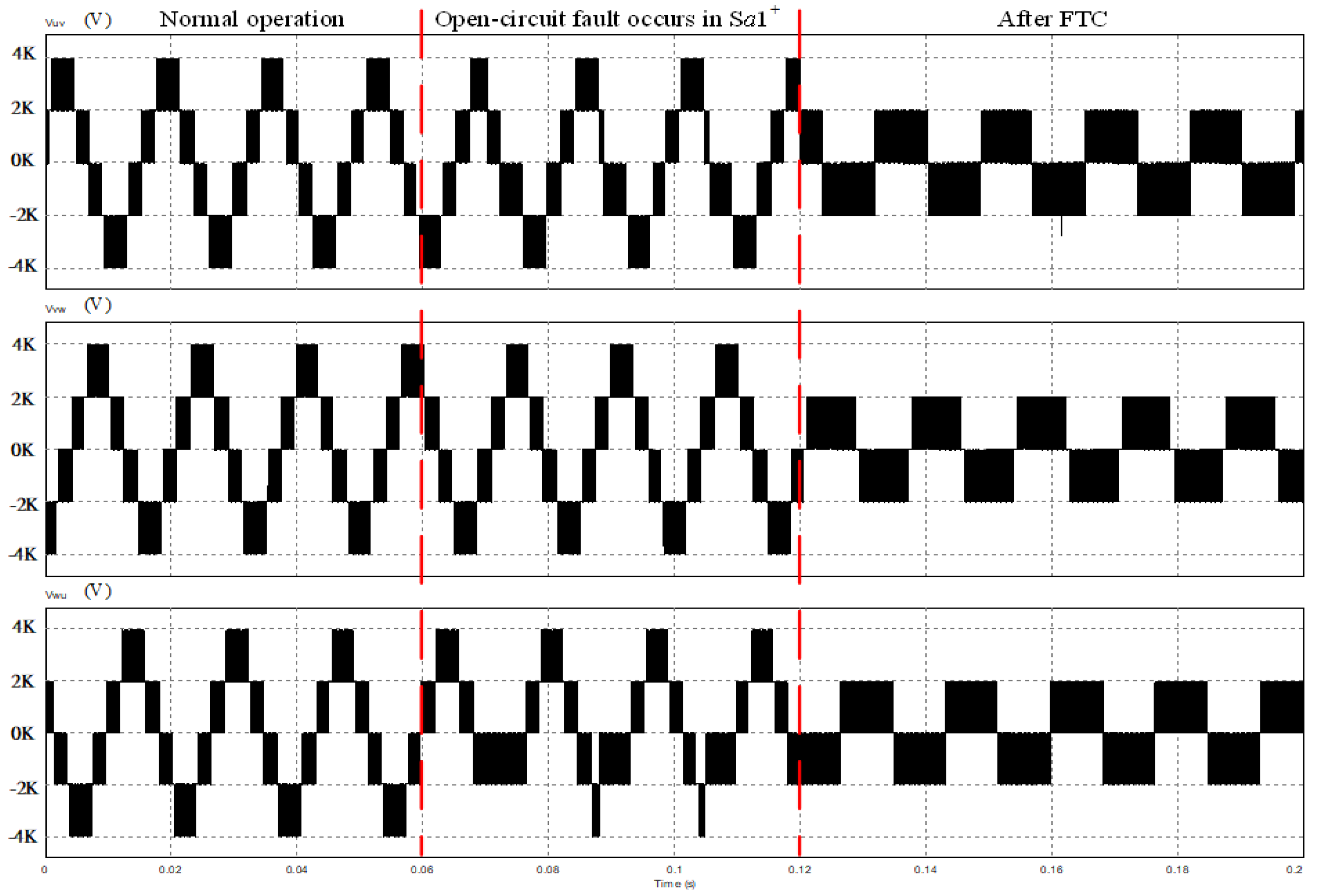

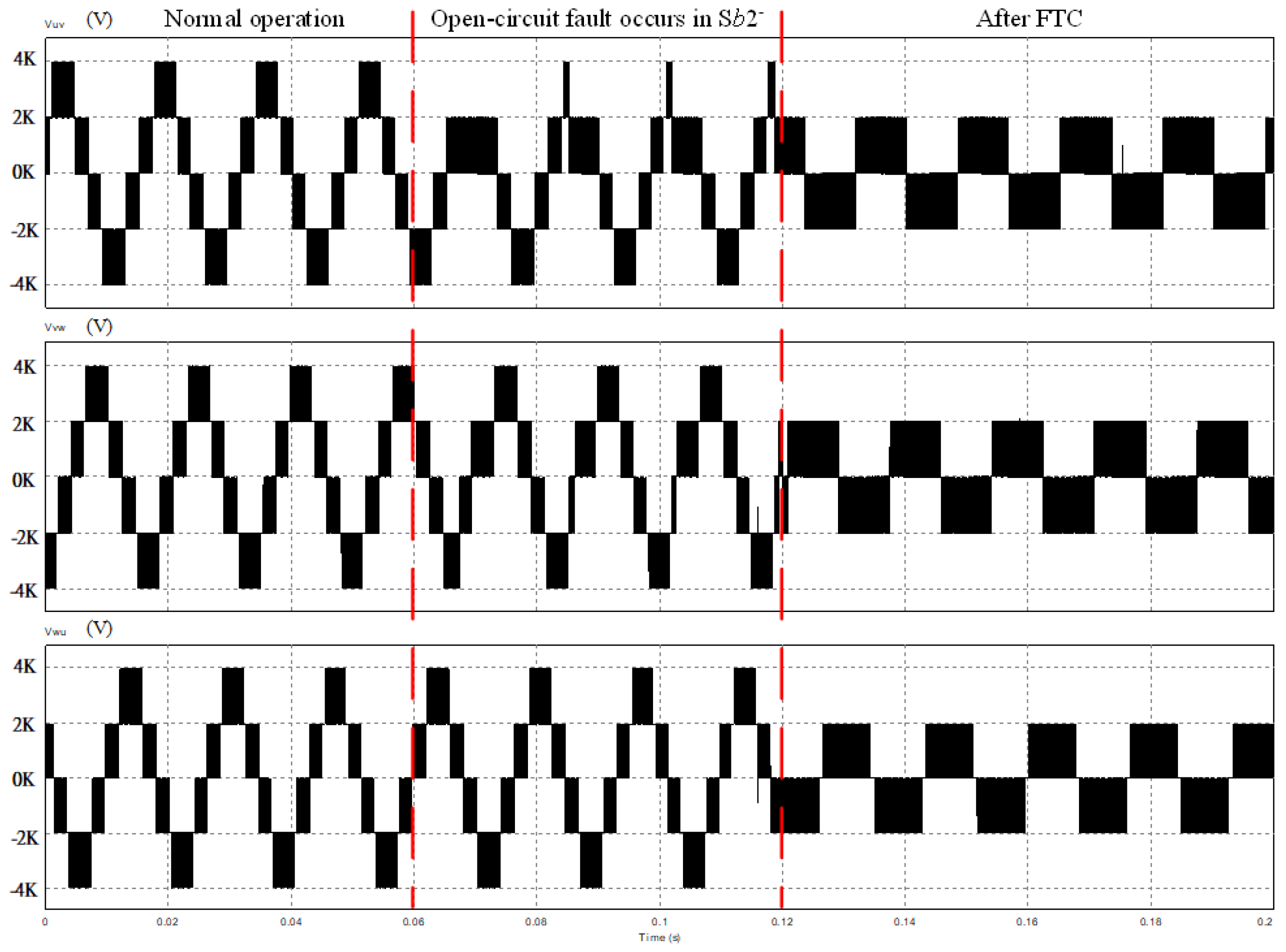

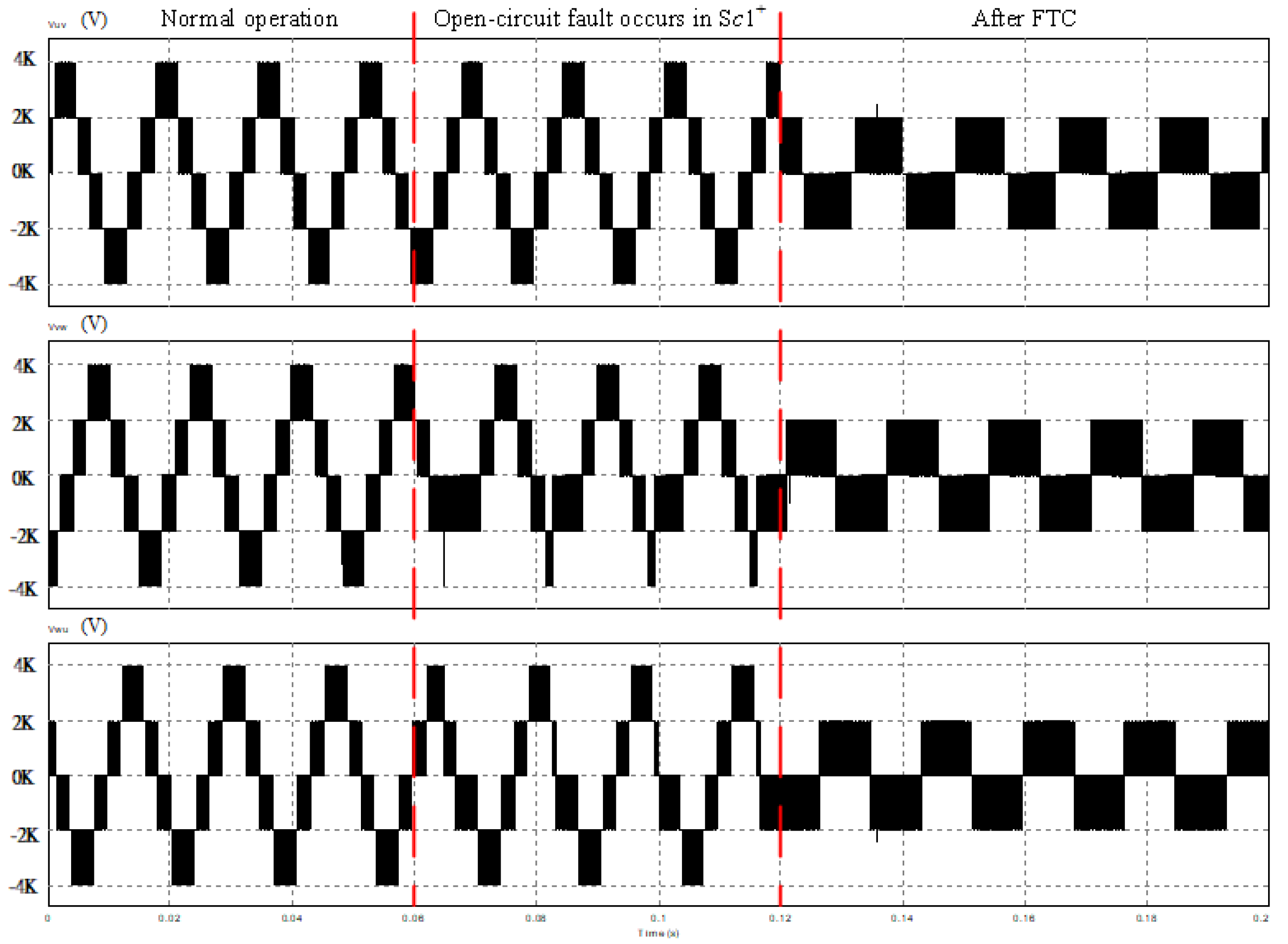

6.2. FTC Simulation Results

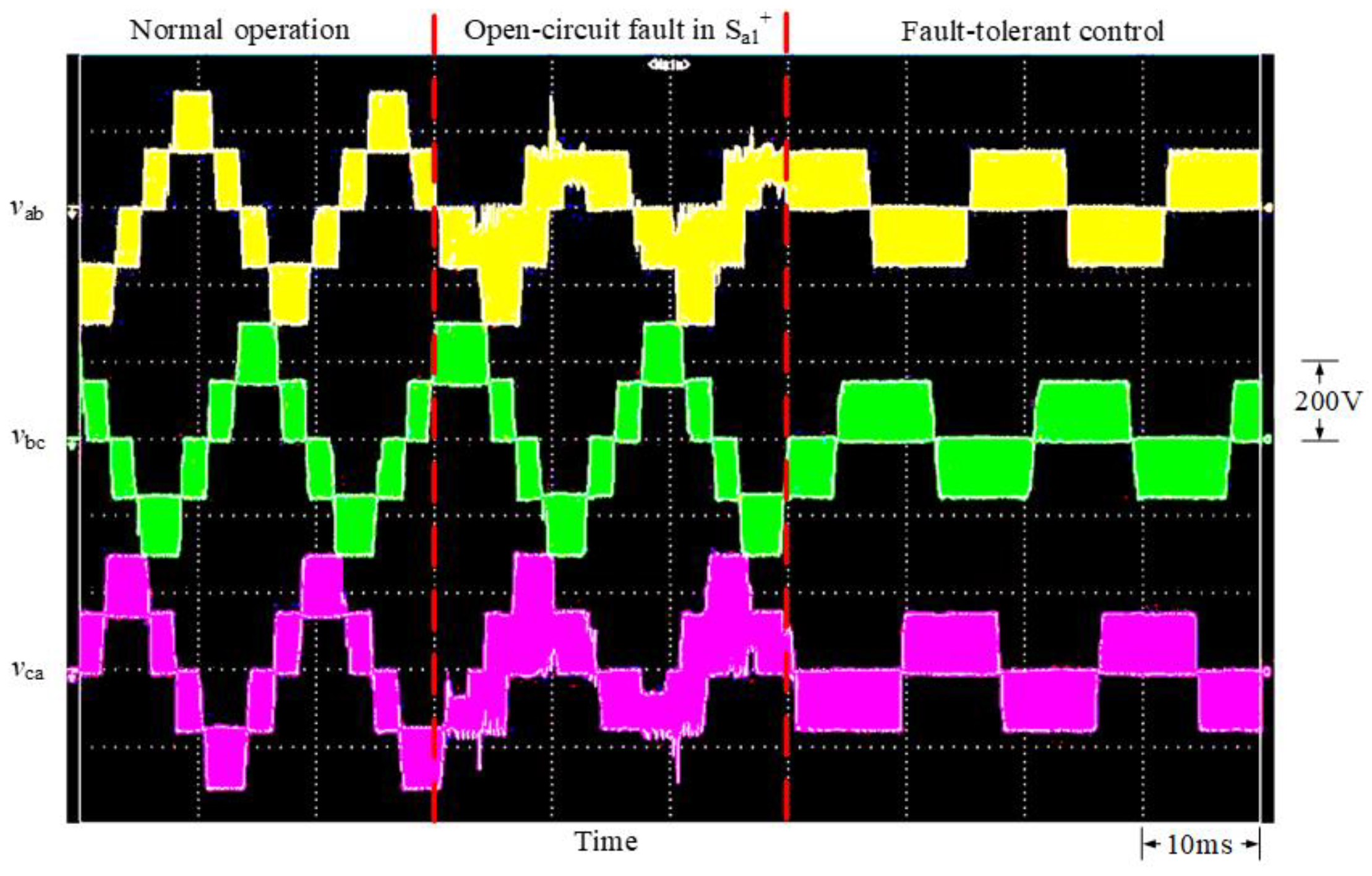

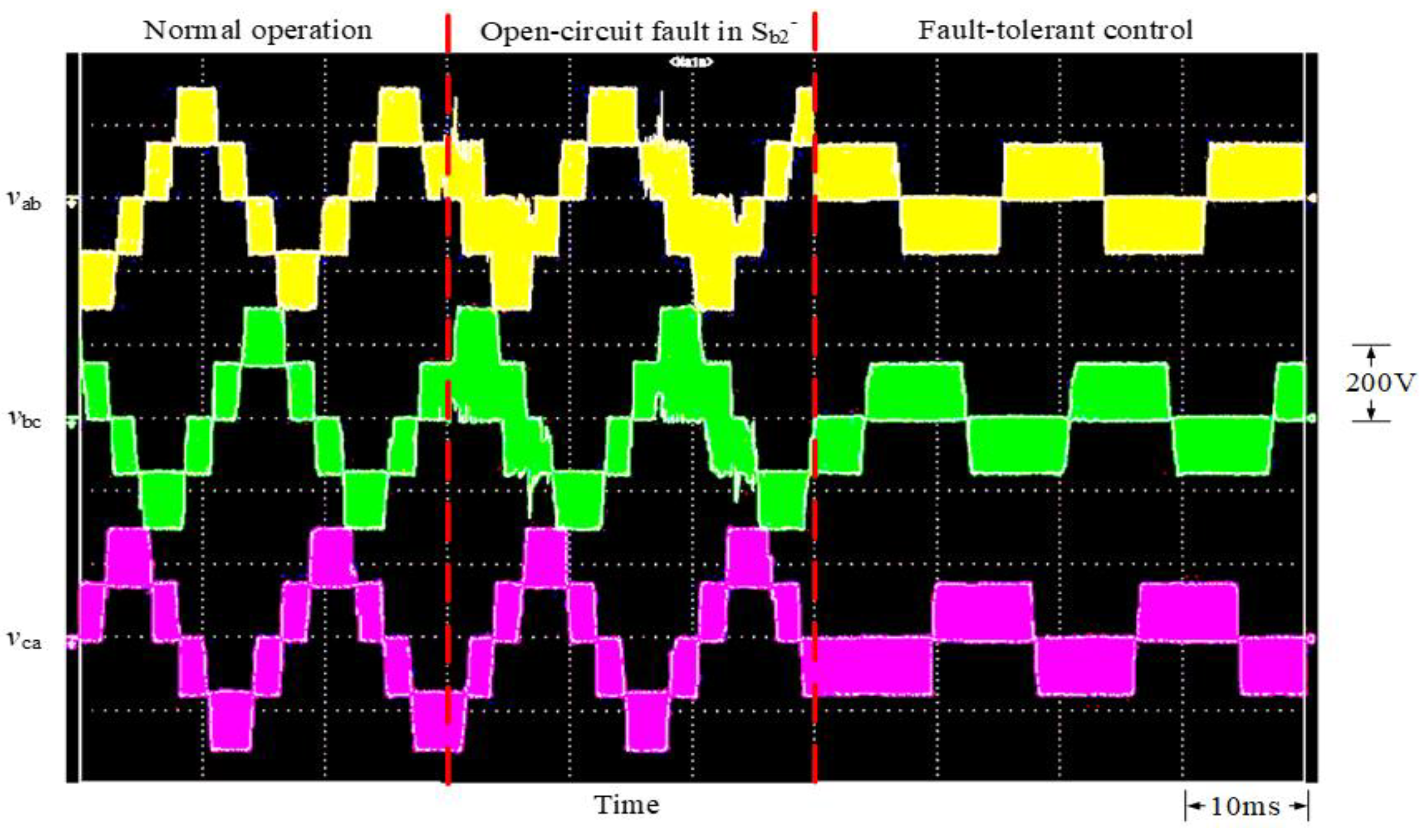

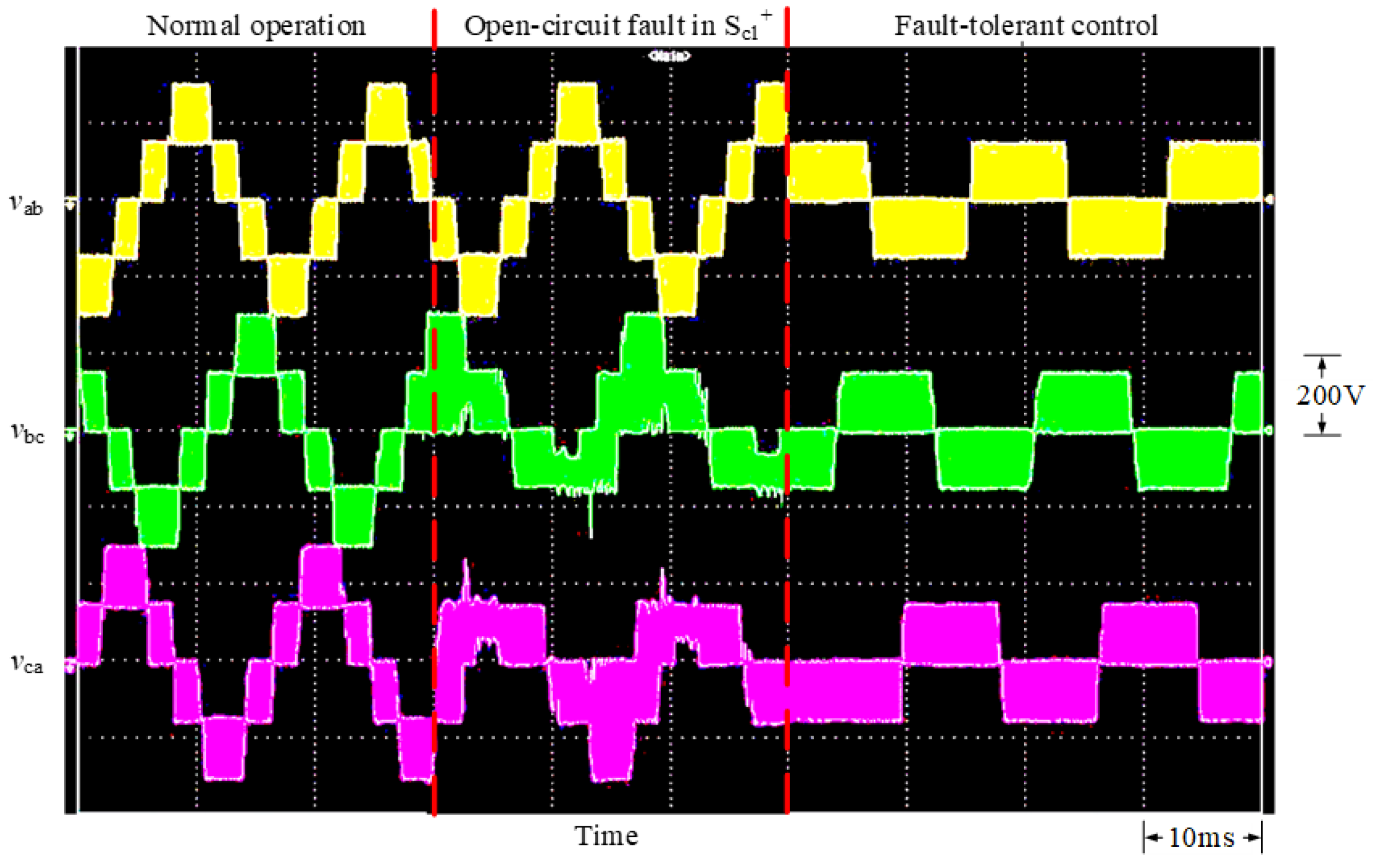

6.3. FTC Experimental Results

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Rodriguez, J.I.; Leeb, S.B. A Multilevel inverter topology for inductively coupled power transfer. IEEE Trans. Power Electron. 2006, 21, 1607–1617. [Google Scholar] [CrossRef]

- Escalante, M.F.; Vannier, J.C.; Arzande, A. Flying capacitor multilevel inverters and DTC motor drive applications. IEEE Trans. Ind. Electron. 2002, 49, 809–815. [Google Scholar] [CrossRef]

- Tourkhani, F.; Viarouge, P.; Meynard, T.A. Optimal design and experimental results of a multilevel inverter for an UPS application. In Proceedings of the Second International Conference on Power Electronics and Drive Systems, Singapore, 26–29 May 1997; pp. 340–343. [Google Scholar]

- Daher, S.; Schmid, J.; Antunes, F.L.M. Multilevel inverter topologies for stand-alone PV systems. IEEE Trans. Ind. Electron. 2008, 55, 2703–2712. [Google Scholar] [CrossRef]

- Naik, R.L.; Udaya, K.R.Y. A novel technique for control of cascaded multilevel inverter for photovoltaic power supplies. In Proceedings of the 2005 European Conference on Power Electronics and Applications, Dresden, Germany, 11–14 September 2005; pp. 1–9. [Google Scholar]

- Nabae, A.; Takahashi, I.; Akagi, H. A new neutral-point clamped PWM inverter. IEEE Trans. Ind. Appl. 1981, 17, 518–523. [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, J.W. Design and implementation of a highly efficient three-level T-type converter for low-voltage applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Chen, A.; Hu, L.; Chen, L.; Deng, Y.; Yao, G.; He, X. A multilevel converter topology with fault-tolerant ability. IEEE Trans. Power Electron. 2005, 20, 405–415. [Google Scholar] [CrossRef]

- Khomfoi, S.; Tolbert, L.M. Fault diagnostic system for a multilevel inverter using a neural network. IEEE Trans. Power Electron. 2007, 22, 1062–1069. [Google Scholar] [CrossRef]

- Choi, U.; Lee, K.; Blaabjerg, F. Diagnosis and tolerant strategy of an open-switch fault for T-type three-level inverter systems. IEEE Trans. Ind. Appl. 2014, 50, 495–508. [Google Scholar] [CrossRef]

- Chao, A.M. Motor Fault Diagnosis by Using Fuzzy Neural Network. Master’s Thesis, Chung Yuan Christian University, Taoyuan, Taiwan, 2004. [Google Scholar]

- Ahmadi, S.; Poure, P.; Saadate, S.; Khaburi, D.A. Fault tolerance analysis of five-level neutral-point-clamped inverters under clamping diode open-circuit failure. Electronics 2022, 11, 1461. [Google Scholar] [CrossRef]

- Chao, K.H.; Ke, C.H. Fault diagnosis and tolerant control of three-level neutral-point clamped inverters in motor drives. Energies 2020, 13, 6302. [Google Scholar] [CrossRef]

- Han, T.; Yang, B.S.; Lee, J.M. A new condition monitoring and fault diagnosis system of induction motors using artificial intelligence algorithms. In Proceedings of the IEEE International Conference on Electrical Machines and Drives, San Antonio, TX, USA, 15 May 2005; pp. 1967–1974. [Google Scholar]

- Chen, T.; Pan, Y.; Xiong, Z. A hybrid system model-based open-circuit fault diagnosis method of three-phase voltage-source inverters for PMSM drive systems. Electronics 2020, 9, 1251. [Google Scholar] [CrossRef]

- Lehtoranta, J.; Koivo, H.N. Fault diagnosis of induction motors with dynamical neural networks. In Proceedings of the IEEE International Conference on System, Man and Cybernetics, Waikoloa, HI, USA, 12 October 2005; pp. 2979–2984. [Google Scholar]

- He, Q.; Du, D.M. Fault diagnosis of induction motor using neural networks. In Proceedings of the International Conference on Machine Learning and Cybernetics, Hong Kong, China, 19–22 August 2007; pp. 1090–1095. [Google Scholar]

- Murphey, Y.L.; Masrur, M.A.; Chen, Z.H.; Zhang, B. Model-based fault diagnosis in electric drives using machine learning. IEEE/ASME Trans. Mechatron. 2006, 11, 290–303. [Google Scholar] [CrossRef]

- Zidani, F.; Benbouzid, M.E.H.; Diallo, D.; Nait-Said, M.S. Induction motor stator faults diagnosis by a current concordia pattern based fuzzy decision system. IEEE Trans. Energy Convers. 2003, 18, 469–475. [Google Scholar] [CrossRef] [Green Version]

- Nejjari, H.; Benbouzid, M.E.H. Monitoring and diagnosis of induction motors electrical faults using a current Park’s vector pattern learning approach. IEEE Trans. Ind. Appl. 2000, 36, 730–735. [Google Scholar] [CrossRef]

- Diallo, D.; Benbouzid, M.E.H.; Hamad, D.; Pierre, X. Fault detection and diagnosis in an induction machine drive: A pattern recognition approach based on concordia stator mean current vector. IEEE Trans. Energy. Convers. 2005, 20, 512–519. [Google Scholar] [CrossRef] [Green Version]

- Zidani, F.; Diallo, D.; Benbouzid, M.E.H.; Nait-Said, R. A Fuzzy-based approach for the diagnosis of fault modes in a voltage-fed PWM inverter induction motor drive. IEEE Trans. Ind. Electron. 2008, 55, 586–593. [Google Scholar] [CrossRef] [Green Version]

- Zhang, K.; Jiang, B.; Staroswiecki, M. Dynamic output feedback fault tolerant controller design for Takagi-Sugeno fuzzy systems with actuator faults. IEEE Trans. Fuzzy Syst. 2010, 18, 194–201. [Google Scholar] [CrossRef]

- Awadallah, M.A.; Morcos, M.M. Diagnosis of switch open-circuit fault in PM brushless DC motor drives. In Proceedings of the Power Engineering Conference on Large Engineering System, Montreal, QC, Canada, 7–9 May 2003; pp. 69–73. [Google Scholar]

- Albus, J.S. A new approach to manipulator control: The cerebellar model articulation controller. Trans. ASME J. Dynam. Syst. Meas. Contr. 1975, 97, 220–227. [Google Scholar] [CrossRef] [Green Version]

- Hung, C.P.; Chao, K.H. CMAC neural network application on lead-acid batteries residual capacity estimation. In Proceedings of the 3th International Conference on Intelligent Computing, Qingdao, China, 21–24 August 2007; pp. 961–970. [Google Scholar]

- Handeiman, D.A.; Lane, S.H.; Gelfand, J.J. Integrating neural networks and knowledge-based systems for intelligent robotic control. IEEE Contr. Syst. Mag. 1990, 10, 77–87. [Google Scholar] [CrossRef]

| Fault Conditions | Category |

|---|---|

| Fault occurs in Sa1+ | F1 |

| Fault occurs in Sa2− | F2 |

| Fault occurs in Sb1+ | F3 |

| Fault occurs in Sb2− | F4 |

| Fault occurs in Sc1+ | F5 |

| Fault occurs in Sc2− | F6 |

| Fault Category | a-Phase Characteristic Spectra | b-Phase Characteristic Spectra | c-Phase Characteristic Spectra | ||||||

|---|---|---|---|---|---|---|---|---|---|

| mf − 1 | mf + 1 | Difference | mf − 1 | mf + 1 | Difference | mf − 1 | mf + 1 | Difference | |

| F1 | 119.613 | 121.643 | 2.030 | 5.313 | 4.388 | 0.925 | 4.758 | 5.824 | 1.066 |

| F2 | 114.776 | 124.832 | 10.056 | 5.321 | 5.855 | 0.534 | 5.230 | 5.144 | 0.086 |

| F3 | 5.747 | 5.700 | 0.047 | 120.198 | 120.783 | 0.585 | 5.726 | 6.377 | 0.651 |

| F4 | 5.991 | 5.839 | 0.152 | 116.877 | 124.288 | 7.411 | 4.527 | 4.709 | 0.182 |

| F5 | 5.067 | 5.678 | 0.611 | 5.630 | 4.802 | 0.828 | 114.667 | 125.159 | 10.492 |

| F6 | 6.368 | 6.210 | 0.158 | 4.728 | 5.491 | 0.763 | 122.676 | 119.228 | 3.448 |

| Fault Category | a-Phase Characteristic Spectra | b-Phase Characteristic Spectra | c-Phase Characteristic Spectra | ||||||

|---|---|---|---|---|---|---|---|---|---|

| mf − 1 | mf + 1 | Difference | mf − 1 | mf + 1 | Difference | mf − 1 | mf + 1 | Difference | |

| F1 | 103.875 | 104.962 | 1.087 | 3.451 | 2.456 | 0.995 | 3.154 | 3.693 | 0.539 |

| F2 | 100.778 | 106.730 | 5.952 | 3.270 | 3.914 | 0.644 | 3.110 | 2.930 | 0.180 |

| F3 | 3.270 | 3.141 | 0.129 | 103.991 | 104.641 | 0.650 | 3.971 | 3.995 | 0.024 |

| F4 | 4.109 | 4.218 | 0.109 | 102.684 | 106.825 | 4.141 | 2.568 | 2.519 | 0.049 |

| F5 | 2.722 | 3.698 | 0.976 | 3.619 | 2.994 | 0.625 | 100.973 | 107.094 | 6.121 |

| F6 | 3.976 | 3.638 | 0.338 | 2.600 | 3.613 | 1.013 | 105.701 | 103.733 | 1.968 |

| Fault Category | a-Phase Characteristic Spectra | b-Phase Characteristic Spectra | c-Phase Characteristic Spectra | ||||||

|---|---|---|---|---|---|---|---|---|---|

| mf − 1 | mf + 1 | Difference | mf − 1 | mf + 1 | Difference | mf − 1 | mf + 1 | Difference | |

| F1 | 90.164 | 91.107 | 0.944 | 2.995 | 2.132 | 0.863 | 2.738 | 3.206 | 0.468 |

| F2 | 87.475 | 92.642 | 5.166 | 2.838 | 3.397 | 0.559 | 2.699 | 2.543 | 0.156 |

| F3 | 2.838 | 2.726 | 0.112 | 90.264 | 90.828 | 0.564 | 3.447 | 3.468 | 0.021 |

| F4 | 3.567 | 3.661 | 0.095 | 89.130 | 92.724 | 3.594 | 2.229 | 2.186 | 0.043 |

| F5 | 2.363 | 3.210 | 0.847 | 3.141 | 2.599 | 0.542 | 87.645 | 92.958 | 5.313 |

| F6 | 3.451 | 3.158 | 0.293 | 2.257 | 3.136 | 0.879 | 91.748 | 90.040 | 1.708 |

| Fault Category | Output Weight | Detection Outcome | |||||

|---|---|---|---|---|---|---|---|

| F1 | F2 | F3 | F4 | F5 | F6 | ||

| F1 | 0.7066 | 0.5039 | 0.2158 | 0.1147 | 0.5605 | 0.4640 | F1 |

| F2 | 0.5594 | 0.6999 | 0.1957 | 0.1363 | 0.4814 | 0.4542 | F2 |

| F3 | 0.2930 | 0.2163 | 0.7419 | 0.6132 | 0.5812 | 0.5308 | F3 |

| F4 | 0.2375 | 0.1476 | 0.5404 | 0.6918 | 0.4793 | 0.5279 | F4 |

| F5 | 0.5462 | 0.4348 | 0.5371 | 0.4375 | 0.8931 | 0.7285 | F5 |

| F6 | 0.4886 | 0.4583 | 0.5007 | 0.4262 | 0.7563 | 0.8933 | F6 |

| Fault Category | Output Weight | Detection Outcome | |||||

|---|---|---|---|---|---|---|---|

| F1 | F2 | F3 | F4 | F5 | F6 | ||

| F1 | 0.7440 | 0.5517 | 0.2297 | 0.2480 | 0.5754 | 0.4923 | F1 |

| F2 | 0.5552 | 0.6683 | 0.2333 | 0.1660 | 0.5146 | 0.5312 | F2 |

| F3 | 0.2803 | 0.2050 | 0.7136 | 0.4682 | 0.5912 | 0.5467 | F3 |

| F4 | 0.2019 | 0.1526 | 0.5619 | 0.5859 | 0.5076 | 0.4151 | F4 |

| F5 | 0.4780 | 0.4384 | 0.4806 | 0.4135 | 0.8566 | 0.6552 | F5 |

| F6 | 0.4745 | 0.4783 | 0.4386 | 0.3918 | 0.7345 | 0.8697 | F6 |

| Fault Category | Output Weight | Detection Outcome | |||||

|---|---|---|---|---|---|---|---|

| F1 | F2 | F3 | F4 | F5 | F6 | ||

| F1 | 0.7291 | 0.5406 | 0.2251 | 0.2431 | 0.5639 | 0.4825 | F1 |

| F2 | 0.5441 | 0.6549 | 0.2286 | 0.1627 | 0.5043 | 0.5206 | F2 |

| F3 | 0.2433 | 0.2009 | 0.6993 | 0.4588 | 0.5794 | 0.5358 | F3 |

| F4 | 0.1979 | 0.1495 | 0.5507 | 0.5742 | 0.4974 | 0.4068 | F4 |

| F5 | 0.4684 | 0.4296 | 0.4710 | 0.4052 | 0.8395 | 0.6421 | F5 |

| F6 | 0.4651 | 0.4687 | 0.4298 | 0.3839 | 0.7198 | 0.8523 | F6 |

| Fault Category | Error Rate | Output Weight | Detection Outcome | |||||

|---|---|---|---|---|---|---|---|---|

| F1 | F2 | F3 | F4 | F5 | F6 | |||

| F1 | +5% | 0.6706 | 0.5592 | 0.2090 | 0.1431 | 0.5708 | 0.5251 | F1 |

| −5% | 0.6457 | 0.4993 | 0.2439 | 0.1454 | 0.5136 | 0.4768 | ||

| F2 | +5% | 0.4525 | 0.7206 | 0.1111 | 0.1148 | 0.4693 | 0.3698 | F2 |

| −5% | 0.4726 | 0.6165 | 0.1711 | 0.1386 | 0.4906 | 0.4526 | ||

| F3 | +5% | 0.2310 | 0.2145 | 0.6713 | 0.5192 | 0.5900 | 0.5044 | F3 |

| −5% | 0.3332 | 0.2504 | 0.6910 | 0.5634 | 0.5757 | 0.5640 | ||

| F4 | +5% | 0.2518 | 0.0922 | 0.5670 | 0.6080 | 0.4840 | 0.4681 | F4 |

| −5% | 0.2470 | 0.1257 | 0.5595 | 0.7397 | 0.5096 | 0.5351 | ||

| F5 | +5% | 0.4445 | 0.4228 | 0.5517 | 0.4030 | 0.9062 | 0.7037 | F5 |

| −5% | 0.5444 | 0.4758 | 0.4715 | 0.4586 | 0.8274 | 0.7609 | ||

| F6 | +5% | 0.5538 | 0.4585 | 0.4769 | 0.4255 | 0.7682 | 0.8771 | F6 |

| −5% | 0.4258 | 0.4217 | 0.4987 | 0.4038 | 0.7699 | 0.8961 | ||

| Fault Category | Error Rate | Output Weight | Detection Outcome | |||||

|---|---|---|---|---|---|---|---|---|

| F1 | F2 | F3 | F4 | F5 | F6 | |||

| F1 | +5% | 0.7012 | 0.4889 | 0.2386 | 0.2282 | 0.5687 | 0.5251 | F1 |

| −5% | 0.6974 | 0.5512 | 0.2385 | 0.1924 | 0.5192 | 0.5309 | ||

| F2 | +5% | 0.5301 | 0.6586 | 0.1823 | 0.1373 | 0.5600 | 0.4343 | F2 |

| −5% | 0.5175 | 0.6687 | 0.1922 | 0.1605 | 0.5172 | 0.4643 | ||

| F3 | +5% | 0.2800 | 0.2232 | 0.6873 | 0.5318 | 0.5848 | 0.5731 | F3 |

| −5% | 0.2104 | 0.1871 | 0.7173 | 0.4320 | 0.6328 | 0.4432 | ||

| F4 | +5% | 0.2057 | 0.1313 | 0.4782 | 0.5397 | 0.4936 | 0.4091 | F4 |

| −5% | 0.1315 | 0.1625 | 0.5224 | 0.5717 | 0.5107 | 0.3889 | ||

| F5 | +5% | 0.4780 | 0.4384 | 0.4806 | 0.4135 | 0.8566 | 0.6552 | F5 |

| −5% | 0.5003 | 0.4220 | 0.4237 | 0.3800 | 0.7992 | 0.6669 | ||

| F6 | +5% | 0.4479 | 0.4731 | 0.4328 | 0.4021 | 0.7341 | 0.8639 | F6 |

| −5% | 0.5313 | 0.4555 | 0.4687 | 0.4098 | 0.6987 | 0.9409 | ||

| Fault Category | Error Rate | Output Weight | Detection Outcome | |||||

|---|---|---|---|---|---|---|---|---|

| F1 | F2 | F3 | F4 | F5 | F6 | |||

| F1 | +5% | 0.6872 | 0.4791 | 0.2338 | 0.2236 | 0.5573 | 0.5146 | F1 |

| −5% | 0.6835 | 0.5402 | 0.2337 | 0.1886 | 0.5088 | 0.5203 | ||

| F2 | +5% | 0.5195 | 0.6454 | 0.1787 | 0.1346 | 0.5488 | 0.4256 | F2 |

| −5% | 0.5072 | 0.6553 | 0.1884 | 0.1573 | 0.5069 | 0.4550 | ||

| F3 | +5% | 0.2744 | 0.2187 | 0.6736 | 0.5212 | 0.5731 | 0.5616 | F3 |

| −5% | 0.2062 | 0.1834 | 0.7030 | 0.4234 | 0.6201 | 0.4343 | ||

| F4 | +5% | 0.2016 | 0.1287 | 0.4686 | 0.5289 | 0.4837 | 0.4009 | F4 |

| −5% | 0.1289 | 0.1593 | 0.5120 | 0.5603 | 0.5005 | 0.3811 | ||

| F5 | +5% | 0.4684 | 0.4296 | 0.4710 | 0.4052 | 0.8395 | 0.6421 | F5 |

| −5% | 0.4903 | 0.4136 | 0.4152 | 0.3724 | 0.7832 | 0.6536 | ||

| F6 | +5% | 0.4389 | 0.4636 | 0.4241 | 0.3941 | 0.7194 | 0.8466 | F6 |

| −5% | 0.5207 | 0.4464 | 0.4593 | 0.4016 | 0.6847 | 0.9221 | ||

| Horsepower (Hp) | Rotor Resistance (Ω) | Rotor Leakage Inductance (H) | Stator Resistance (Ω) | Stator Leakage Inductance (H) | Magnetization Inductance (H) | Moment of Inertia (kg-m2) |

|---|---|---|---|---|---|---|

| 1 | 10.4 | 0.04 | 11.6 | 0.04 | 0.557 | 0.004 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chao, K.-H.; Chang, L.-Y.; Hung, C.-C. Fault Diagnosis and Tolerant Control for Three-Level T-Type Inverters. Electronics 2022, 11, 2496. https://doi.org/10.3390/electronics11162496

Chao K-H, Chang L-Y, Hung C-C. Fault Diagnosis and Tolerant Control for Three-Level T-Type Inverters. Electronics. 2022; 11(16):2496. https://doi.org/10.3390/electronics11162496

Chicago/Turabian StyleChao, Kuei-Hsiang, Long-Yi Chang, and Chien-Chun Hung. 2022. "Fault Diagnosis and Tolerant Control for Three-Level T-Type Inverters" Electronics 11, no. 16: 2496. https://doi.org/10.3390/electronics11162496

APA StyleChao, K.-H., Chang, L.-Y., & Hung, C.-C. (2022). Fault Diagnosis and Tolerant Control for Three-Level T-Type Inverters. Electronics, 11(16), 2496. https://doi.org/10.3390/electronics11162496