Figure 1.

Possible common-mode feedback (CMFB) implementations for a 3-stage amplifier. The blocks labeled H2(s) and H3(s) together constitute the inner amplifier, including its compensation network.

Figure 1.

Possible common-mode feedback (CMFB) implementations for a 3-stage amplifier. The blocks labeled H2(s) and H3(s) together constitute the inner amplifier, including its compensation network.

Figure 2.

Small-signal model of the common-mode (CM) equivalent circuit for the single-loop design.

Figure 2.

Small-signal model of the common-mode (CM) equivalent circuit for the single-loop design.

Figure 3.

Rate of closure (ROC) curves for the single-loop design.

Figure 3.

Rate of closure (ROC) curves for the single-loop design.

Figure 4.

Small-signal model of the CM equivalent circuit for the compensated single-loop design.

Figure 4.

Small-signal model of the CM equivalent circuit for the compensated single-loop design.

Figure 5.

ROC curves for the compensated single-loop design.

Figure 5.

ROC curves for the compensated single-loop design.

Figure 6.

Small-signal model of the CM equivalent circuit for the multi-loop design.

Figure 6.

Small-signal model of the CM equivalent circuit for the multi-loop design.

Figure 7.

Example of the compensation strategy of the differential-mode loop.

Figure 7.

Example of the compensation strategy of the differential-mode loop.

Figure 8.

ROC curves for the first single-Miller-capacitor compensation (CMFB) loop with the SMC compensation example.

Figure 8.

ROC curves for the first single-Miller-capacitor compensation (CMFB) loop with the SMC compensation example.

Figure 9.

CM equivalent small-signal model for CM disturbance rejection in the single-loop solution.

Figure 9.

CM equivalent small-signal model for CM disturbance rejection in the single-loop solution.

Figure 10.

CM equivalent small-signal model for CM disturbance rejection in the multi-loop solution.

Figure 10.

CM equivalent small-signal model for CM disturbance rejection in the multi-loop solution.

Figure 11.

Half-circuit equivalent small-signal model for the nested topology.

Figure 11.

Half-circuit equivalent small-signal model for the nested topology.

Figure 12.

Contour plots of the normalized settling time ( Gain-Bandwidth Product (GBW) to the right) as a function of non-dominant pole parameters ( and Q), final design point highlighted.

Figure 12.

Contour plots of the normalized settling time ( Gain-Bandwidth Product (GBW) to the right) as a function of non-dominant pole parameters ( and Q), final design point highlighted.

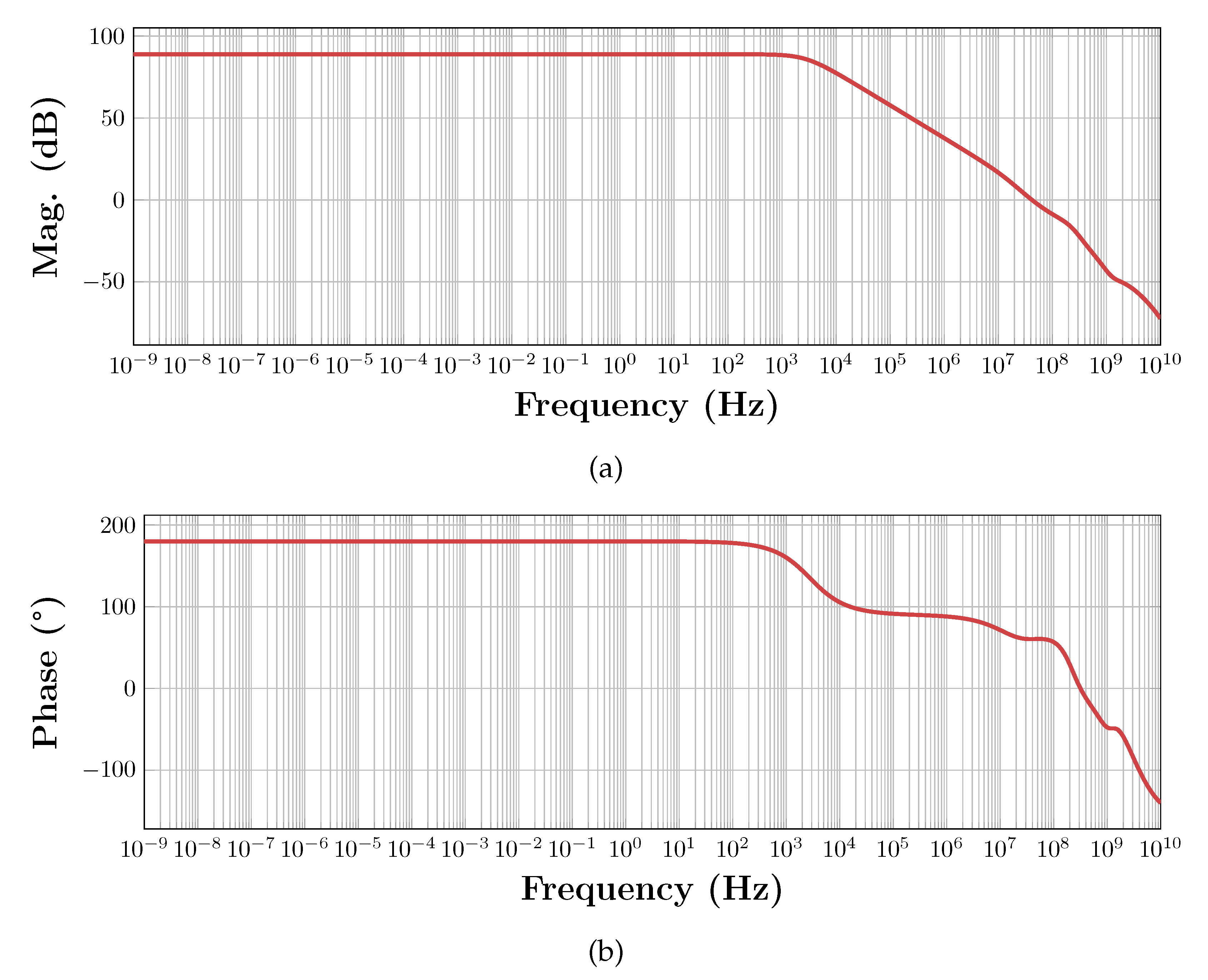

Figure 13.

Transfer function of the macromodel of the designed Operational Transconductance Amplifier (OTA).

Figure 13.

Transfer function of the macromodel of the designed Operational Transconductance Amplifier (OTA).

Figure 14.

Step response of the macromodel of the designed OTA.

Figure 14.

Step response of the macromodel of the designed OTA.

Figure 15.

Schematic of the fully differential nested OTA.

Figure 15.

Schematic of the fully differential nested OTA.

Figure 16.

Low-gain auxiliary amplifiers: (a) Error amplifier for the CMFB loop of the single-loop solution (b) Error amplifier for the CMFB loop 1 of the multi-loop solution.

Figure 16.

Low-gain auxiliary amplifiers: (a) Error amplifier for the CMFB loop of the single-loop solution (b) Error amplifier for the CMFB loop 1 of the multi-loop solution.

Figure 17.

High-gain auxiliary amplifiers: (a) Error amplifier for CMFB loop 2 of the multi-loop solution (b) Amplifier in unity-gain feedback acting as a buffer for the compensation of the CMFB loop in the single-loop solution.

Figure 17.

High-gain auxiliary amplifiers: (a) Error amplifier for CMFB loop 2 of the multi-loop solution (b) Amplifier in unity-gain feedback acting as a buffer for the compensation of the CMFB loop in the single-loop solution.

Figure 18.

Transfer function of the CMFB error amplifiers used in the different CMFB loops, (a) magnitude and (c) phase for the single-loop case and (b) magnitude and (d) phase for the multi-loop case.

Figure 18.

Transfer function of the CMFB error amplifiers used in the different CMFB loops, (a) magnitude and (c) phase for the single-loop case and (b) magnitude and (d) phase for the multi-loop case.

Figure 19.

Replica reference generator for the CM error amplifier of

Figure 16b.

Figure 19.

Replica reference generator for the CM error amplifier of

Figure 16b.

Figure 20.

Transfer function of the differential loop in the single-loop solution (a) magnitude and (b) phase.

Figure 20.

Transfer function of the differential loop in the single-loop solution (a) magnitude and (b) phase.

Figure 21.

Differential-mode step response of the single-loop solution: (a) single-ended output voltages and (b) differential output voltage.

Figure 21.

Differential-mode step response of the single-loop solution: (a) single-ended output voltages and (b) differential output voltage.

Figure 22.

Transfer function of the differential loop in the multi-loop solution (a) magnitude and (b) phase.

Figure 22.

Transfer function of the differential loop in the multi-loop solution (a) magnitude and (b) phase.

Figure 23.

Differential-mode step response of the multi-loop solution: (a) single-ended output voltages and (b) differential output voltage.

Figure 23.

Differential-mode step response of the multi-loop solution: (a) single-ended output voltages and (b) differential output voltage.

Figure 24.

Transfer function of the CMFB loop in the single-loop case (a) magnitude and (b) phase.

Figure 24.

Transfer function of the CMFB loop in the single-loop case (a) magnitude and (b) phase.

Figure 25.

Transfer functions of the CMFB loops in the multi-loop case: (a) magnitude and (b) phase.

Figure 25.

Transfer functions of the CMFB loops in the multi-loop case: (a) magnitude and (b) phase.

Figure 26.

CM step response (a) Single-loop and (b) Multi-loop.

Figure 26.

CM step response (a) Single-loop and (b) Multi-loop.

Figure 27.

Comparison of the linearity of the CMFB solutions.

Figure 27.

Comparison of the linearity of the CMFB solutions.

Figure 28.

Input-referred noise for both cases: (a) input-referred noise and (b) difference between the input-referred noise in the single-loop case and that in the multi-loop case.

Figure 28.

Input-referred noise for both cases: (a) input-referred noise and (b) difference between the input-referred noise in the single-loop case and that in the multi-loop case.

Figure 29.

Input common-mode disturbance rejection.

Figure 29.

Input common-mode disturbance rejection.

Figure 30.

Active-RC biquad implementing the Butterworth low-pass function with 20 MHz cut-off frequency.

Figure 30.

Active-RC biquad implementing the Butterworth low-pass function with 20 MHz cut-off frequency.

Figure 31.

Biquad response. Transistor-level data is the same for both OTA implementations: (a) magnitude and (b) phase.

Figure 31.

Biquad response. Transistor-level data is the same for both OTA implementations: (a) magnitude and (b) phase.

Figure 32.

1-dB compression point curves for both biquad implementations.

Figure 32.

1-dB compression point curves for both biquad implementations.

Table 1.

Device sizes for the schematic in

Figure 15.

Table 1.

Device sizes for the schematic in

Figure 15.

| Device | L (μm) | W (μm) | N (Number of Fingers) | M (Device Multipliers) |

|---|

| M11 | 0.36 | 0.55 | 4 | 9 |

| Mf11 | 0.36 | 0.55 | 4 | 9 |

| M12 | 0.36 | 0.71 | 2 | 4 |

| Mf12 | 0.36 | 0.71 | 2 | 4 |

| M13 | 0.36 | 0.28 | 2 | 4 |

| Mf13 | 0.36 | 0.28 | 2 | 4 |

| M21 | 0.36 | 0.28 | 2 | 4 |

| M22 | 0.36 | 0.67 | 2 | 4 |

| M23 | 0.36 | 0.67 | 2 | 4 |

| M24 | 0.36 | 0.28 | 2 | 4 |

| M31 | 0.36 | 0.67 | 2 | 64 |

| M32 | 0.36 | 0.28 | 2 | 28 |

| M33 | 0.36 | 0.28 | 2 | 32 |

| M34 | 0.36 | 0.28 | 2 | 4 |

Table 2.

Capacitor values for the schematic in

Figure 15.

denotes the capacitor used to compensate the Common-Mode Feedback (CMFB) loop in the single-loop solution.

Table 2.

Capacitor values for the schematic in

Figure 15.

denotes the capacitor used to compensate the Common-Mode Feedback (CMFB) loop in the single-loop solution.

| Capacitor | Value (pF) |

|---|

| CM1 | 0.2 |

| CM2 | 0.1 |

| CCM | 1 |

Table 3.

Device sizes for the auxiliary amplifiers in the single-loop solution (

Figure 16a and

Figure 17b).

Table 3.

Device sizes for the auxiliary amplifiers in the single-loop solution (

Figure 16a and

Figure 17b).

| Device | L (μm) | W (μm) | N | M |

|---|

| Me1 | 0.36 | 0.55 | 4 | 9 |

| Me2 | 0.18 | 0.39 | 2 | 2 |

| Me3 | 0.18 | 0.39 | 2 | 4 |

| Me4 | 0.36 | 0.28 | 2 | 4 |

| Mbb1 | 0.36 | 0.55 | 4 | 9 |

| Mbb2 | 0.18 | 0.39 | 2 | 4 |

| Mbb3 | 0.36 | 0.28 | 2 | 4 |

Table 4.

Device sizes for the auxiliary amplifiers in the multi-loop solution (

Figure 16b and

Figure 17a).

Table 4.

Device sizes for the auxiliary amplifiers in the multi-loop solution (

Figure 16b and

Figure 17a).

| Device | L (μm) | W (μm) | N | M |

|---|

| Me1 (Loop 1) | 0.36 | 0.55 | 4 | 4 |

| Me2 (Loop 1) | 0.18 | 0.27 | 2 | 4 |

| Me3 (Loop 1) | 0.18 | 0.27 | 2 | 8 |

| Me4 (Loop 1) | 0.36 | 0.28 | 2 | 2 |

| Me1 (Loop 2) | 0.36 | 0.55 | 4 | 4 |

| Me2 (Loop 2) | 0.18 | 0.34 | 2 | 1 |

| Me3 (Loop 2) | 0.18 | 0.34 | 2 | 2 |

| Me4 (Loop 2) | 0.36 | 0.28 | 2 | 2 |

Table 5.

DC simulation results for the two solutions along with the target values specified in the initial design.

Table 5.

DC simulation results for the two solutions along with the target values specified in the initial design.

| Parameter | Target | Single-Loop | Multi-Loop |

|---|

| gm1 (μS) | 251 | 253.1 | 253.1 |

| gm2 (μS) | 300 | 320.1 | 321 |

| gm3 (μS) | 4 | 4.25 | 3.89 |

| gmf1 (μS) | 251 | 253.2 | 253.2 |

| gmf2 (μS) | 0.3 | 2.21 | 2.21 |

| Vo,CM (V) | 0.9 | 0.901 | 0.899 |

| I_supply (mA) | - | 1.81 | 1.59 |

Table 6.

Differential-mode results for both solutions.

Table 6.

Differential-mode results for both solutions.

| Parameter | Single-Loop | Multi-Loop |

|---|

| DC gain (dB) | 88.88 | 88.91 |

| UGF (MHz) | 167.01 | 165.75 |

| PM (°) | 51.27 | 50.79 |

| GM (dB) | 33.92 | 34.06 |

| (ns) | 9.90 | 10.06 |

| (ns) | 10.42 | 10.57 |

Table 7.

Common-mode results for both solutions.

Table 7.

Common-mode results for both solutions.

| Parameter | Single-Loop | Multi-Loop (Loop 1) | Multi-Loop (Loop 2) |

|---|

| DC gain (dB) | 88.91 | 29.23 | 48.62 |

| UGF (MHz) | 42.21 | 67.65 | 91.02 |

| PM (°) | 60.37 | 60.57 | 30.34 |

| GM (dB) | 22.11 | ∞ | ∞ |

Table 8.

Comparison of filter metrics with state of the art.

Table 8.

Comparison of filter metrics with state of the art.

| Metric | [23] | [24] | [25] | [26] | This Work |

|---|

| Single-loop | Multi-loop |

|---|

| Technology (nm) | 65 | 65 | 130 | 180 | 180 |

| Order-Type | 4th BPF | 4th LPF | 4th LPF | 5th LPF | 2nd LPF |

| Topology | Switched Gm-C | Active-RC | Active-RC | Active-RC | Active-RC |

| Filter’s (MHz) | 35 | 16 | 20 | 56 | 20 |

| In-band IIP3 (dBm) | 9.1 | 22.1 | 21 | 30.5 | 32.9 |

| (dBm) | −2.4 | 8 | 6.96 | 8 | 2.34 | 9.08 |

| Power per pole (mW) | 1.87 | 4.75 | 1.39 | 2.94 | 3.26 | 2.86 |

Table 9.

Qualitative comparison of the performance of the two CMFB implementations.

Table 9.

Qualitative comparison of the performance of the two CMFB implementations.

| Metric | Single-Loop | Multi-Loop |

|---|

| Stability | Compensation needed | Optional compensation |

| Linearity | Poor | Good |

| Noise | Fair | Fair |

| Input CM disturbance rejection | Poor | Good |

| Output CM disturbance rejection | Fair | Poor |