Conception and Simulation of a 2-Then-1-Bit/Cycle Noise-Shaping SAR ADC

Abstract

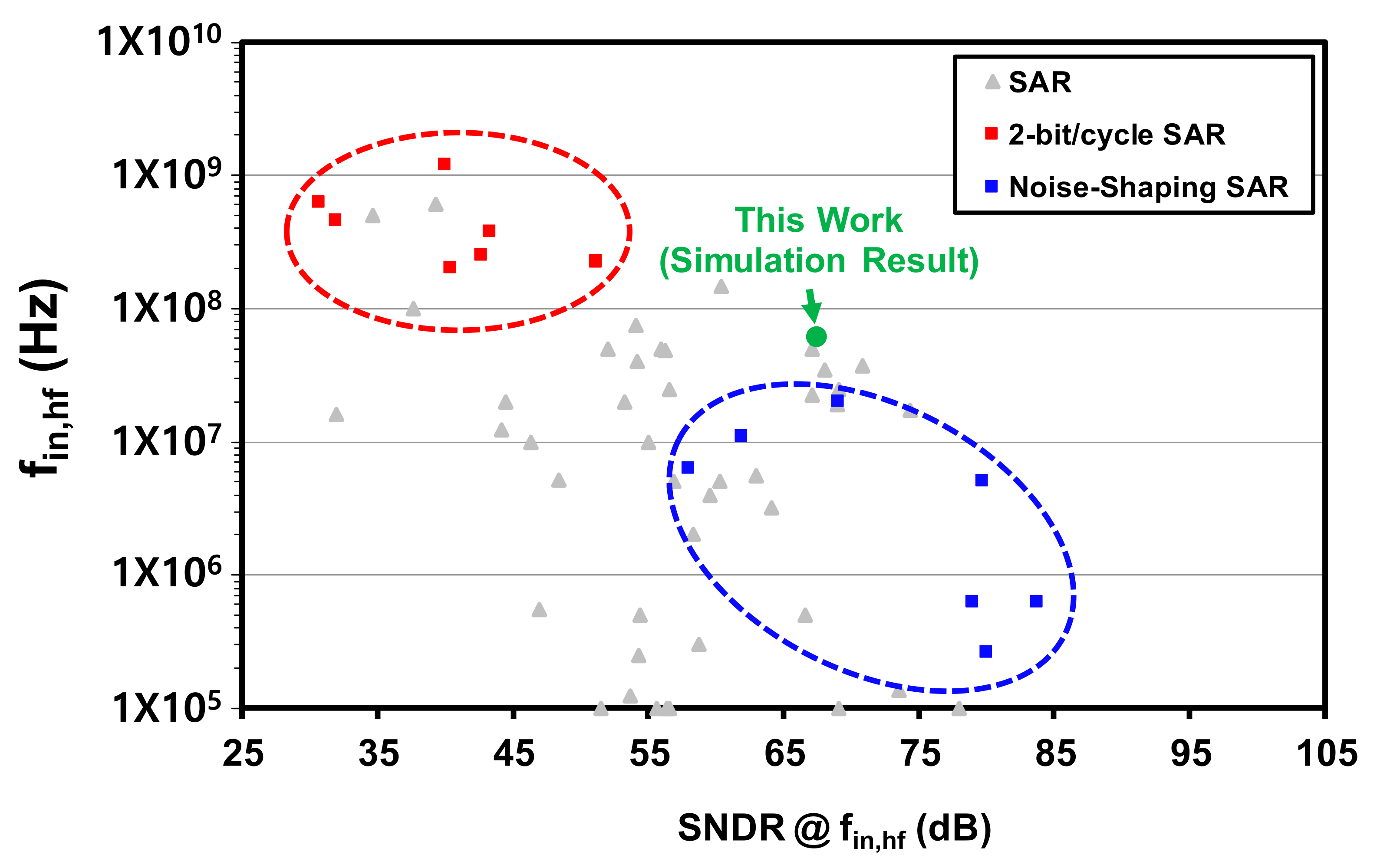

:1. Introduction

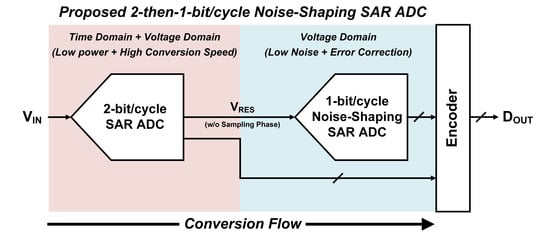

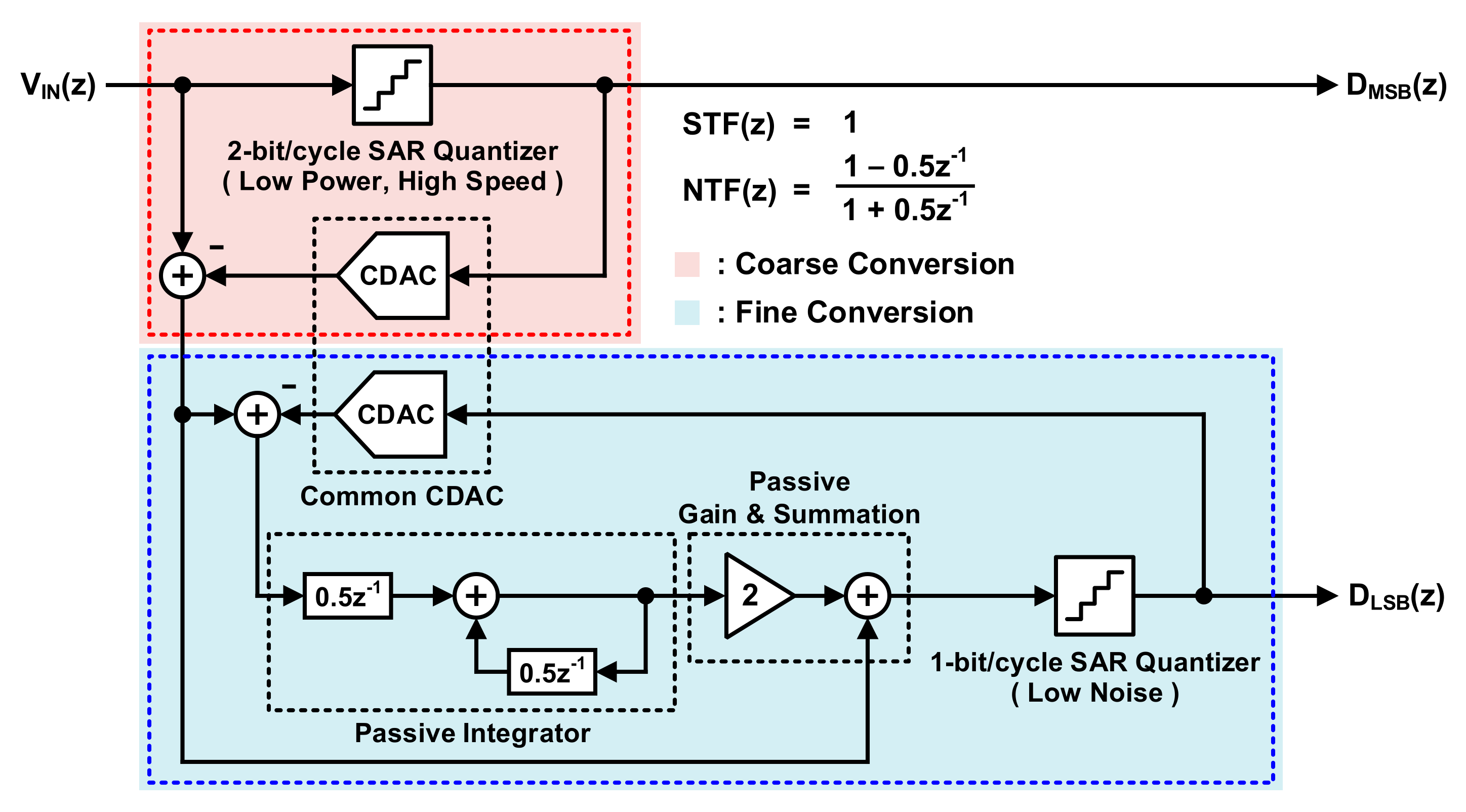

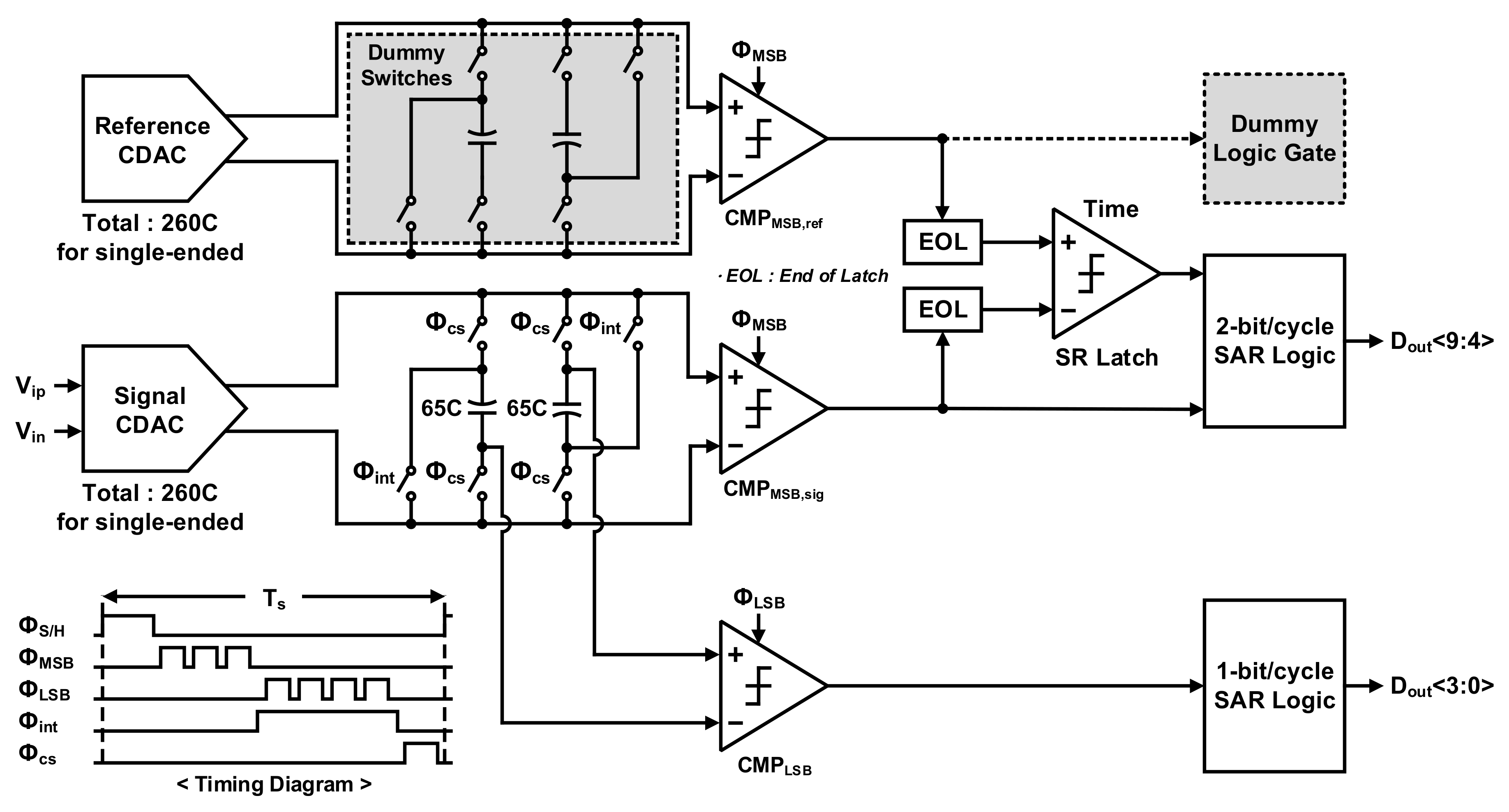

2. Proposed 2-then-1-bit/cycle Noise-Shaping SAR ADC Architecture

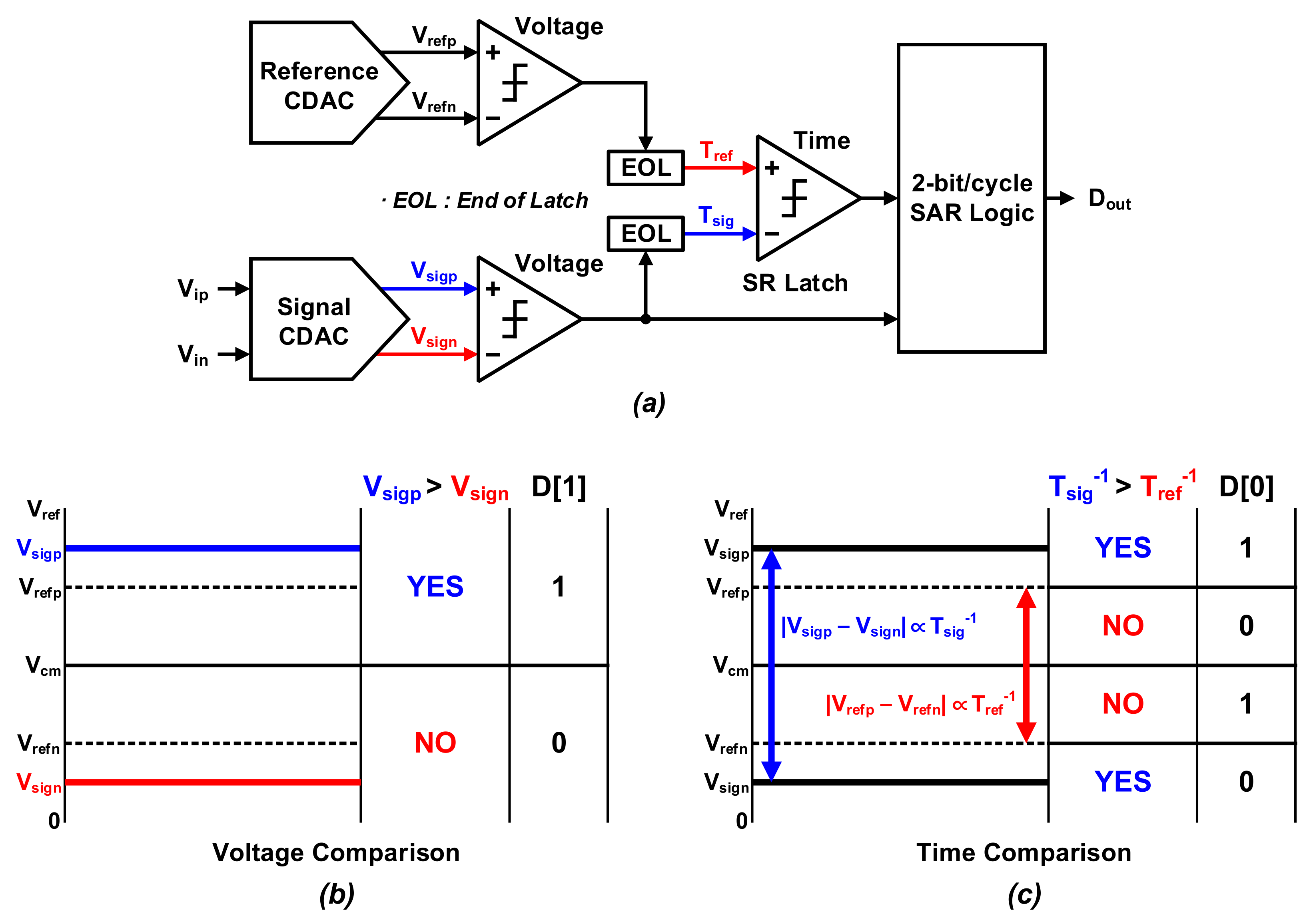

2.1. Coarse SAR Conversion

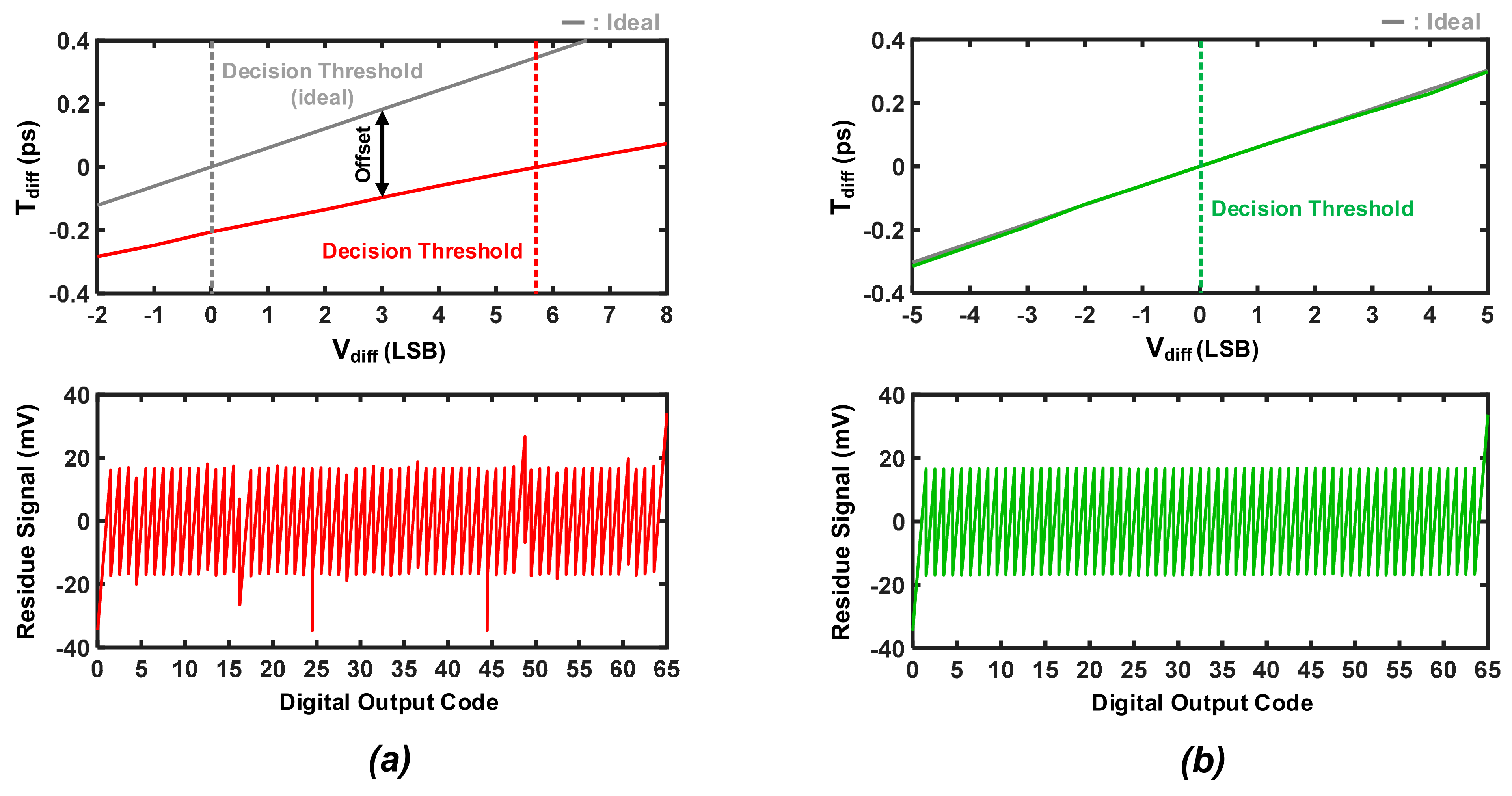

2.2. Jitter Error Correction with Redundancy

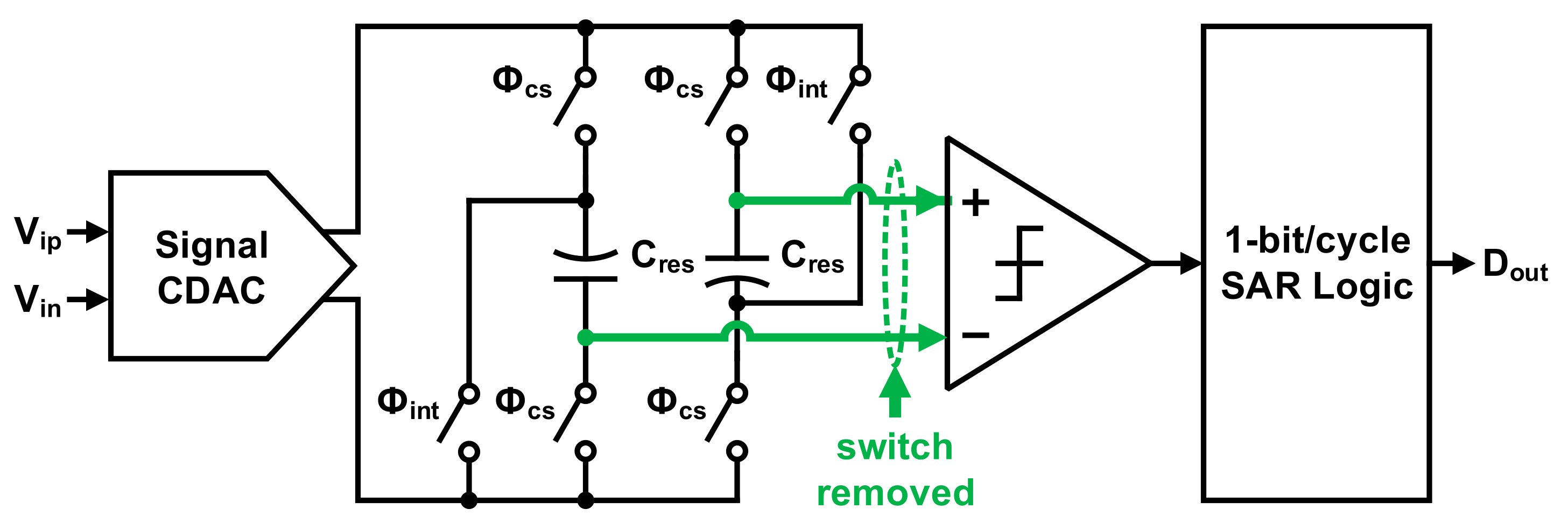

2.3. Fine SAR Conversion

3. Circuit Implementation

3.1. 2-then-1-bit/cycle Noise-Shaping SAR ADC

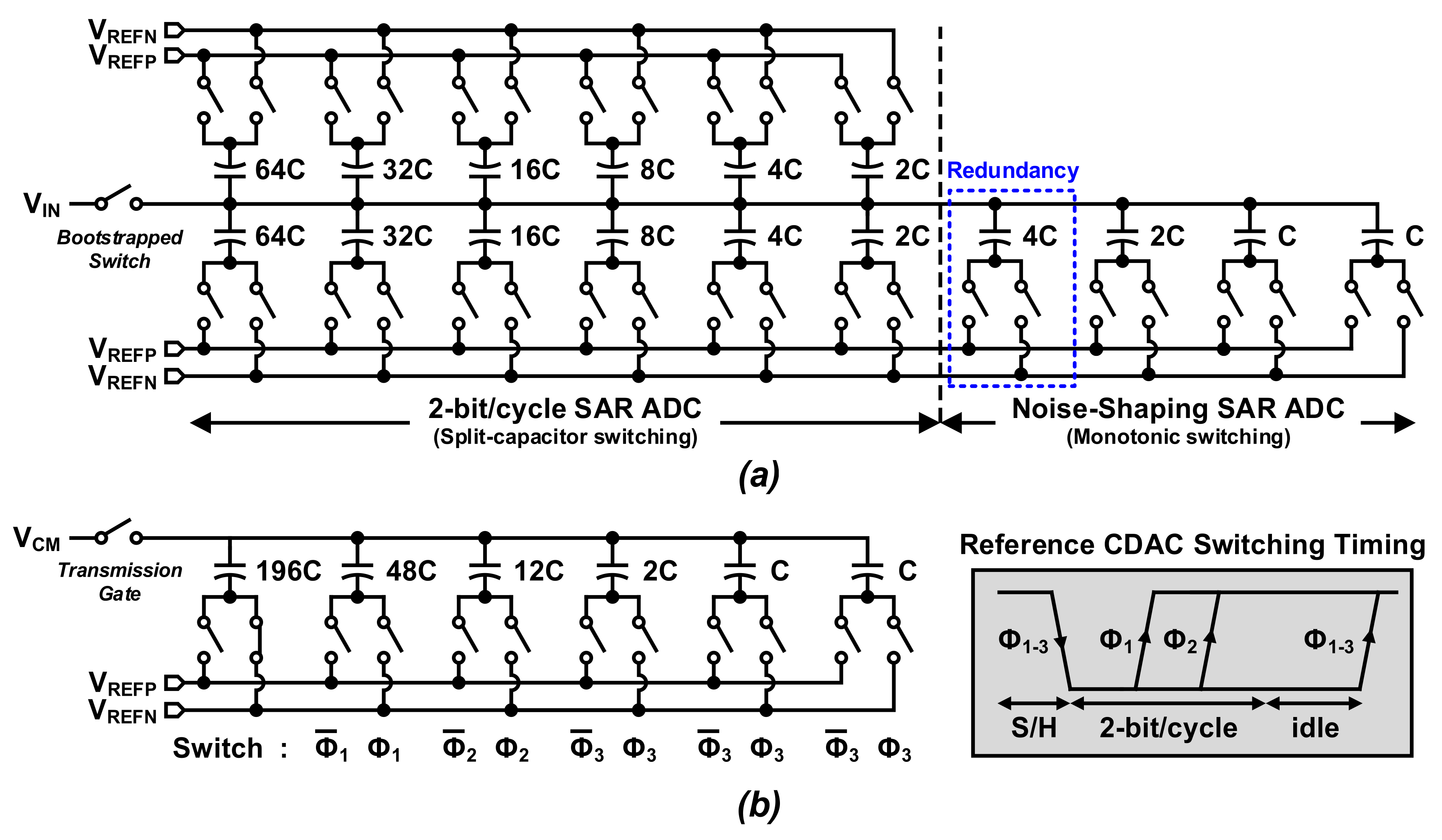

3.2. Signal CDAC and Reference CDAC

3.3. Redundant Bit Size

3.4. Proposed Tail-Current-Sharing Comparator

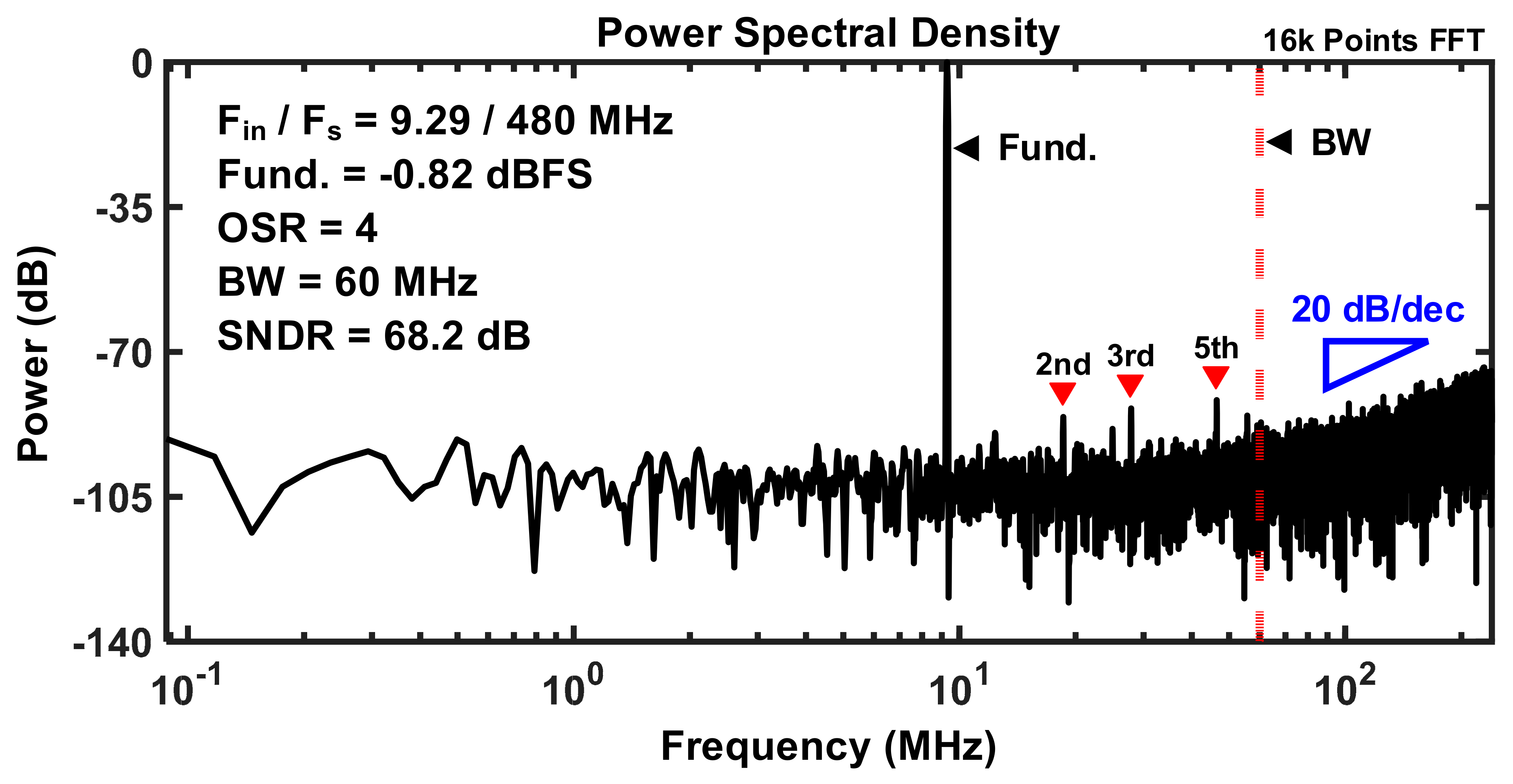

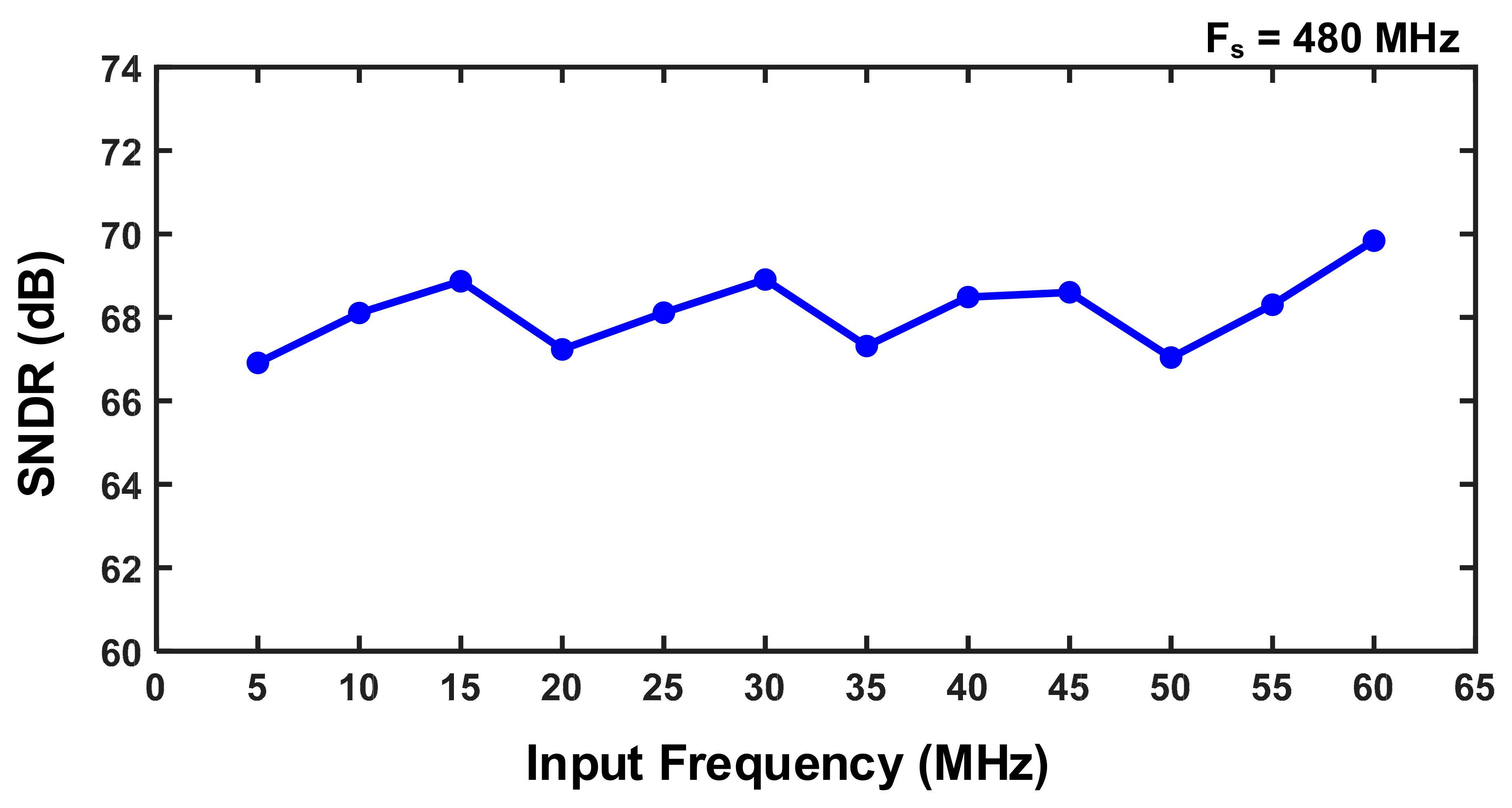

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Cao, Z.; Yan, S.; Li, Y. A 32 mW 1.25 GS/s 6b 2b/Step SAR ADC in 0.13 μm CMOS. IEEE J. Solid-State Circuits 2009, 44, 862–873. [Google Scholar] [CrossRef]

- Hong, H.; Kim, W.; Park, S.; Choi, M.; Park, H.; Ryu, S. A 7b 1GS/s 7.2 mW nonbinary 2b/cycle SAR ADC with register-to-DAC direct control. In Proceedings of the IEEE Custom Integrated Circuits Conference, San Jose, CA, USA, 9–12 September 2012. [Google Scholar]

- Frendenburg, J.; Flynn, M. A 90-MS/s 11-MHz-bandwidth 62-dB SNDR noise-shaping SAR ADC. IEEE J. Solid State Circuits 2012, 47, 2898–2904. [Google Scholar] [CrossRef]

- ADC Performance Survey 1997–2021. Available online: https://web.stanford.edu/~murmann/adcsurvey.html (accessed on 2 September 2021).

- Luo, J.; Liu, Y.; Li, J.; Ning, N.; Wu, K.; Liu, Z.; Yu, Q. A Low Voltage and Low Power 10-bit Non-Binary 2b/Cycle Time and Voltage Based SAR. IEEE Trans. Circuits Syst. I Regular. Pap. 2020, 67, 1136–1148. [Google Scholar] [CrossRef]

- Jie, L.; Zheng, B.; Flynn, M. 20.3 A 50MHz-Bandwidth 70.4dB-SNDR Calibration-Free Time-Interleaved 4th-Order Noise-Shaping SAR ADC. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019. [Google Scholar]

- Lin, Y.; Lin, C.; Tsai, S.; Lu, C. 20.2 A 40MHz-BW 320MS/s passive Noise-Shaping SAR ADC with Passive Signal-Residue Summation in 14nm FinFET. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019. [Google Scholar]

- Song, Y.; Chan, C.-H.; Zhu, Y.; Martins, R.P. A 12.5-MHz Bandwidth 77-dB SNDR SAR-Assisted Noise Shaping Pipeline ADC. IEEE J. Solid-State Circuits 2020, 55, 312–321. [Google Scholar] [CrossRef]

- Hsu, C.-K.; Tang, X.; Liu, J.; Xu, R.; Zhao, W.; Mukherjee, A.; Andeen, T.R.; Sun, N. A 77.1-dB-SNDR 6.25-MHz-BW Pipeline SAR ADC with Enhanced Interstage Gain Error Shaping and Quantization Noise Shaping. IEEE J. Solid-State Circuits 2021, 56, 739–749. [Google Scholar] [CrossRef]

- Ginsburg, B.; Chandrakasan, A. 500-MS/s 5-bit ADC in 65-nm CMOS with Split Capacitor Array DAC. IEEE J. Solid-State Circuits 2007, 42, 739–747. [Google Scholar] [CrossRef]

- Sanyal, A.; Sun, N. An Energy-Efficient Low Frequency-Dependence Switching Technique for SAR ADCs. IEEE Trans. Circuits Syst. II Express Briefs 2014, 65, 294–298. [Google Scholar]

- Babayan-M, S.; Lotfi, R. Analysis and design of a low-voltage low-power double-tail comparator. IEEE Trans. Very Large Scale Integr. Syst. 2014, 22, 343–352. [Google Scholar] [CrossRef]

- Miitteregger, G.; Ebner, C.; Mechnig, S.; Blon, T.; Holuigue, C.; Romani, E. A 20-mW 640-MHz CMOS Continuous-Time ΔΣ ADC with 20-MHz Signal Bandwidth, 80-dB Dynamic Range and 12-bit ENOB. IEEE J. Solid-State Circuits 2012, 41, 2641–2649. [Google Scholar] [CrossRef]

- Chan, C.; Zhu, Y.; Sin, S.U.; Martins, R.P. A 3.8mW 8b 1GS/s 2b/cycle interleaving SAR ADC with compact DAC structure. In Proceedings of the Symposium on VLSI Circuits Digest of Technical Papers, Honolulu, HI, USA, 13–15 June 2012. [Google Scholar]

- Lin, Y.; Tsai, C.; Tsou, S.; Chu, R.; Lu, C. A 2.4-mW 25-MHz BW 300-MS/s Passive Noise Shaping SAR ADC with Noise Quantizer Technique in 14-nm CMOS. In Proceedings of the Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017. [Google Scholar]

- Tsai, T.-H.; Tai, H.-Y.; Tsai, P.-Y.; Tsai, C.-H.; Chen, H.-S. An 8 b 700 MS/s 1 b/cycle SAR ADC using a delay-shift technique. IEEE Trans. Circuits Syst. I Regular. Pap. 2016, 63, 683–692. [Google Scholar] [CrossRef]

- Song, J.; Park, Y.; Lim, C.; Choi, Y.; Ahn, S.; Park, S.; Kim, C. A 9-bit 500-MS/s 2-bit/cycle SAR ADC with Error-Tolerant Interpolation Technique. IEEE J. Solid-State Circuits 2021. [Google Scholar] [CrossRef]

| [7] | [14] * | [15] | [16] | [17] | This Work | ||

|---|---|---|---|---|---|---|---|

| Process (nm) | 14 | 65 | 14 | 40 | 28 | 28 | |

| Supply (V) | 0.9 | 1.2 | 1 | 1.2 | 1.0 | 1.1 | |

| Resolution (bits) | 10 | 8 | 8 | 8 | 9 | 9 | |

| Architecture | 1-bit/cycle noise-shaping | 2-bit/cycle | 1-bit/cycle noise-shaping | 1-bit/cycle | 1-then-2-bit/cycle | 1-bit/cycle noise-shaping | 2-then-1-bit/cycle noise-shaping |

| Power (mW) | 1.25 | 1.9 | 2.4 | 5 | 1.87 | 1.57 | 2.13 |

| Total cycles | 10 + 3 ** | 4 | 10 + 3 ** | 8 | 5 | 9 + 1 ** | 6 + 1 ** |

| Fs (MS/s) | 320 | 500 | 300 | 700 | 500 | 360 | 480 |

| OSR | 4 | 1 | 6 | 1 | 1 | 4 | 4 |

| BW (MHz) | 40 | 250 | 25 | 350 | 250 | 45 | 60 |

| SNDR (dB) | 66.6 | 42.98 | 69.1 | 43.9 | 50.6 | 68.4 | 68.2 |

| FoMs (dB) | 171.7 | 154.2 | 169.3 | 152.4 | 161.9 | 173 | 172.7 |

| Measurement | Experiment | Experiment | Experiment | Experiment | Experiment | Simulation | Simulation |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, K.; Oh, S.; Chae, H. Conception and Simulation of a 2-Then-1-Bit/Cycle Noise-Shaping SAR ADC. Electronics 2021, 10, 2545. https://doi.org/10.3390/electronics10202545

Kim K, Oh S, Chae H. Conception and Simulation of a 2-Then-1-Bit/Cycle Noise-Shaping SAR ADC. Electronics. 2021; 10(20):2545. https://doi.org/10.3390/electronics10202545

Chicago/Turabian StyleKim, Kihyun, Sein Oh, and Hyungil Chae. 2021. "Conception and Simulation of a 2-Then-1-Bit/Cycle Noise-Shaping SAR ADC" Electronics 10, no. 20: 2545. https://doi.org/10.3390/electronics10202545

APA StyleKim, K., Oh, S., & Chae, H. (2021). Conception and Simulation of a 2-Then-1-Bit/Cycle Noise-Shaping SAR ADC. Electronics, 10(20), 2545. https://doi.org/10.3390/electronics10202545