Experimental Validation of Metaheuristic and Conventional Modulation, and Hysteresis Control of the Dual Boost Nine-Level Inverter

Abstract

1. Introduction

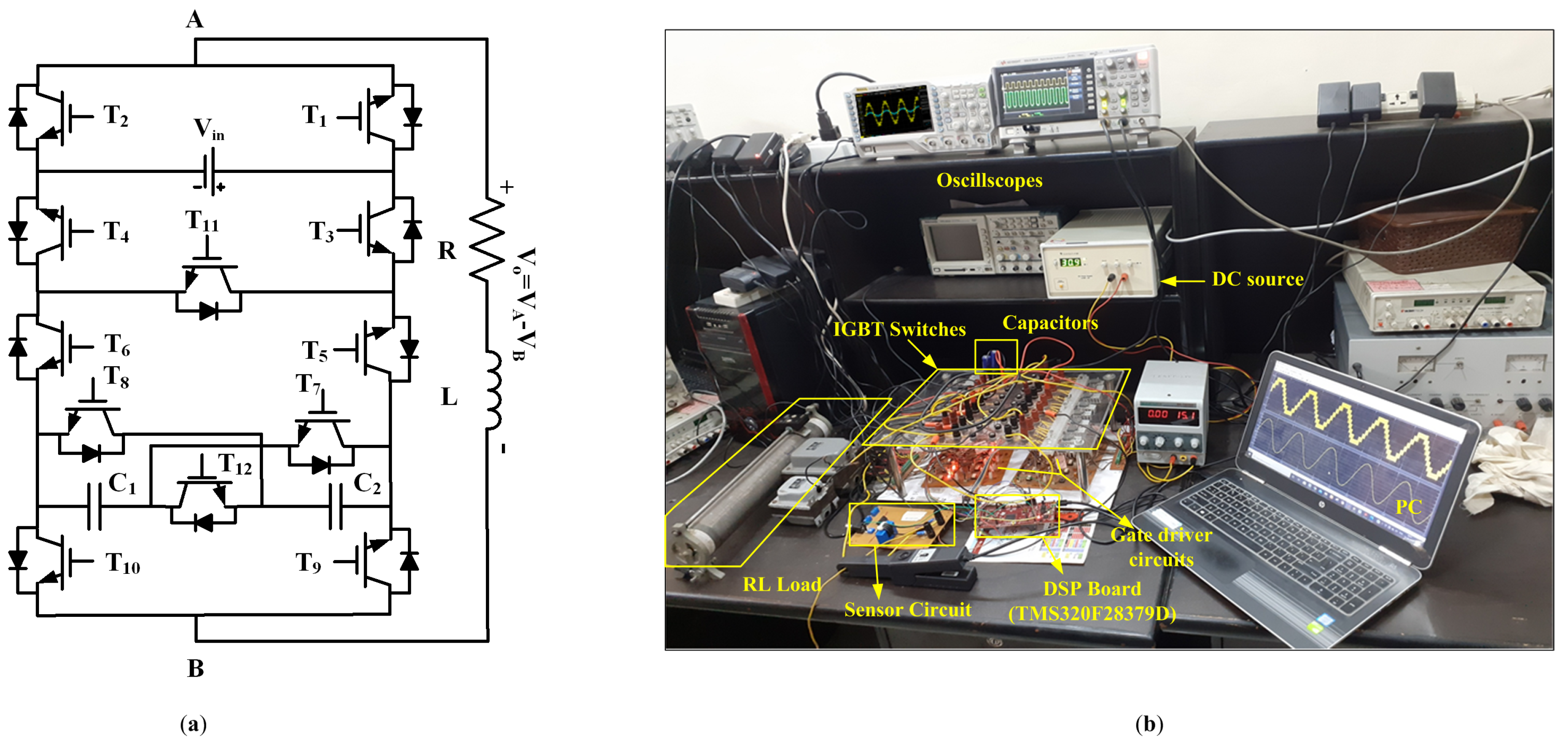

2. DB9LI Operation and Assessment

2.1. Operation of DB9LI

2.2. Assessment of DB9LI

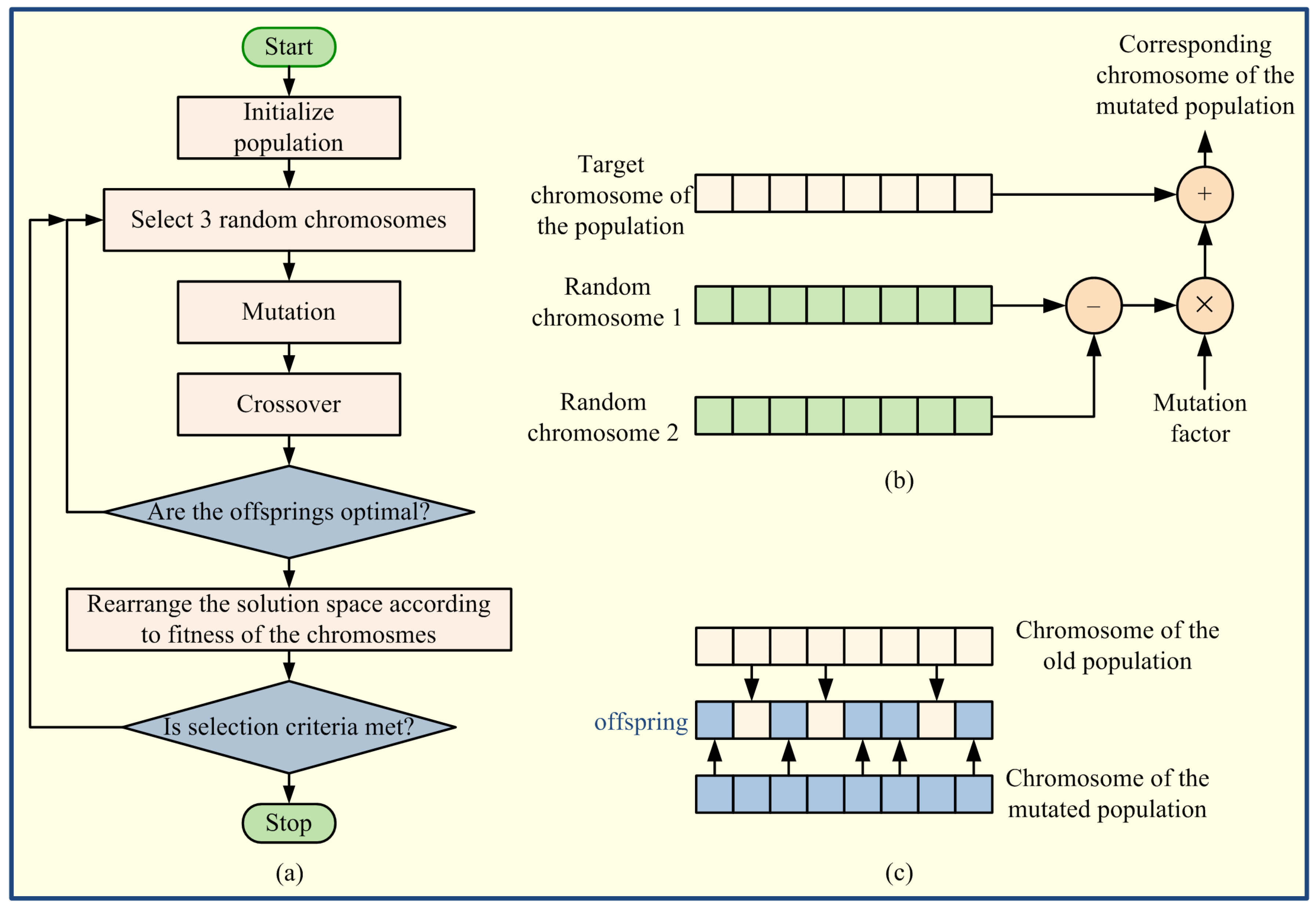

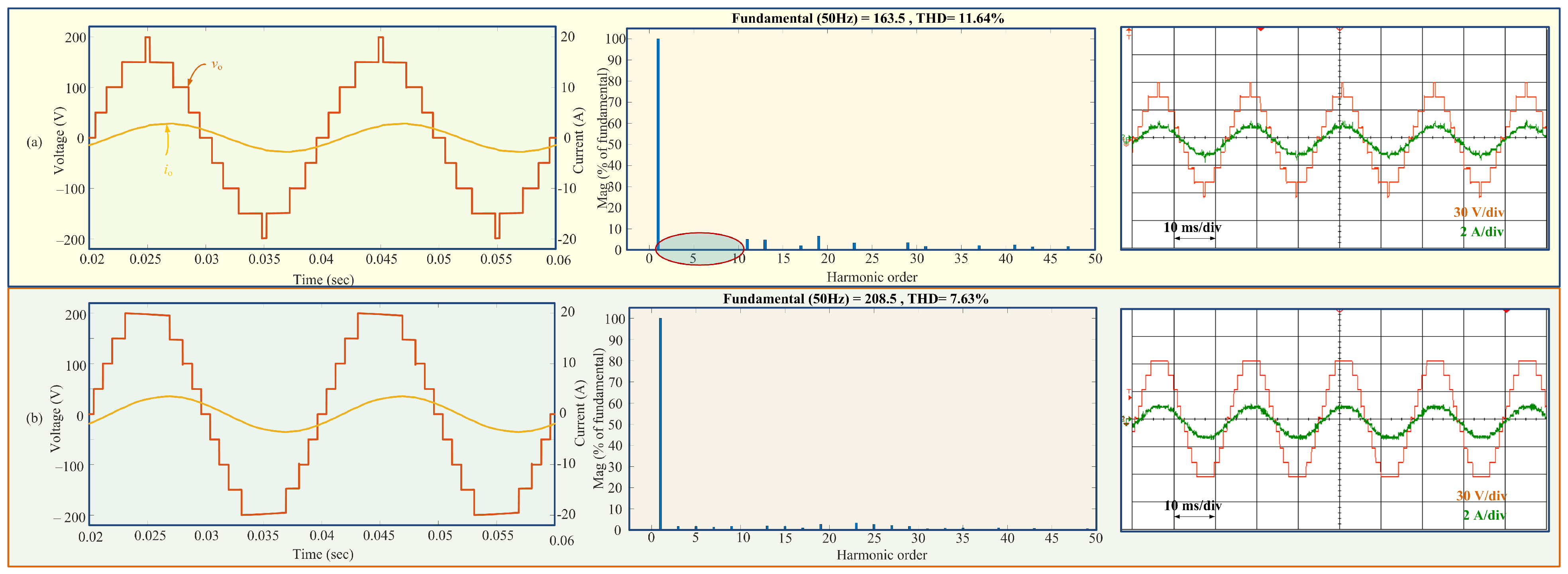

3. Metaheuristic-Based Modulation of DB9LI

3.1. Selective Harmonic Elimination and Mitigation

3.2. Differential Evolution

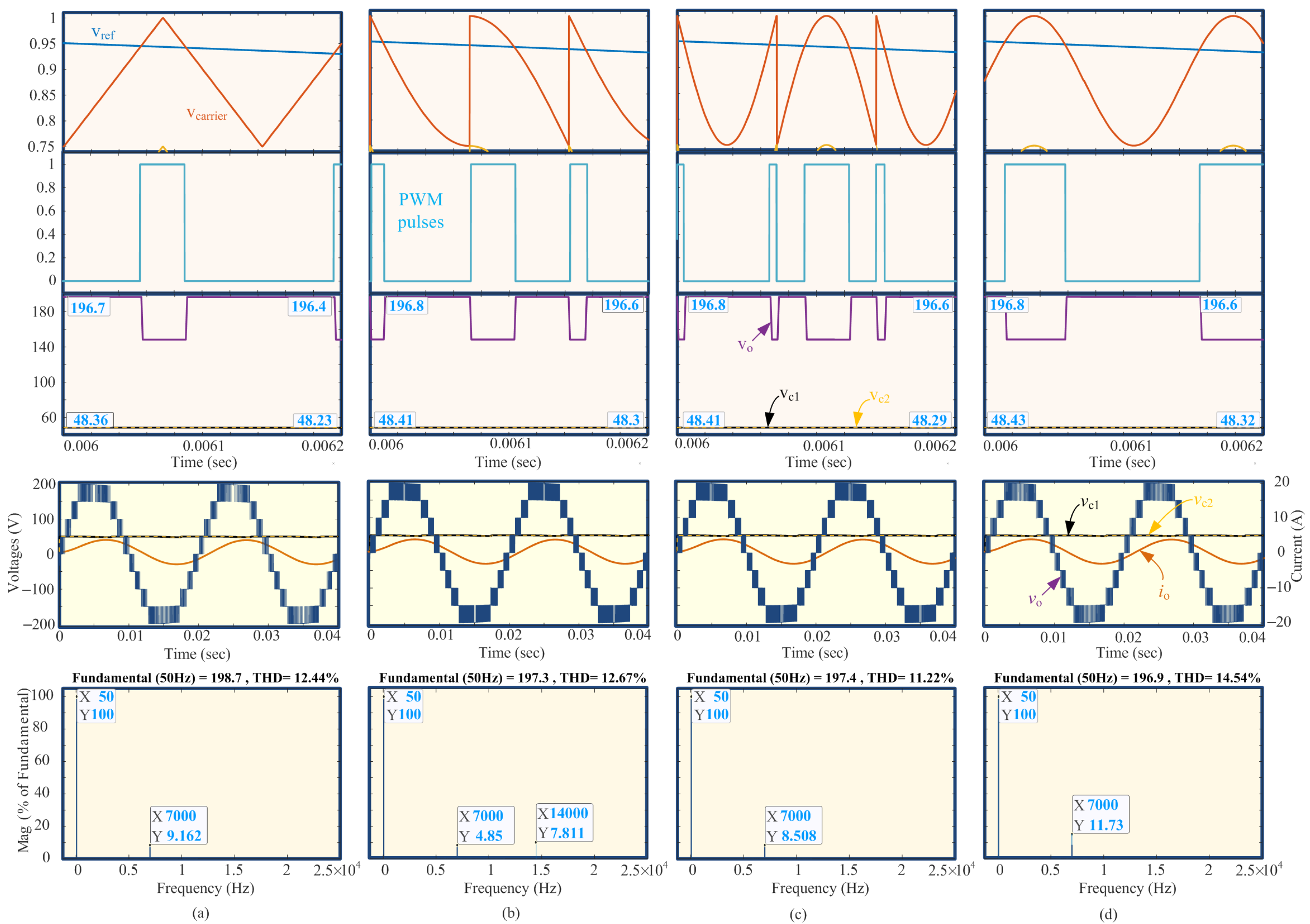

4. Pulse-Width Modulation of DB9LI

4.1. Control Strategy

4.2. Results and Discussion

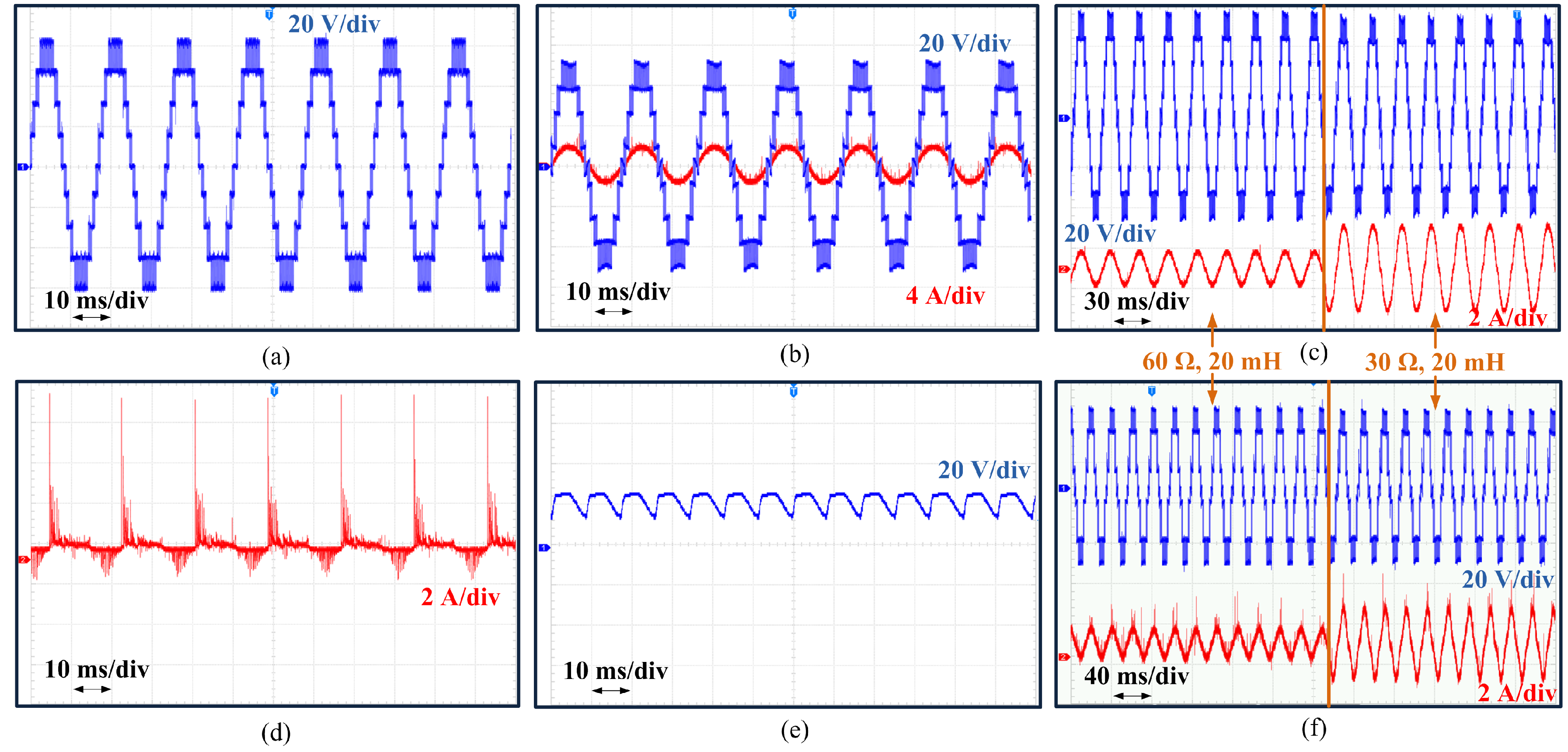

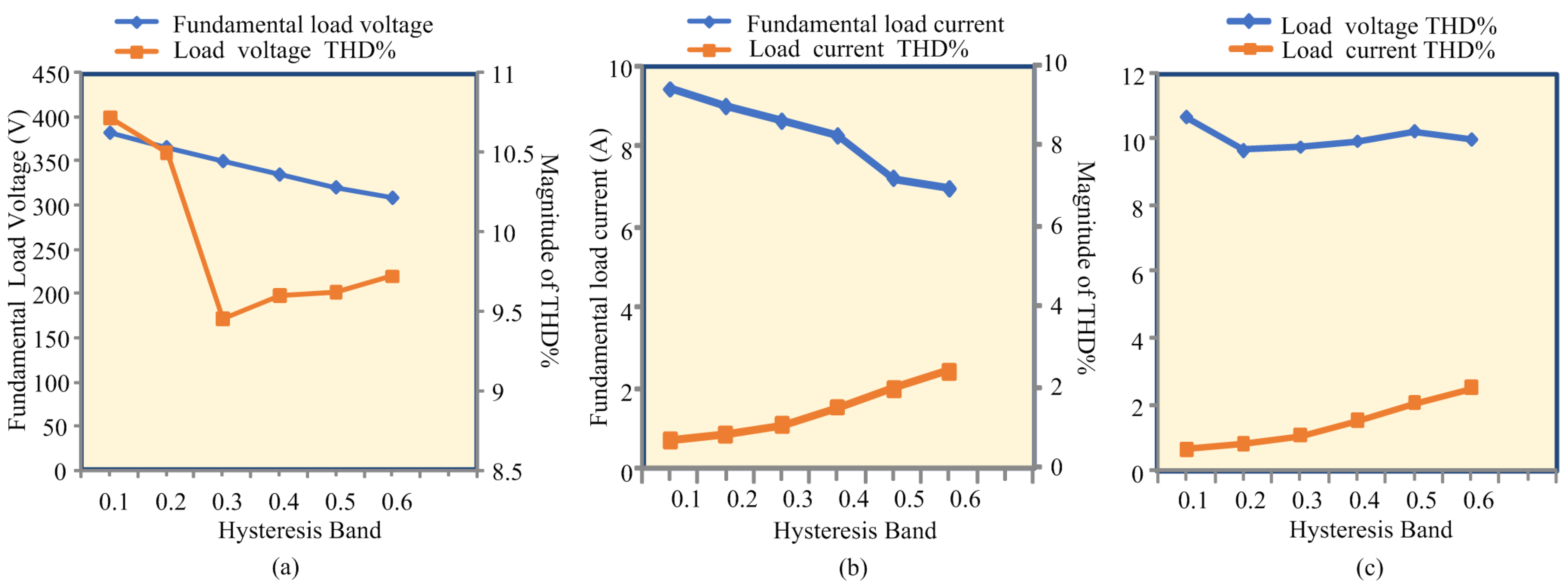

5. Hysteresis Control of DB9LI

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Norambuena, M.; Kouro, S.; Dieckerhoff, S.; Rodríguez, J. Reduced Multilevel Converter: A Novel Multilevel Converter with Reduced Number of Active Switches. IEEE Trans. Ind. Electron. 2017, 65, 3636–3645. [Google Scholar] [CrossRef]

- Vahedi, H.; Shojaei, A.A.; Dessaint, L.A.; Al-Haddad, K. Reduced DC-Link Voltage Active Power Filter Using Modified PUC5 Converter. IEEE Trans. Power Electron. 2018, 33, 943–947. [Google Scholar] [CrossRef]

- Gontijo, G.; Wang, S.; Kerekes, T.; Teodorescu, R. New ac-ac modular multilevel converter solution for medium-voltage machine-drive applications: Modular multilevel series converter. Energies 2020, 13, 3664. [Google Scholar] [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A survey on neutral-point-clamped inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Tackie, S.N.; Babaei, E. Modified topology for three-phase multilevel inverters based on a developed H-bridge inverter. Electronics 2020, 9, 1848. [Google Scholar] [CrossRef]

- Laali, S.; Babaei, E. Optimum Structures of Proposed New Cascaded Multilevel Inverter with Reduced Number of Components. IEEE Trans. Ind. Electron. 2015, 62, 6887–6895. [Google Scholar] [CrossRef]

- Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. IEEE Trans. Ind. Electron. 2010, 57, 2197–2206. [Google Scholar] [CrossRef]

- Lai, Y.; Shyu, F. New topology for hybrid multilevel inverter. In Proceedings of the 2002 International Conference on Power Electronics, Machines and Drives (Conf. Publ. No. 487), Sante Fe, NM, USA, 4–7 June 2002; pp. 1–6. [Google Scholar]

- Thamizharasan, S.; Baskaran, J.; Ramkumar, S.; Jeevananthan, S. Electrical Power and Energy Systems A new dual bridge multilevel dc-link inverter topology. Electr. Power Energy Syst. 2013, 45, 376–383. [Google Scholar] [CrossRef]

- Rech, C.; Pinheiro, J.R. Hybrid Multilevel Converters: Unified Analysis and Design Considerations. IEEE Trans. Ind. Electron. 2007, 54, 1092–1104. [Google Scholar] [CrossRef]

- Azimi, E.; Khodaparast, A.; Rostami, M.J.; Adabi, J.; Adabi, M.E.; Rezanejad, M.; Rodrigues, E.M.G.; Pouresmaeil, E. X-Type Step-Up Multi-Level Inverter with Reduced Component Count Based on Switched-Capacitor Concept. Electronics 2020, 9, 1987. [Google Scholar] [CrossRef]

- Ramkumar, S.; Kamaraj, V.; Thamizharasan, S.; Jeevananthan, S. A new series parallel switched multilevel dc-link inverter topology. Electr. Power Energy Syst. 2012, 36, 93–99. [Google Scholar] [CrossRef]

- Sato, Y.; Member, S.; Uno, M.; Nagata, H. Nonisolated Multiport Converters Based on Integration of PWM Converter and Phase-Shift Switched Capacitor Converter. IEEE Trans. Power Electron. 2020, 35, 455–470. [Google Scholar] [CrossRef]

- Gupta, K.K.; Ranjan, A.; Bhatnagar, P.; Sahu, L.K.; Jain, S. Multilevel Inverter Topologies With Reduced Device Count: A Review. IEEE Trans. Power Electron. 2016, 31, 135–151. [Google Scholar] [CrossRef]

- Zhang, C.; Gao, Z. A Novel Multilevel DC/AC Inverter Based on Three-Level Half Bridge with Voltage Vector Selecting Algorithm. IEEE Access 2019, 7, 88733–88742. [Google Scholar] [CrossRef]

- Dhanamjayulu, C.; Meikandasivam, S. Implementation and Comparison of Symmetric and Asymmetric Multilevel Inverters for Dynamic Loads. IEEE Access 2017, 6, 738–746. [Google Scholar] [CrossRef]

- Karthikeyan, D.; Vijayakumar, K.; Jagabar Sathik, M. Generalized cascaded symmetric and level doubling multilevel converter topology with reduced THD for photovoltaic applications. Electronics 2019, 8, 161. [Google Scholar] [CrossRef]

- Kang, J.W.; Hyun, S.W.; Ha, J.O.; Won, C.Y. Improved neutral-point voltage-shifting strategy for power balancing in cascaded NPC/H-bridge inverter. Electronics 2018, 7, 167. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Self-Balanced Step-Up Multilevel Inverter Based on Switched-Capacitor Structure. IEEE Trans. Power Electron. 2018, 33, 199–209. [Google Scholar] [CrossRef]

- Taghvaie, A.; Adabi, J.; Rezanejad, M. A Multilevel Inverter Structure based on Combination of Switched-Capacitors and DC Sources. IEEE Trans. Ind. Inform. 2017, 13, 2162–2171. [Google Scholar] [CrossRef]

- Vahedi, H.; Sharifzadeh, M.; Al-Haddad, K. Modified Seven-Level Pack U-Cell Inverter for Photovoltaic Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1508–1516. [Google Scholar] [CrossRef]

- Iqbal, A.; Meraj, M.; Tariq, M.; Lodi, K.A.; Maswood, A.I. Experimental Investigation and Comparative Evaluation of Standard Level Shifted Multi- Carrier Modulation Schemes with a Constraint GA Based SHE Techniques for Seven-Level. IEEE Access 2019, 7, 100605–100617. [Google Scholar] [CrossRef]

- Shojaei, A.A.; Najafi, B.; Vahedi, H. Standalone operation of modified seven-level packed U-Cell (MPUC) single-phase inverter. Electronics 2019, 8, 268. [Google Scholar] [CrossRef]

- Ounejjar, Y.; Al-Haddad, K.; Dessaint, L.A. A Novel Six-Band Hysteresis Control for the Packed U Cells Seven-Level Converter: Experimental Validation. IEEE Trans. Ind. Electron. 2012, 59, 3808–3816. [Google Scholar] [CrossRef]

- Shuvo, S.; Hossain, E.; Islam, T.; Akib, A.; Padmanaban, S.; Khan, M.Z.R. Design and Hardware Implementation Considerations of Modified Multilevel Cascaded H-Bridge Inverter for Photovoltaic System. IEEE Access 2019, 7, 16504–16524. [Google Scholar] [CrossRef]

- Sharifzadeh, M.; Al-Haddad, K. Packed E-Cell (PEC) Converter Topology Operation and Experimental Validation. IEEE Access 2019, 7, 93049–93061. [Google Scholar] [CrossRef]

- Sebaaly, F.; Sharifzadeh, M.; Kanaan, H.Y.; Al-haddad, K. Multilevel Switching Mode Operation of Finite Set Model Predictive Control for Grid-Connected Packed E-Cell (PEC) Inverter. IEEE Trans. Ind. Electron. 2020. [Google Scholar] [CrossRef]

- Babaei, E.; Kangarlu, M.F.; Mazgar, F.N. Symmetric and asymmetric multilevel inverter topologies with reduced switching devices. Electr. Power Syst. Res. 2012, 86, 122–130. [Google Scholar] [CrossRef]

- Sharifzadeh, M.; Vahedi, H.; Al-Haddad, K. New Constraint in SHE-PWM for Single-Phase Inverter Applications. IEEE Trans. Ind. Appl. 2018, 54, 4554–4562. [Google Scholar] [CrossRef]

- Al-Hitmi, M.; Ahmad, S.; Iqbal, A.; Padmanaban, S.; Ashraf, I. Selective Harmonic Elimination in a Wide Modulation Range using Modified Newton-Raphson and Pattern Generation Methods for a Multilevel Inverter. Energies 2018, 11, 458. [Google Scholar] [CrossRef]

- Lodi, K.A.; Azeem, A.; Tariq, M.; Ali, M.; Bharatiraja, C. Harmonic Minimization in Modified PUC-5 Inverter Using Genetic Algorithm. In Proceedings of the 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Chennai, India, 18–21 December 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Luo, L.; Abdulkareem, S.S.; Rezvani, A.; Miveh, M.R.; Samad, S.; Aljojo, N.; Pazhoohesh, M. Optimal scheduling of a renewable based microgrid considering photovoltaic system and battery energy storage under uncertainty. J. Energy Storage 2020, 28, 101306. [Google Scholar] [CrossRef]

- Ali, M.; Iqbal, A.; Anees, M.A.; Khan, M.R.; Rahman, K.; Ayyub, M. Differential evolution-based pulse-width modulation technique for multiphase MC. IET Power Electron. 2019, 12, 2224–2235. [Google Scholar] [CrossRef]

- Shukla, A.; Ghosh, A.; Joshi, A. Hysteresis Modulation of Multilevel Inverters. IEEE Trans. Power Electron. 2011, 26, 1396–1409. [Google Scholar] [CrossRef]

- Sarkar, I.; Fernandes, B.G. Multi-carrier Based Hysteresis Current Control Technique For Five-Level Symmetric Cascaded Multilevel Converter. In Proceedings of the 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivandrum, India, 14–17 December 2016; pp. 1–6. [Google Scholar]

- Ounejjar, Y.; Al-Haddad, K. Multiband Hysteresis Controller Of The Novel Three Phase Seven-Level PUC-NPC Converter. In Proceedings of the 39th Annual Conference of the IEEE Industrial Electronics Society (IECON 2013), Vienna, Austria, 10–13 November 2013; pp. 6257–6262. [Google Scholar]

- Saeedian, M.; Pouresmaeil, E.; Samadaei, E.; Rodrigues, E.M.G.; Godina, R.; Marzband, M. An Innovative Dual-Boost Nine-Level Inverter with Low-Voltage Rating Switches. Energies 2019, 12, 207. [Google Scholar] [CrossRef]

- Siddique, M.D.; Iqbal, A.; Sathik, J.; Mekhilef, S.; Almakhles, D. Design and implementation of a new unity gain nine-level active neutral point clamped multilevel inverter topology. IET Power Electron. 2020, 13, 3204–3208. [Google Scholar] [CrossRef]

- Lee, S.S. Single-Stage Switched-Capacitor Module (S3CM) Topology for Cascaded Multilevel Inverter. IEEE Trans. Power Electron. 2018, 33, 8204–8207. [Google Scholar] [CrossRef]

- Nakagawa, Y.; Koizumi, H. A Boost-Type Nine-Level Switched Capacitor Inverter. IEEE Trans. Power Electron. 2019, 34, 6522–6532. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Moradzadeh, M.; Zamiri, E.; Madadi Kojabadi, H.; Blaabjerg, F. A New Boost Switched-Capacitor Multilevel Converter with Reduced Circuit Devices. IEEE Trans. Power Electron. 2018, 33, 6738–6754. [Google Scholar] [CrossRef]

- Sathik, M.J.; Krishnasamy, V. Compact Switched Capacitor Multilevel Inverter (CSCMLI) with Self-Voltage Balancing and Boosting Ability. IEEE Trans. Power Electron. 2019, 34, 4009–4013. [Google Scholar] [CrossRef]

- Siddique, M.D.; Member, S.; Mekhilef, S.; Member, S.; Mohamed, N. A New Switched Capacitor 7L Inverter with Triple Voltage Gain and Low Voltage Stress. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1294–1298. [Google Scholar] [CrossRef]

- Rout, U.K.; Sahu, R.K.; Panda, S. Design and analysis of differential evolution algorithm based automatic generation control for interconnected power system. Ain Shams Eng. J. 2013, 4, 409–421. [Google Scholar] [CrossRef]

- Eltaeib, T.; Mahmood, A. Differential evolution: A survey and analysis. Appl. Sci. 2018, 8, 1945. [Google Scholar] [CrossRef]

| S. No. | Parameters | Simulation Value | Experimental Value | Quantity |

|---|---|---|---|---|

| 1. | DC Source Voltage | 100 V | 30 V | 1 |

| 2. | Capacitors | 4700 F | 4700 F, 50 V | 2 |

| 3. | Resistive Load | 30 , 60 | 30 , 60 | 2 |

| 4. | Inductive Load | 20 mH | 20 mH | 1 |

| 5. | Power frequency | 50 Hz | 50 Hz | - |

| 6. | Switching frequency | 7 kHz | 7 kHz | - |

| 7. | Controller | MATLAB/Simulink | TMS320F28379D | 1 |

| Switches | Switching Sequence | ||||||||

|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | |

| 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | |

| 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | |

| Levels | 2 | 1.5 | 0.5 | 0 | −0.5 | −1.5 | −2 | ||

| Parameters | [43] | [39] | [41] | [42] | [41] | Investigated |

|---|---|---|---|---|---|---|

| Levels | 7 | 9 | 9 | 9 | 9 | 9 |

| Switches | 12 | 12 | 12 | 11 | 10 | 12 |

| DC sources | 1 | 1 | 1 | 1 | 1 | 1 |

| Capacitors | 2 | 2 | 3 | 2 | 2 | 2 |

| Boosting | 3 | 2 | 4 | 2 | 2 | 2 |

| TSV | 5.3 | 5.5 | 6 | 5 | 7.7 | 5.25 |

| S. No. | Parameter | Value |

|---|---|---|

| 1. | No. of variables | 4 |

| 2. | Initial Population | 50 |

| 3. | Mutation factor | 0.5 |

| 4. | Iterations | 100 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Upadhyay, D.; Khan, S.A.; Ali, M.; Tariq, M.; Sarwar, A.; Chakrabortty, R.K.; Ryan, M.J. Experimental Validation of Metaheuristic and Conventional Modulation, and Hysteresis Control of the Dual Boost Nine-Level Inverter. Electronics 2021, 10, 207. https://doi.org/10.3390/electronics10020207

Upadhyay D, Khan SA, Ali M, Tariq M, Sarwar A, Chakrabortty RK, Ryan MJ. Experimental Validation of Metaheuristic and Conventional Modulation, and Hysteresis Control of the Dual Boost Nine-Level Inverter. Electronics. 2021; 10(2):207. https://doi.org/10.3390/electronics10020207

Chicago/Turabian StyleUpadhyay, Deepak, Shahbaz Ahmad Khan, Mohammad Ali, Mohd Tariq, Adil Sarwar, Ripon K. Chakrabortty, and Michael J. Ryan. 2021. "Experimental Validation of Metaheuristic and Conventional Modulation, and Hysteresis Control of the Dual Boost Nine-Level Inverter" Electronics 10, no. 2: 207. https://doi.org/10.3390/electronics10020207

APA StyleUpadhyay, D., Khan, S. A., Ali, M., Tariq, M., Sarwar, A., Chakrabortty, R. K., & Ryan, M. J. (2021). Experimental Validation of Metaheuristic and Conventional Modulation, and Hysteresis Control of the Dual Boost Nine-Level Inverter. Electronics, 10(2), 207. https://doi.org/10.3390/electronics10020207