Load-Independent Voltage Balancing of Multi-Level Flying Capacitor Converters in Quasi-2-Level Operation

Abstract

:1. Introduction

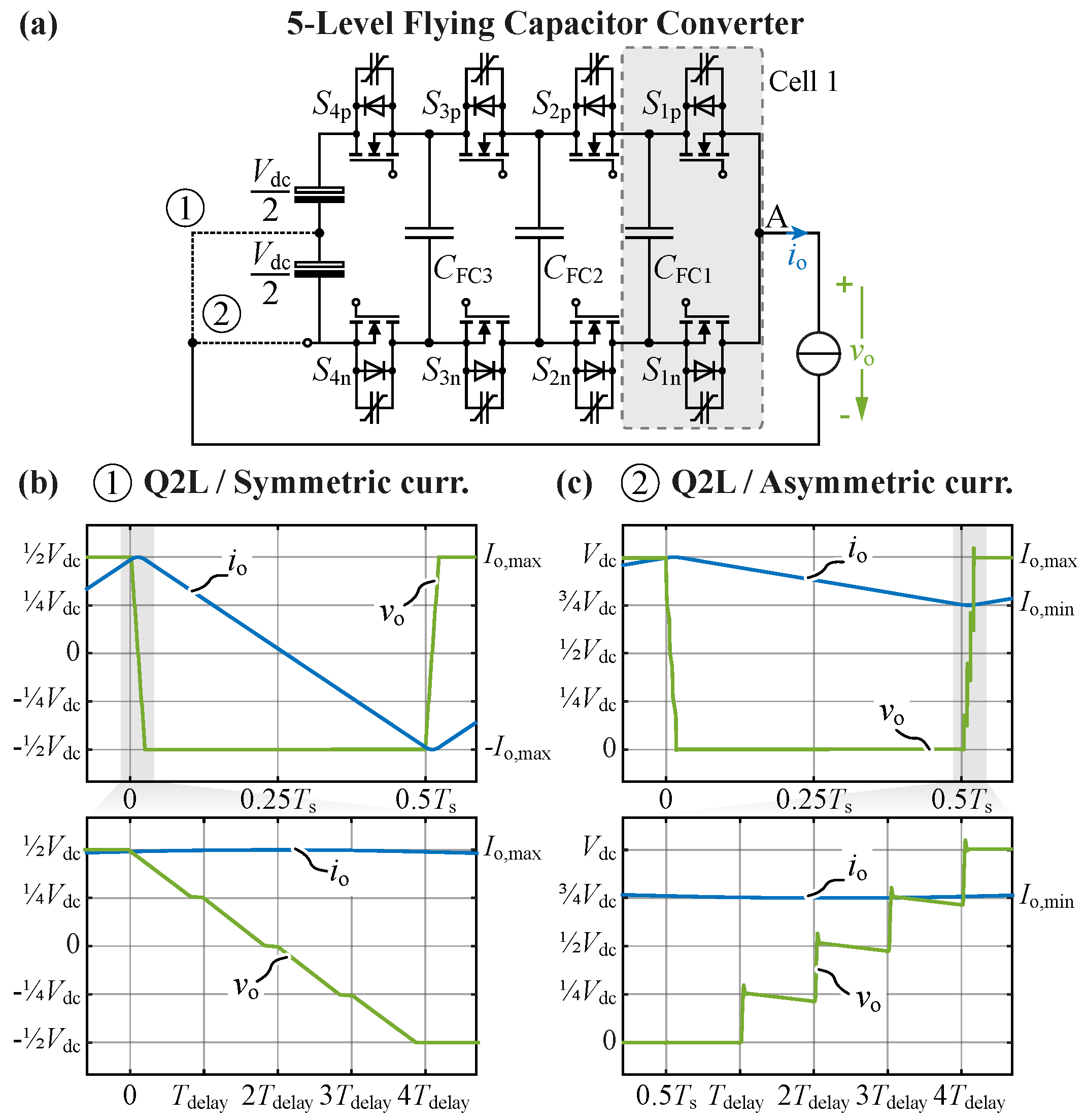

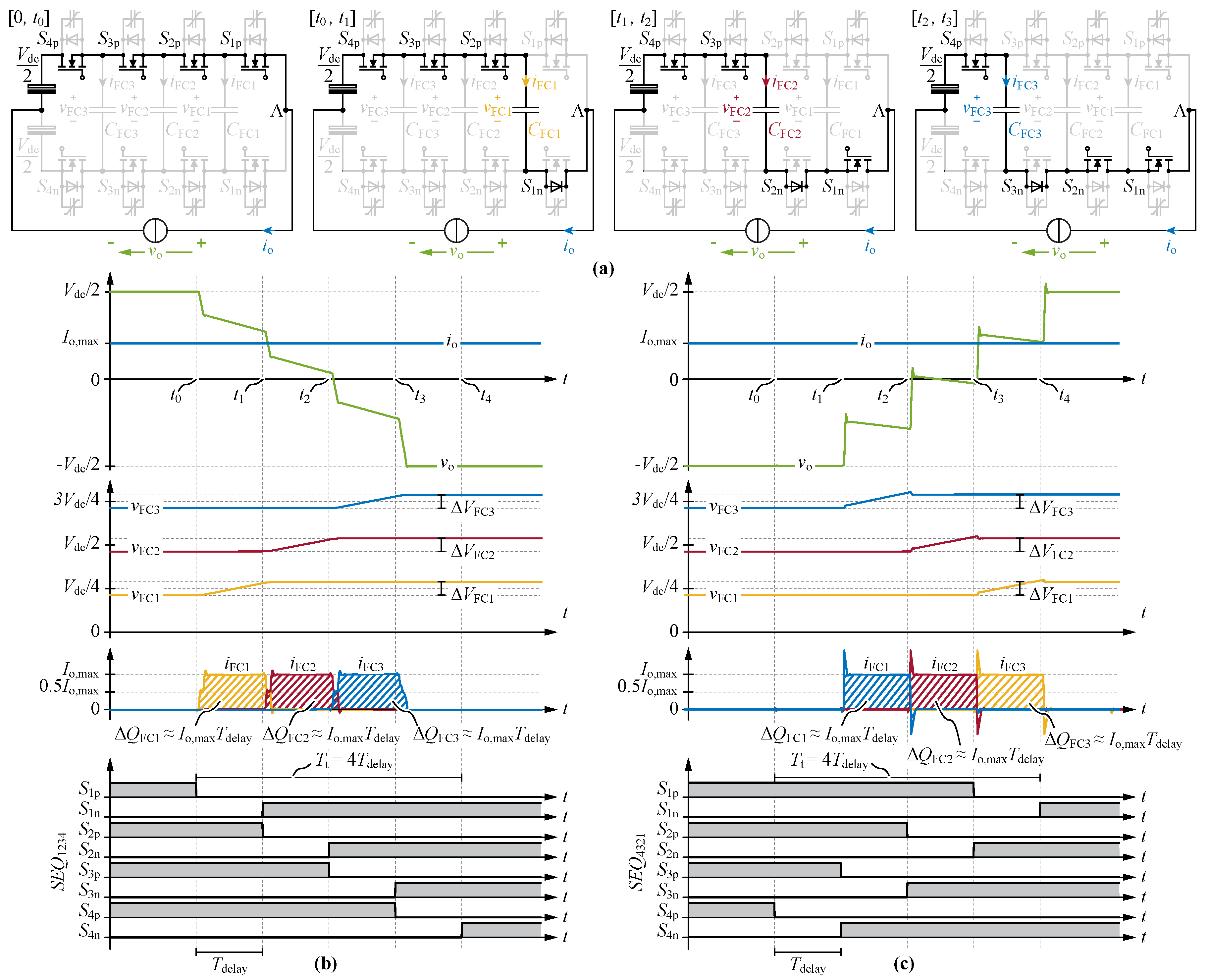

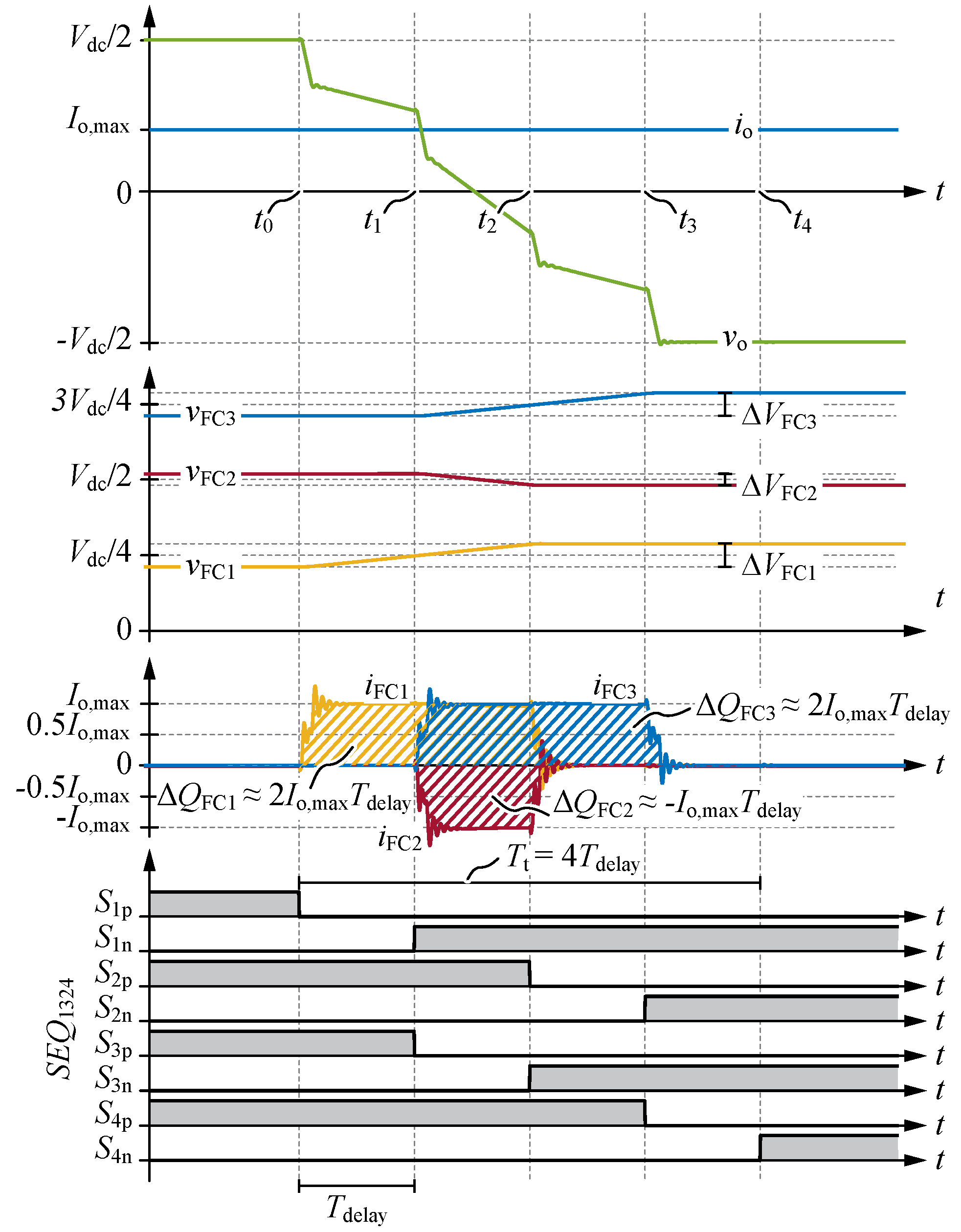

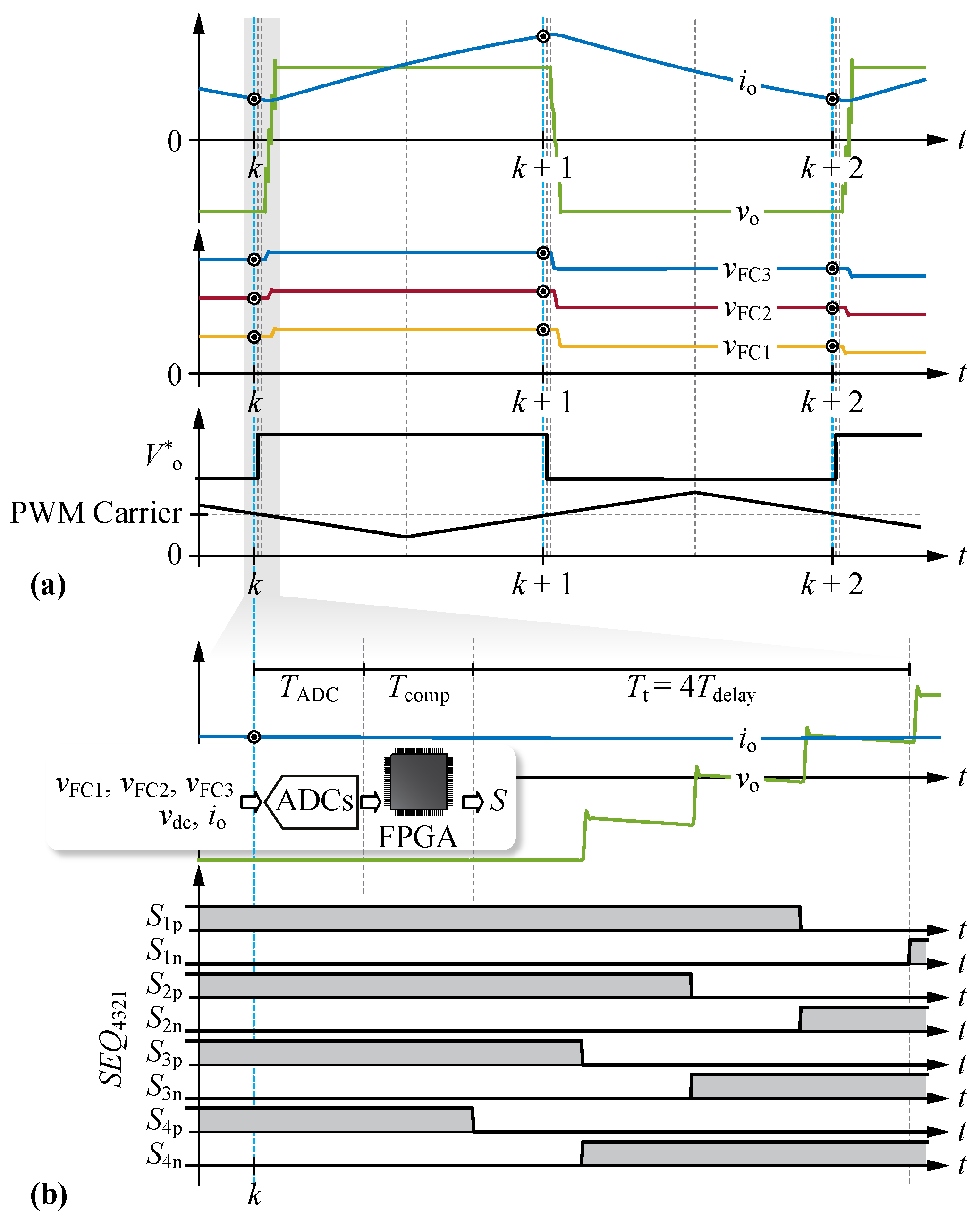

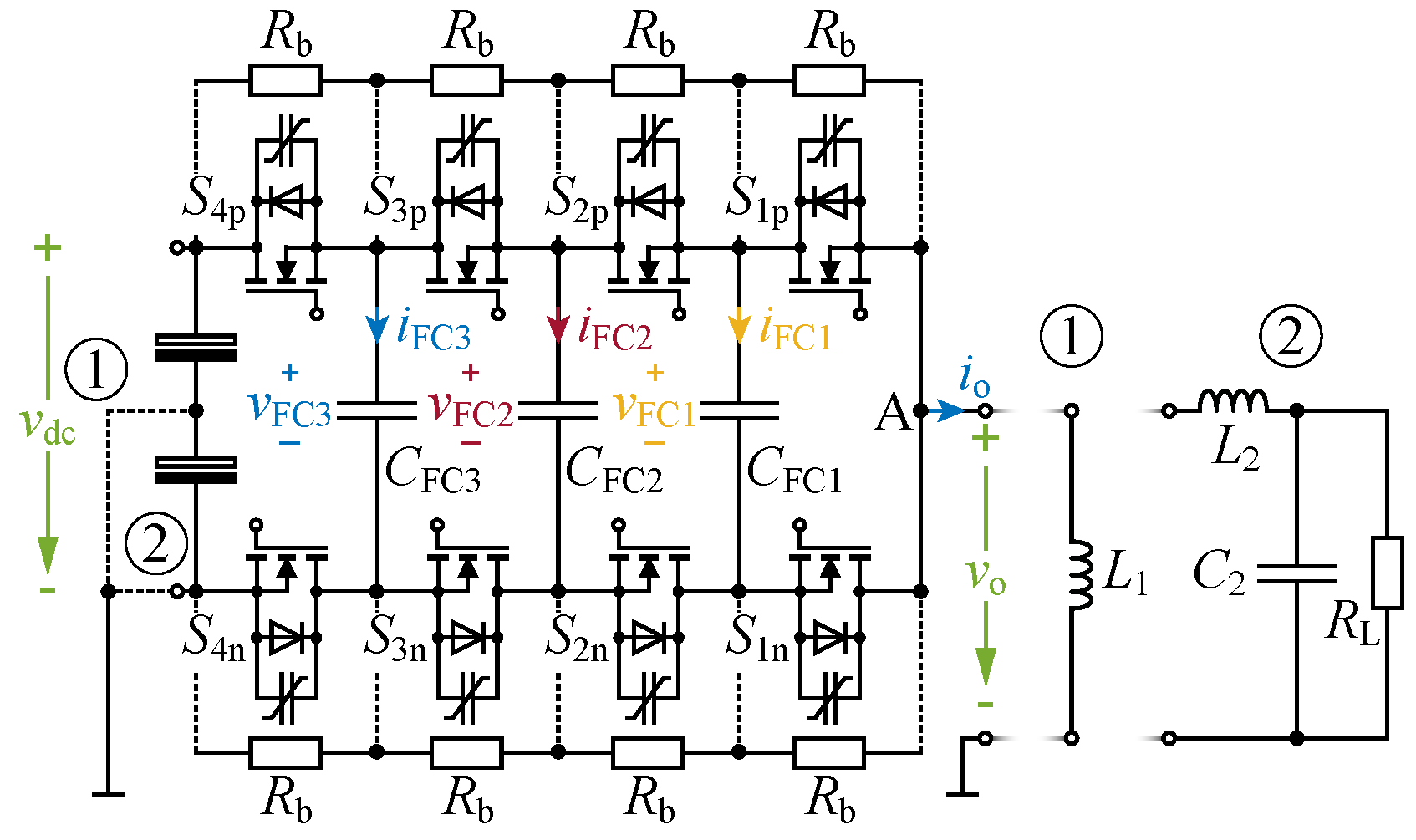

2. Q2L Operation of the 5L-FCC

2.1. Operating Principle with Non-Zero Output Current

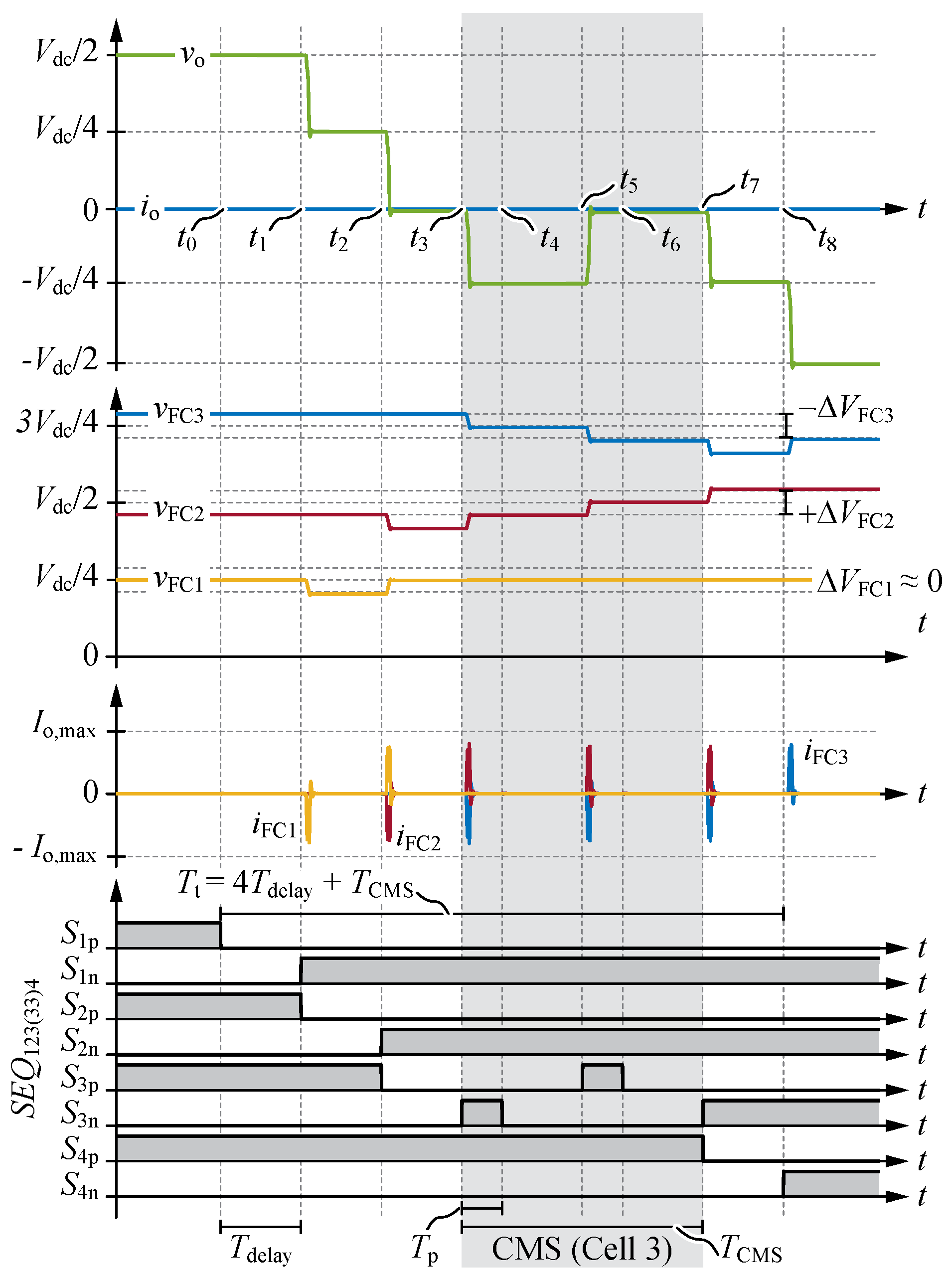

2.2. Operating Principle with Zero Output Current: Cell Multiple Switching

2.3. Duty Cycle Limitation/Selection of

3. Open-Loop FC Balancing

4. Load-Independent Closed-Loop Balancing

4.1. Closed-Loop Control with Non-Zero Output Current

- All delay times in a given switching transition are equal, i.e., .

- Two discrete delay time values are used: , where is intended to be selected by the controller in the steady-state in order to keep the voltage ripple small. On the other hand, is selected in cases of significant unbalance to reduce the error more aggressively.

4.1.1. FC Voltage Tracking

4.1.2. Cell Voltage Tracking

4.2. Closed-Loop Control with Zero Output Current

- The delay times are set to the minimum value as their duration does not impact the balancing when .

- Similarly, the sequence of the switching actions within a Q2L transition does not influence the total voltage increments when . Therefore only the sequence is used for simplicity when CMS is active.

- The pulse time of a CMS event must be sufficiently long for a zero-current HS transition to complete. Therefore, we set .

5. Hardware Implementation

6. Measurement Results

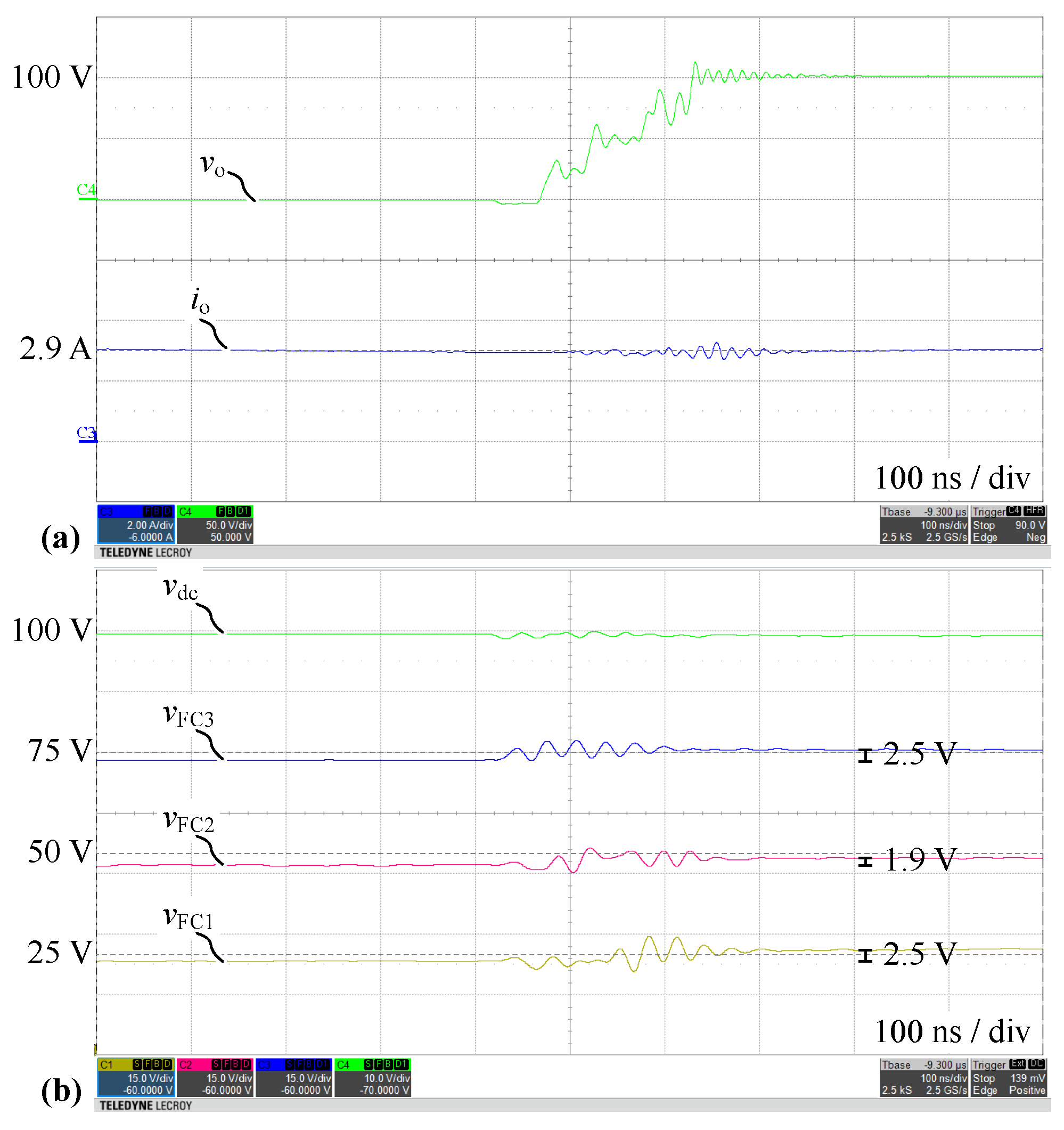

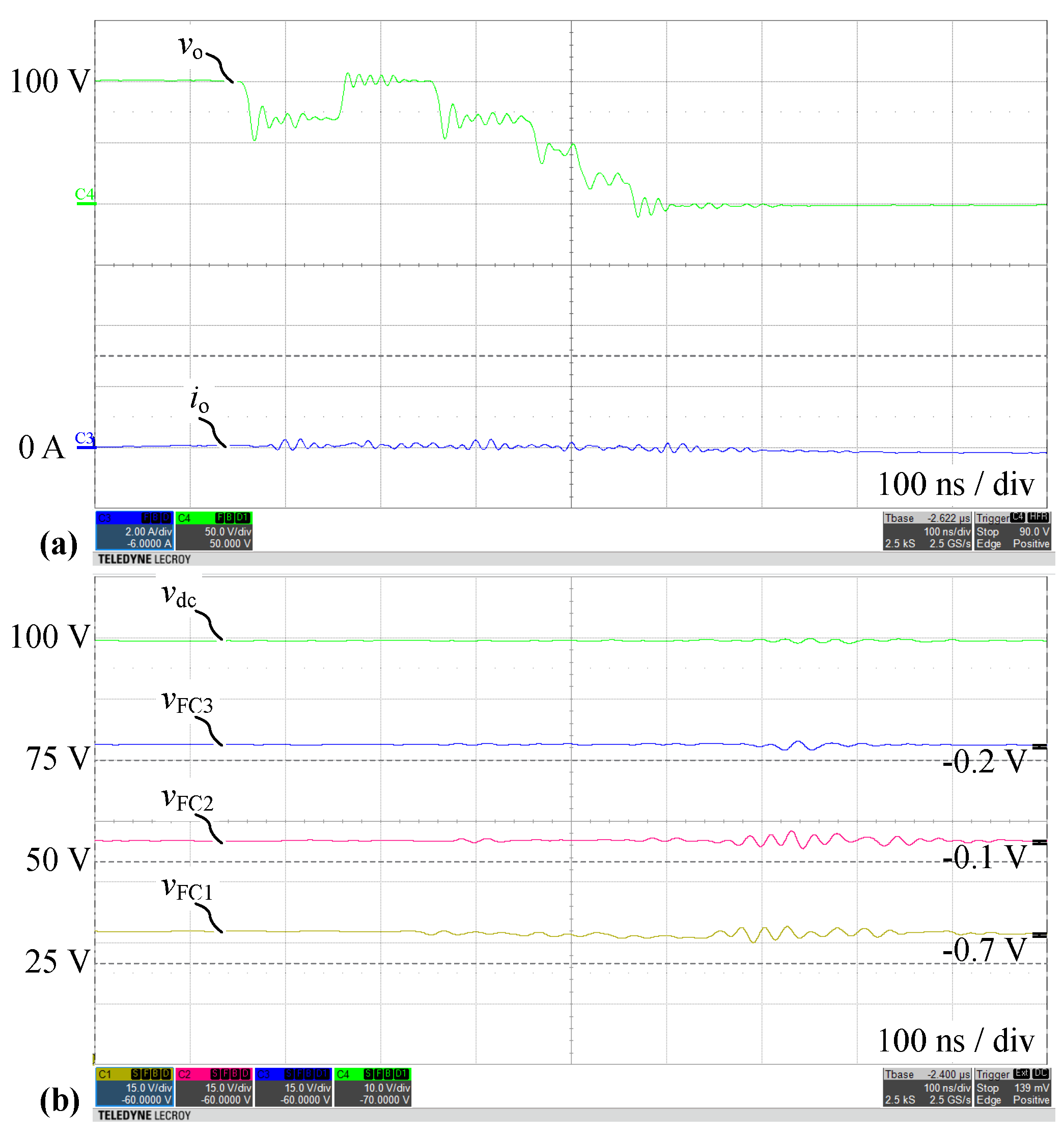

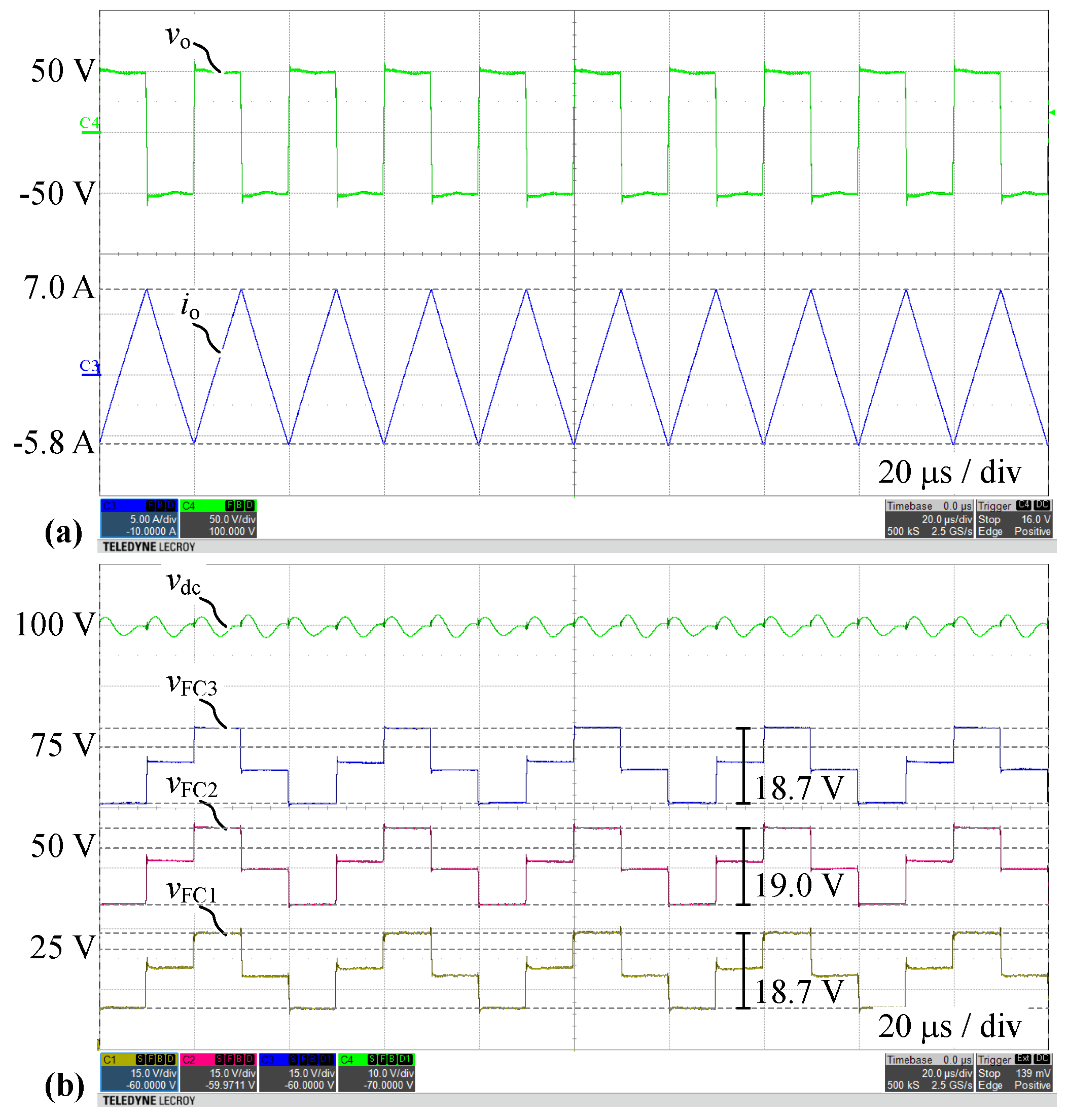

6.1. Q2L Transitions

6.2. Open-Loop Balancing

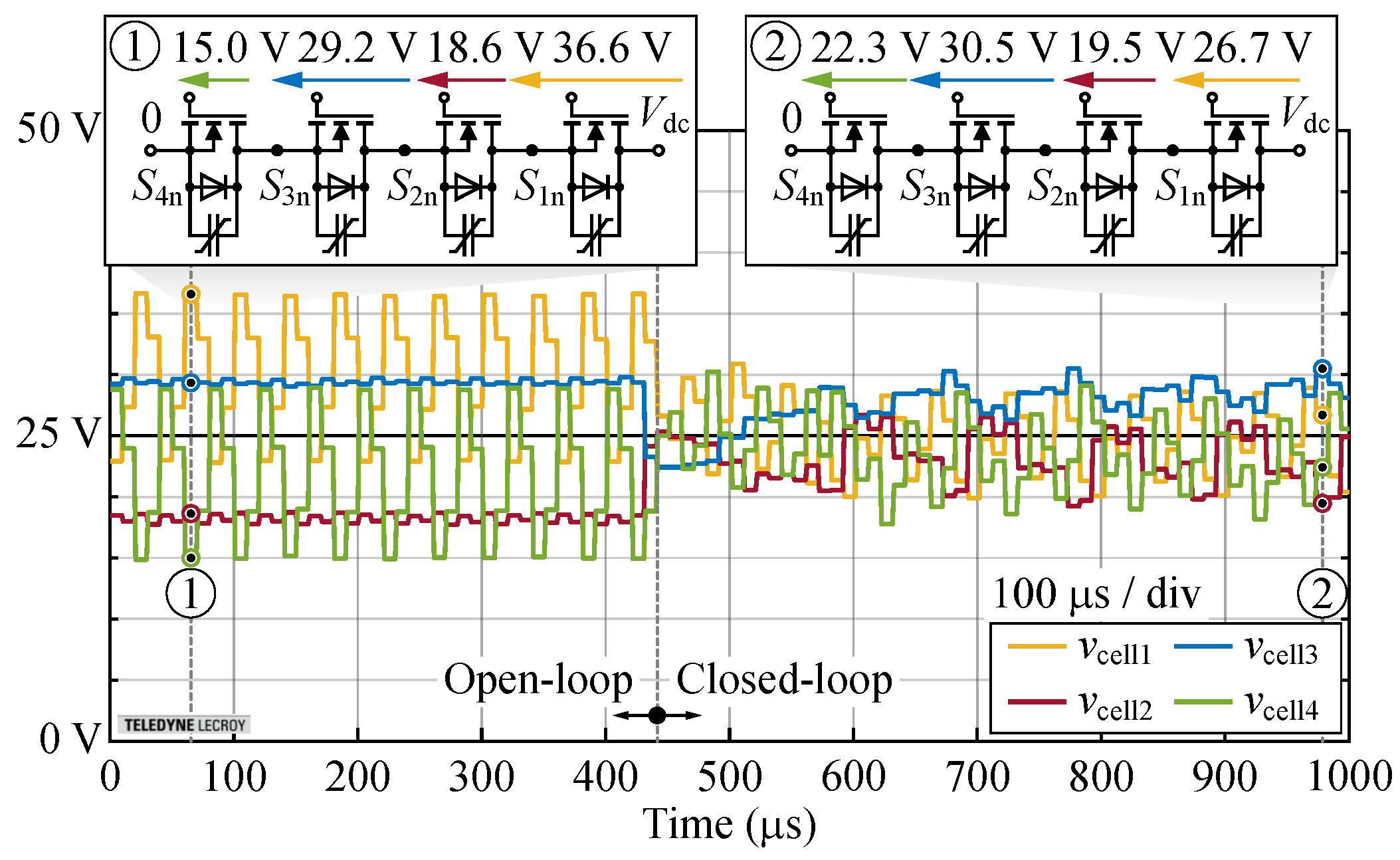

6.3. Closed-Loop Balancing

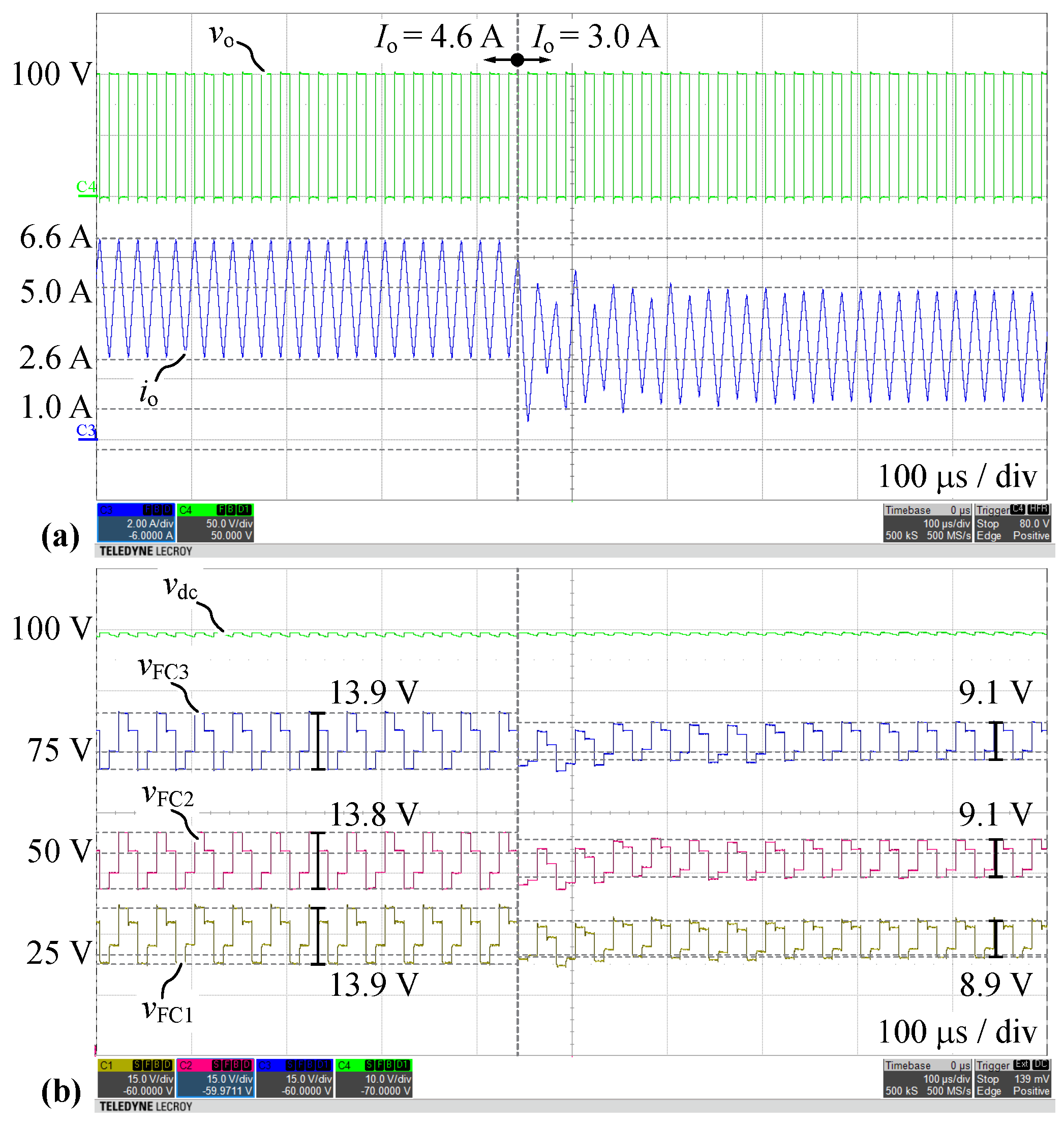

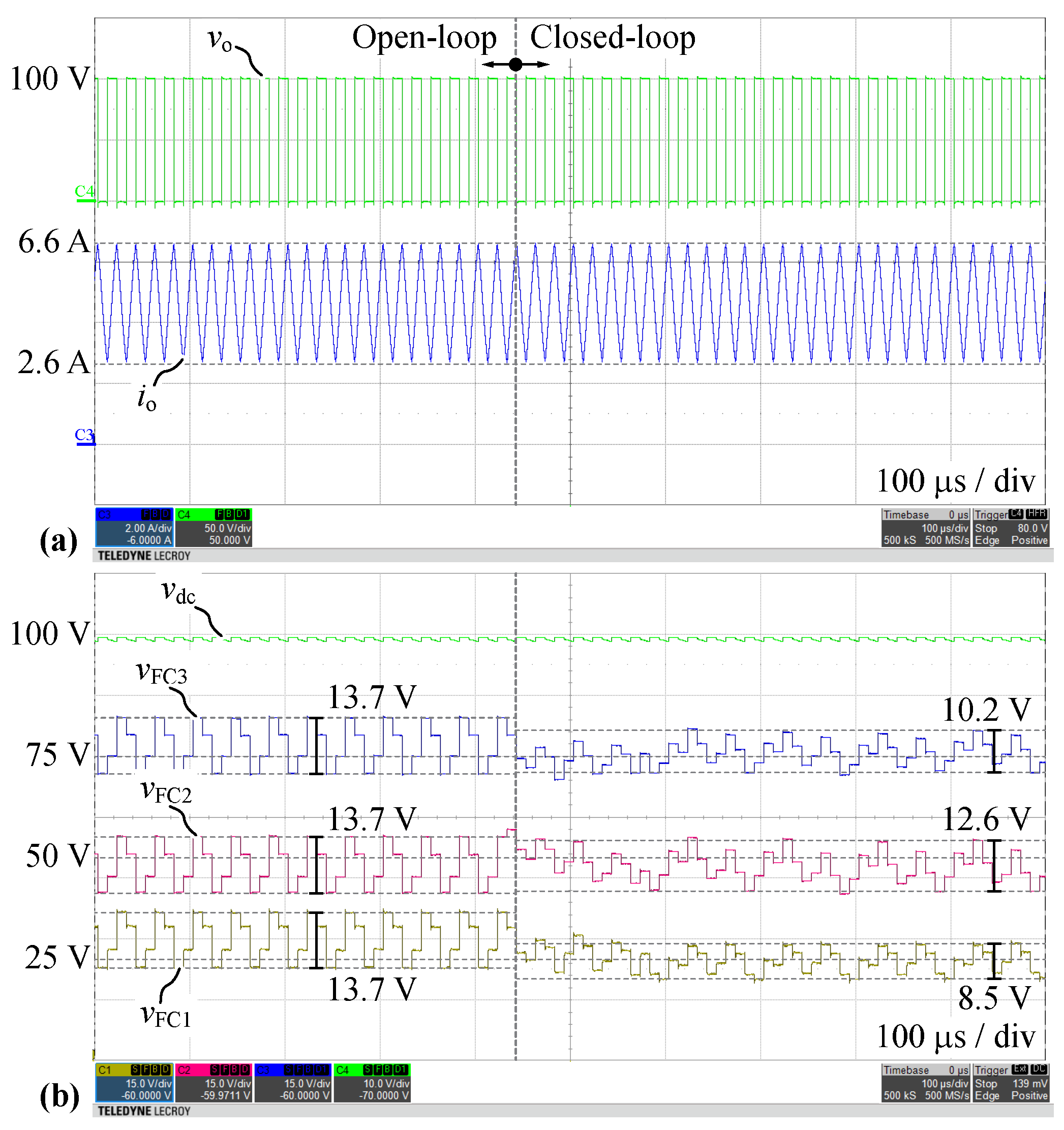

6.3.1. Balancing with Non-Zero Output Current

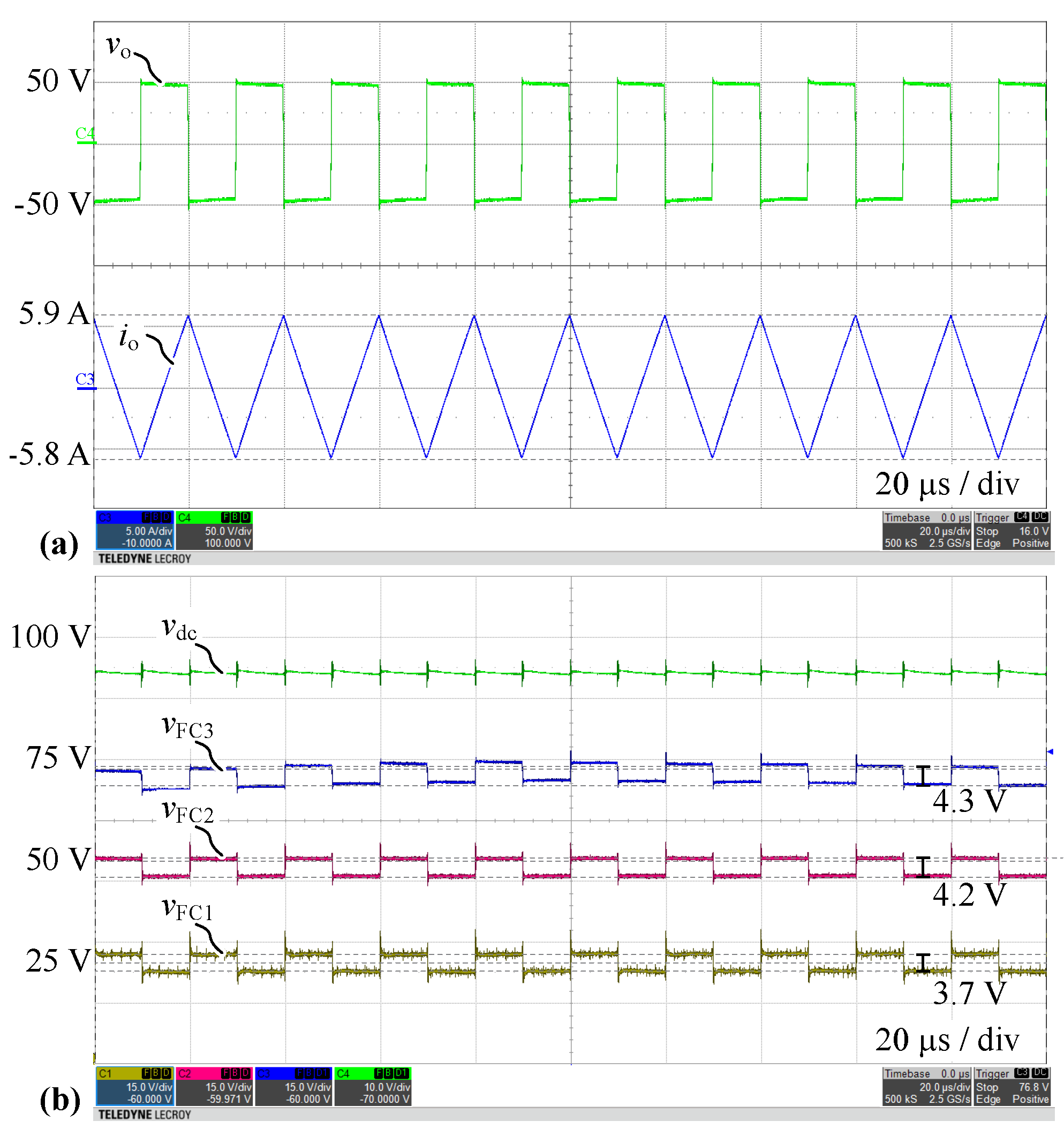

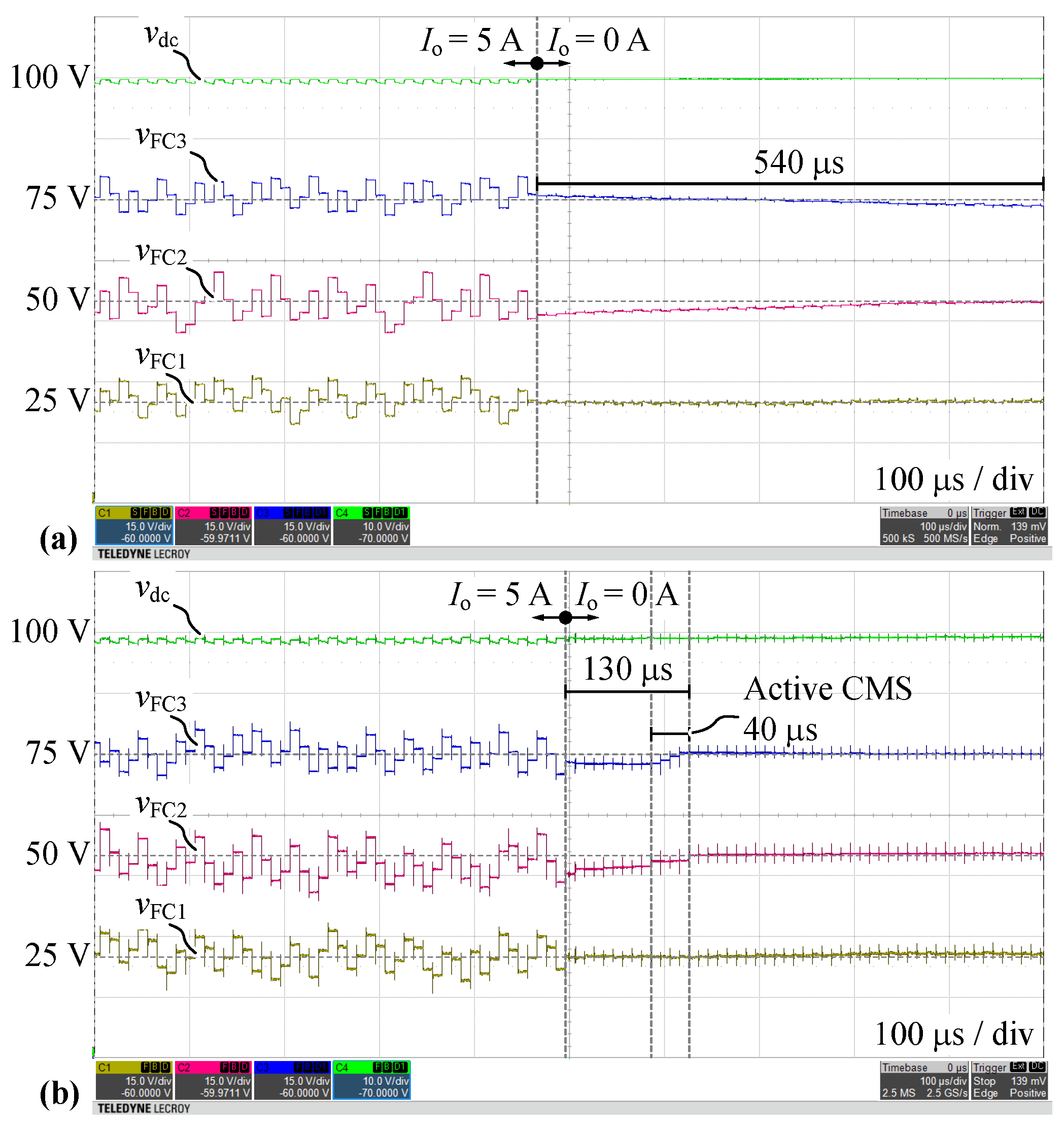

6.3.2. Balancing with Zero Output Current

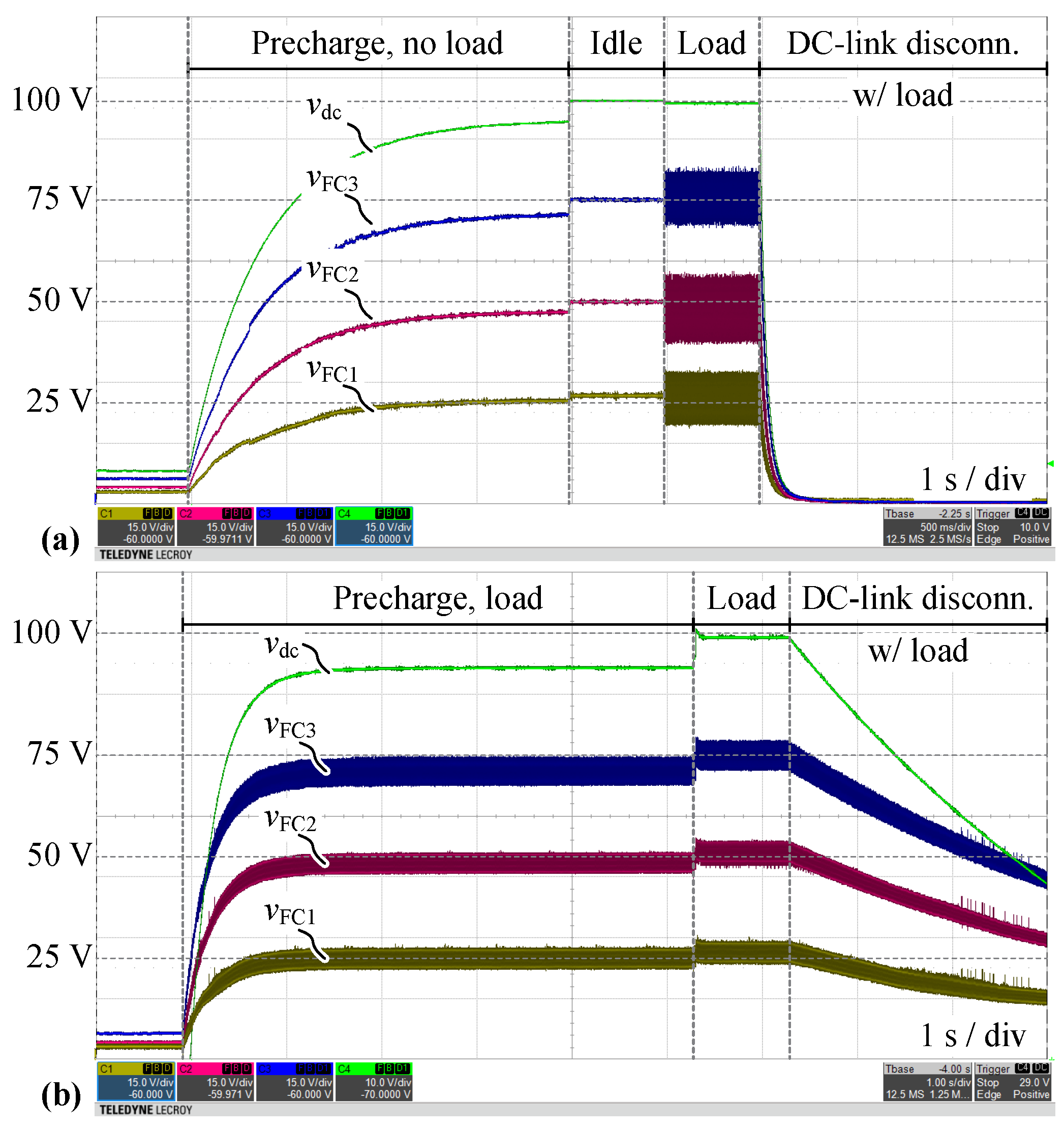

6.4. Start-Up and Shut-Down

7. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| CMS | Cell multiple switching |

| FC | Flying capacitor |

| FCC | Flying capacitor converter |

| HS | Hard-switching |

| MPC | Model predictive control |

| MS | Mixed sequences |

| Q2L | Quasi-2-level |

| ZVS | Zero voltage switching |

| Matrix of ones of dimensions | |

| FC value | |

| Charge equivalent output capacitance | |

| d | Duty cycle |

| Peak-to-peak output current ripple | |

| Voltage increment on the FC | |

| Peak-to-peak voltage ripple | |

| Voltage increment in CMS | |

| Charge increments in FC | |

| Instantaneous FC current | |

| Instantaneous output current | |

| Average output current | |

| Maximum peak output current | |

| j | Number of FCs |

| J | Cost function |

| k | Discrete time step |

| N | Number of FCC voltage levels |

| n | Number of FCC cells () |

| Prediction horizon | |

| Sequence of cell commutations | |

| Transition time | |

| Delay time | |

| Pulse time | |

| CMS time | |

| Switching period | |

| Instantaneous FC voltage | |

| Instantaneous output voltage | |

| DC-link voltage |

Appendix A. CMS for Semiconductors of Various Voltage Classes

), the value of corresponds to approx. half of the maximum increment when operated at (). This can be explained by the higher switch voltage but approx. factor of 2 lower in case of ➁ which indicates that the controllability at would be better for the same absolute value of voltage ripple which is discussed in detail in the following.

), the value of corresponds to approx. half of the maximum increment when operated at (). This can be explained by the higher switch voltage but approx. factor of 2 lower in case of ➁ which indicates that the controllability at would be better for the same absolute value of voltage ripple which is discussed in detail in the following.| Param. | 150 V GaN (EPC2033) | 1.7 kV SiC (C2M0045170P) | 10 kV SiC (QPM3-10000-0300) | ||

|---|---|---|---|---|---|

| ➀ | ➁ | ➂ | ➃ | ||

| DC-link voltage | |||||

| switch voltage | |||||

| charge eq. capacitance | |||||

| max. output current | |||||

| min. output current w/ZVS | |||||

| max. delay time | |||||

| Relative controllability | |||||

| relative CMS controllability | |||||

| 5–20 V | 5–20 V | 57–227 V | 0.33–1.33 kV | peak-to-peak volt. ripple | |

Appendix B. Discussion of Overload and Short-Circuit Operation

References

- Hafez, B.; Krishnamoorthy, H.S.; Enjeti, P.; Ahmed, S.; Pitel, I.J. Medium Voltage Power Distribution Architecture with Medium Frequency Isolation Transformer for Data Centers. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition-APEC 2014, Fort Worth, TX, USA, 16–20 March 2014. [Google Scholar]

- Rothmund, D.; Guillod, T.; Bortis, D.; Kolar, J.W. 99% Efficient 10 kV SiC-Based 7 kV/400 V DC-Transformer for Future Data Centers. IEEE Trans. Emerg. Sel. Top. Power Electron. 2019, 7, 753–767. [Google Scholar] [CrossRef]

- Li, Z.; Hsieh, Y.H.; Li, Q.; Lee, F.C.; Ahmed, M.H. High-Frequency Transformer Design with High-Voltage Insulation for Modular Power Conversion from Medium-Voltage AC to 400-V DC. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), Detroit, MI, USA, 11–15 October 2020. [Google Scholar]

- Zhao, C.; Hsieh, Y.H.; Lee, F.C.; Li, Q. Design and Analysis of a High-Frequency CLLC Resonant Converter with Medium Voltage Insulation for Solid-State-Transformer. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021. [Google Scholar]

- Srdic, S.; Lukic, S. Toward Extreme Fast Charging: Challenges and Opportunities in Directly Connecting to Medium-Voltage Line. IEEE Electrif. Mag. 2019, 7, 22–31. [Google Scholar] [CrossRef]

- Tu, H.; Feng, H.; Srdic, S.; Lukic, S. Extreme Fast Charging of Electric Vehicles: A Technology Overview. IEEE Trans. Transp. Electrif. 2019, 5, 861–878. [Google Scholar] [CrossRef]

- Delta Electronics. High-Efficiency, Medium-Voltage-Input, Solid-State-Transformer-Based 400-kW/1000-V/400-A Extreme Fast Charger for Electric Vehicles. Available online: https://www.energy.gov/ (accessed on 30 August 2021).

- Liang, X.; Srdic, S.; Won, J.; Aponte, E.; Booth, K.; Lukic, S. A 12.47 kV Medium Voltage Input 350 kW EV Fast Charger using 10 kV SiC MOSFET. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019. [Google Scholar]

- Zhao, S.; Li, Q.; Lee, F.C.; Li, B. High-Frequency Transformer Design for Modular Power Conversion from Medium-Voltage AC to 400 VDC. IEEE Trans. Power Electron. 2018, 33, 7545–7557. [Google Scholar] [CrossRef]

- Huber, J.E.; Kolar, J.W. Applicability of Solid-State Transformers in Today’s and Future Distribution Grids. IEEE Trans. Smart Grid 2019, 10, 317–326. [Google Scholar] [CrossRef]

- Cree/Wolfspeed. Medium Voltage SiC R&D Update 2016. Available online: https://www.wolfspeed.com/ (accessed on 30 August 2021).

- She, X.; Huang, A.Q.; Lucia, O.; Ozpineci, B. Review of Silicon Carbide Power Devices and Their Applications. IEEE Trans. Ind. Electron. 2017, 64, 8193–8205. [Google Scholar] [CrossRef]

- Kicin, S.; Burkart, R.; Loisy, J.Y.; Canales, F.; Nawaz, M.; Stampf, G.; Morin, P.; Keller, T. Ultra-Fast Switching 3.3 kV SiC High-Power Module. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe), Nuremberg, Germany, 7–8 July 2020. [Google Scholar]

- ABB Power Grids. Power Semiconductors. Available online: https://library.abb.com/ (accessed on 30 August 2021).

- Mainali, K.; Tripathi, A.; Madhusoodhanan, S.; Kadavelugu, A.; Patel, D.; Hazra, S.; Hatua, K.; Bhattacharya, S. A Transformerless Intelligent Power Substation: A Three-Phase SST Enabled by a 15-kV SiC IGBT. IEEE Power Electron. Mag. 2015, 2, 31–43. [Google Scholar] [CrossRef]

- PowerAmerica. Annual Report: Through Advances in Wide Bandgap Power Electronics. Available online: https://poweramericainstitute.org/ (accessed on 30 August 2021).

- Vechalapu, K.; Negi, A.; Bhattacharya, S. Comparative Performance Evaluation of Series Connected 15 kV SiC IGBT Devices and 15 kV SiC MOSFET Devices for MV Power Conversion Systems. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016. [Google Scholar]

- Rodriguez, J.; Bernet, S.; Wu, B.; Pontt, J.O.; Kouro, S. Multilevel Voltage-Source-Converter Topologies for Industrial Medium-Voltage Drives. IEEE Trans. Ind. Electron. 2007, 54, 2930–2945. [Google Scholar] [CrossRef]

- Biela, J.; Aggeler, D.; Bortis, D.; Kolar, J.W. Balancing Circuit for a 5-kV/50-ns Pulsed-Power Switch Based on SiC-JFET Super Cascode. IEEE Trans. Plasma Sci. 2012, 40, 2554–2560. [Google Scholar] [CrossRef]

- Li, Z.; Bhalla, A. USCi SiC JFET Cascode and Super Cascode Technologies. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Asia), Shanghai, China, 26–28 June 2018. [Google Scholar]

- Gowaid, I.A.; Adam, G.P.; Ahmed, S.; Holliday, D.; Williams, B.W. Analysis and Design of a Modular Multilevel Converter with Trapezoidal Modulation for Medium and High Voltage DC-DC Transformers. IEEE Trans. Power Electron. 2015, 30, 5439–5457. [Google Scholar] [CrossRef] [Green Version]

- Aeloiza, D.; Canales, F.; Burgos, R. Power Converter Having Integrated Capacitor-Blocked Transistor Cells. U.S. Patent 9525348B1, 20 December 2016. [Google Scholar]

- Gowaid, I.A.; Adam, G.P.; Massoud, A.M.; Ahmed, S.; Holliday, D.; Williams, B.W. Quasi Two-Level Operation of Modular Multilevel Converter for Use in a High-Power DC Transformer with DC Fault Isolation Capability. IEEE Trans. Power Electron. 2015, 30, 108–123. [Google Scholar] [CrossRef] [Green Version]

- Milovanovic, S.; Dujic, D. Comprehensive Analysis and Design of a Quasi Two-Level Converter Leg. CPSS Trans. Power Electron. Appl. 2019, 4, 181–196. [Google Scholar] [CrossRef]

- Jiao, D.; Huang, Q.; Huang, A.Q. Evaluation of Medium Voltage SiC Flying Capacitor Converter and Modular Multilevel Converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE USA), Detroit, MI, USA, 11–15 October 2020. [Google Scholar]

- Fazel, S.S.; Bernet, S.; Krug, D.; Jalili, K. Design and Comparison of 4-kV Neutral-Point-Clamped, Flying-Capacitor, and Series-Connected H-Bridge Multilevel Converters. IEEE Trans. Ind. Appl. 2007, 43, 1032–1040. [Google Scholar] [CrossRef]

- Papamanolis, P.; Neumayr, D.; Kolar, J.W. Behavior of the Flying Capacitor Converter under Critical Operating Conditions. In Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE), Edinburgh, UK, 19–21 June 2017. [Google Scholar]

- Schweizer, M.; Soeiro, T.B. Heatsink-Less Quasi 3-Level Flying Capacitor Inverter Based on Low Voltage SMD MOSFETs. In Proceedings of the IEEE European Conference on Power Electronics and Applications (EPE), Warsaw, Poland, 11–14 September 2017. [Google Scholar]

- Czyz, P.; Papamanolis, P.; Guillod, T.; Krismer, F.; Kolar, J.W. New 40kV/300kVA Quasi-2-Level Operated 5-Level Flying Capacitor SiC “Super-Switch” IPM. In Proceedings of the IEEE International Power Electronics Conference (ECCE Asia), Busan, Korea, 27–30 May 2019. [Google Scholar]

- Kucka, J.; Lin, S.; Friebe, J.; Mertens, A. Quasi-Two-Level PWM-Operated Modular Multilevel Converter with Non-Linear Branch Inductors. IEEE Trans. Power Electron. 2019, 36, 7600–7611. [Google Scholar] [CrossRef]

- Gierschner, S.; Hein, Y.; Gierschner, M.; Sajid, A.; Eckel, H.G. Quasi-Two-Level Operation of a Five-Level Flying-Capacitor Converter. In Proceedings of the IEEE European Conference on Power Electronics and Applications (EPE), Genova, Italy, 3–5 September 2019. [Google Scholar]

- Mersche, S.; Bernet, D.; Hiller, M. Quasi-Two-Level Flying-Capacitor-Converter for Medium Voltage Grid Applications. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE USA), Baltimore, MD, USA, 29 September–3 October 2019. [Google Scholar]

- Tcai, A.; Wijekoon, T.; Liserre, M. Evaluation of Flying Capacitor Quasi 2-level Modulation for MV Applications. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management (PCIM Europe), Online, 3–7 May 2021. [Google Scholar]

- Lu, C.; Hu, W.; Wu, H.; Lee, F.C. Quasi-Two-Level Bridgeless PFC Rectifier for Cascaded Unidirectional Solid State Transformer. IEEE Trans. Power Electron. 2021, 36, 12033–12044. [Google Scholar] [CrossRef]

- Fabiani, D.; Montanari, G.C.; Contin, A. Aging Acceleration of Insulating Materials for Electrical Machine Windings Supplied by PWM in the Presence and in the Absence of Partial Discharges. In Proceedings of the IEEE Conference on Solid Dielectrics (ICSD), Eindhoven, The Netherlands, 25–29 June 2001. [Google Scholar]

- Wang, P.; Montanari, G.C.; Cavallini, A. Partial Discharge Phenomenology and Induced Aging Behavior in Rotating Machines Controlled by Power Electronics. IEEE Trans. Ind. Electron. 2014, 61, 7105–7112. [Google Scholar] [CrossRef]

- Guillod, T.; Faerber, R.; Rothmund, D.; Krismer, F.; Franck, C.M.; Kolar, J.W. Dielectric Losses in Dry-Type Insulation of Medium-Voltage Power Electronic Converters. IEEE Trans. Emerg. Sel. Top. Power Electron. 2020, 8, 2716–2732. [Google Scholar] [CrossRef] [Green Version]

- Hu, A.; Biela, J. Evaluation of the Imax-fsw-dv/dt Trade-off of High Voltage SiC MOSFETs Based on an Analytical Switching Loss Model. In Proceedings of the IEEE European Conference on Power Electronics and Applications (EPE), Lyon, France, 7–11 September 2020. [Google Scholar]

- Wilkinson, R.H.; Meynard, T.A.; du Toit Mouton, H. Natural Balance of Multicell Converters: The General Case. IEEE Trans. Power Electron. 2006, 21, 1658–1666. [Google Scholar] [CrossRef]

- Czyz, P.; Papamanolis, P.; Lazarevic, V.; Guillod, T.; Krismer, F.; Kolar, J.W. Voltage Source Converter Configured to Transition Between at Least Two Voltage Levels. Patent SE 2051394-1, 11 February 2020. [Google Scholar]

- Geyer, T. Model Predictive Control of High Power Converters and Industrial Drives; John Wiley & Sons: Hoboken, NJ, USA, 2017. [Google Scholar]

- Antoniewicz, K.; Jasinski, M.; Kazmierkowski, M.P.; Malinowski, M. Model Predictive Control for Three-Level Four-Leg Flying Capacitor Converter Operating as Shunt Active Power Filter. IEEE Trans. Ind. Electron. 2016, 63, 5255–5262. [Google Scholar]

- Acuna, J.; Walter, J.; Kallfass, I. Very Fast Short Circuit Protection for Gallium-Nitride Power Transistors Based on Printed Circuit Board Integrated Current Sensor. In Proceedings of the IEEE European Conference on Power Electronics and Applications (EPE), Riga, Latvia, 17–21 September 2018. [Google Scholar]

- Rothmund, D.; Bortis, D.; Kolar, J.W. Highly Compact Isolated Gate Driver with Ultrafast Overcurrent Protection for 10 kV SiC MOSFETs. CPSS Trans. Power Electron. Appl. 2018, 3, 278–291. [Google Scholar] [CrossRef]

| FC1 | FC2 | FC3 | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Sequence | |||||||||||||

| +1 | 0 | 0 | 0 | 0 | +1 | 0 | 0 | 0 | 0 | +1 | 0 | ||

| +1 | 0 | 0 | 0 | 0 | +1 | 0 | +1 | 0 | 0 | 0 | −1 | ||

| +1 | 0 | +1 | 0 | 0 | 0 | −1 | 0 | 0 | +1 | +1 | 0 | ||

| +1 | 0 | +1 | +1 | 0 | 0 | −1 | −1 | 0 | 0 | +1 | 0 | ||

| +1 | 0 | 0 | +1 | 0 | +1 | 0 | 0 | 0 | −1 | 0 | −1 | ||

| +1 | 0 | +1 | +1 | 0 | 0 | −1 | 0 | 0 | 0 | 0 | −1 | ||

| 0 | −1 | 0 | 0 | +1 | +1 | 0 | 0 | 0 | 0 | +1 | 0 | ||

| 0 | −1 | 0 | 0 | +1 | +1 | 0 | +1 | 0 | 0 | 0 | −1 | ||

| 0 | −1 | −1 | 0 | 0 | +1 | 0 | 0 | +1 | 0 | +1 | 0 | ||

| 0 | −1 | −1 | −1 | 0 | +1 | 0 | 0 | 0 | 0 | +1 | 0 | ||

| 0 | −1 | 0 | −1 | +1 | +1 | 0 | +1 | −1 | 0 | 0 | −1 | ||

| 0 | −1 | −1 | −1 | 0 | +1 | 0 | +1 | 0 | 0 | 0 | −1 | ||

| Sequence | |||||||||||||

| FC3 | FC2 | FC1 |  | ||||||||||

| CMS Events | CMS seq. | |||

|---|---|---|---|---|

| 0001 | 0 | 0 | +1 | |

| 0010 | 0 | +1 | −1 | |

| 0100 | +1 | −1 | 0 | |

| 1000 | −1 | 0 | 0 | |

| 0011 | 0 | +1 | 0 | |

| 1100 | 0 | −1 | 0 |

| 100 V | DC-link voltage | |

| 6.6 A | output current maximum | |

| 50 kHz | switching frequency | |

| d | 50% | duty cycle |

| Flying capacitors | ||

| 66 nF | CAA572C0G3A663J640LH | |

| 20 V | max. peak-to-peak volt. ripple | |

| Semiconductors | ||

| S | 150 V/7 m | GaN eFET EPC2033 |

| 760 pF | charge eq. capacitance | |

| Control parameters | ||

| 400 ns | max. transition time | |

| 50 ns | min. delay time | |

| 100 ns | max. delay time | |

| 50 ns | pulse time | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Czyz, P.; Papamanolis, P.; Trunas Bruguera, F.; Guillod, T.; Krismer, F.; Lazarevic, V.; Huber, J.; Kolar, J.W. Load-Independent Voltage Balancing of Multi-Level Flying Capacitor Converters in Quasi-2-Level Operation. Electronics 2021, 10, 2414. https://doi.org/10.3390/electronics10192414

Czyz P, Papamanolis P, Trunas Bruguera F, Guillod T, Krismer F, Lazarevic V, Huber J, Kolar JW. Load-Independent Voltage Balancing of Multi-Level Flying Capacitor Converters in Quasi-2-Level Operation. Electronics. 2021; 10(19):2414. https://doi.org/10.3390/electronics10192414

Chicago/Turabian StyleCzyz, Piotr, Panteleimon Papamanolis, Francesc Trunas Bruguera, Thomas Guillod, Florian Krismer, Vladan Lazarevic, Jonas Huber, and Johann W. Kolar. 2021. "Load-Independent Voltage Balancing of Multi-Level Flying Capacitor Converters in Quasi-2-Level Operation" Electronics 10, no. 19: 2414. https://doi.org/10.3390/electronics10192414

APA StyleCzyz, P., Papamanolis, P., Trunas Bruguera, F., Guillod, T., Krismer, F., Lazarevic, V., Huber, J., & Kolar, J. W. (2021). Load-Independent Voltage Balancing of Multi-Level Flying Capacitor Converters in Quasi-2-Level Operation. Electronics, 10(19), 2414. https://doi.org/10.3390/electronics10192414