An 87% Power-Efficiency Hybrid of Voltage- and Current-Mode Line Driver with an Adaptive Amplitude Tuning

Abstract

:1. Introduction

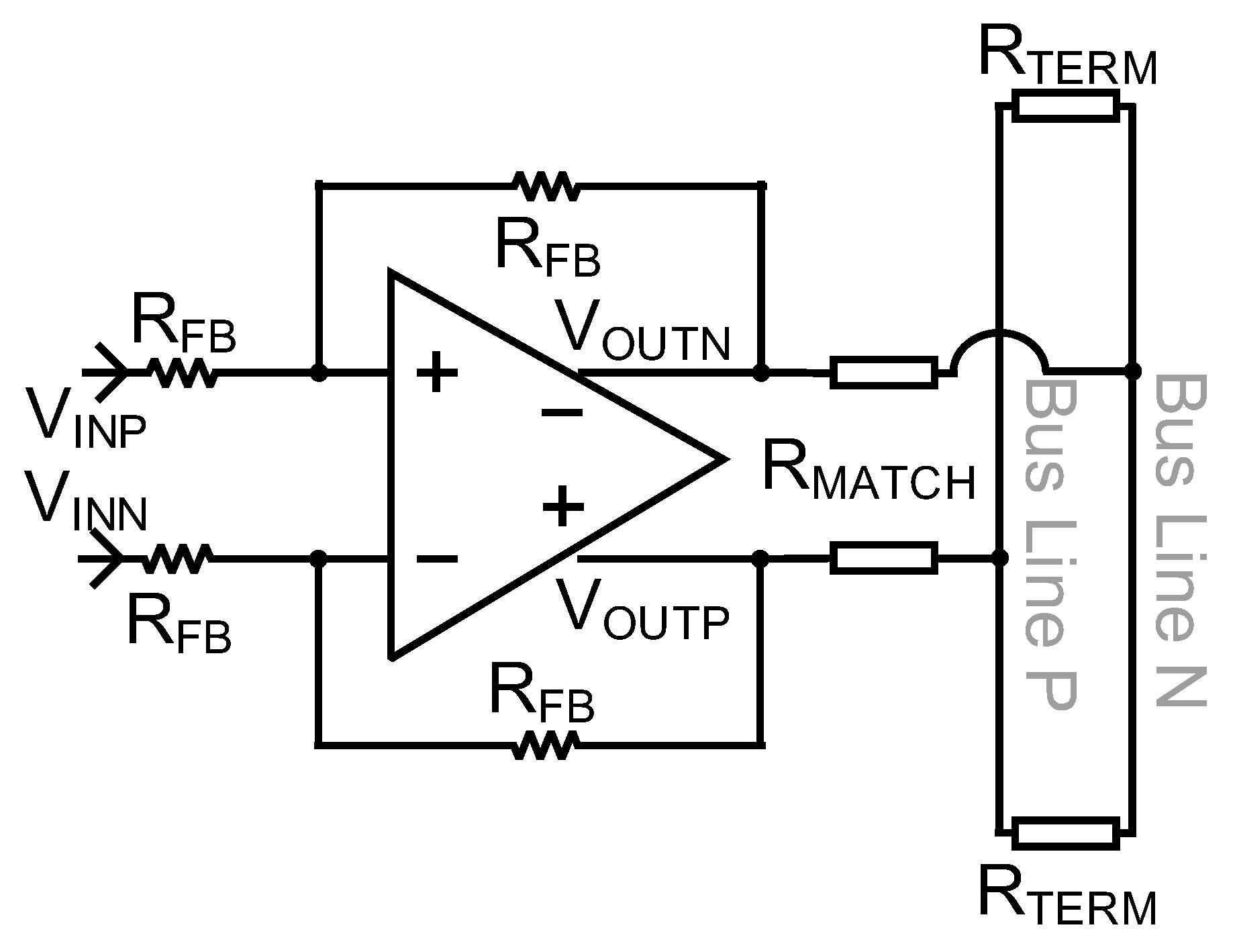

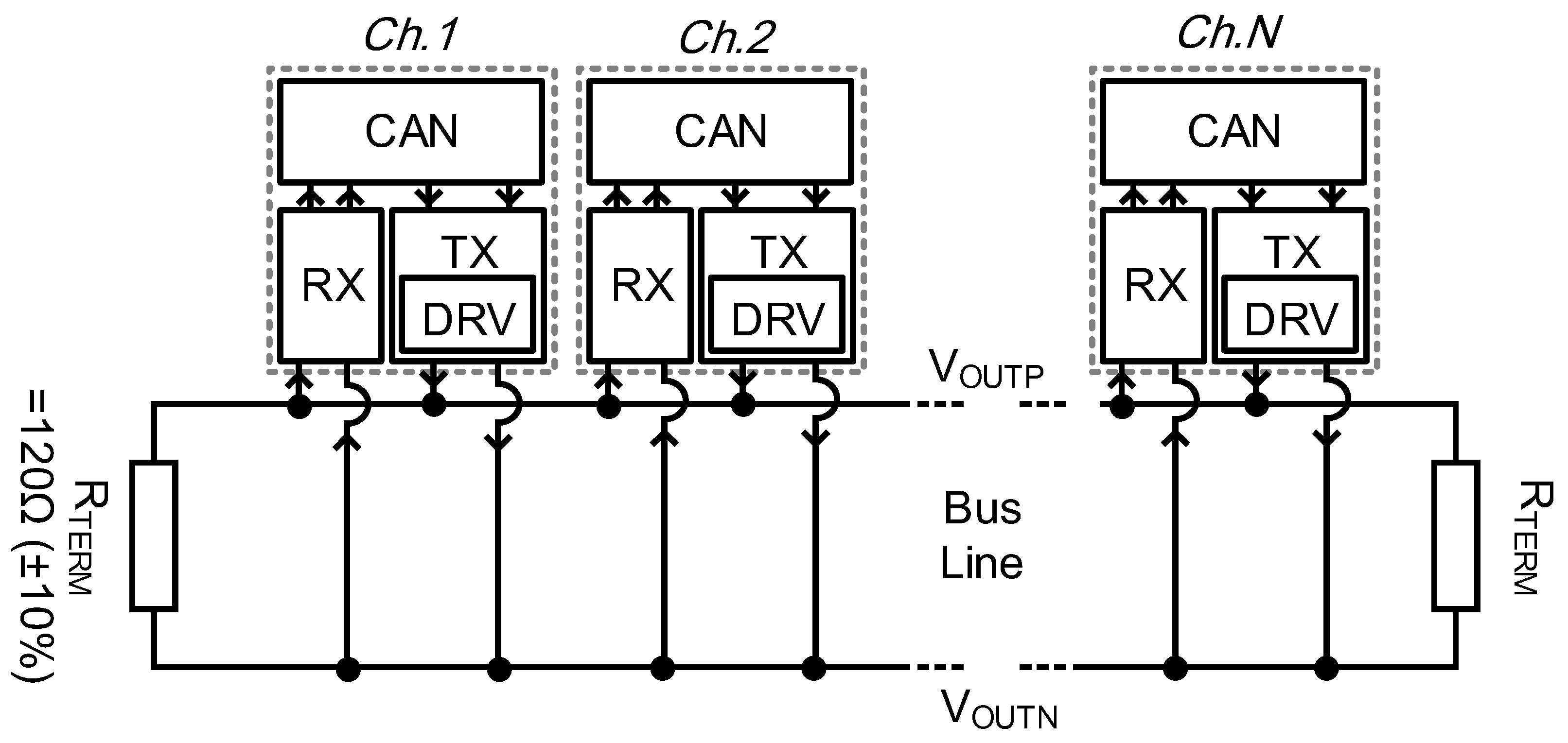

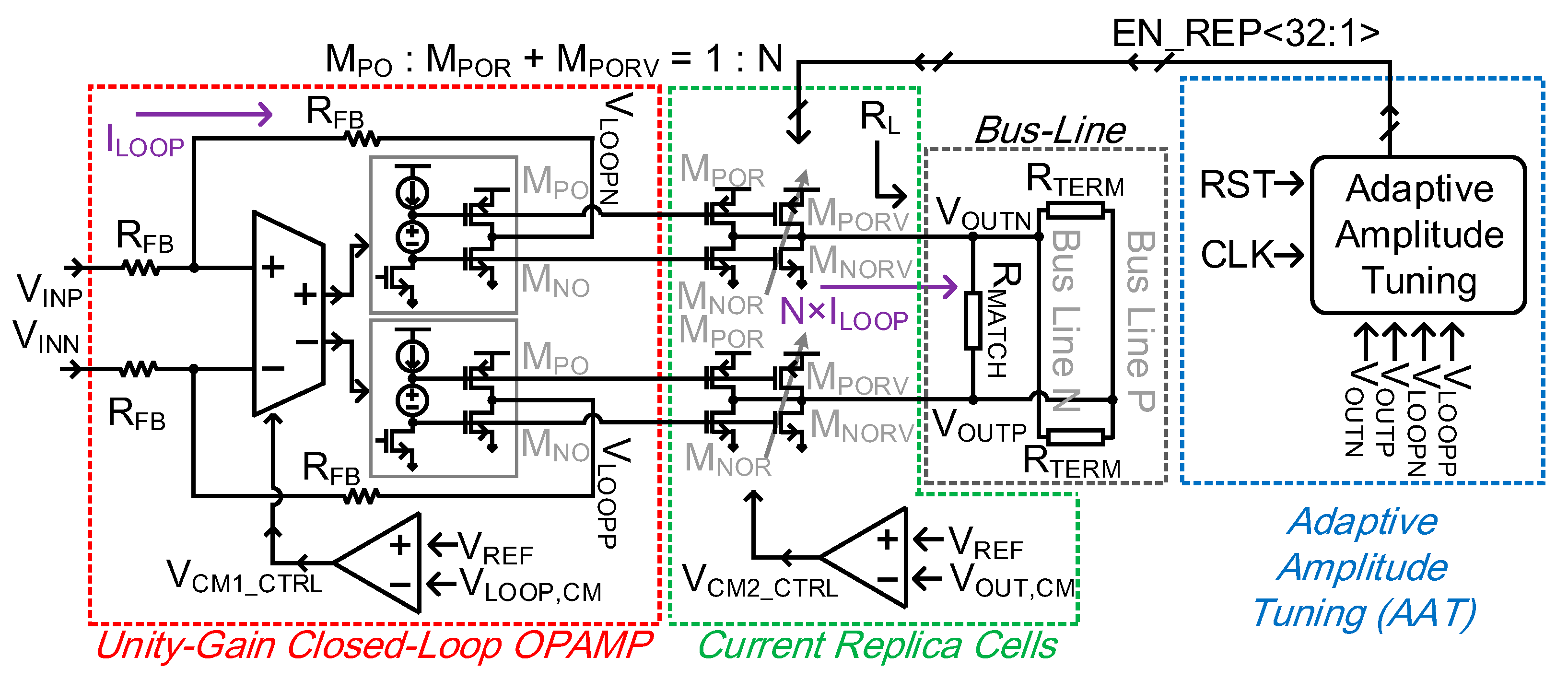

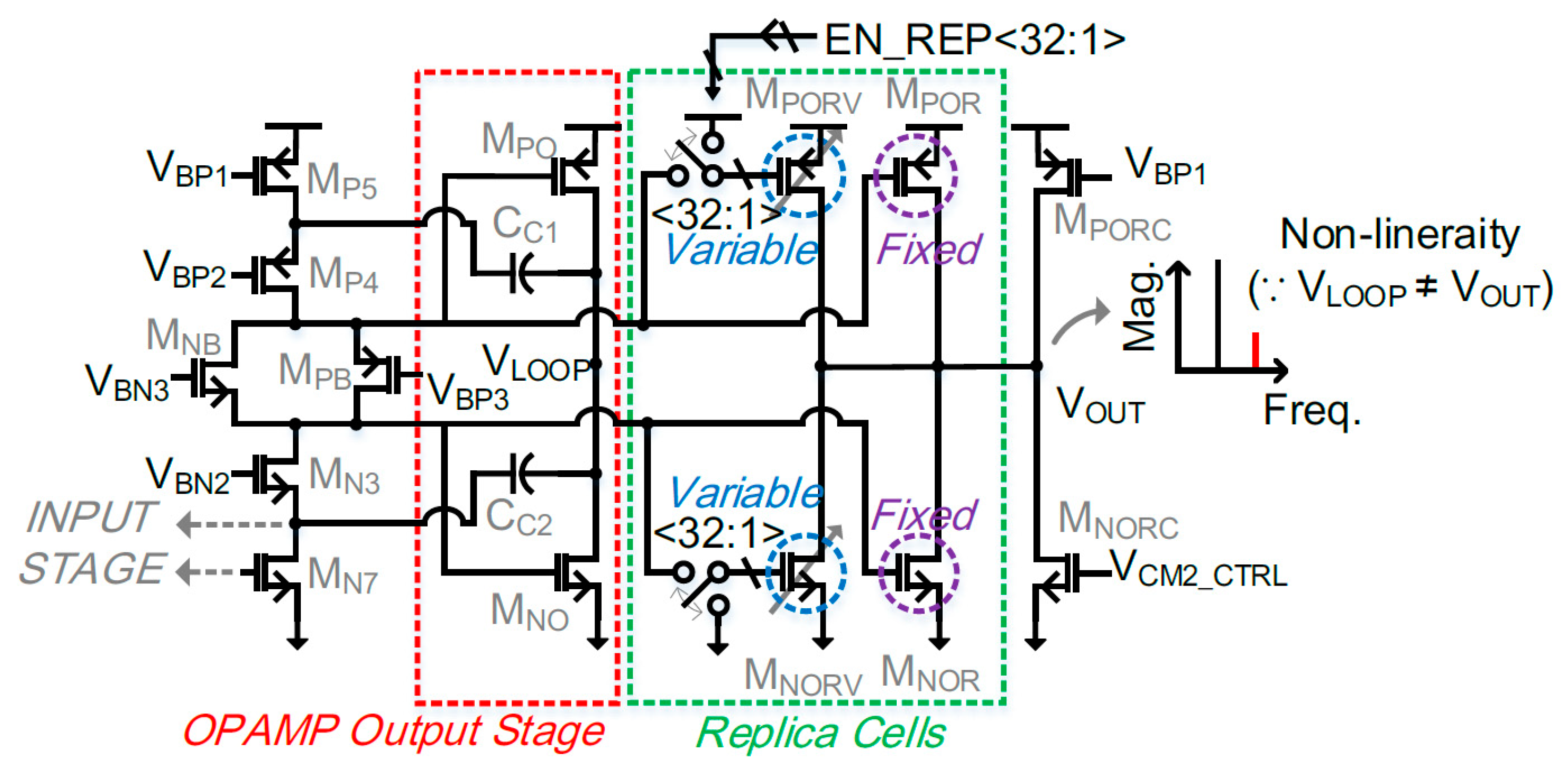

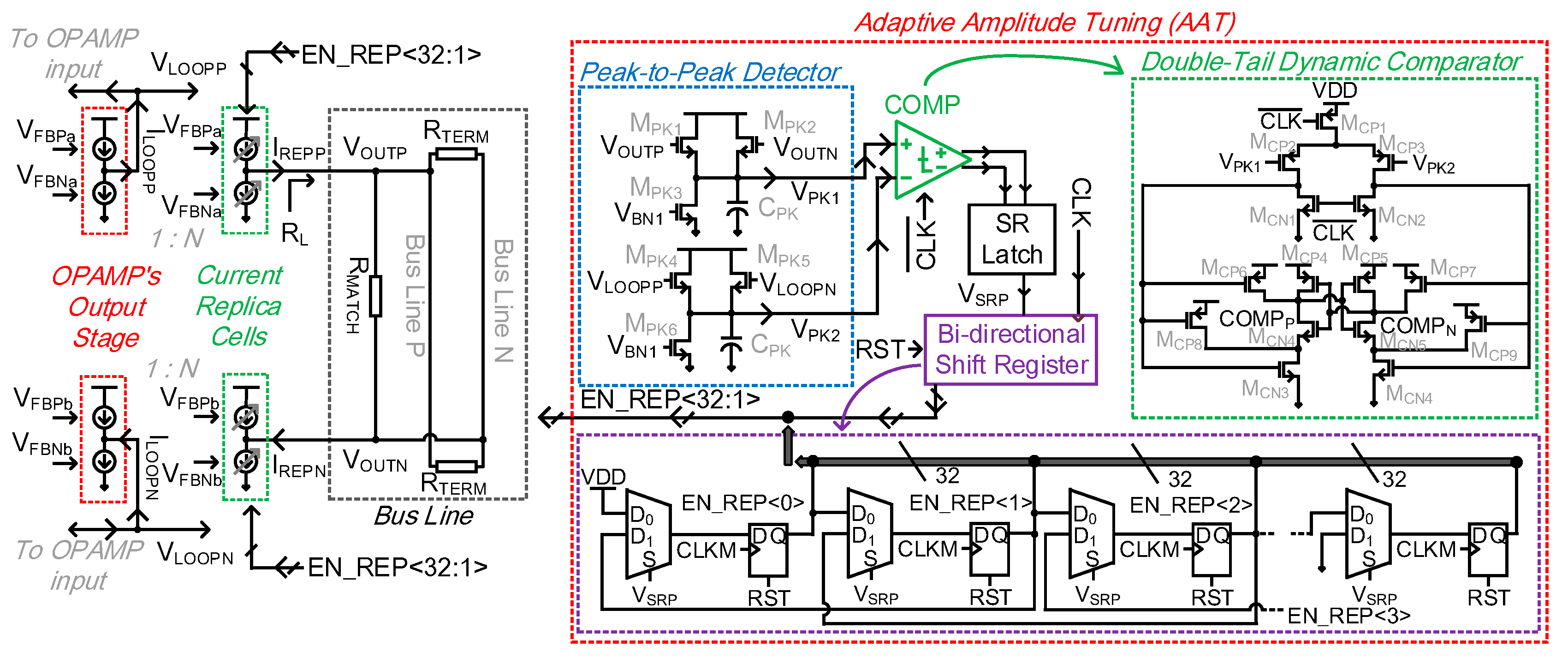

2. Proposed Hybrid of Voltage- and Current-Mode Line Driver

2.1. Architecture of the Hybrid of a Voltage- and a Current-Mode Line Driver

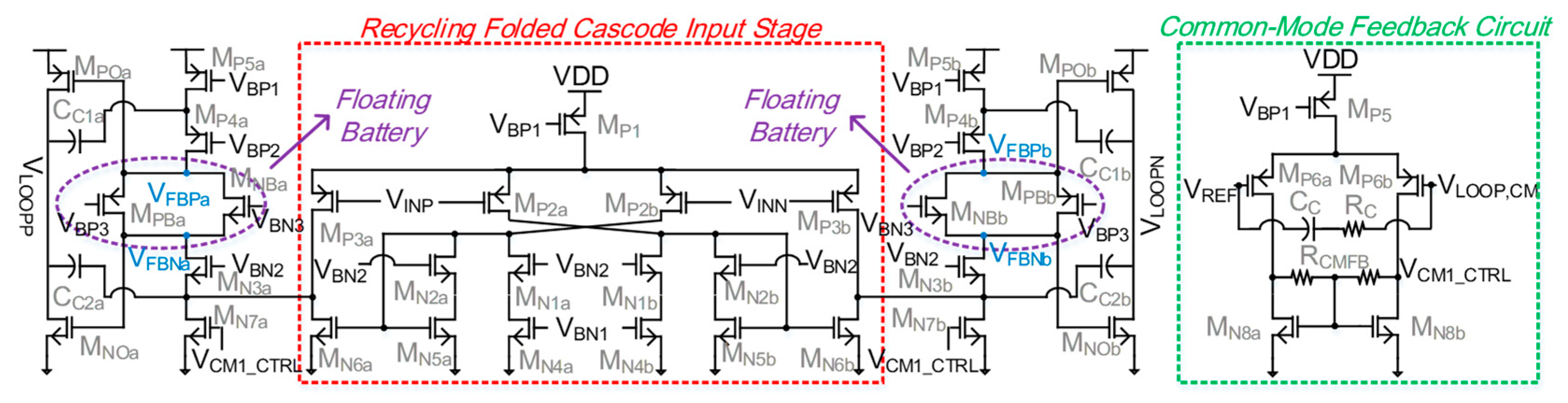

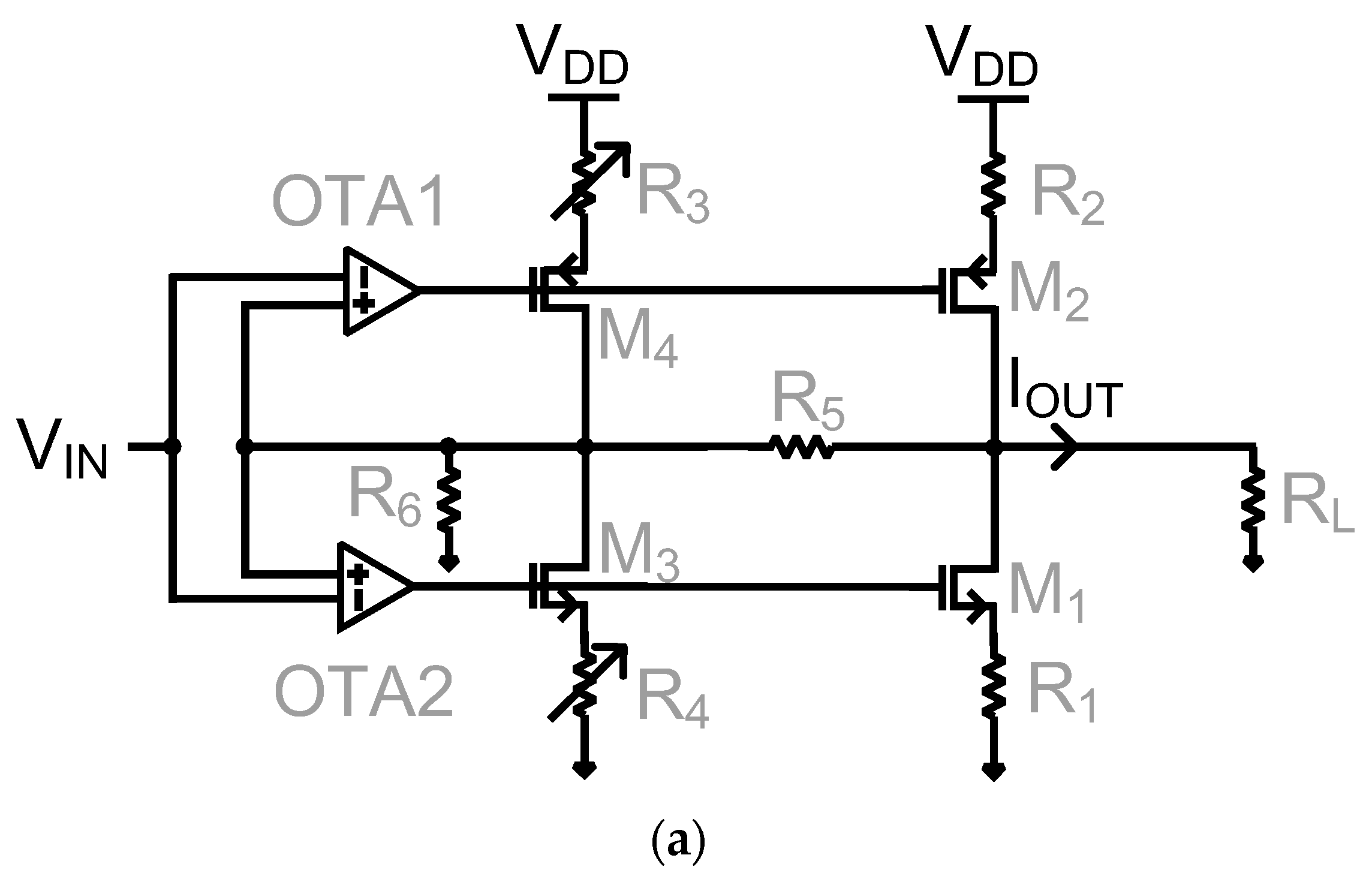

2.2. Architecture of the Operational Amplifier

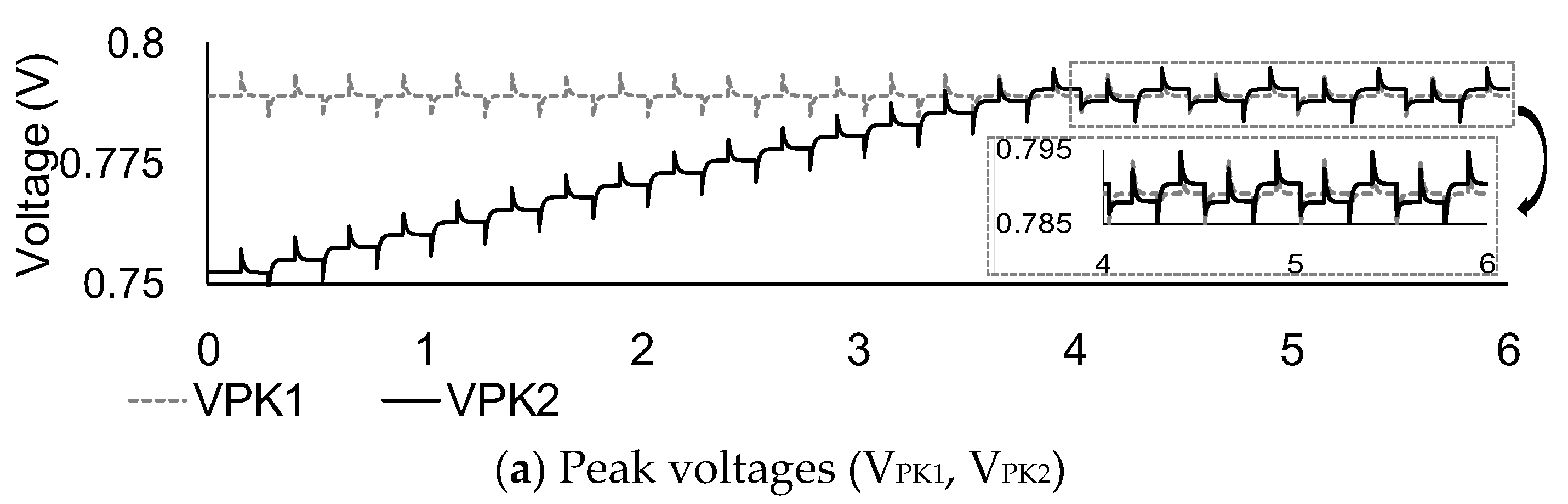

3. Adaptive Amplitude Tuning for Load Impedance Variations

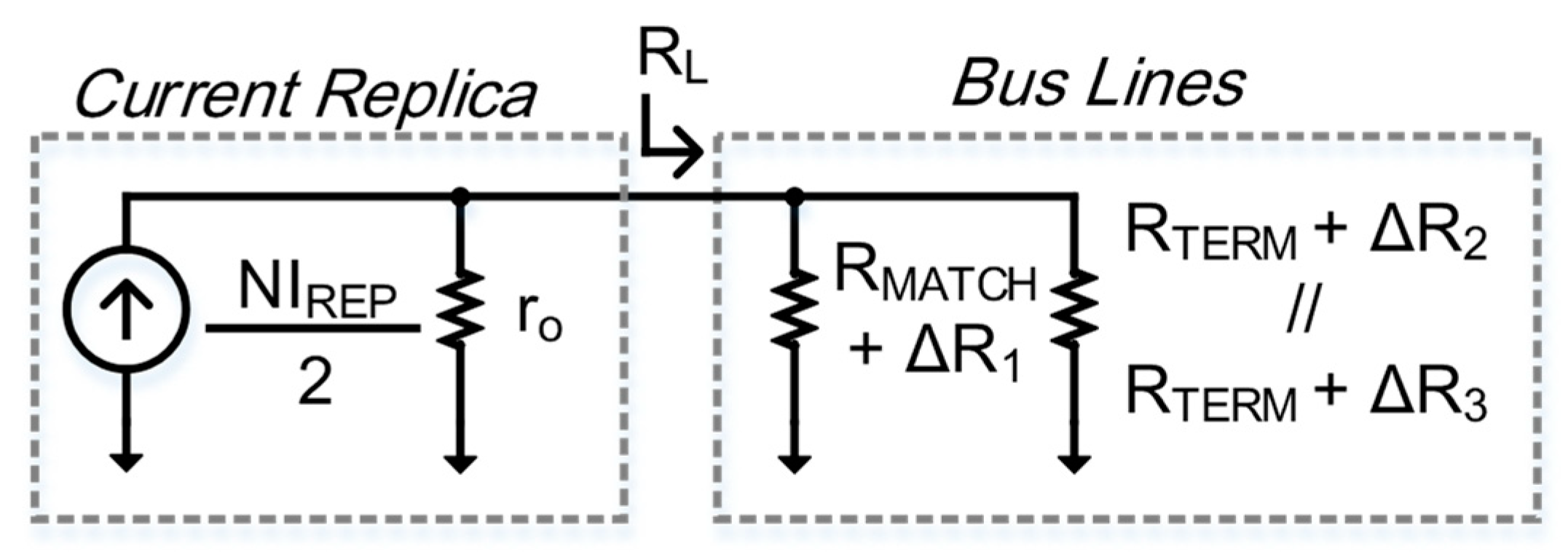

3.1. Effect of Load Impedance Variations on the Line Driver’s Performances

3.2. Conventional Signal Linearity Enhancement and Signal Gain Control Techniques

3.3. Proposed Signal Linearity Enhancement and Signal Gain Control Technique

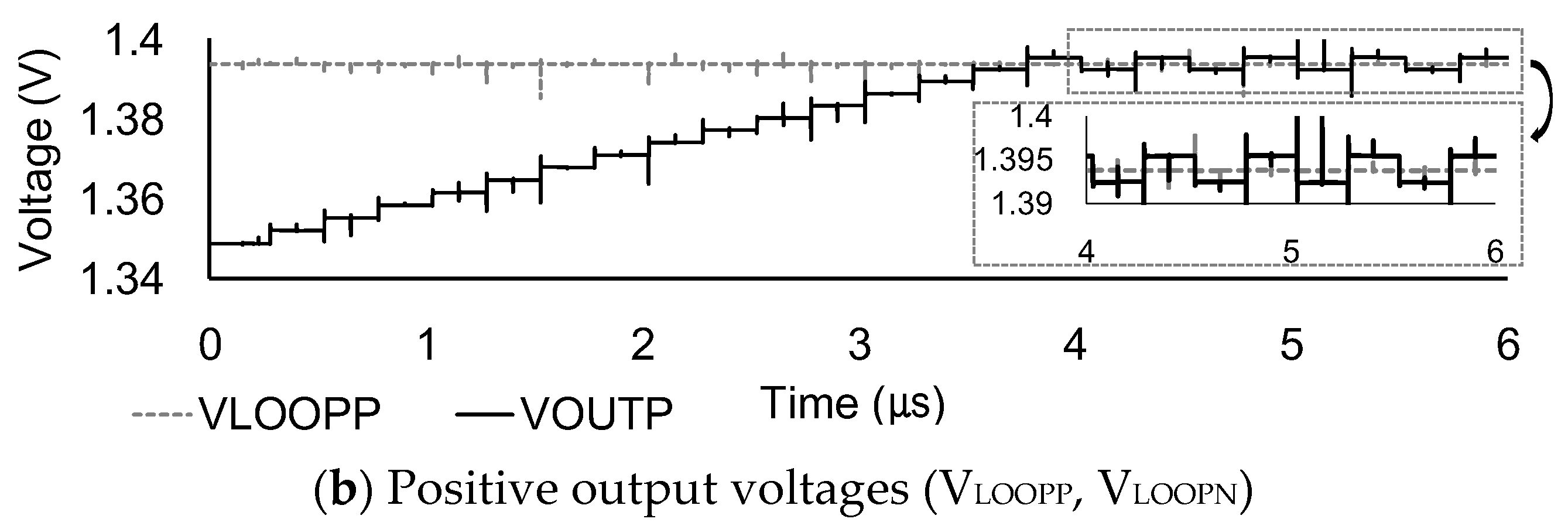

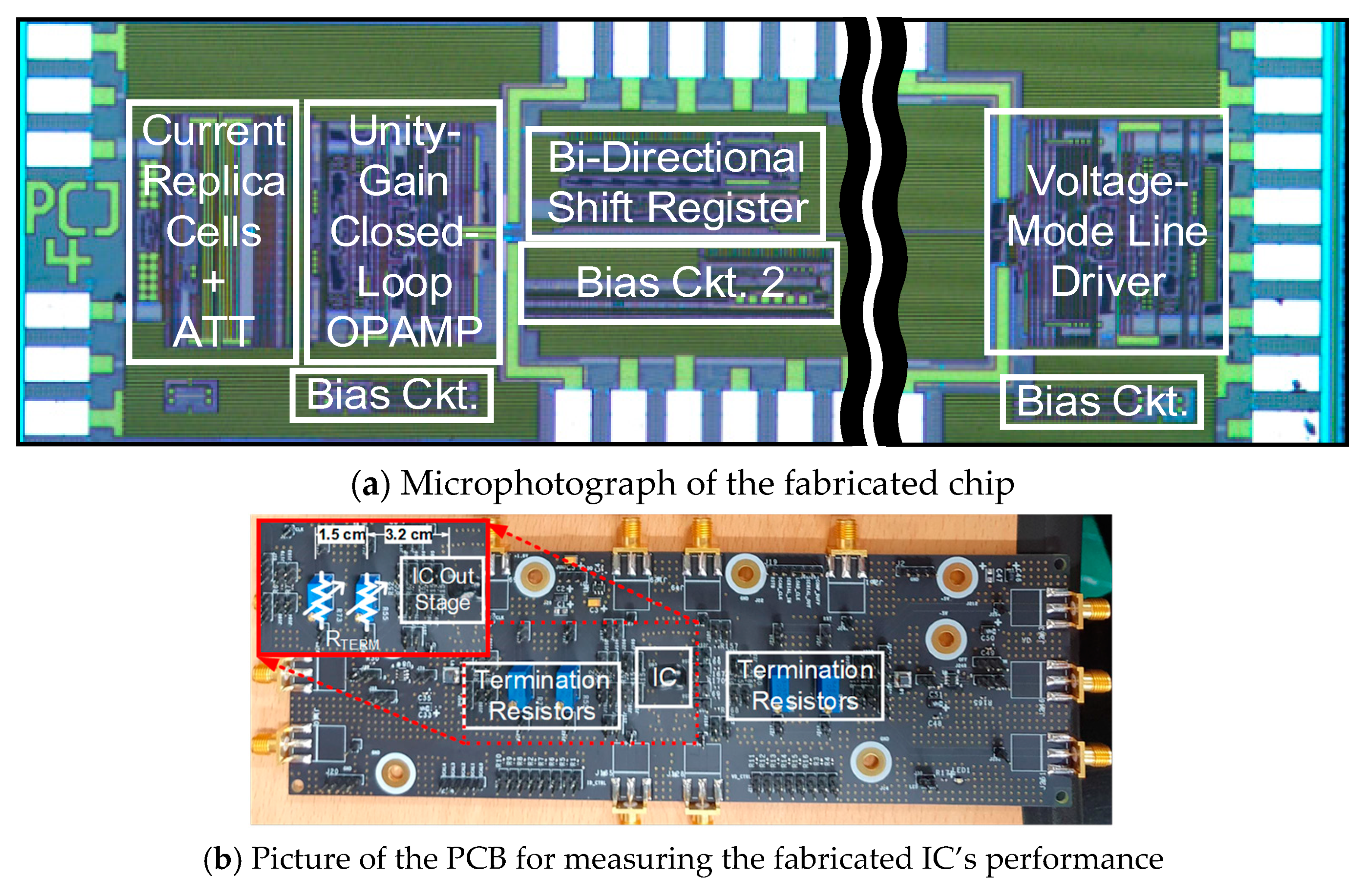

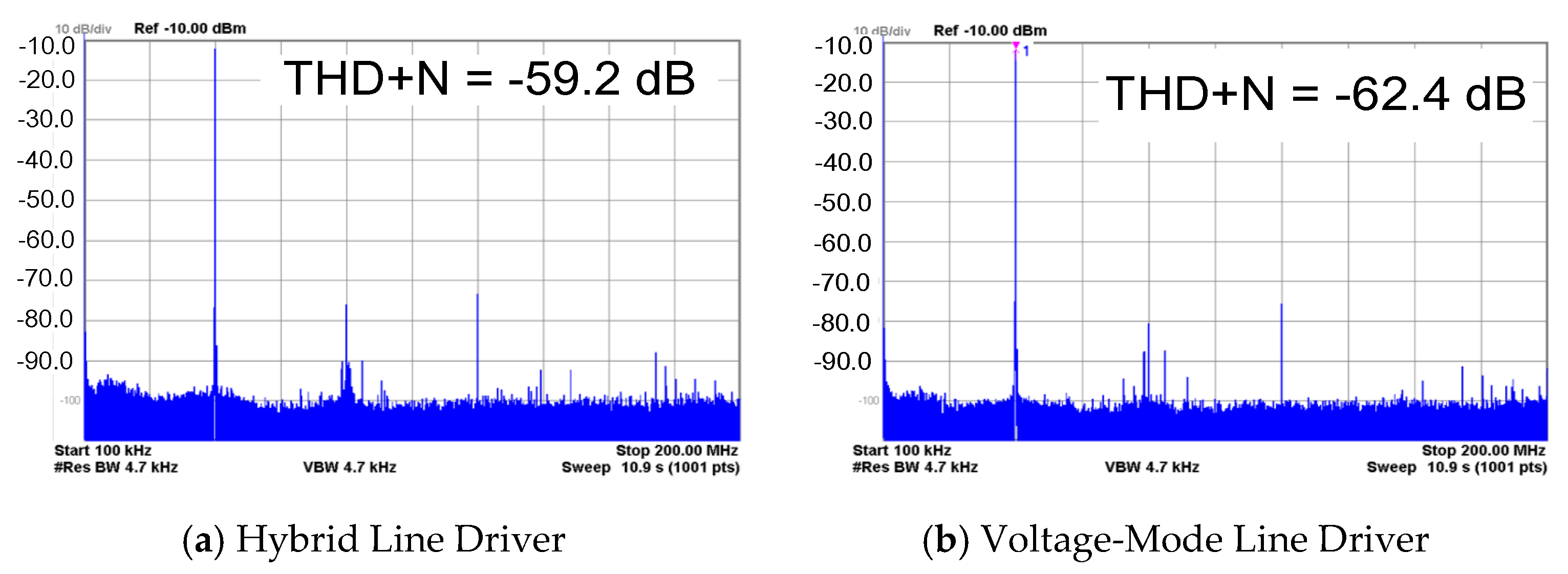

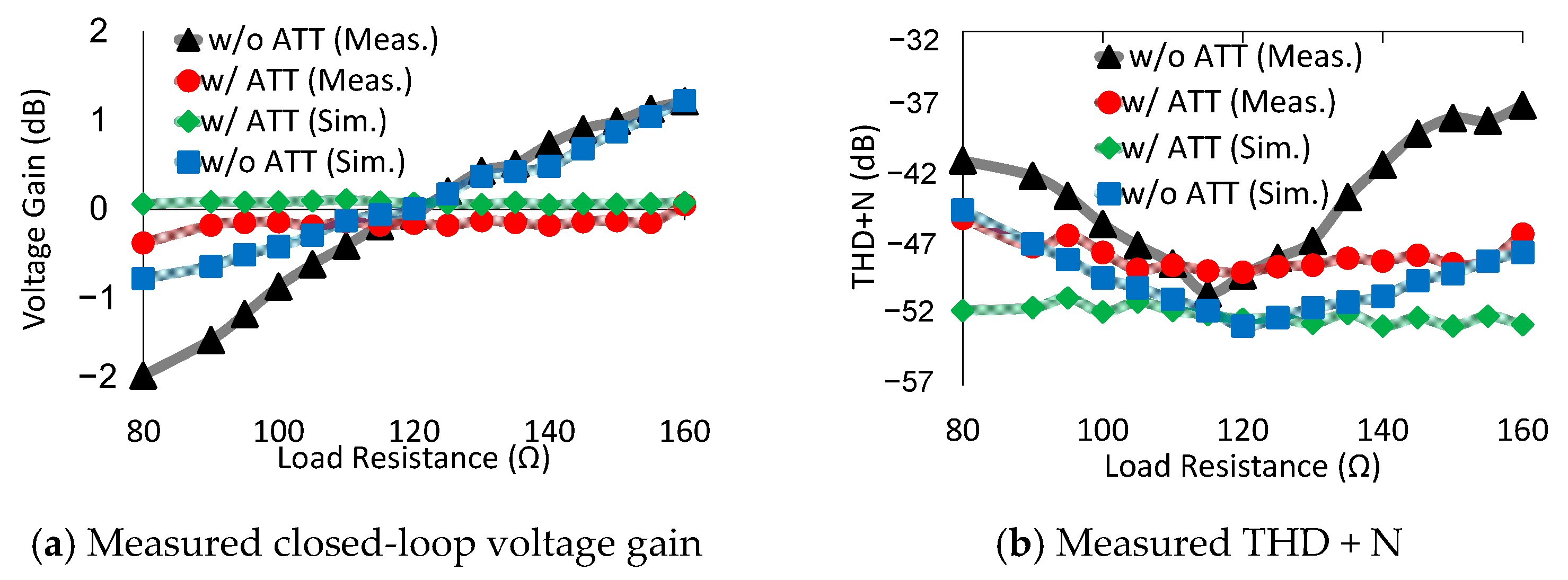

4. Measurement Results

5. Discussion and Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Ramachandran, N.; Dinc, H.; Karsilayan, A. A 3.3-V CMOS adaptive analog video line driver with low distortion performance. IEEE J. Solid-State Circuits 2003, 38, 1051–1058. [Google Scholar] [CrossRef]

- Babanezhad, J.N. A 100-MHz, 50-Ω, -45-dB distortion, 3.3-V CMOS line driver for Ethernet and fast Ethernet net-working applications. IEEE J. Solid-State Circuits 1999, 34, 1044–1050. [Google Scholar] [CrossRef]

- Ara, B.; Kim, C.-S.; Lee, S.-S. A CMOS line driver for ADSL central office applications. IEEE J. Solid-State Circuits 2003, 38, 2201–2208. [Google Scholar]

- Liu, P.-K.; Hung, S.-Y.; Liu, C.-Y.; Hsieh, M.-H.; Chen, C.C.-P. A 52 dBc MTPR line driver for powerline communication HomePlug AV standard in 0.18-μm CMOS technology. In Proceedings of the 2013 IEEE International Symposium on Circuits and Systems (ISCAS2013), Beijing, China, 19–23 May 2013; pp. 1404–1407. [Google Scholar] [CrossRef]

- Zhu, Z.; Wang, J. A Compact High-Performance Programmable-Gain Analog Front End for HomePlug AV2 Communication in 0.18 um CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1–13. [Google Scholar] [CrossRef]

- Johns, D.; Essig, D. Integrated circuits for data transmission over twisted-pair channels. IEEE J. Solid-State Circuits 1997, 32, 398–406. [Google Scholar] [CrossRef]

- Hadidi, K.; Oshima, H.; Sasaki, M.; Matsumoto, T. A highly linear fully differential low power CMOS line driver. In Proceedings of the ESSCIRC 2004—29th European Solid-State Circuits Conference (IEEE Cat. No.03EX705), Estoril, Portugal, 16–18 September 2004; pp. 541–544. [Google Scholar] [CrossRef]

- Pan, H.; Yao, Y.; Hammad, M.; Tan, J.; Abdelhalim, K.; Wang, E.W.; Hsu, R.C.J.; Tam, D.; Fujimori, I. A Full-Duplex Line Driver for Gigabit Ethernet with Rail-to-Rail Class-AB Output Stage in 28 nm CMOS. IEEE J. Solid-State Circuits 2014, 49, 3141–3155. [Google Scholar] [CrossRef]

- Mahadevan, R.; Johns, D. A differential 160-MHz self-terminating adaptive CMOS line driver. IEEE J. Solid-State Circuits 2000, 35, 1889–1894. [Google Scholar] [CrossRef]

- Sung, G.-M.; Chou, W.-D.; Yu, C.-P. A 10-bit 1.8 V 45 mW 100 MHz CMOS transmitter chip for use in an XDSL modem in a home network. Analog. Integr. Circuits Signal Process. 2014, 81, 515–527. [Google Scholar] [CrossRef]

- Kang, S.; Han, S.; Cho, S.; Jang, D.; Choi, H.; Choi, J.-W. High speed CAN transmission scheme supporting data rate of over 100 Mb/s. IEEE Commun. Mag. 2016, 54, 128–135. [Google Scholar] [CrossRef]

- Rida, S.A.; Silva-Martinez, J. The recycling folded cascode: A general enhancement of the folded cascode am-plifier. IEEE J. Solid-State Circuits 2009, 44, 2535–2542. [Google Scholar]

- Dasgupta, U. Low voltage 2-stage and 3-stage push-pull output amplifiers in 65-nm CMOS technology. In Proceedings of the 2016 International Symposium on Integrated Circuits (ISIC), Sinapore, 12–14 December 2016; pp. 1–4. [Google Scholar] [CrossRef]

- Nandish, M.; Huijsing, J.H.; Stojanović, V. A 1-mW Class-AB Amplifier With− 101 dB THD+ N for High-Fidelity 16 Ω Headphones in 65-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 948–958. [Google Scholar]

| Process Variations | |||||

| TT | SS | FF | SF | FS | |

| Loop Gain at DC [dB] | 64.1 | 68 | 61.3 | 64.9 | 63.4 |

| Phase Margin [deg.] | 57.2 | 57.2 | 57.9 | 55.1 | 59.3 |

| Unity-Gain Frequency [MHz] | 517 | 468 | 568 | 530 | 501 |

| Temperature Variations [°C] | |||||

| −40 | 27 | 125 | |||

| Loop Gain at DC [dB] | 67.4 | 64.1 | 59.5 | ||

| Phase Margin [deg.] | 54.3 | 57.2 | 60.1 | ||

| Unity-Gain Frequency [MHz] | 622 | 517 | 395 | ||

| Supply Voltage Variations [V] | |||||

| 1.62 | 1.8 | 1.98 | |||

| Loop Gain at DC [dB] | 62.4 | 64.1 | 65.2 | ||

| Phase Margin [deg.] | 57.6 | 57.2 | 55.9 | ||

| Unity-Gain Frequency [MHz] | 457 | 517 | 562 | ||

| 1000-Run Monte-Carlo Mismatch Simulation | |||||

| Mean | Standard Deviation | ||||

| Loop Gain at DC [dB] | 64.1 | 0.808 | |||

| Phase Margin [deg.] | 57.3 | 1.13 | |||

| Unity-Gain Frequency [MHz] | 516 | 16.0 | |||

| This Work (Hybrid LD) | This Work (VMLD) | [1] | [7] | [9] | [10] | |

|---|---|---|---|---|---|---|

| Process | 180 nm | 180 nm | 500 nm | 180 nm | 350 nm | 180 nm |

| Supply [V] | 1.8 | 1.8 | ±1.65 | 2.5 | 3.3 | 1.8 |

| VOUT [VPP,rms] | 0.99 | 0.33 | 0.85 | 1.06 | 1.41 | 1.24 |

| Eq. RLOAD [Ω] | 30 | 60 | 75 | 75 | 75 | 100 |

| PQ [mW] | 37.6 | 25.2 | 26.4 | 130 | 155 | 38.6 |

| Driving Mode 1 | I+V | V | I | V | I | I |

| PL [mW] | 32.7 | 1.82 | 19.2 | 15.6 | 26.6 | 30.6 |

| ηpower [%] | 87.0 | 7.22 | 36.5 | 12 | 17.2 | 39.8 |

| THD+N [dB] | −49.0 | −62.4 | −42 | −51.2 | −42 | −48 |

| THD+N [%] | 0.55 | 0.0759 | 0.794 | 0.275 | 0.794 | 0.398 |

| FIN [MHz] | 40 | 40 | 5 | 10 | 30 | 100 |

| Area [mm2] | 0.377 | 0.133 | 0.22 | 0.094 | 0.210 | 0.48 |

| FoM | 1.58 | 0.95 | 0.46 | 0.42 | 0.22 | 1.00 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, C.; Lee, M. An 87% Power-Efficiency Hybrid of Voltage- and Current-Mode Line Driver with an Adaptive Amplitude Tuning. Electronics 2021, 10, 1785. https://doi.org/10.3390/electronics10151785

Park C, Lee M. An 87% Power-Efficiency Hybrid of Voltage- and Current-Mode Line Driver with an Adaptive Amplitude Tuning. Electronics. 2021; 10(15):1785. https://doi.org/10.3390/electronics10151785

Chicago/Turabian StylePark, Changjoo, and Minjae Lee. 2021. "An 87% Power-Efficiency Hybrid of Voltage- and Current-Mode Line Driver with an Adaptive Amplitude Tuning" Electronics 10, no. 15: 1785. https://doi.org/10.3390/electronics10151785

APA StylePark, C., & Lee, M. (2021). An 87% Power-Efficiency Hybrid of Voltage- and Current-Mode Line Driver with an Adaptive Amplitude Tuning. Electronics, 10(15), 1785. https://doi.org/10.3390/electronics10151785