Evaluation of Low-Frequency Noise in MOSFETs Used as a Key Component in Semiconductor Memory Devices

Abstract

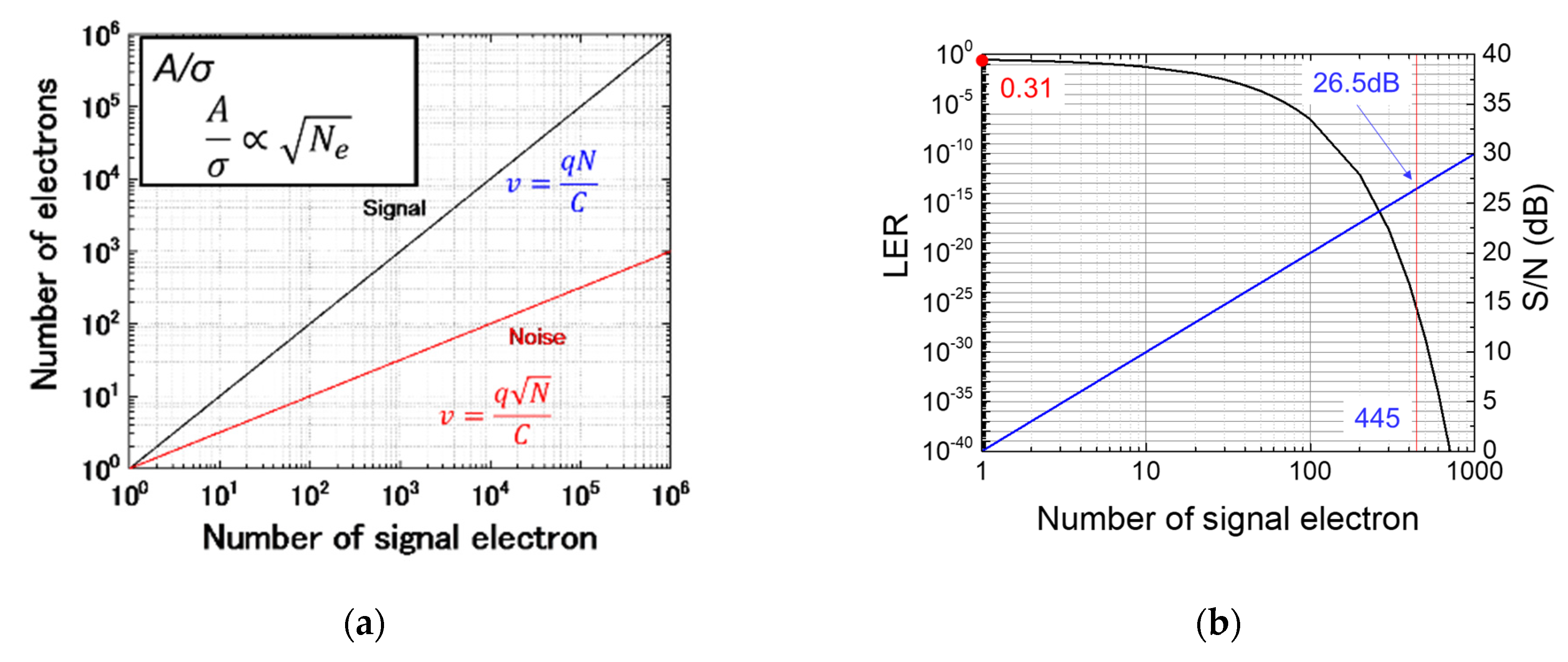

:1. Introduction

2. Evaluation Methods

2.1. Test Pattern for Noise Evaluation

2.2. Extraction of Amplitude and Time Constant of RTN

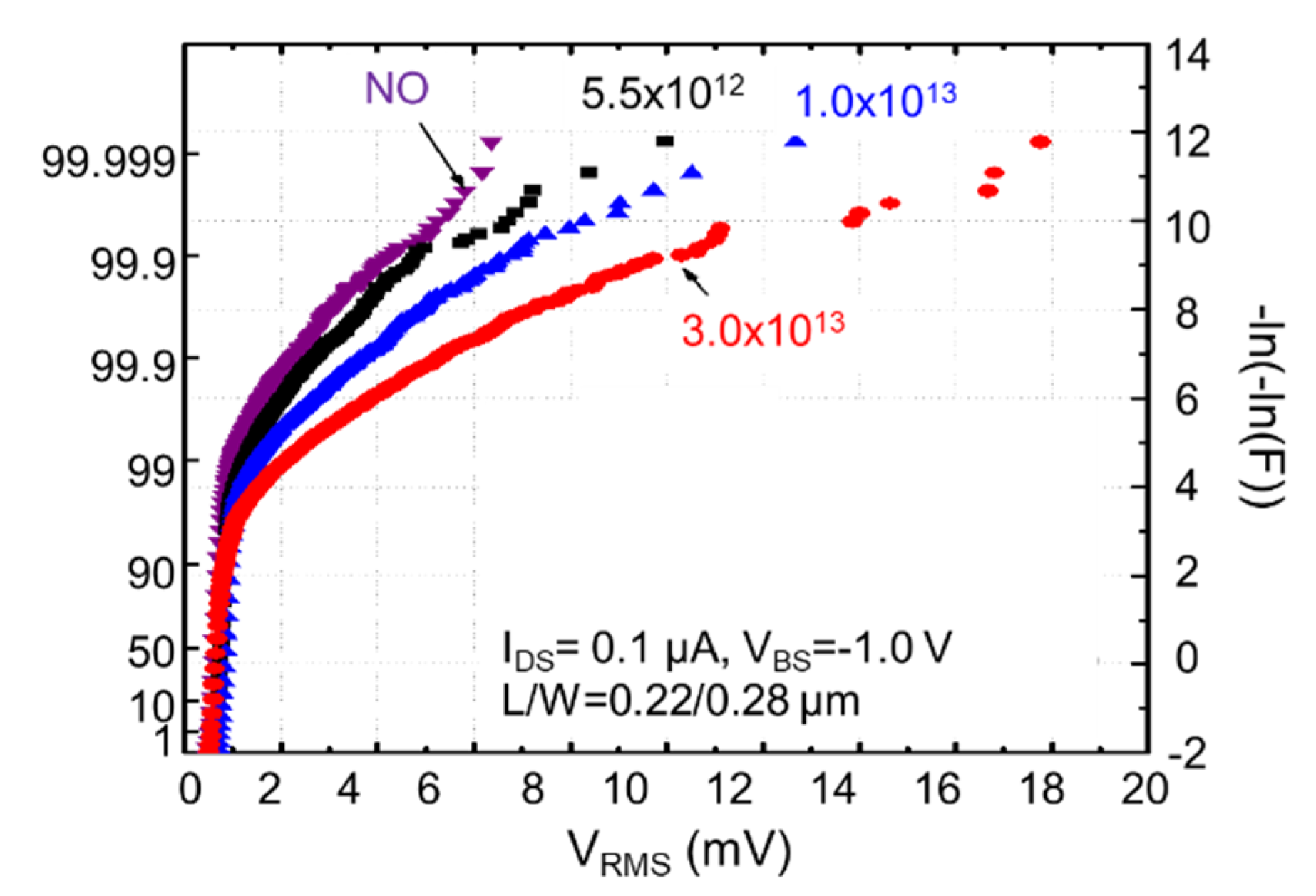

2.3. Root Mean Square of RTN Waveform

3. Results and Discussion

3.1. Statistical Evaluation of RTN Characteristics

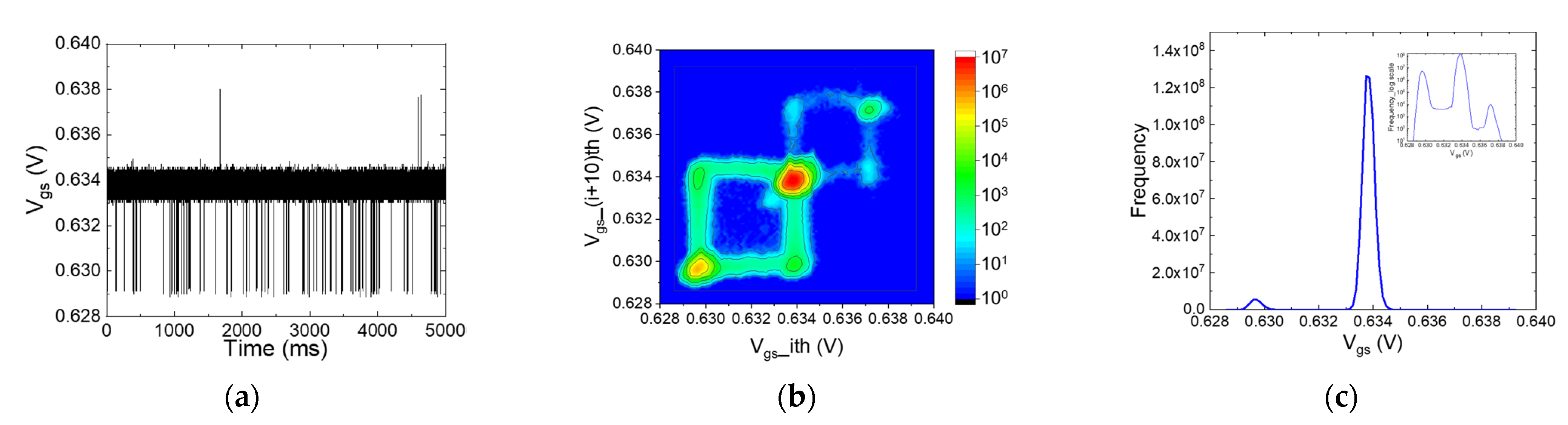

3.2. Multi-State RTN

3.3. Time Constants in Individual RTN

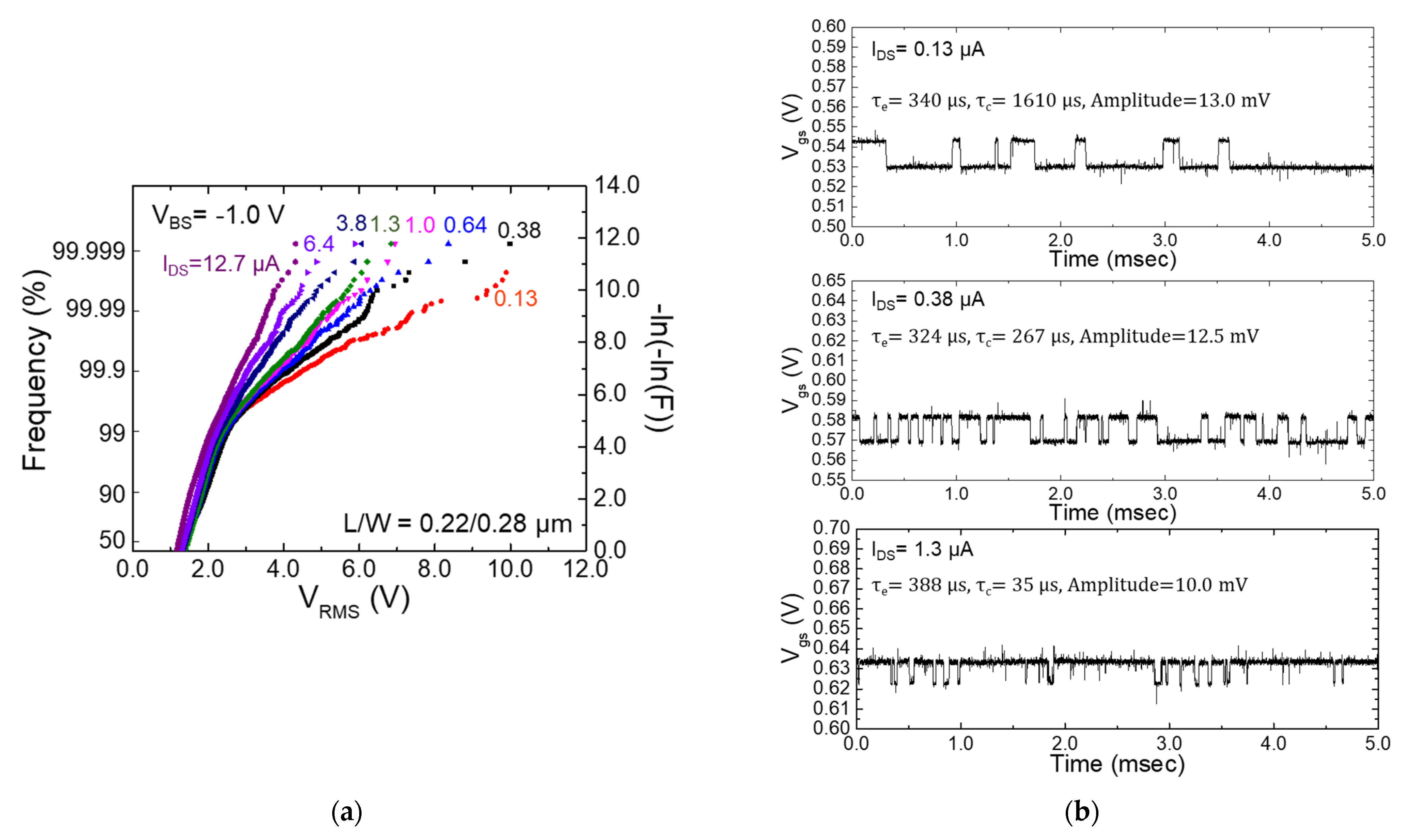

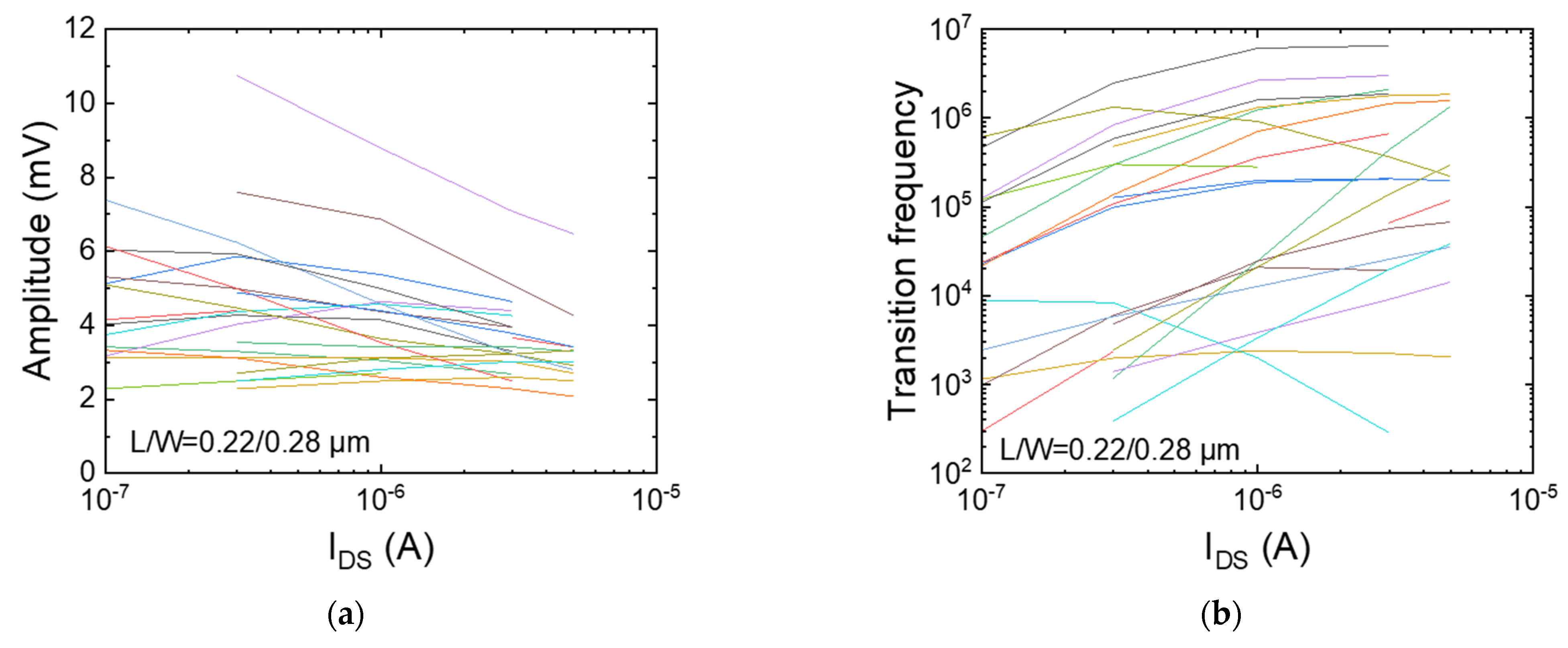

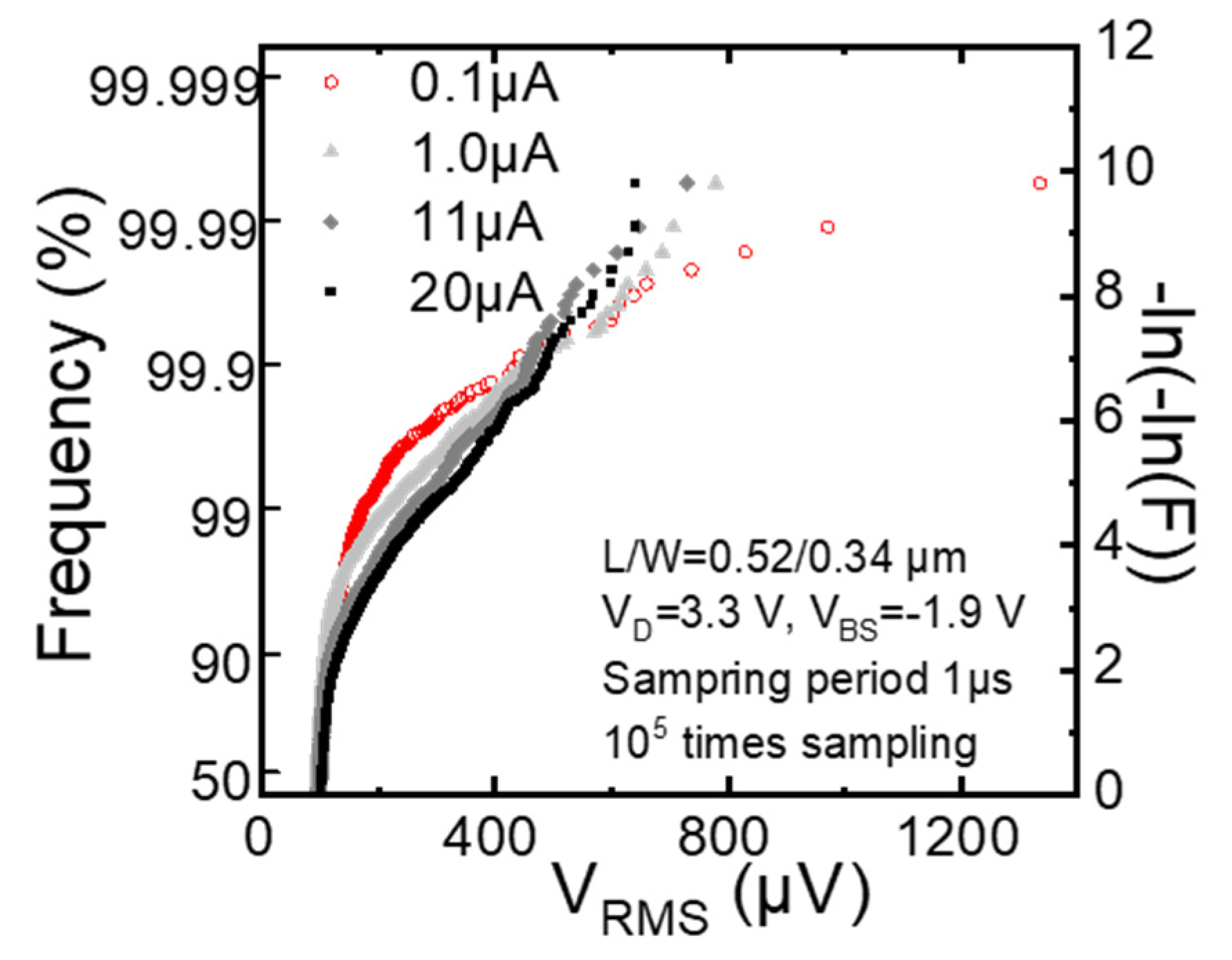

3.4. Effect of Drain Current on Appearance Probability and Amplitude

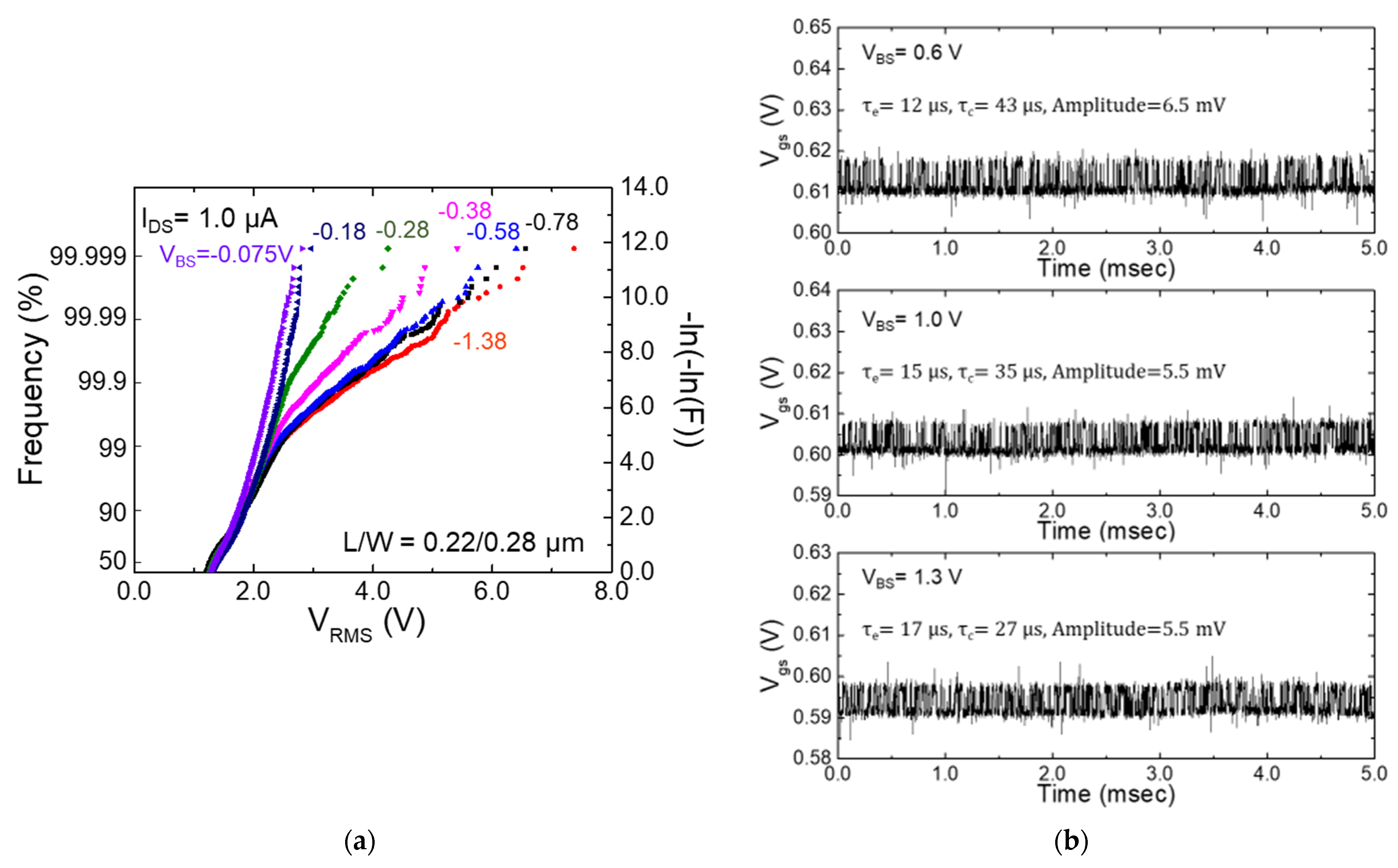

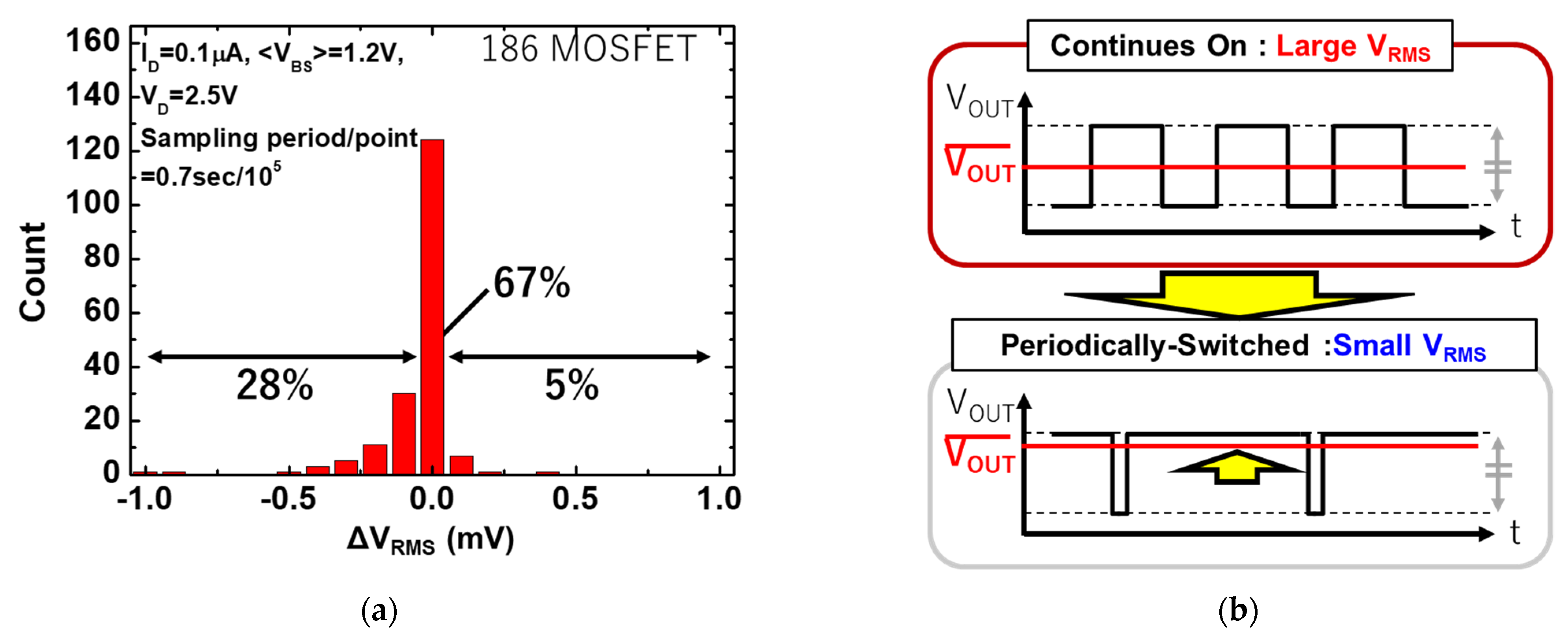

3.5. Modulation of Time Constants

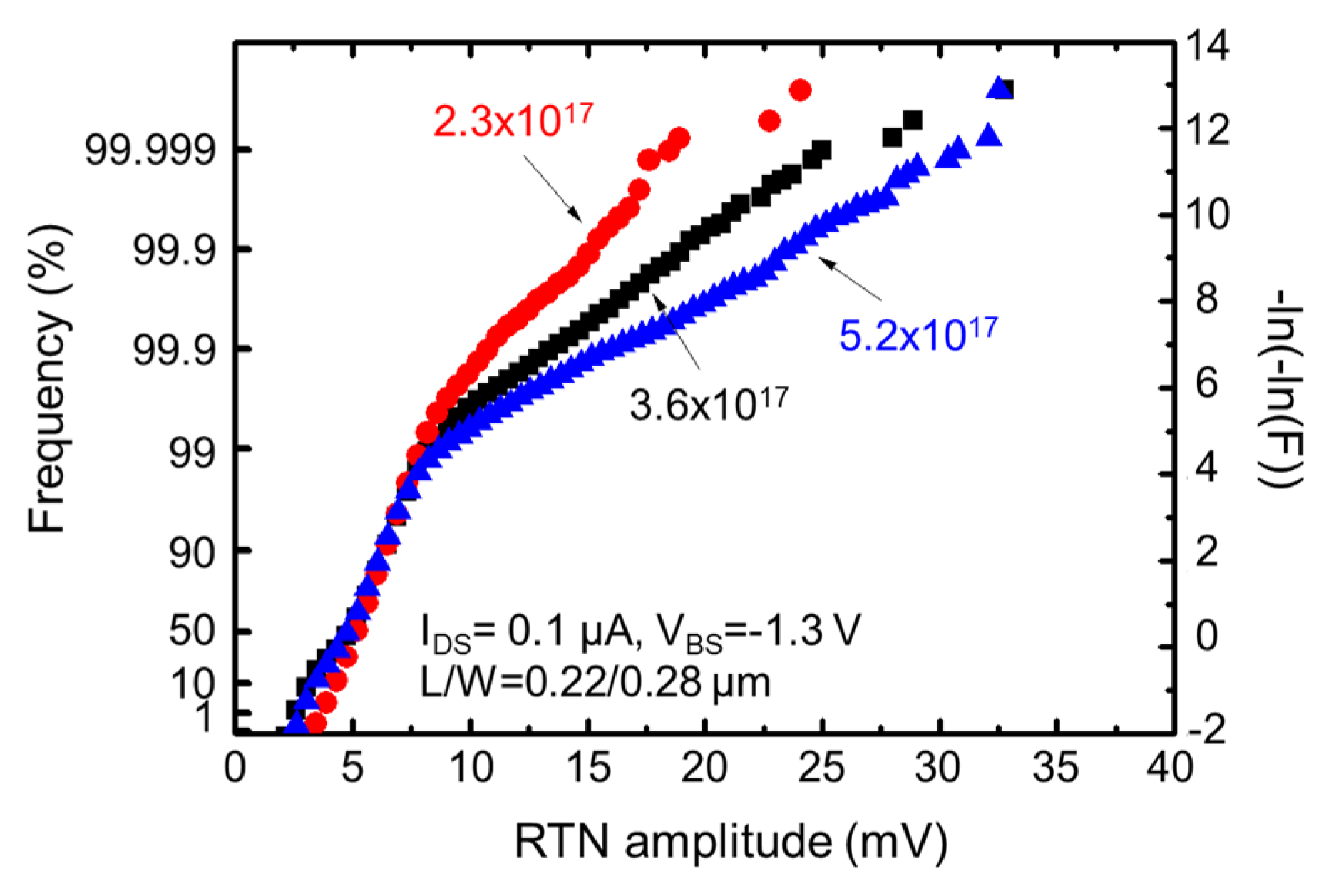

3.6. Device Structure Dependence of RTN

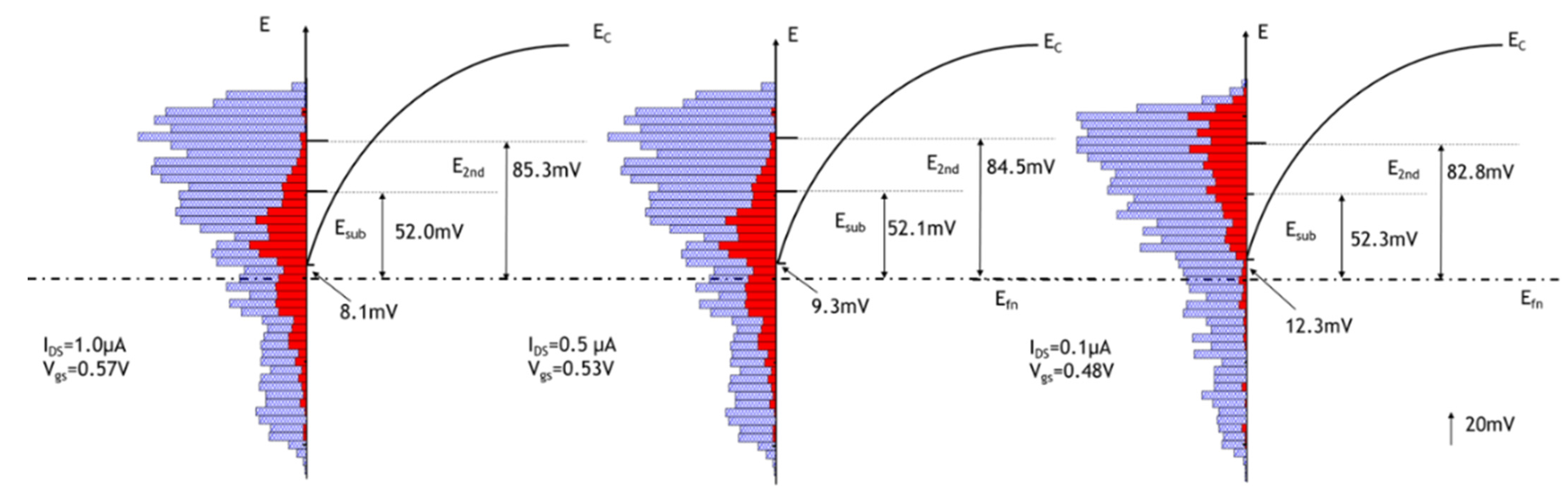

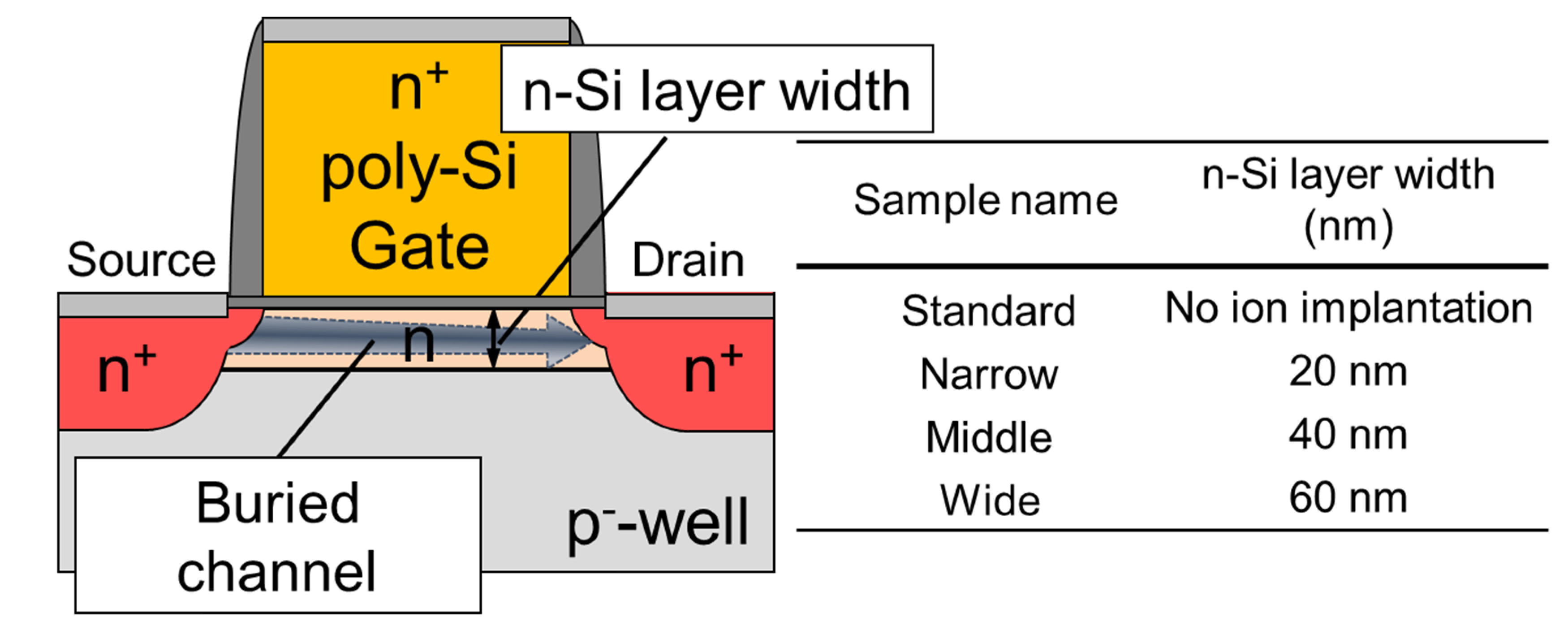

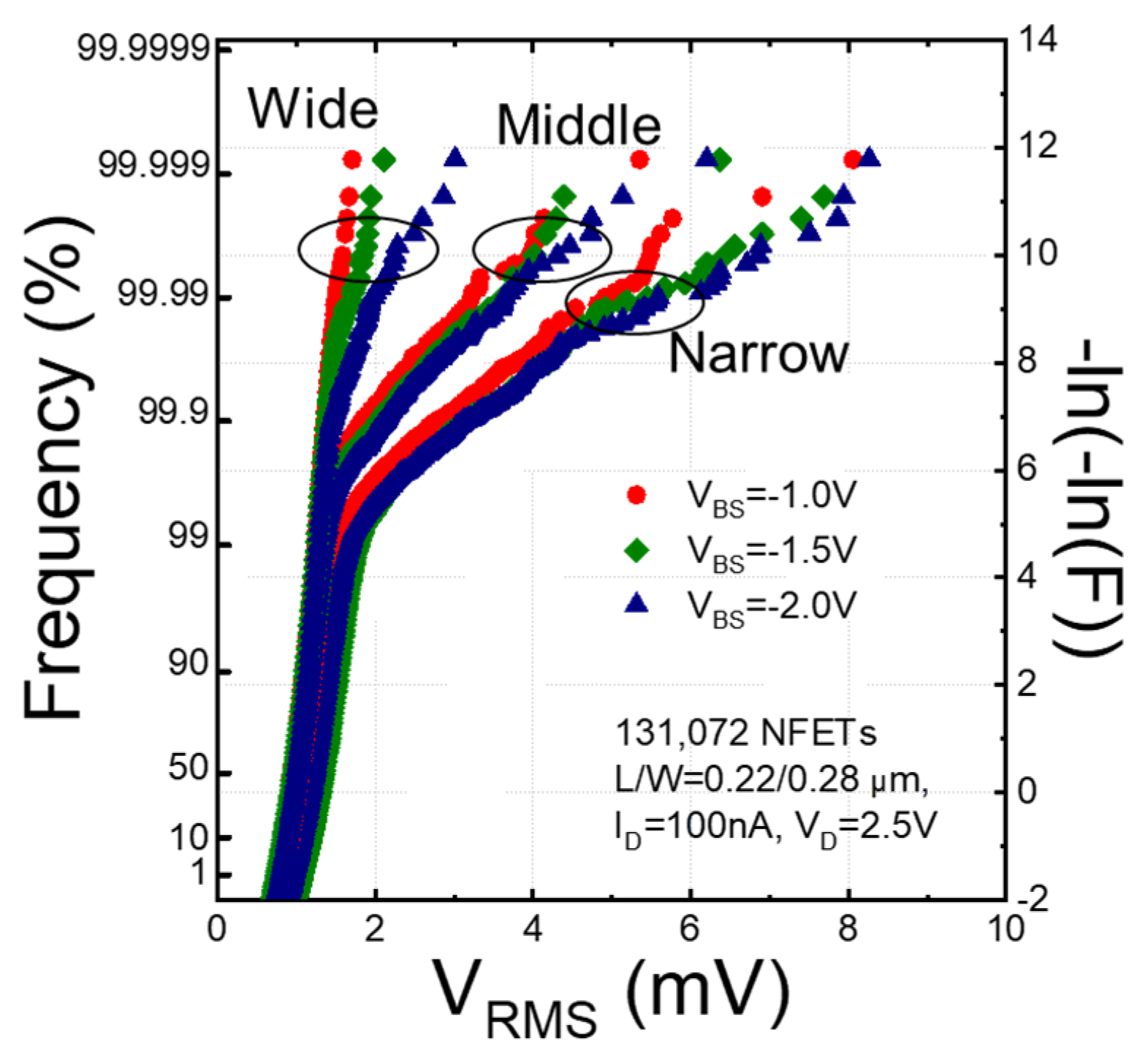

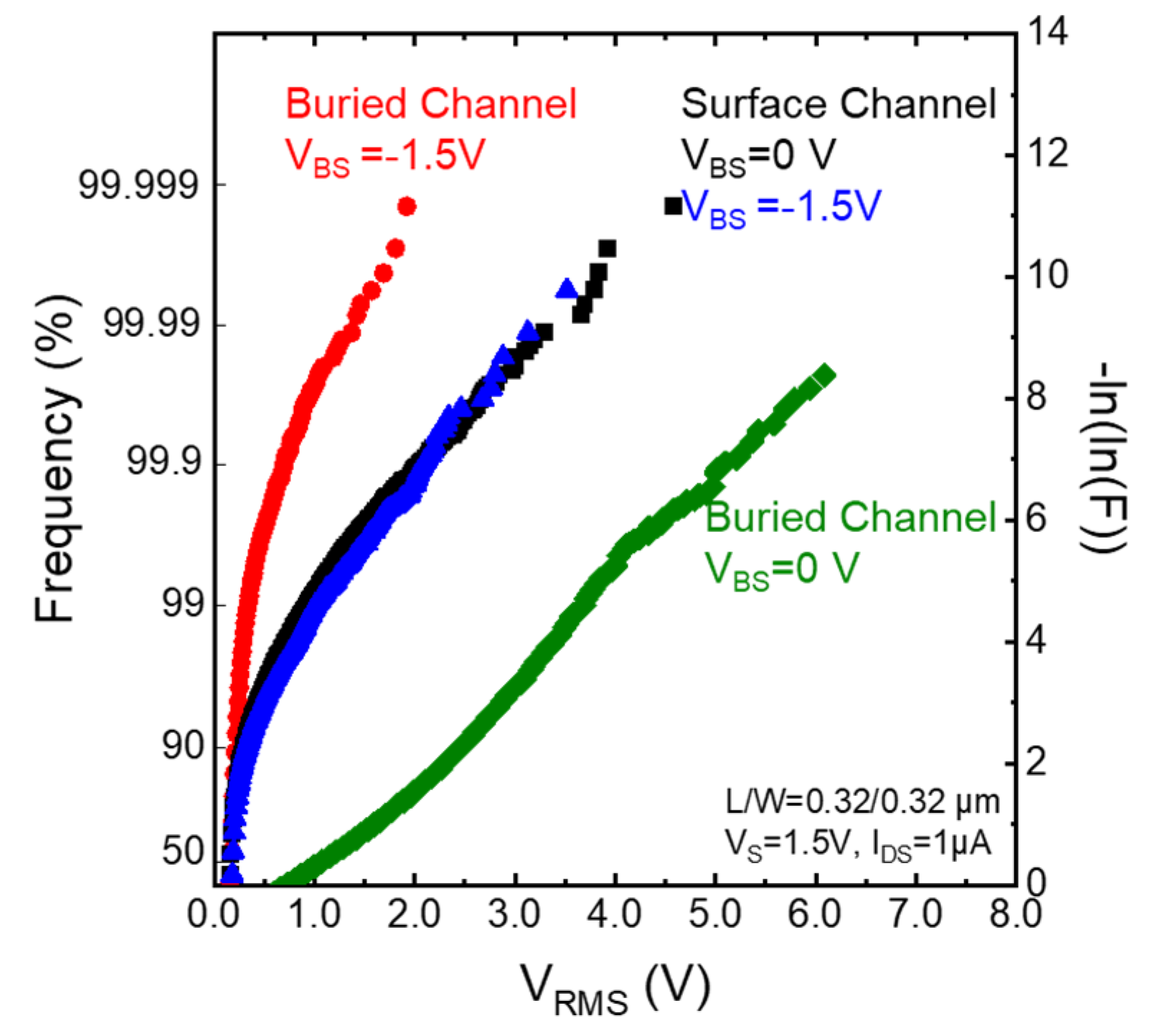

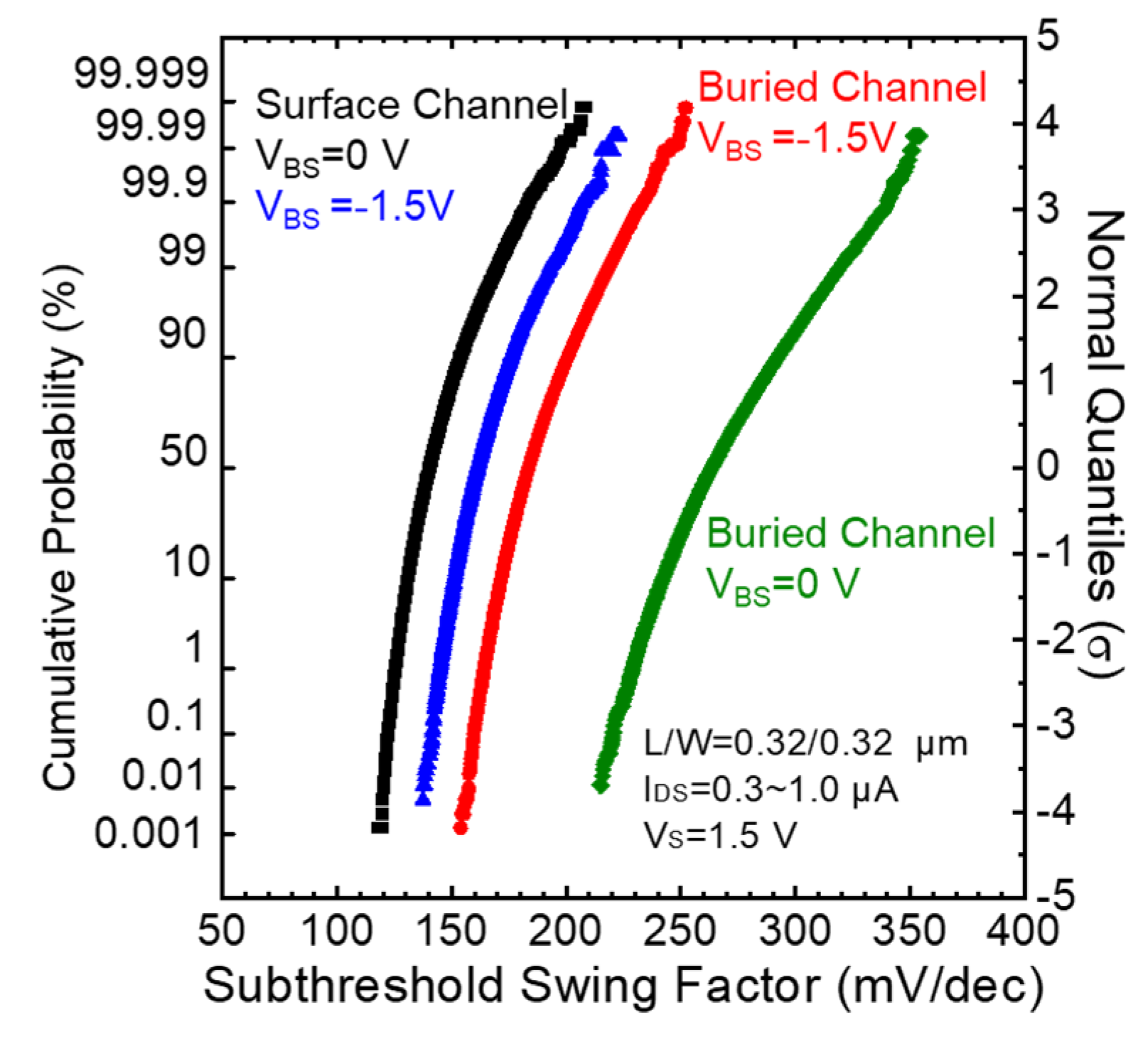

3.6.1. Buried Channel MOSFETs

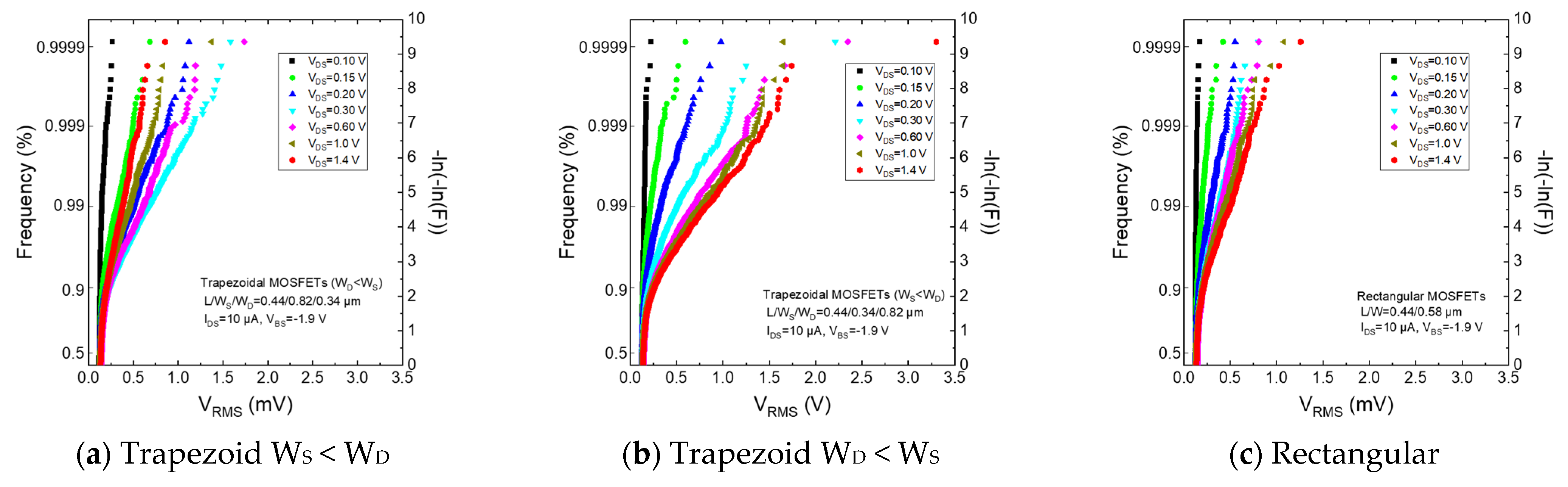

3.6.2. Asymmetry Source and Drain Width MOSFETs

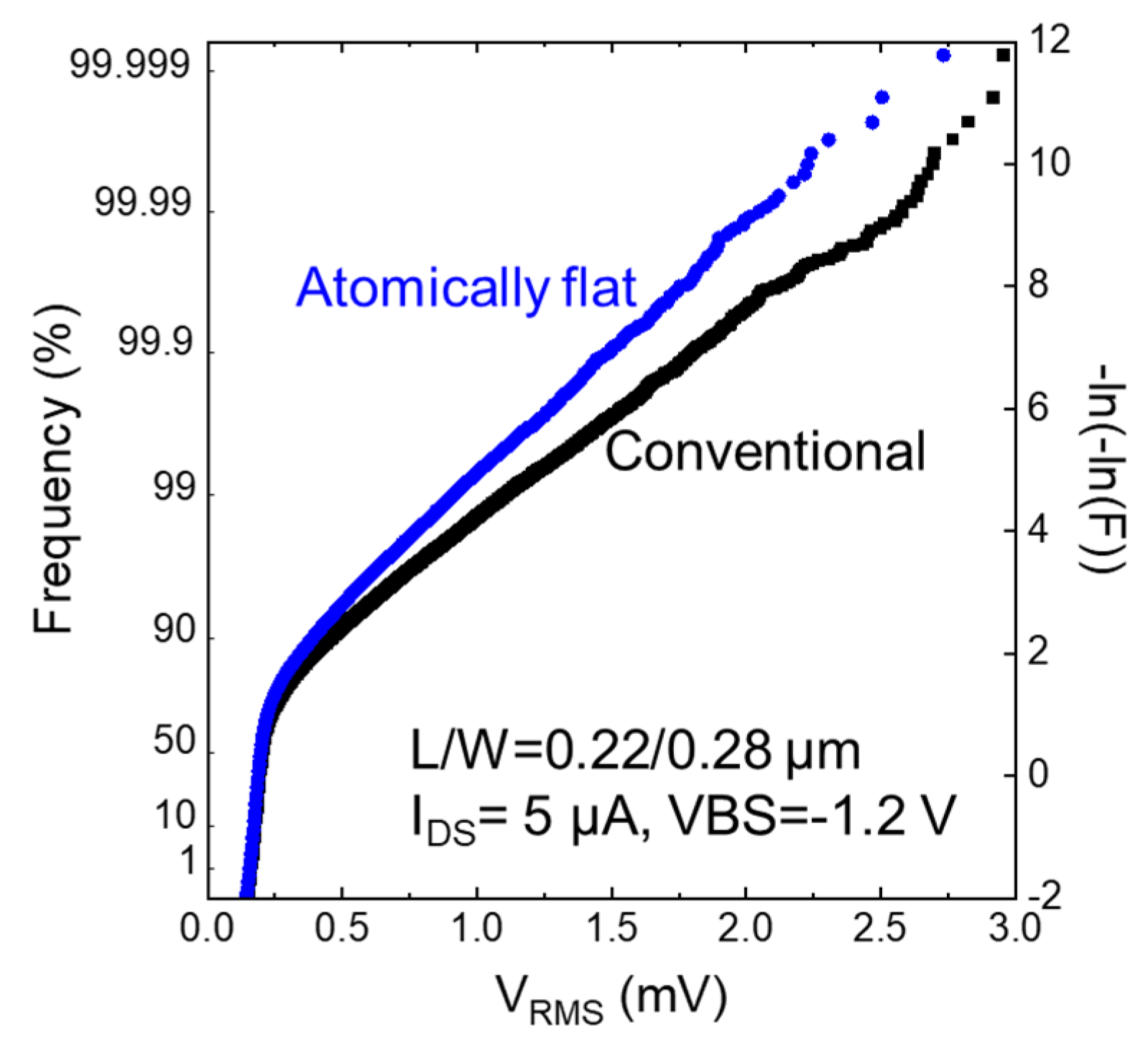

3.6.3. MOSFETs with Atomically Flat Gate Insulator/Si Interface

4. Conclusions

Funding

Acknowledgments

Conflicts of Interest

References

- Dennard, R.H.; Gaensslen, F.H.; Kuhn, L.; Yu, H.N. Design of micron MOS switching devices. In Proceedings of the 1972 International Electron Devices Meeting, Washington, DC, USA, 4–6 December 1972; pp. 168–170. [Google Scholar]

- Dennard, R.H.; Gaensslen, F.H.; Rideout, V.L.; Bassous, E.; LeBlanc, A.R. Design of ion-implanted MOSFET’s with very small physical dimensions. IEEE J. Solid-State Circuits 1974, 9, 256–268. [Google Scholar] [CrossRef] [Green Version]

- Moore, G.E. Cramming more components onto integrated circuits. Electronics 1965, 38, 114. [Google Scholar] [CrossRef]

- Boukhbza, J.; Plivier, P. Flash Memory Integration -Performance and Energy Considerations; Elsevier Ltd.: Oxford, UK, 2017. [Google Scholar]

- Parameswaran, S.; Hui, G. Power consumption in CMOS combinational logic blocks at high frequencies. In Proceedings of the ASP-DAC ‘97: Asia and South Pacific Design Automation Conference, Chiba, Japan, 28–31 January 1997; pp. 195–200. [Google Scholar]

- Appuswamy, R.; Olma, M.; Ailamaki, A. Scaling the Memory Power Wall With DRAM-Aware Data Management. In Proceedings of the 11th International Workshop on Data Management on New Hardware, Melbourne, VIC, Australia, 31 May–4 July 2015. [Google Scholar]

- Poess, M.; Nambiar, R.O. Energy cost, the key challenge of today’s data centers: A power consumption analysis of TPC-C results. In Proceedings of the 34th International Conference on Very Large Data Bases, Auckland, New Zealand, 23–28 August 2008; pp. 1229–1240. [Google Scholar]

- Karyakin, A.; Salem, K. An analysis of memory power consumption in database systems. In Proceedings of the 13th International Workshop on Data Management on New Hardware, Chicago, IL, USA, 15 May 2017. [Google Scholar]

- Carter, J.; Rajamani, K. Designing Energy-Efficient Servers and Data Centers. Computer 2010, 43, 76–78. [Google Scholar] [CrossRef]

- Ohmi, T.; Hirayama, M.; Teramoto, A. New era of silicon technologies due to radical reaction based semiconductor manufacturing. J. Phys. D Appl. Phys. 2006, 39, R1–R17. [Google Scholar] [CrossRef]

- Uren, M.J.; Day, D.J.; Kirton, M.J. 1/f and random telegraph noise in silicon metal-oxide-semiconductor field-effect transistors. Appl. Phys Lett. 1985, 47, 1195–1197. [Google Scholar] [CrossRef]

- Kirton, M.J.; Uren, M.J. Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise. Adv. Phys. 1989, 38, 367–468. [Google Scholar] [CrossRef]

- Christensson, S.; Lundström, I.; Svensson, C. Low frequency noise in MOS transistors—I Theory. Solid State Electron. 1968, 11, 797–812. [Google Scholar] [CrossRef]

- Toita, M.; Vandamme, L.K.J.; Sugawa, S.; Teramoto, A.; Ohmi, T. Geometry and bias dependence of low-frequency random telegraph signal and 1/f noise levels in mosfets. Fluct. Noise Lett. 2005, 5, L539–L548. [Google Scholar] [CrossRef]

- Sugawa, S. The Advanced Technology of the Semiconductor Integrated Circuits Needs the “Analog Intelligence” Again. DENSO Tech. Rev. 2005, 10, 3–9. (In Japanese) [Google Scholar]

- Leyris, C.; Martinez, F.; Valenza, M.; Hoffmann, A.; Vildeuil, J.C.; Roy, F. Impact of Random Telegraph Signal in CMOS Image Sensors for Low-Light Levels. In Proceedings of the 32nd European Solid-State Circuits Conference, Montreux, Swizerland, 19–21 September 2006; pp. 376–379. [Google Scholar]

- Wang, X.; Rao, P.R.; Mierop, A.; Theuwissen, A.J.P. Random Telegraph Signal in CMOS Image Sensor Pixels. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 115–118. [Google Scholar]

- Chao, C.Y.-P.; Tu, H.; Wu, T.M.-H.; Chou, K.-Y.; Yeh, S.-F.; Yin, C.; Lee, C.-L. Statistical Analysis of the Random Telegraph Noise in a 1.1 μm Pixel, 8.3 MP CMOS Image Sensor Using On-Chip Time Constant Extraction Method. Sensors 2017, 17, 2704. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Chao, C.Y.-P.; Yeh, S.-F.; Wu, M.-H.; Chou, K.-Y.; Tu, H.; Lee, C.-L.; Yin, C.; Paillet, P.; Goiffon, V. Random Telegraph Noises from the Source Follower, the Photodiode Dark Current, and the Gate-Induced Sense Node Leakage in CMOS Image Sensors. Sensors 2019, 19, 5447. [Google Scholar] [CrossRef] [Green Version]

- Kuroda, R.; Teramoto, A.; Sugawa, S. Impacts of Random Telegraph Noise with Various Time Constants and Number of States in Temporal Noise of CMOS Image Sensors. ITE Trans. Media Technol. Appl. 2018, 6, 171–179. [Google Scholar] [CrossRef]

- Wang, X.; Snoeij, M.F.; Rao, P.R.; Mierop, A.; Theuwissen, A.J.P. A CMOS Image Sensor with a Buried-Channel Source Follower. In Proceedings of the IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 3–7 February 2008; pp. 62–595. [Google Scholar]

- Toh, S.O.; Tsukamoto, Y.; Zheng, G.; Jones, L.; Tsu-Jae King, L.; Nikolic, B. Impact of random telegraph signals on Vmin in 45nm SRAM. In Proceedings of the IEEE International Electron Devices Meeting, Baltimore, MD, USA, 24 July 2020; pp. 767–770. [Google Scholar]

- Takeuchi, K.; Nagumo, T.; Takeda, K.; Asayama, S.; Yokogawa, S.; Imai, K.; Hayashi, Y. Direct observation of RTN-induced SRAM failure by accelerated testing and its application to product reliability assessment. In Proceedings of the Symposium on VLSI Technology, 15–17 June 2010; pp. 189–190. [Google Scholar]

- Tanizawa, M.; Ohbayashi, S.; Okagaki, T.; Sonoda, K.; Eikyu, K.; Hirano, Y.; Ishikawa, K.; Tsuchiya, O.; Inoue, Y. Application of a Statistical Compact Model for Random Telegraph Noise to Scaled-SRAM Vmin Analysis. In Proceedings of the Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2010; pp. 95–96. [Google Scholar]

- Aadithya, K.V.; Demir, A.; Venugopalan, S.; Roychowdhury, J. Accurate Prediction of Random Telegraph Noise Effects in SRAMs and DRAMs. IEEE Trans. Computer-Aided Des. Integr. Circuits Syst. 2013, 32, 73–86. [Google Scholar] [CrossRef] [Green Version]

- Compagnoni, C.M.; Gusmeroli, R.; Spinelli, A.S.; Lacaita, A.L.; Bonanomi, M.; Visconti, A. Statistical Investigation of Random Telegraph Noise ID Instabilities in Flash Cells at Different Initial Trap-filling Conditions. In Proceedings of the International Reliability physics symposium, Phoenix, AZ, USA, 15–19 April 2007; pp. 161–166. [Google Scholar]

- Tega, N.; Miki, H.; Osabe, T.; Kotabe, A.; Otsuga, K.; Kurata, H.; Kamohara, S.; Tokami, K.; Ikeda, Y.; Yamada, R. Anomalously Large Threshold Voltage Fluctuation by Complex Random Telegraph Signal in Floating Gate Flash Memory. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 1995; pp. 491–494. [Google Scholar]

- Kurata, H.; Otsuga, K.; Kotabe, A.; Kajiyama, S.; Osabe, T.; Sasago, Y.; Narumi, S.; Tokami, K.; Kamohara, S.; Tsuchiya, O. The Impact of Random Telegraph Signals on the Scaling of Multilevel Flash Memories. In Proceedings of the Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2006; pp. 112–113. [Google Scholar]

- Kurata, H.; Otsuga, K.; Kotabe, A.; Kajiyama, S.; Osabe, T.; Sasago, Y.; Narumi, S.; Tokami, K.; Kamohara, S.; Tsuchiya, O. Random Telegraph Signal in Flash Memory: Its Impact on Scaling of Multilevel Flash Memory Beyond the 90-nm Node. IEEE J. Olid-State Circuits 2007, 42, 1362–1369. [Google Scholar] [CrossRef]

- Sing-Rong, L.; McMahon, W.; Lu, Y.L.R.; Yung-Huei, L. RTS Noise Characterization in Flash Cells. IEEE Electron Device Lett. 2008, 29, 106–108. [Google Scholar]

- Ghetti, A.; Compagnoni, C.M.; Spinelli, A.S.; Visconti, A. Comprehensive Analysis of Random Telegraph Noise Instability and Its Scaling in Deca-Nanometer Flash Memories. IEEE Trans. Electron Devices 2009, 56, 1746–1752. [Google Scholar] [CrossRef]

- Cai, Y.; Song, Y.H.; Kwon, W.-H.; Lee, B.Y.; Park, C.-K. The Impact of Random Telegraph Signals on the Threshold Voltage Variation of 65 nm Multilevel NOR Flash Memory. Jpn. J. Appl. Phys. 2008, 47, 2733. [Google Scholar] [CrossRef]

- Toita, M.; Sugawa, S.; Teramoto, A.; Ohmi, T. Sub-Micron MOSFETs Technology Characterization by Low-Frequency Noise. In Proceedings of the 3rd European Microelectronics and Packaging Symposium, Prague, Czech Republic, 16–18 June 2004; pp. 19–24. [Google Scholar]

- Abe, K.; Fujisawa, T.; Teramoto, A.; Watabe, S.; Sugawa, S.; Ohmi, T. Anomalous Random Telegraph Signal Extractions from a Very Large Number of n-Metal Oxide Semiconductor Field-Effect Transistors Using Test Element Groups with 0.47 Hz-3.0 MHz Sampling Frequency. Jpn. J. Appl. Phys. 2009, 48. [Google Scholar] [CrossRef]

- Watabe, S.; Sugawa, S.; Teramoto, A.; Ohmi, T. New Statistical Evaluation Method for the Variation of Metal-Oxide-Semiconductor Field-Effect Transistors. Jpn. J. Appl. Phys. 2007, 46, 2054–2057. [Google Scholar] [CrossRef]

- Abe, K.; Sugawa, S.; Watabe, S.; Miyamoto, N.; Teramoto, A.; Toita, M.; Kamata, Y.; Shibusawa, K.; Ohmi, T. Statistical Analysis of RTS Noise and Low Frequency Noise in 1M MOSFETs Using an Advanced TEG. In Proceedings of the 19th International Conference on Noise and Fluctuations, Tokyo, Japan, 9–14 September 2007; pp. 115–118. [Google Scholar]

- Abe, K.; Sugawa, S.; Watabe, S.; Miyamoto, N.; Teramoto, A.; Kamata, Y.; Shibusawa, K.; Toita, M.; Ohmi, T. Random Telegraph Signal Statistical Analysis using a Very Large-scale Array TEG with 1M MOSFETs. In Proceedings of the IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 210–211. [Google Scholar]

- Kumagai, Y.; Abe, K.; Fujisawa, T.; Watabe, S.; Kuroda, R.; Miyamoto, N.; Suwa, T.; Teramoto, A.; Sugawa, S.; Ohmi, T. Large-Scale Test Circuits for High-Speed and Highly Accurate Evaluation of Variability and Noise in Metal-Oxide-Semiconductor Field-Effect Transistor Electrical Characteristics. Jpn. J. Appl. Phys. 2011, 50. [Google Scholar] [CrossRef]

- Abe, K.; Sugawa, S.; Kuroda, R.; Watabe, S.; Miyamoto, N.; Teramoto, A.; Ohmi, T.; Kamata, Y.; Shibusawa, K. Analysis of Source Follower Random Telegraph Signal Using nMOS and pMOS Array TEG. In Proceedings of the International Image Sensor Workshop, Ogunquit, MA, USA, 7–10 June 2007; pp. 62–65. [Google Scholar]

- Watabe, S.; Teramoto, A.; Abe, K.; Fujisawa, T.; Miyamoto, N.; Sugawa, S.; Ohmi, T. A Simple Test Structure for Evaluating the Variability in Key Characteristics of a Large Number of MOSFETs. IEEE Trans. Semicond. Manuf. 2012, 25, 145–154. [Google Scholar] [CrossRef]

- Teramoto, A.; Fujisawa, T.; Abe, K.; Sugawa, S.; Ohmi, T. Statistical evaluation for trap energy level of RTS characteristics. In Proceedings of the Symposium on VLSI Technology, Honolulu, HI, USA, 15–17 June 2016; pp. 99–100. [Google Scholar]

- Fujisawa, T.; Abe, K.; Watabe, S.; Miyamoto, N.; Teramoto, A.; Sugawa, S.; Ohmi, T. Analysis of Hundreds of Time Constant Ratios and Amplitudes of Random Telegraph Signal with Very Large Scale Array Test Pattern. Jpn. J. Appl. Phys. 2010, 49. [Google Scholar] [CrossRef]

- Fujisawa, T.; Abe, K.; Watabe, S.; Miyamoto, N.; Teramoto, A.; Sugawa, S.; Ohmi, T. Accurate Time Constant of Random Telegraph Signal Extracted by a Sufficient Long Time Measurement in Very Large-Scale Array TEG. In Proceedings of the IEEE International Conference on Microelectronic Test Structures, Oxnard, CA, USA, 30 March–2 April 2009; pp. 19–24. [Google Scholar]

- Abe, K.; Teramoto, A.; Sugawa, S.; Ohmi, T. Understanding of Traps Causing Random Telegraph Noise Based on Experimentally Extracted Time Constants and Amplitude. In Proceedings of the International Reliability physics symposium, Monterey, CA, USA, 10–14 April 2011; pp. 381–386. [Google Scholar]

- Haartman, M.V.; Östling, M. LOW-Frequency Noise in Advanced Mos Devices, 1 ed.; Springer Netherlands: Dordrecht, The Netherland, 2007. [Google Scholar] [CrossRef]

- Slavcheva, G.; Davies, J.H.; Brown, A.R.; Asenov, A. Potential fluctuations in metal--oxide--semiconductor field-effect transistors generated by random impurities in the depletion layer. J. Appl. Phys. 2002, 91, 4326–4334. [Google Scholar] [CrossRef] [Green Version]

- Asenov, A.; Balasubramaniam, R.; Brown, A.R.; Davies, J.H. RTS amplitudes in decananometer MOSFETs: 3-D simulation study. IEEE Trans. Electron Devices 2003, 50, 839–845. [Google Scholar] [CrossRef]

- Sano, N.; Yoshida, K.; Yao, C.-W.; Watanabe, H. Physics of Discrete Impurities under the Framework of Device Simulations for Nanostructure Devices. Materials 2018, 11, 2559. [Google Scholar] [CrossRef] [Green Version]

- Sonoda, K.; Ishikawa, K.; Eimori, T.; Tsuchiya, O. Discrete Dopant Effects on Statistical Variation of Random Telegraph Signal Magnitude. IEEE Trans. Electron Devices 2007, 54, 1918–1925. [Google Scholar] [CrossRef]

- Taur, Y.; Ning, T.H. Fundamentals of Modern VLSI Devices, 2nd ed.; Cambridge University Press: Cambridge, UK, 2009; pp. 234–239. [Google Scholar]

- Abe, K.; Teramoto, A.; Watabe, S.; Fujisawa, T.; Sugawa, S.; Kamata, Y.; Shibusawa, K.; Ohmi, T. Experimental Investigation of Effect of Channel Doping Concentration on Random Telegraph Signal Noise. Jpn. J. Appl. Phys. 2010, 49. [Google Scholar] [CrossRef]

- Hauser, J.R. Handbook of Semiconductor Manufacturing Technology, 2 ed.; CRC Press: Boca Raton, FL, USA, 2007. [Google Scholar]

- Obara, T.; Teramoto, A.; Yonezawa, A.; Kuroda, R.; Sugawa, S.; Ohmi, T. Analyzing Correlation between Multiple Traps in RTN Characteristics. In Proceedings of the International Reliability Physics Symposium, Waikoloa, HI, USA, 1–5 June 2014. [Google Scholar]

- Nagumo, T.; Takeuchi, K.; Yokogawa, S.; Imai, K.; Hayashi, Y. New Analysis Methods for Comprehensive Understanding of Random Telegraph Noise. In Proceedings of the Technical Digest IEEE International Electron Devices Meeting, Baltimore, MD, USA, 7–9 December 2009; pp. 759–762. [Google Scholar]

- Nagumo, T.; Takeuchi, K.; Hase, T.; Hayashi, Y. Statistical characterization of trap position, energy, amplitude and time constants by RTN measurement of multiple individual traps. In Proceedings of the 2010 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 628–631. [Google Scholar]

- Tsuchiya, T.; Tamura, N.; Sakakidani, A.; Sonoda, K.; Kamei, M.; Yamakawa, S.; Kuwabara, S. Characterization of Oxide Traps Participating in Random Telegraph Noise Using Charging History Effects in Nano-Scaled MOSFETs. ECS Trans. 2013, 58, 265–279. [Google Scholar] [CrossRef]

- Yonezawa, A.; Teramoto, A.; Kuroda, R.; Suzuki, H.; Sugawa, S.; Ohmi, T. Statistical analysis of Random Telegraph Noise reduction effect by separating channel from the interface. In Proceedings of the IRPS, Anaheim, CA, USA, 15–19 April 2012. [Google Scholar]

- Obara, T.; Yonezawa, A.; Teramoto, A.; Kuroda, R.; Sugawa, S.; Ohmi, T. Extraction of time constants ratio over nine orders of magnitude for understanding random telegraph noise in metal–oxide–semiconductor field-effect transistors. Jpn. J. Appl. Phys. 2014, 53. [Google Scholar] [CrossRef]

- Yonezawa, A.; Teramoto, A.; Obara, T.; Kuroda, R.; Sugawa, S.; Ohmi, T. The study of time constant analysis in random telegraph noise at the sub-threshold voltage region. In Proceedings of the International Reliability Physics Symposium Monterey, Anaheim, CA, USA, 14–18 April 2012; p. XT11. [Google Scholar]

- Ichino, S.; Mawaki, T.; Teramoto, A.; Kuroda, R.; Park, H.; Wakashima, S.; Goto, T.; Suwa, T.; Sugawa, S. Effect of drain current on appearance probability and amplitude of random telegraph noise in low-noise CMOS image sensors. Jpn. J. Appl. Phys. 2018, 57. [Google Scholar] [CrossRef] [Green Version]

- Yonezawa, A.; Kuroda, R.; Teramoto, A.; Obara, T.; Sugawa, S. A statistical evaluation of effective time constants of random telegraph noise with various operation timings of in-pixel source follower transistors. In Proceedings of the SPIE-IS&T Electronic Imaging, SPIE, San Francisco, CA, USA, 2–6 February 2014; p. 90220F. [Google Scholar]

- Ichino, S.; Mawaki, T.; Teramoto, A.; Kuroda, R.; Wakashima, S.; Suwa, T.; Sugawa, S. Statistical Analyses of Random Telegraph Noise in Pixel Source Follower with Various Gate Shapes in CMOS Image Sensor. ITE Trans. Media Technol. Appl. 2018, 6, 163–170. [Google Scholar] [CrossRef] [Green Version]

- Akimoto, R.; Kuroda, R.; Teramoto, A.; Mawaki, T.; Ichino, S.; Suwa, T.; Sugawa, S. Effect of Drain-to-Source Voltage on Random Telegraph Noise Based on Statistical Analysis of MOSFETs with Various Gate Shapes. In Proceedings of the 2020 IEEE International Reliability Physics Symposium, 28 April–30 May 2020; p. 9A2. [Google Scholar]

- Kuroda, R.; Yonezawa, A.; Teramoto, A.; Li, T.L.; Tochigi, Y.; Sugawa, S. A Statistical Evaluation of Random Telegraph Noise of In-Pixel Source Follower Equivalent Surface and Buried Channel Transistors. IEEE Trans. Electron Devices 2013, 60, 3555–3561. [Google Scholar] [CrossRef]

- Suzuki, H.; Kuroda, R.; Teramoto, A.; Yonezawa, A.; Sugawa, S.; Ohmi, T. Impact of Random Telegraph Noise Reduction with Buried Channel MOSFET. In Proceedings of the 2011 International Conference on Solid State Devices and Materials, Nagoya, Japan, 28–30 September 2011; pp. 851–852. [Google Scholar]

- Yamanaka, T.; Fang, S.J.; Heng-Chih, L.; Snyder, J.P.; Helms, C.R. Correlation between inversion layer mobility and surface roughness measured by AFM. IEEE Electron Device Lett. 1996, 17, 178–180. [Google Scholar] [CrossRef]

- Ohmi, T.; Kotani, K.; Teramoto, A.; Miyashita, M. Dependence of electron channel mobility on Si-SiO2 interface microroughness. IEEE Electron Device Lett. 1991, 12, 652–654. [Google Scholar] [CrossRef]

- Ishizaka, M.; Iizuka, T.; Ohi, S.; Fukuma, M.; Mikoshiba, H. Advanced electron mobility model of MOS inversion layer considering 2D-degenerate electron gas physics. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 9–12 December 1990; pp. 763–766. [Google Scholar]

- Ferry, D.K. The transport of electrons in quantized inversion and accumulation layers in III–V compounds. Thin Solid Films 1979, 56, 243–252. [Google Scholar] [CrossRef]

- Takagi, S.; Toriumi, A.; Iwase, M.; Tango, H. On the universality of inversion layer mobility in Si MOSFET’s: Part I-effects of substrate impurity concentration. IEEE Trans. Electron Devices 1994, 41, 2357–2362. [Google Scholar] [CrossRef]

- Teramoto, A.; Hamada, T.; Yamamoto, M.; Gaubert, P.; Akahori, H.; Nii, K.; Hirayama, M.; Arima, K.; Endo, K.; Sugawa, S.; et al. Very High Carrier Mobility for High-Performance CMOS on a Si(110) Surface. IEEE Trans. Electron Devices 2007, 54, 1438–1445. [Google Scholar] [CrossRef]

- Ohmi, T.; Miyashita, M.; Itano, M.; Imaoka, T.; Kawanabe, I. Dependence of thin-oxide films quality on surface microroughness. IEEE Trans. Electron Devices 1992, 39, 537–545. [Google Scholar] [CrossRef]

- Morita, M.; Teramoto, A.; Makihara, K.; Ohmi, T.; Nakazato, Y.; Uchiyama, A.; Abe, T. Effects of Si Wafer Surface Micro-Roughness on Electrical Properties of Very-Thin Gate Oxide Films. In ULSI Science and Technology/1991; Electrochemical Society: Pennington, NJ, USA, 1991; pp. 400–408. [Google Scholar]

- Makihara, K.; Teramoto, A.; Nakamura, K.; Kwon, M.Y.; Morita, M.; Ohmi, T. Preoxide-Controlled Oxidation for Very Thin Oxide Films. Jpn. J. Appl. Phys. 1993, 32, 294–297. [Google Scholar] [CrossRef]

- Gaubert, P.; Teramoto, A.; Hamada, T.; Yamamoto, M.; Nii, K.; Akahori, H.; Kotani, K.; Ohmi, T. Impact of interface micro-roughness on low frequency noise in (110) and (100) pMOSFETs. In Proceedings of the 18th International Conference on Noise and Fluctuations, Salamanca, Spain, 19–23 September 2005; pp. 199–202. [Google Scholar]

- Gaubert, P.; Teramoto, A.; Hamada, T.; Yamamoto, M.; Kotani, K.; Ohmi, T. 1/f noise suppression of pMOSFETs fabricated on Si(100) and Si(110) using an alkali-free cleaning process. IEEE Trans. Electron Devices 2006, 53, 851–856. [Google Scholar] [CrossRef]

- Matsushita, Y.; Watatsuki, M.; Saito, Y. Improvement of Silicon Surface Quality by H2 Anneal. In Proceedings of the Conference of Solid State Device and Materials, Tokyo, Japan, 20–22 August 1986; pp. 529–535. [Google Scholar]

- Morita, Y.; Tokumoto, H. Atomic scale flattening and hydrogen termination of the Si(001) surface by wet-chemical treatment. In Proceedings of the 42nd national symposium of the American Vacuum Society, Mineapolis, MN, USA, 16–20 October 1995; pp. 854–858. [Google Scholar]

- Kuroda, R.; Teramoto, A.; Suwa, T.; Hasebe, R.; Li, X.; Konda, M.; Sugawa, S.; Ohmi, T. Atomically flat gate insulator/silicon (100) interface formation introducing high mobility, ultra-low noise, and small characteristics variation CMOSFET. In Proceedings of the 38th European Solid-State Device Research Conference, Edinburgh, UK, 15–19 September 2008; pp. 83–86. [Google Scholar]

- Li, X.; Suwa, T.; Teramoto, A.; Kuroda, R.; Sugawa, S.; Ohmi, T. Atomically Flattening Technology at 850 °C for Si(100) Surface. ECS Trans. 2010, 28, 299–309. [Google Scholar] [CrossRef]

- Li, X.; Teramoto, A.; Suwa, T.; Kuroda, R.; Sugawa, S.; Ohmi, T. Formation speed of atomically flat surface on Si (100) in ultra-pure argon. Microelectron. Eng. 2011, 88, 3133–3139. [Google Scholar] [CrossRef]

- Goto, T.; Kuroda, R.; Suwa, T.; Teramoto, A.; Akagawa, N.; Kimoto, D.; Sugawa, S.; Ohmi, T.; Kamata, Y.; Kumagai, Y.; et al. Low Temperature Atomically Flattening of Si Surface of Shallow Trench Isolation Pattern. ECS Trans. 2015, 66, 285–292. [Google Scholar] [CrossRef]

- Goto, T.; Kuroda, R.; Akagawa, N.; Suwa, T.; Teramoto, A.; Li, X.; Obara, T.; Kimoto, D.; Sugawa, S.; Ohmi, T.; et al. Atomically flattening of Si surface of silicon on insulator and isolation-patterned wafers. Jpn. J. Appl. Phys. 2015, 54. [Google Scholar] [CrossRef]

- Goto, T.; Kuroda, R.; Akagawa, N.; Suwa, T.; Teramoto, A.; Li, X.; Obara, T.; Kimoto, D.; Sugawa, S.; Kamata, Y.; et al. Introduction of Atomically Flattening of Si Surface to Large-Scale Integration Process Employing Shallow Trench Isolation. ECS J. Solid State Sci. Technol. 2016, 5, P67–P72. [Google Scholar] [CrossRef]

- Gaubert, P.; Kircher, A.; Park, H.; Kuroda, R.; Sugawa, S.; Goto, T.; Suwa, T.; Teramoto, A. Atomically flat interface for noise reduction in SOIMOSFETs. In Proceedings of the 24th International Conference on Noise and Fluctuations, Vilnius, Lithuania, 20–23 June 2017. [Google Scholar]

- Tanaka, K.; Watanabe, K.; Ishino, H.; Sugawa, S.; Teramoto, A.; Hirayama, M.; Ohmi, T. A Technology for Reducing Flicker Noise for ULSI Applications. Jpn. J. Appl. Phys. 2003, 42, 2106–2109. [Google Scholar] [CrossRef]

- Kuroda, R.; Suwa, T.; Teramoto, A.; Hasebe, R.; Sugawa, S.; Ohmi, T. Atomically Flat Silicon Surface and Silicon/Insulator Interface Formation Technologies for (100) Surface Orientation Large-Diameter Wafers Introducing High Performance and Low-Noise Metal-Insulator-Silicon FETs. IEEE Trans. Electron Devices 2009, 56, 291–298. [Google Scholar] [CrossRef]

- Gaubert, P.; Kuroda, R.; Endo, S.; Kuboyama, Y.; Kitagaki, T.; Nada, H.; Tamura, H.; Teramoto, A.; Ohmi, T. Atomically Flat Interface for the Reduction of the Low Frequency Noise on Si(100) nMOS Transistors. In Proceedings of the 215th ECS Meeting, San Francisco, CA, USA, 24–29 May 2009; p. 916. [Google Scholar]

| Gate Length (μm) | Gate Width (μm) | Number of MOSFETs | Supply Voltage (V) |

|---|---|---|---|

| 0.22 | 0.28 | 131,072 (128 × 1024) | 2.5 |

| 0.22 | 0.30 | 131,072 | |

| 0.24 | 0.30 | 131,072 | |

| 0.24 | 1.5 | 131,072 | |

| 0.24 | 15 | 131,072 | |

| 0.4 | 1.5 | 32,768 (128 × 256) | |

| 0.4 | 15 | 32,768 | |

| 1.2 | 0.3 | 65,536 (64 × 1024) | |

| 1.2 | 1.5 | 65,536 | |

| 4.0 | 0.30 | 65,536 | |

| 4.0 | 1.5 | 65,536 | |

| 0.24 | 0.30 | 32,768 (AR:100) | |

| 0.24 | 0.30 | 4096 (16 × 256, AR:1000) | |

| 0.24 | 0.30 | 1344 (32 × 42, AR:10000) | |

| 0.4 | 1.5 | 131,072 | 3.3 |

| 0.4 | 15 | 32,768 | |

| 1.2 | 15 | 16,384 (64 × 256) | |

| 4.0 | 15 | 16,384 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Teramoto, A. Evaluation of Low-Frequency Noise in MOSFETs Used as a Key Component in Semiconductor Memory Devices. Electronics 2021, 10, 1759. https://doi.org/10.3390/electronics10151759

Teramoto A. Evaluation of Low-Frequency Noise in MOSFETs Used as a Key Component in Semiconductor Memory Devices. Electronics. 2021; 10(15):1759. https://doi.org/10.3390/electronics10151759

Chicago/Turabian StyleTeramoto, Akinobu. 2021. "Evaluation of Low-Frequency Noise in MOSFETs Used as a Key Component in Semiconductor Memory Devices" Electronics 10, no. 15: 1759. https://doi.org/10.3390/electronics10151759

APA StyleTeramoto, A. (2021). Evaluation of Low-Frequency Noise in MOSFETs Used as a Key Component in Semiconductor Memory Devices. Electronics, 10(15), 1759. https://doi.org/10.3390/electronics10151759